# A NOVEL DYNAMIC POWER CUTOFF TECHNOLOGY (DPCT) FOR ACTIVE LEAKAGE REDUCTION IN DEEP SUBMICRON VLSI CMOS CIRCUITS

# **BY BAOZHEN YU**

A dissertation submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Doctor of Philosophy Graduate Program in Electrical and Computer Engineering Written under the direction of Prof. Michael L. Bushnell and approved by

> New Brunswick, New Jersey October, 2007

# ABSTRACT OF THE DISSERTATION

# A Novel Dynamic Power Cutoff Technology (DPCT) for Active Leakage Reduction in Deep Submicron VLSI CMOS Circuits

# by Baozhen Yu Dissertation Director: Prof. Michael L. Bushnell

Due to the exponential increase of subthreshold and gate leakage currents with technology scaling, leakage power is increasingly significant in CMOS circuits as the technology scales down. The leakage power is as much as 50% of the total power in the 90*nm* technology and is becoming dominant in more advanced CMOS technologies with smaller feature sizes. Also, the leakage in active mode is significantly larger due to the higher die temperature in active mode. Although many leakage reduction techniques have been proposed, most of them can only reduce the circuit leakage power in standby mode.

In this thesis, we present a novel active leakage power reduction technique using dynamic power cutoff, called the *dynamic power cutoff technique* (DPCT). To reduce the active leakage power, we target the idle part of the circuit when it is in active mode. First, the *switching window* for each gate, during which a gate makes its transitions, is identified by static timing analysis. Then, the circuit is optimally partitioned into different groups based on the *minimal switching window* (MSW) of each gate. Finally, power cutoff transistors are inserted into each group to control the power connections of that group. The power of each gate is only turned on during a small timing window within each clock cycle, which results in significant active leakage power savings. Standby leakage can also be reduced by turning off the power connections of all gates all of the time once the circuit is idle. This technique also reduces dynamic power and short-circuit power by reducing the circuit glitches.

Experimental results on ISCAS '85 benchmark circuits at the logic level modeled using

70*nm* Berkeley Predictive Models show up to 90% of active leakage, 99% of standby leakage, up to 54% of dynamic, and up to 72% of total power savings. DPCT can also reduce the maximal voltage drop on the power grid by more than 30% on average. With process variations, the average total power and active leakage power savings will be reduced by 12.7% and 14.8%, respectively. In spite of that, DPCT still gives excellent power savings, which are 73.6% of active leakage power and 34.7% of total power under process variations. We also implemented the layouts of a 16-bit multiplier and a c432 using DPCT. The experimental results for the layout designs confirmed the effectiveness of DPCT in physical level design.

# Acknowledgements

First, I would like to thank Prof. Michael Bushnell, my advisor, for his guidance, encouragement and patience on my Ph.D. research and dissertation. Second, I would like to thank all my committee members for their comments on my dissertation. Finally, I would like to thank all of the members of my research group for their valuable comments and suggestions on my dissertation.

# Dedication

To my grandmother, father, mother, sister, and my wife.

# **Table of Contents**

| Ab | strac             | <b>t</b>                           |             |                                                        | ii  |  |  |  |  |  |  |

|----|-------------------|------------------------------------|-------------|--------------------------------------------------------|-----|--|--|--|--|--|--|

| Ac | Acknowledgements  |                                    |             |                                                        |     |  |  |  |  |  |  |

| De | <b>Dedication</b> |                                    |             |                                                        |     |  |  |  |  |  |  |

| Li | List of Tables    |                                    |             |                                                        |     |  |  |  |  |  |  |

| Li | st of F           | ligures                            |             |                                                        | xii |  |  |  |  |  |  |

| 1. | Intro             | oduction                           | <b>n</b>    |                                                        | 1   |  |  |  |  |  |  |

|    | 1.1.              | Backg                              | ound and    | Motivation                                             | 1   |  |  |  |  |  |  |

|    | 1.2.              | Problem                            | m Stateme   | nt                                                     | 2   |  |  |  |  |  |  |

|    | 1.3.              | Summa                              | ary of Orig | ginal Contributions                                    | 2   |  |  |  |  |  |  |

|    | 1.4.              | Organi                             | zation of t | he Thesis                                              | 2   |  |  |  |  |  |  |

| 2. | Prio              | r Work                             | : Techniq   | ues for Leakage Power Reduction                        | 4   |  |  |  |  |  |  |

|    | 2.1.              | Introdu                            | ction       |                                                        | 4   |  |  |  |  |  |  |

|    | 2.2.              | Power Dissipation in CMOS Circuits |             |                                                        |     |  |  |  |  |  |  |

|    |                   | 2.2.1. Dynamic Power               |             |                                                        |     |  |  |  |  |  |  |

|    |                   | 2.2.2.                             | Short-Cir   | cuit Power                                             | 5   |  |  |  |  |  |  |

|    |                   | 2.2.3.                             | Leakage     | Power                                                  | 5   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.1.    | pn Junction Reversed-Bias Current                      | 6   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.2.    | Subthreshold Leakage Current                           | 7   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.3.    | Tunneling into and through Gate Oxide                  | 8   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.4.    | Injection of Hot Carriers from Substrate to Gate Oxide | 9   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.5.    | Gate-Induced Drain Leakage (GIDL)                      | 9   |  |  |  |  |  |  |

|    |                   |                                    | 2.2.3.6.    | Punchthrough                                           | 9   |  |  |  |  |  |  |

|    | 2.3.              | Techno                             | ology Tren  | ds of Power Dissipation in CMOS Circuits               | 10  |  |  |  |  |  |  |

|    |      | 2.3.1.   | Dynamic    | Power vs. Leakage Power                                   | 10 |

|----|------|----------|------------|-----------------------------------------------------------|----|

|    |      | 2.3.2.   | Relative   | Magnitudes of Different Leakage Power Components          | 11 |

|    | 2.4. | Leakag   | ge Power R | Reduction Techniques                                      | 12 |

|    |      | 2.4.1.   | Device-L   | evel Leakage Reduction Techniques                         | 12 |

|    |      |          | 2.4.1.1.   | Retrograde Doping                                         | 13 |

|    |      |          | 2.4.1.2.   | Halo Doping                                               | 14 |

|    |      | 2.4.2.   | Circuit-L  | evel Leakage Reduction Techniques                         | 15 |

|    |      |          | 2.4.2.1.   | Transistor Stacking                                       | 15 |

|    |      |          | 2.4.2.2.   | Leakage Reduction by Input Vector Control                 | 16 |

|    |      |          | 2.4.2.3.   | Leakage Reduction by Multiple Threshold Voltage Designs . | 16 |

|    |      |          | 2.4.2.4.   | Leakage Reduction by Power Cut-Off                        | 18 |

|    |      |          | 2.4.2.5.   | Dynamic Power Gating Using the Shannon Expansion          | 20 |

|    |      | 2.4.3.   | Summary    | 7                                                         | 20 |

| 3. | Drio | r Wark   | Dowor C    | rid and Process Variation Analysis                        | 22 |

| 5. |      |          |            |                                                           |    |

|    | 5.1. | 3.1.1.   |            | rid Modeling                                              |    |

|    |      | 3.1.2.   |            | ver Grid Analysis Techniques                              |    |

|    | 32   |          |            |                                                           |    |

|    | 5.2. | 3.2.1.   |            | Variation Modeling                                        |    |

|    |      | 3.2.2.   |            | 1 Static Timing Analysis                                  |    |

|    |      | 3.2.3.   |            | tistical Static Timing Analysis Techniques                |    |

|    |      | 5.2.5.   | 11101 514  |                                                           | 21 |

| 4. | Nove | el Dynai | nic Power  | Cutoff Technique (DPCT)                                   | 28 |

|    | 4.1. | Introdu  | iction     |                                                           | 28 |

|    | 4.2. | Basic I  | dea of DP  | СТ                                                        | 28 |

|    | 4.3. | Six Ste  | ps to Impl | ement DPCT                                                | 29 |

|    |      | 4.3.1.   | 1st Step:  | Calculate the Minimal Switching Window of Each Gate by    |    |

|    |      |          | Static Tir | ning Analysis                                             | 30 |

|    |      |          | 4.3.1.1.   | Switching Window Based on Traditional Timing Window       | 30 |

|    |      |          | 4.3.1.2.   | Minimal Switching Window                                  | 32 |

|    |      | 4.3.2.      | 2nd Step:   | Heuristic Partitioning of the Circuit by Dynamic Programming | 33 |

|----|------|-------------|-------------|--------------------------------------------------------------|----|

|    |      |             | 4.3.2.1.    | The Objective Function to Optimize                           | 34 |

|    |      |             | 4.3.2.2.    | Computational Complexity of Finding the Optimal Partition .  | 36 |

|    |      |             | 4.3.2.3.    | Basic Ideas of the Heuristic Partitioning Algorithm by Dy-   |    |

|    |      |             |             | namic Programming                                            | 36 |

|    |      |             | 4.3.2.4.    | Flow of the Heuristic Partitioning Algorithm                 | 37 |

|    |      |             | 4.3.2.5.    | Computational Complexity and Memory Complexity of the        |    |

|    |      |             |             | Heuristic Partitioning Algorithm                             | 42 |

|    |      |             | 4.3.2.6.    | Experimental Results of the Partitioning Algorithm           | 42 |

|    |      | 4.3.3.      | 3rd Step:   | Insert Cutoff MOSFETs                                        | 43 |

|    |      | 4.3.4.      | 4th Step:   | Generate Cutoff Control Signals                              | 44 |

|    |      | 4.3.5.      | 5th Step:   | Add Latches to POs to Capture the Data                       | 45 |

|    |      | 4.3.6.      | 6th Step:   | Verify the DPCT Circuit Using Analog Simulation              | 46 |

|    | 4.4. | Power       | Savings of  | DPCT                                                         | 46 |

| 5. | Powe | er Grid     | and Proce   | ess Variation Analysis on DPCT                               | 47 |

|    | 5.1. | Introdu     | ction       |                                                              | 47 |

|    | 5.2. | Power       | Grid Analy  | vsis on DPCT                                                 | 47 |

|    |      | 5.2.1.      | Modeling    | of Power Grid                                                | 48 |

|    |      | 5.2.2.      | Procedure   | es                                                           | 49 |

|    | 5.3. | Process     | s Variation | Analysis on DPCT                                             | 50 |

|    |      | 5.3.1.      | Modeling    | of Process Variations                                        | 50 |

|    |      | 5.3.2.      | Modeling    | of Gate Delay                                                | 51 |

|    |      | 5.3.3.      | Procedure   | es                                                           | 52 |

|    | 5.4. | Summa       | ary         |                                                              | 53 |

| 6. | Resu | l <b>ts</b> |             |                                                              | 54 |

|    | 6.1. | Experii     | mental Res  | sults for Power Savings                                      | 54 |

|    |      | 6.1.1.      | Power Sa    | vings for DPCT                                               | 55 |

|    |      | 6.1.2.      | Power Ef    | feciency Improvements for DPCT                               | 55 |

|    |      | 6.1.3.      | Effect of   | MSW Window Size on Power Savings of DPCT                     | 56 |

|    |      | 6.1.4.   | Delay an   | d Area Cost of DPCT                                           | 57 |

|----|------|----------|------------|---------------------------------------------------------------|----|

|    | 6.2. | Experi   | mental Re  | sults of Power Grid Analysis                                  | 57 |

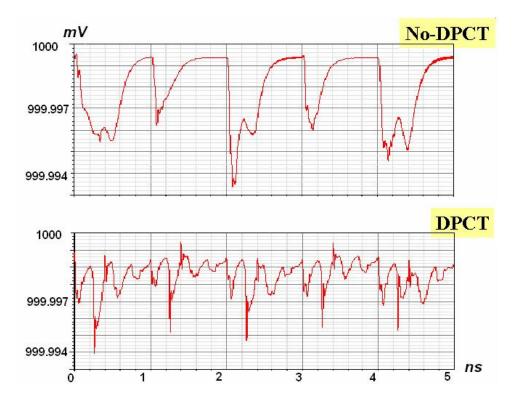

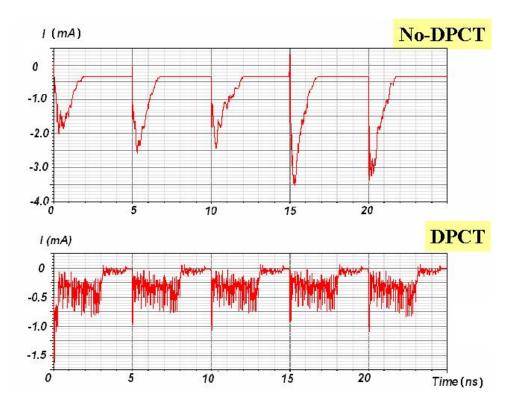

|    |      | 6.2.1.   | A Typica   | l Power Grid Node for DPCT and non-DPCT Circuits              | 58 |

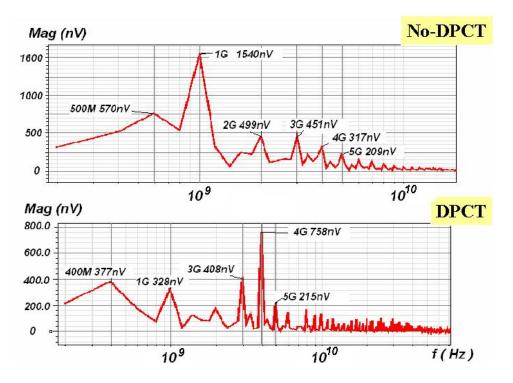

|    |      | 6.2.2.   | Spectral   | Analysis of Power Grid Nodes                                  | 59 |

|    |      | 6.2.3.   | Maximal    | Voltage Drop on All Power Grid Nodes                          | 59 |

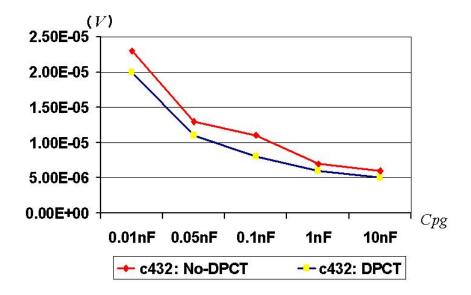

|    |      | 6.2.4.   | Maximal    | Voltage Drop vs. $C_{PG}$                                     | 60 |

|    |      | 6.2.5.   | Summar     | y of Power Grid Analysis                                      | 61 |

|    | 6.3. | Experi   | mental Re  | sults for Process Variation Analysis                          | 62 |

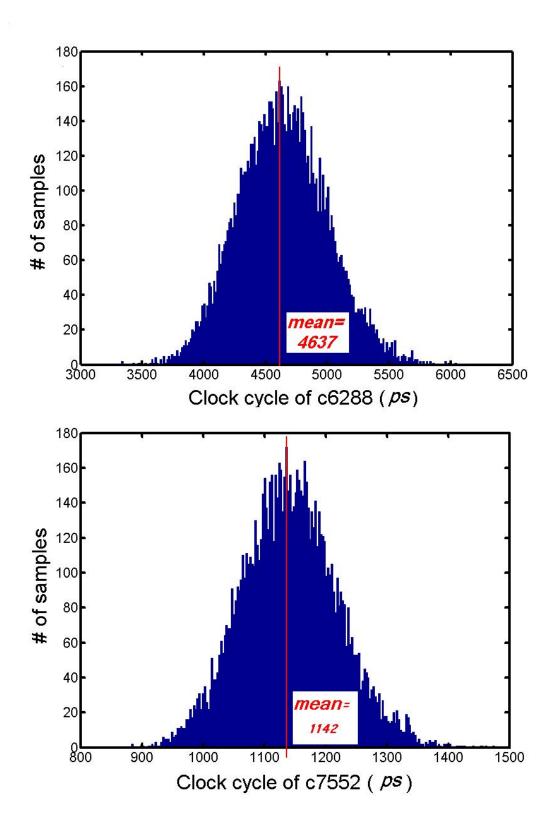

|    |      | 6.3.1.   | Process V  | Variations' Effect on Clock Cycles                            | 63 |

|    |      | 6.3.2.   | Process V  | Variations' Effect on Cutoff Windows                          | 65 |

|    |      | 6.3.3.   | Process V  | Variations' Effect on Power Savings                           | 65 |

|    |      | 6.3.4.   | Conclusi   | ons on Process Variation Analysis                             | 66 |

| 7. | A La | ayout Ir | nplement   | ation of DPCT                                                 | 67 |

|    | 7.1. | Introdu  | uction     |                                                               | 67 |

|    | 7.2. | Backg    | round on   | Application-Specific Integrated Circuit (ASIC) and Custom-    |    |

|    |      | Design   | Flow       |                                                               | 67 |

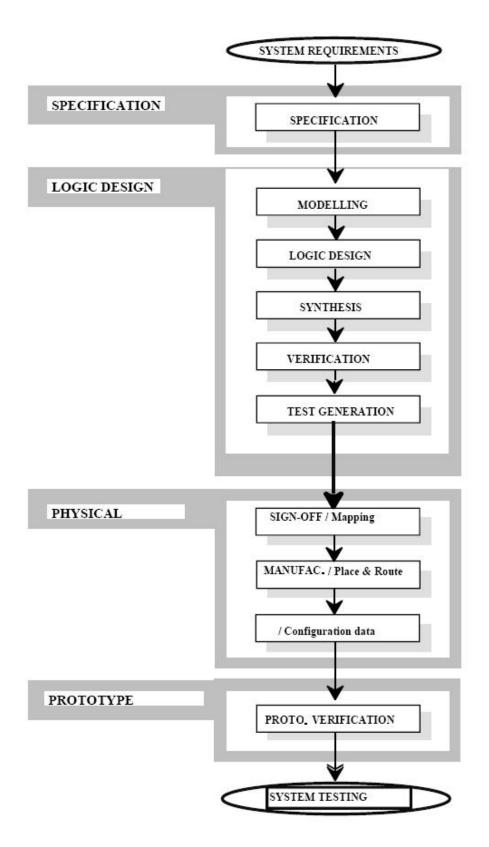

|    |      | 7.2.1.   | ASIC De    | sign Flow                                                     | 68 |

|    |      | 7.2.2.   | Custom-    | Design Flow                                                   | 68 |

|    | 7.3. | Physic   | al Implem  | entation of a 16-bit Multiplier with DPCT                     | 70 |

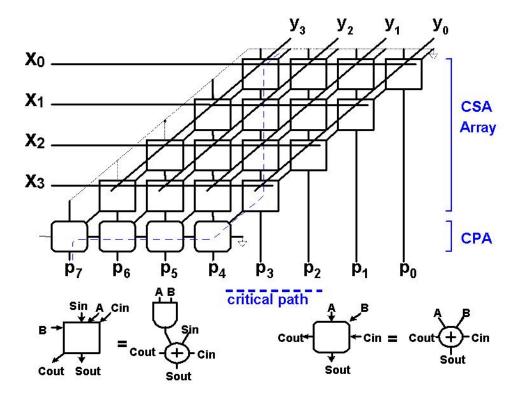

|    |      | 7.3.1.   | Architec   | ture of the 16-bit Multiplier                                 | 70 |

|    |      |          | 7.3.1.1.   | Layout Design of the 16-bit Multiplier without DPCT           | 71 |

|    |      |          | 7.3.1.2.   | Procedures for the Layout Design of the 16-bit Multiplier     |    |

|    |      |          |            | with DPCT                                                     | 72 |

|    |      |          | 7.3.1.3.   | Experimental Results for the 16-bit Multiplier with and with- |    |

|    |      |          |            | out DPCT                                                      | 78 |

|    | 7.4. | Standa   | rd Cell Ba | sed Physical Design Using DPCT                                | 80 |

|    |      | 7.4.1.   | Adjustm    | ents of the Traditional Standard Cell Based Physical Design   |    |

|    |      |          | Flow for   | DPCT                                                          | 80 |

|    |      |          | 7.4.1.1.   | Modification of the Physical Standard Cell Library            | 80 |

|    |      |          | 7.4.1.2.   | Modification of the Logical Standard Cell Library             | 81 |

| 7.4.1.3. Modification of the Logic Synthesis and Layout Automatic          | 2     |

|----------------------------------------------------------------------------|-------|

| Placement and Routing Tools                                                | . 82  |

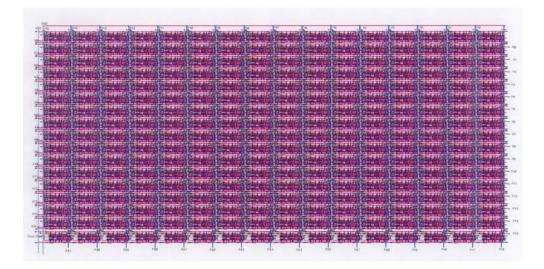

| 7.4.2. Layout Design of c432 Using the Modified Standard Cell Based Design | 1     |

| Flow                                                                       | . 82  |

| 7.4.2.1. Steps of Standard Cell Based Layout Design of c432                | . 82  |

| 7.4.2.2. Experimental Results of the Standard Cell Based Layout De         | -     |

| sign of c432                                                               | . 86  |

| 7.5. Does DPCT Support the Power Saving Mode with a Slowed Clock Rate?     | . 88  |

| 7.6. Summary                                                               | . 89  |

| 8. Conclusion and Future Work                                              | . 90  |

| 8.1. Conclusion                                                            | . 90  |

| 8.2. Future Work                                                           | . 90  |

| Appendix A. User's Guide                                                   | . 92  |

| A.1. Heuristic Partitioning of Circuits                                    | . 92  |

| A.2. Power Grid Analysis                                                   | . 92  |

| A.3. Process Variation Analysis                                            | . 93  |

| A.4. Standard Cell Based Layout Design                                     | . 93  |

| References                                                                 | . 94  |

| Curriculum Vita                                                            | . 101 |

# List of Tables

| Estimated Average Power Savings and Cost vs. pb for ISCAS '85 Circuits       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Heuristic Partitioning Results on ISCAS '85 Benchmarks                       | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Complexity of our Partitioning Algorithm                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Power Grid Size of Each ISCAS '85 Benchmark Circuit                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Nominal Values for $L, W, t_{ox}$ and $V_{th}$                               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BSIM3v3 Model Parameters of the 70nm CMOS Process by Berkeley Predic-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tive Models                                                                  | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Power Savings and Area Cost of DPCT on ISCAS '85 Benchmarks                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Minimal MSW Size of ISCAS '85 Circuits and the Corresponding Power Savings   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Area Cost of DPCT on ISCAS '85 Benchmarks                                    | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Maximal Voltage Drop on ISCAS '85 Benchmarks                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Clock Cycles (ps) of ISCAS '85 Benchmark Circuits under Process Variations . | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Process Variations' Effect on DPCT with ISCAS '85 Benchmarks                 | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Performance of DPCT on the Layout Design of a 16-bit Multiplier              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Comparison of DPCT's Performance on c6288 and Layout Level 16-bit Multiplier | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Performance of DPCT on the Layout Design of c432                             | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Time for Virtual <i>VDD/GND</i> to Collapse in c432                          | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                              | Complexity of our Partitioning Algorithm       Power Grid Size of Each ISCAS '85 Benchmark Circuit         Power Grid Size of Each ISCAS '85 Benchmark Circuit       Nominal Values for L, W, t <sub>ox</sub> and V <sub>th</sub> Nominal Values for L, W, t <sub>ox</sub> and V <sub>th</sub> BSIM3v3 Model Parameters of the 70nm CMOS Process by Berkeley Predictive Models         Bower Savings and Area Cost of DPCT on ISCAS '85 Benchmarks       Power Savings and Area Cost of DPCT on ISCAS '85 Benchmarks         Minimal MSW Size of ISCAS '85 Circuits and the Corresponding Power Savings         Area Cost of DPCT on ISCAS '85 Benchmarks         Maximal Voltage Drop on ISCAS '85 Benchmarks         Clock Cycles (ps) of ISCAS '85 Benchmarks         Process Variations' Effect on DPCT with ISCAS '85 Benchmarks         Performance of DPCT on the Layout Design of a 16-bit Multiplier         Comparison of DPCT's Performance on c6288 and Layout Level 16-bit Multiplier |

# List of Figures

| 2.1.  | A CMOS Inverter                                                                   | 4  |

|-------|-----------------------------------------------------------------------------------|----|

| 2.2.  | Leakage Current Mechanisms of Deep-Submicron Transistors [34]                     | 6  |

| 2.3.  | Dynamic Power Trend [35]                                                          | 11 |

| 2.4.  | Leakage Power Trend [35]                                                          | 11 |

| 2.5.  | Contribution of Different Leakage Components in <i>n</i> MOS Devices at Different |    |

|       | Technology Generations [7]                                                        | 12 |

| 2.6.  | Band Diagrams (Shown on Top) at the Threshold Condition for a Uniformly           |    |

|       | Doped and an Extreme Retrograde-Doped Channel (Doping Profiles Shown at           |    |

|       | Bottom) [75]                                                                      | 13 |

| 2.7.  | Halo or Nonuniform Channel Doping                                                 | 14 |

| 2.8.  | Stacking Effect in Two-Input NAND Gate                                            | 15 |

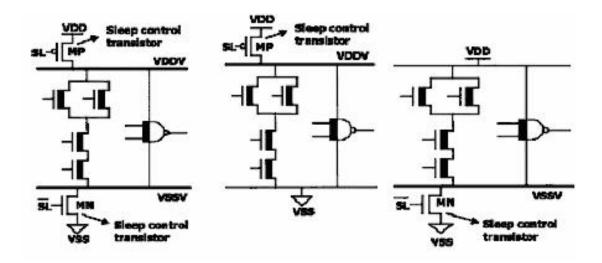

| 2.9.  | (a) Original MTCMOS (b) pMOS Insertion MTCMOS (c) nMOS Insertion                  |    |

|       | MTCMOS [54]                                                                       | 17 |

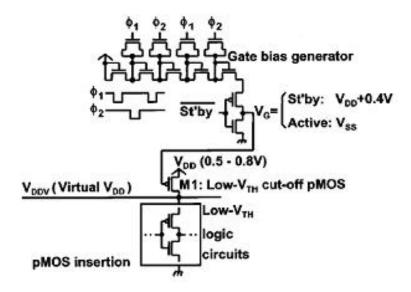

| 2.10. | Concept of SCCMOS                                                                 | 19 |

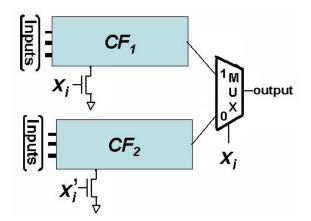

| 2.11. | Dynamic Supply Gating Using the Shannon Expansion                                 | 20 |

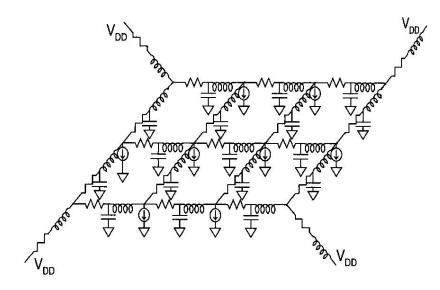

| 3.1.  | <i>RLC</i> Model of Power Grid                                                    | 23 |

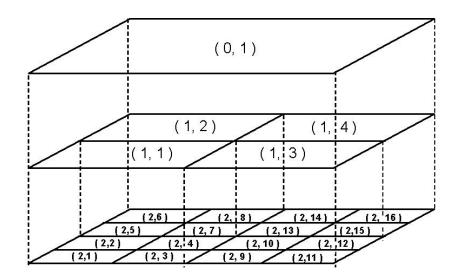

| 3.2.  | Modeling Spatial Correlations Using Quad-Tree Partitioning [6]                    | 25 |

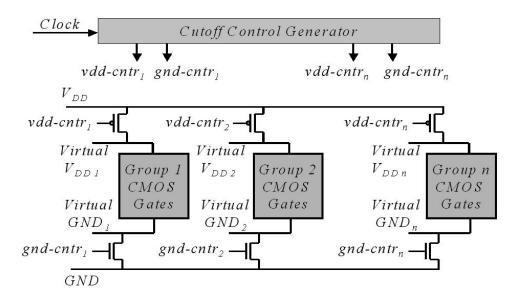

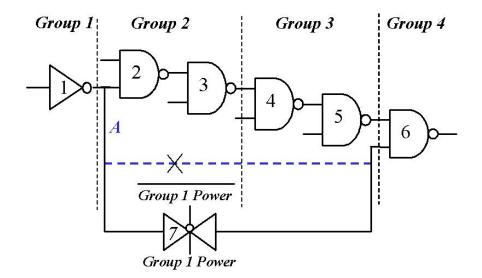

| 4.1.  | Architecture of a Circuit with DPCT                                               | 29 |

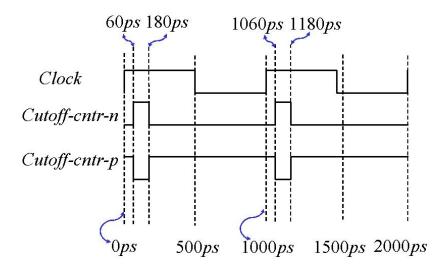

| 4.2.  | The Clock and One Pair of Cutoff Control Signals                                  | 30 |

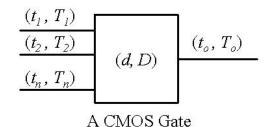

| 4.3.  | Timing Window of a CMOS Gate                                                      | 31 |

| 4.4.  | A Special Case of DPCT                                                            | 34 |

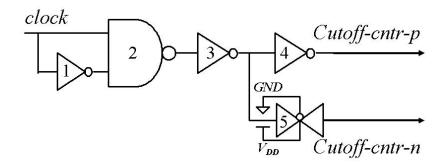

| 4.5.  | Clock Stretcher for Generating Cutoff Control Signals                             | 45 |

| 5.1.  | Mapping a DPCT Circuit to a Power Grid                                            | 48 |

| 5.2.  | Modeling Spatial Correlations Using Quad-Tree Partitioning [5]                    | 51 |

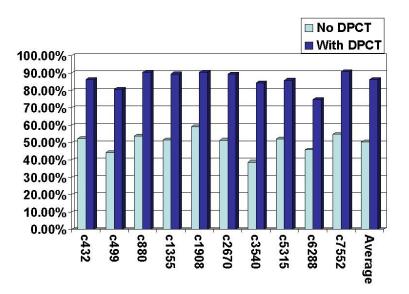

| 6.1.  | Power Efficiencies of <i>ISCAS</i> '85 Benchmarks with and without DPCT           | 56 |

| 6.2.  | Typical Waveform of a Power Grid Node                                                | 58 |

|-------|--------------------------------------------------------------------------------------|----|

| 6.3.  | The Spectrum of a Power Grid Node                                                    | 59 |

| 6.4.  | Total Current of c6288 without DPCT and with DPCT                                    | 61 |

| 6.5.  | Maximal Voltage Drop versus $C_{PG}$                                                 | 62 |

| 6.6.  | Histograms of the Clock Cycles of c6288 and c7552                                    | 64 |

| 7.1.  | ASIC Design Flow                                                                     | 69 |

| 7.2.  | The Architecture of a 4-bit Multiplier                                               | 71 |

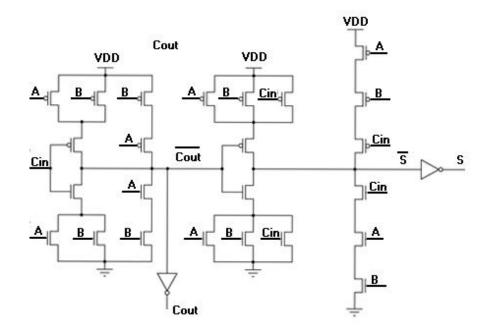

| 7.3.  | The Schematic of a Full Adder                                                        | 72 |

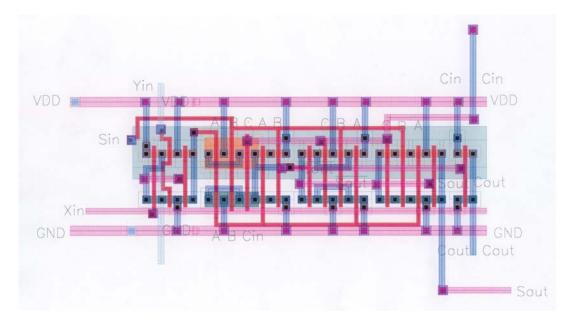

| 7.4.  | The Layout of a 1-bit CSA                                                            | 73 |

| 7.5.  | The Layout of a 1-bit CPA                                                            | 73 |

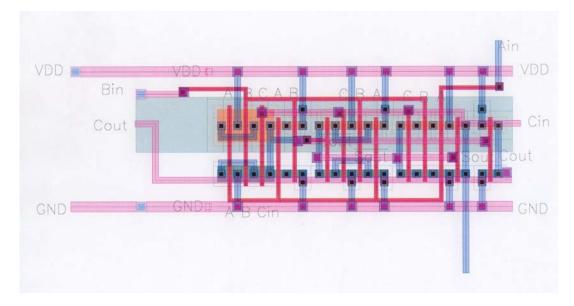

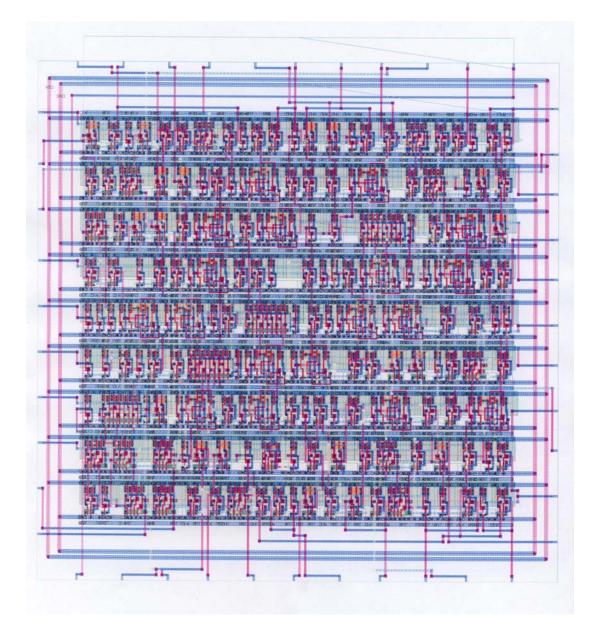

| 7.6.  | The Layout of the 16-bit Multiplier without DPCT                                     | 74 |

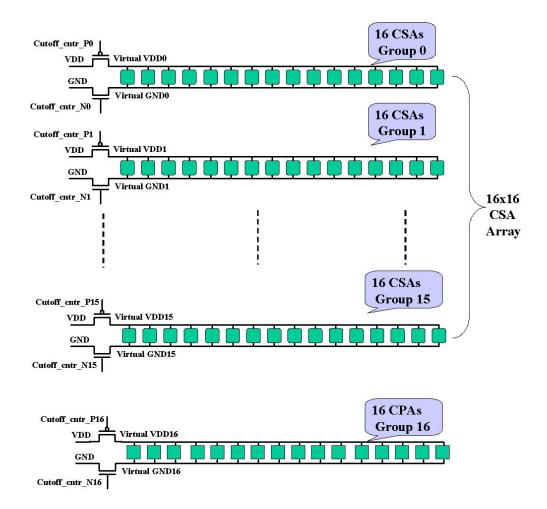

| 7.7.  | The Architecture of the 16-bit Multiplier with DPCT                                  | 74 |

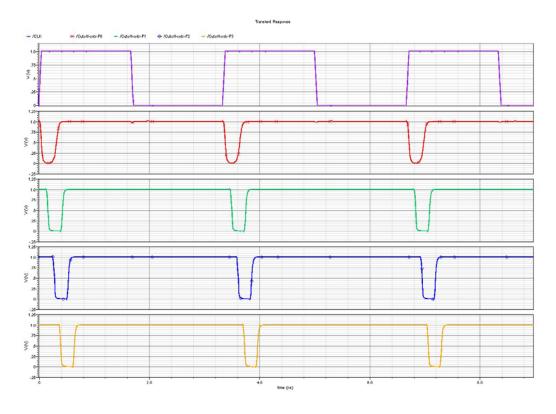

| 7.8.  | The System Clock and <i>p</i> MOSFT Cutoff Control Signals for Groups 0 to $3 \dots$ | 76 |

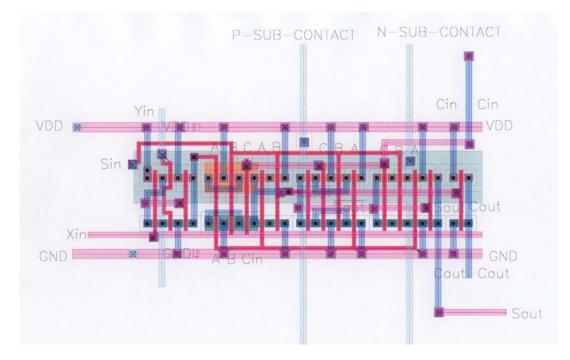

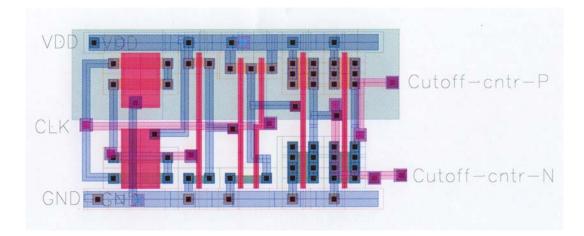

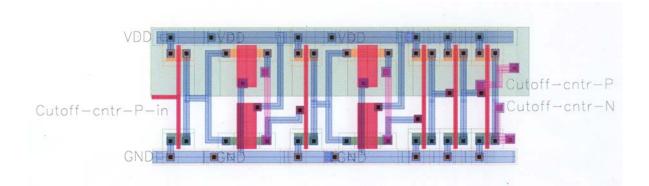

| 7.9.  | The Layout of a 1-bit CSA for DPCT                                                   | 76 |

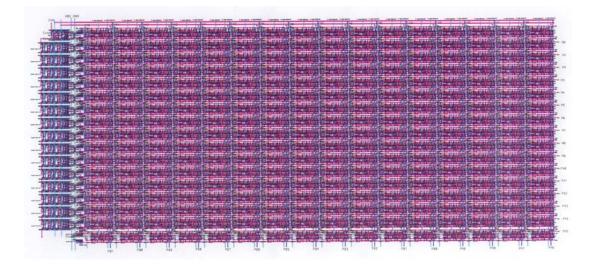

| 7.10. | The Layout of the 16-bit Multiplier with DPCT                                        | 77 |

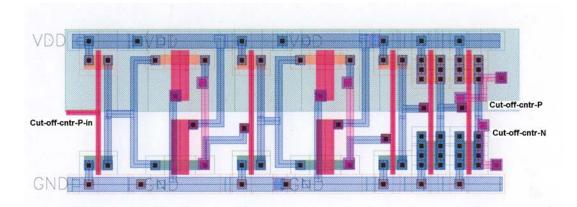

| 7.11. | The Layout of the Cutoff Control Generator for Group 0                               | 77 |

| 7.12. | The Layout of the Cutoff Control Shifter                                             | 78 |

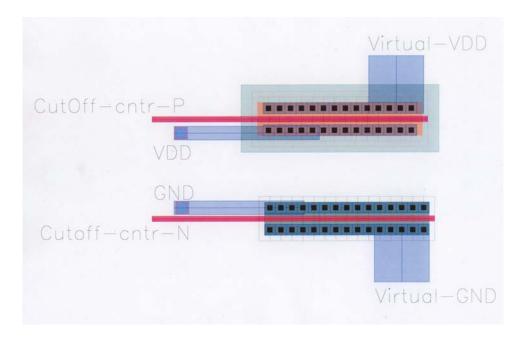

| 7.13. | The Layout of the Cutoff MOSFETs for One Group                                       | 79 |

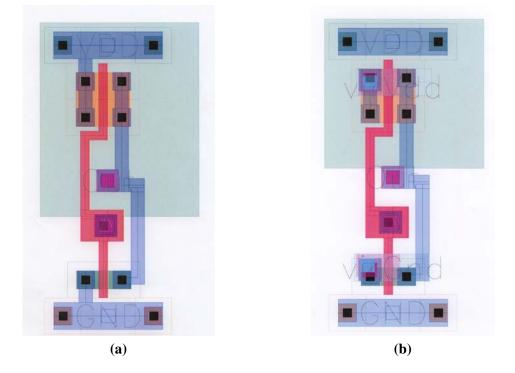

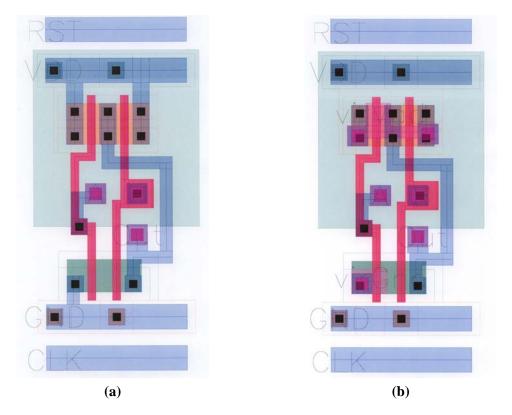

| 7.14. | The <i>INVERTER</i> Layout of Traditional (a) and DPCT Standard Cell Library (b)     | 81 |

| 7.15. | The NAND2 Layout of Traditional (a) and DPCT Standard Cell Library (b)               | 83 |

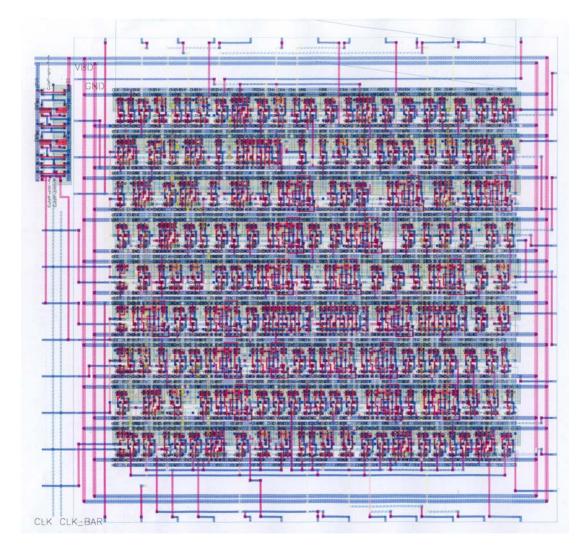

| 7.16. | The Layout of c432 without DPCT                                                      | 85 |

| 7.17. | The Layout of the Cutoff Control Shifter Used in c432                                | 86 |

| 7.18. | The Layout of c432 with DPCT                                                         | 87 |

# **Chapter 1**

# Introduction

# 1.1 Background and Motivation

There are three sources of power dissipation in CMOS digital circuits: dynamic power, shortcircuit power and leakage power. Usually, the dynamic power is dominant and the other two parts are negligible. But this will not be the case as the CMOS technology scales down further. As the CMOS technology scales down, the supply voltage must be reduced such that dynamic power can be kept at reasonable levels. In order to prevent a negative effect on performance, the threshold voltage must be reduced at a rate such that a sufficient gate overdrive is maintained. This reduction in the threshold voltage causes an increase in the leakage current of about 5 times per generation, which in turn can increase the static power of the device to unacceptable levels. In 0.1um CMOS technology, the leakage power is approaching 30% of the total processor power [13]. The leakage power is as much as 50% of the total power in the 90nm technology [23]. Thus, leakage reduction is necessary for CMOS technologies below 0.1um. Also, leakage is important in both standby and active operation modes. Actually, the leakage in active mode is significantly larger due to the higher die temperature in active mode.

To solve the leakage problem many leakage reduction techniques have been proposed. Among them, some require modification of the process technology, achieving leakage reduction during the fabrication stage. Others are based on circuit-level optimization schemes that require architecture support. In spite of all these available techniques to reduce leakage power in circuits, leakage power still remains a big problem for deep submicron circuits. Furthermore, most of the available leakage reduction techniques can only reduce the circuit leakage power in standby mode. So, more efficient active leakage power reduction techniques are still necessary to keep the leakage power under control as CMOS technology scales down.

## **1.2 Problem Statement**

The problem to be solved in this work is: Given a CMOS circuit, find a technique to reduce the active leakage power in the circuit significantly without introducing much performance cost. The implementation complexity of the technique should be feasible so that it can be practical for large circuits.

#### **1.3 Summary of Original Contributions**

In this work, we present a novel active leakage power reduction technique using dynamic power cutoff, called the *dynamic power cutoff technique* (DPCT). We propose a new *minimal switching window* (MSW) for CMOS gates to identify when the gate is active, which is equal to the worst-case delay of the gate. We propose a heuristic partitioning algorithm based on dynamic program to partition the circuit into groups based on the MSW of each gate so that the cost of adding extra power cutoff controls will be minimized without sacrificing much of the leakage power savings. We propose a six-step approach to implement DPCT. We also present the procedures to do power grid analysis and process variation analysis on DPCT.

Experimental results on *ISCAS* '85 benchmark circuits modeled using 70*nm* Berkeley Predictive Models [17] show up to 90% in active leakage power saving, 99% in standby leakage saving, up to 54% in dynamic power saving, and up to 72% in total power saving. DPCT can also reduce the maximal voltage drop on the power grid by more than 30% on average. With process variations, the average total power and active leakage power savings will be reduced by 12.7% and 14.8%, respectively. In spite of that, DPCT still gives excellent power savings, which are 73.6% of active leakage power and 34.7% of total power with process variations. We also implemented the layouts of a 16-bit multiplier and c432 using DPCT. The 16-bit multiplier with DPCT saves 54.7% of the total power, 85.7% of the active leakage power (including short-circuit power) and 38.1% of the dynamic power with 7.7% delay overhead and 8.6% area overhead. The c432 circuit with DPCT saves 22.5% of the total power, 73.6% of the active leakage power (including short-circuit power) and 2.3% of the dynamic power with 9% delay overhead and 13.7% area overhead. The experimental results on the layout designs confirmed the effectiveness of DPCT in physical level design.

# 1.4 Organization of the Thesis

In Chapter 2, we introduce some background on the power dissipation of CMOS circuits

and present a survey on prior leakage reduction techniques. In Chapter 3, we introduce the background and prior work on the power grid analysis and the process variation analysis. The detail of our novel DPCT technique is introduced in Chapter 4. The procedures to analyze the power grid and process variations for DPCT are presented in Chapter 5. Chapter 6 presents the experimental results on the power savings, power grid analysis and process variation analysis for DPCT. Chapter 7 presents a layout implementation of 16-bit multiplier with DPCT. Chapter 8 gives the future work and concludes.

# **Chapter 2**

# **Prior Work: Techniques for Leakage Power Reduction**

# 2.1 Introduction

In this section, we first review the basic mechanisms of power dissipation in CMOS circuits, where we focus on the mechanisms of leakage power. Then we review some existing leakage reduction techniques.

#### **2.2** Power Dissipation in CMOS Circuits

There are three sources of power dissipation in CMOS digital circuits: *dynamic* power, *short-circuit* power, and *leakage* power. Formerly, the dynamic power was dominant and the other two parts were negligible. But leakage power is becoming more and more significant as the CMOS technology goes into the deep submicron scale. Now, all three are important and leakage power is beginning to dominate.

# 2.2.1 Dynamic Power

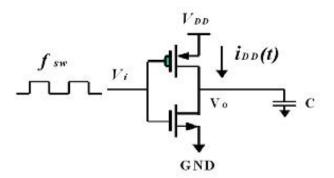

Figure 2.1: A CMOS Inverter

Dynamic power is the power required to charge and discharge the load capacitances when

transistors switch. Suppose that we have a CMOS inverter with load capacitance *C*, which is shown in Figure 2.1. One cycle involves a rising and a falling transition at the gate output. Charge  $Q = CV_{DD}$  is required on a low-to-high transition at the gate output and the charge is dumped to *GND* during the high-to-low transition at the gate output. This charging and discharging process repeats  $T f_{sw}$  times over an interval of *T*, where  $f_{sw}$  is the frequency of the input signal. So, the dynamic power can be calculated by the following formula:

$$P_{dynamic} = \frac{1}{T} \int_{0}^{T} i_{DD}(t) V_{DD} dt = \frac{V_{DD}}{T} \int_{0}^{T} i_{DD}(t) dt = \frac{V_{DD}}{T} (T f_{sw} C V_{DD}) = C V_{DD}^{2} f_{sw}$$

(2.1)

The dynamic power can also be formalized as:  $P_{dynamic} = \alpha C_L V_{DD}^2 f$ , where *f* is the clock frequency and  $\alpha$  is the node transition activity factor.

### 2.2.2 Short-Circuit Power

When transistors switch, both nMOS and pMOS networks may be momentarily on at once. This leads to a blip of short circuit current. The short circuit power is given by:

$$P_{short-circuit} = I_{mean} V_{DD} \tag{2.2}$$

where  $I_{mean}$  is average short-circuit current. For a symmetric inverter shown in Figure 2.1,

$$I_{mean} = \frac{\beta}{12} (V_{DD} - 2V_t)^3 \frac{t_{rf}}{t_p}$$

(2.3)

where  $V_{DD}$  is the power supply voltage,  $V_t = V_{tn} = -V_{tp}$  is the threshold of the MOSFETs,  $\beta = \beta_n = \beta_p$  is the  $\beta$  of the MOSFETs,  $t_r = t_f = t_{rf}$  are the rising and falling times of the input pulse, and  $t_p$  is the period of the input pulse [81].

# 2.2.3 Leakage Power

Leakage power, also called static power, is due to the off-state current of a transistor when it is off. Suppose that there are *N* transistors in a circuit, and  $I_{off_i}$  is the off-state current of the *i*th transistor. Then, the total leakage power of the circuit can be expressed in the following formula:

$$P_{leakage} = V_{DD} \sum_{i=1}^{N} I_{off_i}$$

(2.4)

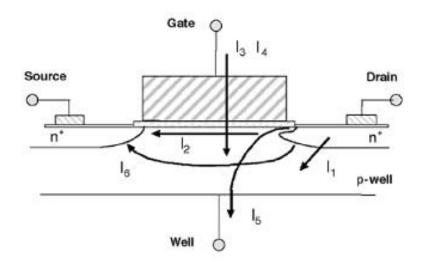

There are mainly six short-channel leakage mechanisms as illustrated in Figure 2.2 [34].  $I_1$  is the reverse-bias *pn* junction leakage;  $I_2$  is the subthreshold leakage;  $I_3$  is the oxide tunneling

current;  $I_4$  is the gate current due to hot-carrier injection;  $I_5$  is the *gate-induced drain leakage* (GIDL); and  $I_6$  is the channel punchthrough current. Currents  $I_2$ ,  $I_5$ , and  $I_6$  are off-state leakage mechanisms, while  $I_1$  and  $I_3$  occur in both ON and OFF states.  $I_4$  can occur in the off state, but more typically occurs when the transistor bias states are in transition.

Figure 2.2: Leakage Current Mechanisms of Deep-Submicron Transistors [34]

# 2.2.3.1 pn Junction Reversed-Bias Current

Drain and source to well junctions are typically reverse biased, causing *pn* junction leakage current. The *pn* junction reverse-bias leakage is a function of junction area and doping concentration [61]. If both *n* and *p* regions are heavily doped (this is the case for advanced MOSFETs using heavily doped shallow junctions and halo doping for better short channel effects (SCEs)), *band-to-band tunneling* (BTBT) dominates the *pn* junction leakage. The tunneling current density is given by [76]:

$$J_{b2b} = A \frac{EV_{app}}{\sqrt{E_g}} exp(-B \frac{E_g^{\frac{1}{2}}}{E}), A = \frac{\sqrt{2m^*}q^3}{4\pi^3 h^2}, and B = \frac{\sqrt{2m^*}}{3qh}$$

(2.5)

where  $m^*$  is effective mass of the electron;  $E_g$  is the energy band gap;  $V_{app}$  is the applied reverse bias; *E* is the electric field at the junction; *q* is the electronic charge; and *h* is Planck's constant.

#### 2.2.3.2 Subthreshold Leakage Current

Subthreshold or weak inversion conduction current between source and drain in a MOS transistor occurs when the gate voltage is below  $V_{th}$ . It typically dominates modern device off-state leakage. The weak inversion current can be expressed based on the following [89]:

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_{th}}{nv_T}} \left(1 - e^{\frac{-V_{ds}}{v_T}}\right)$$

(2.6)

$$I_{ds0} = \beta v_T^2 e^{1.8}$$

(2.7)

where  $V_{th}$  is the threshold voltage;  $V_{gs}$  is gate-source voltage;  $V_{ds}$  is drain-source voltage;  $v_T$  is the thermal voltage;  $I_{ds0}$  is the current at the threshold and is dependent on process and device geometry; the  $e^{1.8}$  term was found empirically; and *n* is a process-dependent term affected by the depletion region characteristics and is typically in the range of 1.4-1.5 for CMOS processes.

The inverse of the slope of the  $\log_{10} I_{ds}$  versus  $V_{gs}$  characteristic is called the *subthreshold swing* ( $S_t$ ). Subthreshold slope indicates how effectively the transistor can be turned off (rate of decrease of  $I_{off}$ ) when  $V_{gs}$  is decreased below  $V_{th}$ .  $S_t$  is given by Equation 2.8, where  $C_{dm}$  is the capacitance of the depletion layer, and  $C_{ox}$  is the gate oxide capacitance [76].

$$S_t = 2.3 \frac{kT}{q} (1 + \frac{C_{dm}}{C_{ox}})$$

(2.8)

Many factors affect the subthreshold current, such as temperature, body effect, DIBL (*drain induced barrier lowering*), the narrow-width effect, the effect of channel length, and  $V_h$  rolloff.

#### **Temperature.**

Subthreshold leakage increases as temperature is raised due to the change of the two parameters: (1)  $S_t$  linearly increases with temperature; and (2) the threshold voltage  $V_{th}$  decreases.

# **Body Effect.**

Body effect is due to the change of threshold with the substrate bias voltage, which is given by the equation:

$$V_{th} = V_{fb} + \Psi_B + \frac{\sqrt{2\varepsilon_{si}qN_A(2\Psi_B + V_{bs})}}{C_{ox}}$$

(2.9)

where  $V_{bs}$  is the substrate bias voltage,  $V_{fb}$  is the flat-band voltage,  $N_A$  is the doping density in the substrate,  $C_{ox}$  is the gate oxide capacitance,  $\varepsilon_{si}$  is permittivity of silicon, and  $\Psi_B$  is the difference between the Fermi potential and the intrinsic potential in the substrate. A change of body bias can change the threshold voltage, which will in turn change the leakage current.

## DIBL.

In a short-channel device the source and drain depletion widths in the vertical direction and the source drain potential have a strong effect on the band bending over a significant portion of the device. Therefore, the threshold voltage, and consequently the subthreshold current of short-channel devices, vary with the drain bias. This effect is referred to as DIBL. DIBL does not change the subthreshold slope  $S_i$ , but does lower  $V_{th}$ , which in turn will increase the subthreshold current.

### Narrow-Width Effect.

The decrease in gate width modulates the threshold voltage of a transistor, and thereby modulates the subthreshold leakage.

#### Effect of Channel Length and V<sub>th</sub> Rolloff.

Threshold voltage of a MOSFET decreases as the channel length is reduced. This reduction of the threshold voltage with reduction of channel length is known as  $V_{h}$  rolloff. The principal reason behind this effect is the presence of 2-D field patterns in short-channel devices instead of one-dimensional (1-D) field patterns in long-channel devices.

#### 2.2.3.3 Tunneling into and through Gate Oxide

Reduction of gate oxide thickness results in an increase in the field across the oxide. The high electric field coupled with low oxide thickness results in tunneling of electrons from substrate to gate and also from gate to substrate through the gate oxide, resulting in the gate oxide tunneling current. This is becoming a significant part of leakage power consumption. The mechanism of tunneling between substrate and gate polysilicon can be primarily divided into two parts, namely: (1) *Fowler-Nordheim* (FN) tunneling; and (2) direct tunneling. In the case of FN tunneling, electrons tunnel through a triangular potential barrier, whereas in the case of direct tunneling, electrons tunnel through a trapezoidal potential barrier. The current density in the FN tunneling is given by [76]:

$$J_{FN} = \frac{q^3 E_{ox}^2}{16\pi^2 h \phi_{ox}} \exp\left(-\frac{4\sqrt{2m^*}\phi_{ox}^{3/2}}{3hq E_{ox}}\right)$$

(2.10)

where  $E_{ox}$  is the field across the oxide,  $\phi_{ox}$  is the barrier height for electrons in the conduction band, and  $m^*$  is the effective mass of an electron in the conduction band of silicon. The equation governing the current density of the direct tunneling is given by [70]:

$$I_{DR} = AE_{ox}^{2} \exp\left\{-\frac{B[1 - (1 - \frac{V_{ox}}{\phi_{ox}})^{3/2}]}{E_{ox}}\right\}$$

(2.11)

where  $V_{ox}$  is the voltage across the oxide,  $A = q^3/(16\pi^2 h \phi_{ox})$ , and  $B = (4\sqrt{2m^*}\phi_{ox}^{3/2})/(3hq)$ .

# 2.2.3.4 Injection of Hot Carriers from Substrate to Gate Oxide

In a short-channel transistor, due to a high electric field near the *Si-SiO* interface, electrons or holes can gain sufficient energy from the electric field to cross the interface potential barrier and enter into the oxide layer. This effect is known as hot-carrier injection.

#### 2.2.3.5 Gate-Induced Drain Leakage (GIDL)

GIDL is due to a high field effect in the drain junction of an MOS transistor. A thinner oxide thickness and higher  $V_{DD}$  (higher potential between gate and drain) enhance the electric field and therefore increase GIDL. GIDL is worse for moderate drain doping (in between the extremes previously mentioned), where both the electric field and depletion width (tunneling volume) are considerable. Very high and abrupt drain doping is preferred for minimizing GIDL, as it provides lower series resistance required for high transistor drive currents.

#### 2.2.3.6 Punchthrough

In short-channel devices, due to the proximity of the drain and the source, the depletion regions at the drain-substrate and source-substrate junctions extend into the channel. An increase in the reverse bias across the junctions also pushes the junctions nearer to each other. When the combination of channel length and reverse bias leads to the merging of the depletion regions, punchthrough is said to have occurred.

The device parameter commonly used to characterize the punchthrough is the punchthrough voltage  $V_{PT}$ , which estimates the value of  $V_{DS}$  for which the punchthrough occurs (i.e., the subthreshold current reaches a particular value) at  $V_{GS} = 0$ . It is roughly estimated as the value of the  $V_{DS}$  for which the sum of the widths of the drain and source depletion regions is equal to

the effective channel length [69]:

$$V_{PT} \propto N_B (L - W_i)^3 \tag{2.12}$$

where  $N_B$  is the doping concentration in the bulk; *L* is the channel length; and  $W_j$  is the junction width.

#### 2.3 Technology Trends of Power Dissipation in CMOS Circuits

CMOS technology has to keep scaling down to improve the circuit performance and reduce the cost. As technology scales downward, the transistor density and circuit frequency all increase dramatically. So, the supply voltage  $V_{DD}$  must also scale down to reduce dynamic power and maintain reliability. However, this requires the scaling of  $V_{th}$  to maintain a reasonable gate overdrive. The scaling of transistor size,  $V_{DD}$ , and  $V_{th}$  all have a big effect on both the dynamic and leakage power of CMOS circuits. Not only their absolute values, but also their relative magnitudes change dramatically, which has a big impact on CMOS circuits design.

# 2.3.1 Dynamic Power vs. Leakage Power

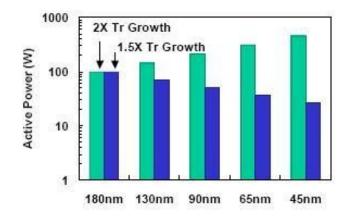

As technology scales below 90*nm*, transistor density will continue to double, allowing higher integration. Transistor delay will also continue to improve, at least modestly to 30% reduction per generation. Supply voltage ( $V_{DD}$ ) will continue to scale modestly by 15%, not by the historic 30% per generation, due to the difficulties in scaling threshold voltage  $V_{th}$  and to meet transistor performance goals. Figure 2.3 shows growth in active power of a microprocessor assuming historical 2× growth in number of transistors and with hypothetical 1.5× growth [35].

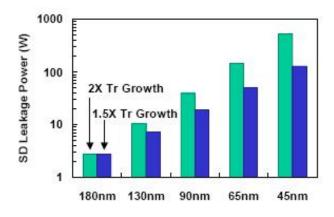

Subthreshold leakage increase exponentially with the reduction of  $V_{th}$ . Assume that  $V_{th}$  decreases by 15% per generation, the subthreshold leakage current  $I_{off}$  will increase by 5 times each generation. Figure 2.4 projects the *source-drain* (SD) subthreshold leakage power of the microprocessor with  $2 \times$  and  $1.5 \times$  transistor growth. Except for the skyrocketing subthreshold leakage, gate leakage becomes larger than  $100A/cm^2$  as the physical gate oxide thickness approaches sub-10Å regime. Junction leakage is also increasing dramatically as channel dopping concentrations approach  $5 \times 10^{18} cm^{-3}$  in the channel [71]. Overall, leakage power increases exponentially with technology scaling.

Since dynamic power remains constant and leakage power increases exponentially with technology scaling, leakage power is becoming dominant in sub-90*nm* CMOS technologies.

Figure 2.3: Dynamic Power Trend [35]

This poses serious challenges for deep submicron CMOS VLSI circuit design. Leakage reduction techniques have to be applied to put the leakage power under control.

Figure 2.4: Leakage Power Trend [35]

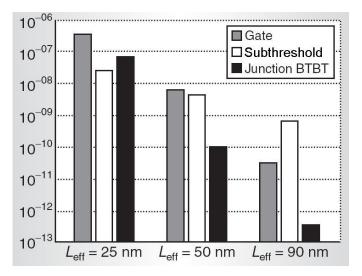

## 2.3.2 Relative Magnitudes of Different Leakage Power Components

The three major types of leakage mechanisms are: subthreshold leakage, gate leakage, and *pn* junction reverse-bias band-to-band tunneling (BTBT) leakage [7]. Although they all increase rapidly with technology scaling, their relative magnitudes will change dramatically. Figure

2.5 shows the contribution of different leakage components in *n*MOS devices at different technology generations [7]. We see that subthreshold leakage is dominant in 90*nm* technology. However, gate leakage becomes equally important in 50*nm* technology and BTBT leakage is also very significant. As the technology scales down to 25nm, all three components become nearly equally important. So, each leakage reduction technique needs reevaluation in scaled technologies as the relative magnitudes of different leakage components change.

Figure 2.5: Contribution of Different Leakage Components in *n*MOS Devices at Different Technology Generations [7]

#### 2.4 Leakage Power Reduction Techniques

The reduction in leakage current has to be achieved using both process and circuit-level techniques. At the process level, leakage reduction can be achieved by controlling the dimensions (length, oxide thickness, junction depth, etc.) and doping profiles in transistors. At the circuit level, threshold voltage and leakage current of transistors can be effectively controlled by controlling the voltages of different device terminals [drain, source, gate, and body (substrate)].

# 2.4.1 Device-Level Leakage Reduction Techniques

Well engineering is always used to improve short-channel characteristics. By changing the doping profile in the channel region, the distribution of the electric field and potential contours

can be changed. The goal is to optimize the channel profiles to minimize the OFF-state leakage while maximizing the linear and saturated drive currents. Supersteep retrograde wells and halo implants have been used as a means to scale the channel length and increase the transistor drive current without causing an increase in the OFF-state leakage current [32, 77, 82, 91].

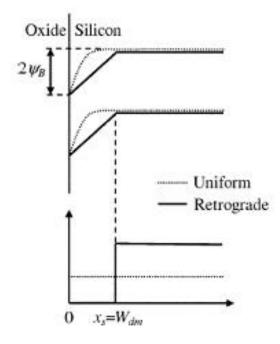

# 2.4.1.1 Retrograde Doping

Retrograde channel doping is a vertically nonuniform, low-high channel doping. It is used to improve the *short channel effects* (SCEs) and to increase surface channel mobility by creating a low surface channel concentration followed by a highly doped subsurface region. The low surface concentration increases surface channel mobility by minimizing channel impurity scattering while the highly doped subsurface region acts as a barrier against punchthrough.

Figure 2.6 shows a schematic band-bending diagram at the threshold condition of an extreme retrograde profile with an undoped surface layer of thickness. For the same gate depletion width, the surface electric field and the total depletion charge of an extreme retrograde channel is one-half that of a uniformly doped channel. This reduces the threshold voltage and improves mobility.

Figure 2.6: Band Diagrams (Shown on Top) at the Threshold Condition for a Uniformly Doped and an Extreme Retrograde-Doped Channel (Doping Profiles Shown at Bottom) [75]

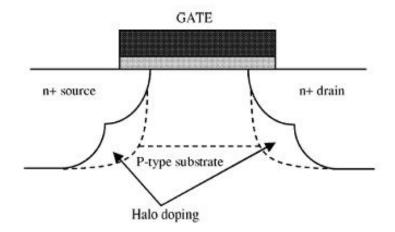

#### 2.4.1.2 Halo Doping

Halo doping or nonuniform channel profile in a lateral direction was introduced below the  $0.25\mu$ m technology node to provide another way to control the dependence of threshold voltage on channel length. For *n*-channel MOSFETs, more highly *p*-type doped regions are introduced near the two ends of the channel as shown in Figure 2.7.

Under the edges of the gate, in the vicinity of what will eventually become the end of the channel, point defects are injected during sidewall oxidation. These point defects gather doping impurities from the substrate, thereby increasing the doping concentration near the source and drain ends of the channel [28]. A more highly doped *p*-type substrate near the edges of the channel reduces the charge-sharing effects from the source and drain fields, thus reducing the width of the depletion region in the drain-substrate and source-substrate regions. Reduction of charge-sharing effects reduces the threshold voltage degradation due to channel length reduction. Thus, threshold voltage dependence on channel length becomes more flat and the off-current becomes less sensitive to channel length variation. The reduction in drain and source junction depletion region widths also reduces the barrier lowering in the channel, thus reducing DIBL. Since the channel edges are more heavily doped and junction depletion widths are smaller, the distance between source and drain depletion regions is larger. This reduces the punchthrough possibility [75].

Figure 2.7: Halo or Nonuniform Channel Doping

### 2.4.2 Circuit-Level Leakage Reduction Techniques

In this section, we will review six major circuit design techniques for leakage reduction in digital circuits: transistor stacking, input vector control, multiple  $V_{h}$ , supply voltage scaling (multiple and dynamic  $V_{DD}$ ), power cut-off, and dynamic power-gating using the Shannon Expansion.

#### 2.4.2.1 Transistor Stacking

Subthershold leakage current flowing through a stack of series-connected transistors reduces when more than one transistor in the stack is turned off. This effect is known as the stacking effect, which is shown in Figure 2.8. The technique of inserting an extra series connected transistor in the pulldown path of a gate and turning it off in the standby-mode of operation is known as forced stacking [33]. The extra transistor is turned on during the regular mode of operation and turned off during the idle mode of operation. When the extra transistor is turned off, the intermediate source voltage increases, which results in a decrease in the subthreshold current through the top transistor. Hence, the total subthreshold leakage through a two-transistor stack is reduced. Forced stacking only works for standby leakage power reduction.

Figure 2.8: Stacking Effect in Two-Input NAND Gate

Another way of using the stacking effect for leakage reduction is to replace a single transistor with two transistors of the same size. This is equivalent to replacing a low threshold transistor with a high threshold transistor in the dual-threshold transistor technique. Static timing analysis is needed to identify those gates on non-critical paths for possible insertion of stacking transistors. Similar algorithms as high threshold transistor insertion in the dual-threshold transistor technique can be used. Please refer to Section 2.4.2.3 for the detail introduction of the dual-threshold transistor technique.

### 2.4.2.2 Leakage Reduction by Input Vector Control

Due to the stacking effect, the subthreshold leakage through a logic gate depends on the applied input vector. This makes the total leakage current of a circuit dependent on the states of the primary inputs [25]. It has been shown that the leakage current ratio between different input combinations can be as high as 10. The goal can then be expressed as finding the input pattern that maximizes the number of disabled (off) transistors in all stacks across the circuit [90].

One possible way is to perform an exhaustive circuit-level simulation for all input patterns to find the pattern with the minimum leakage current. However, this approach is not practical for large circuits. Z. Chen *et al.* proposed a genetic algorithm [21] to locate the vector that results in the near minimal leakage current. J. Halter and F. Najm [29] used probabilistic methods to reduce the number of simulations necessary to find a solution with a desired accuracy. SAT-based formulation [3, 4, 8] were also proposed for finding the minimum leakage vector at the circuit inputs.

#### 2.4.2.3 Leakage Reduction by Multiple Threshold Voltage Designs

One way of decreasing the leakage current is to increase the threshold voltages of transistors. Multiple-threshold CMOS technologies, which provide both high- and low-threshold transistors in a single chip, can be used to deal with the leakage problem. The high-threshold transistors can suppress the subthreshold leakage current, while the low-threshold transistors are used to achieve high performance. Several multiple-threshold circuit design techniques have been developed recently, including multi-threshold CMOS, dual-threshold CMOS, variable threshold CMOS, and dynamic threshold CMOS.

### Multi-Threshold Voltage CMOS.

*Multi-threshold voltage CMOS* (MTCMOS) reduces the leakage by inserting high-threshold devices in series with low-threshold circuitry [54]. Figure 2.9 shows the schematic of an MTC-MOS circuit. In the active mode, the sleep control transistors (MP and MN) are turned on.

Since their on-resistances are small, the virtual supply voltages (*VDDV* and *VSSV*) almost function as real power lines. In the standby mode, MN and MP are turned off, and the leakage current is low.

Figure 2.9: (a) Original MTCMOS (b) *p*MOS Insertion MTCMOS (c) *n*MOS Insertion MTC-MOS [54]

In fact, only one type of high transistor is enough for leakage control. Figures 2.9 (b) and (c) show the *p*MOS insertion and *n*MOS insertion schemes, respectively. The *n*MOS insertion scheme is preferable, since the *n*MOS on-resistance is smaller at the same width; therefore, it can be sized smaller than the corresponding *p*MOS. This technique is only effective for standby leakage power reduction.

## **Dual-Threshold CMOS.**

Another approach of MTCMOS is to use high-threshold voltage devices on noncritical paths to reduce the leakage power while using low-threshold devices on critical paths so that the circuit performance is maintained. This technique has been called dual-threshold CMOS [20]. It is an integer linear program to choose an optimal assignment of dual- $V_{th}$  for all of the transistors or gates in the circuit. Various heuristic algorithms are proposed to solve this problem for big circuits [51, 74, 84, 86, 87]. Dual-threshold CMOS is a very effective approach for leakage reduction in both active mode and standby mode. More than 80% of leakage power savings have been reported. Comparied with other leakage reduction techniques, it requires very little

modification of the circuit design. It can also be combined with transistor sizing and multiple  $V_{DD}$  to get more leakage power savings [31, 36, 39, 56, 59, 60, 72, 72, 88]. Y. Lu *et al.* combine dual- $V_{th}$  assignment with path balancing using integer linear programing to reduce both leakage and dynamic glitch power simultaneously [47–50]. Thus, dual-threshold CMOS is widely used in modern CMOS fabrication lines.

### Variable Threshold CMOS.

*Variable threshold CMOS* (VTMOS) is a technique, which uses the body bias voltage to change the threshold of CMOS transistors [43]. It has been reported that reverse body biasing lowers integrated circuit leakage by three orders of magnitude in a  $0.35\mu$ m technology [38]. However, it was also shown that the effectiveness of reverse body bias in lowering leakage decreases as technology scales. This technology also requires routing the body grid, which will add to the overall chip area.

#### **Dynamic Threshold CMOS.**

In *dynamic threshold CMOS* (DTMOS), the threshold voltage is altered dynamically to suit the operating state of the circuit. It can be achieved by tying the gate and body together [9]. DTMOS can be developed in bulk technologies by using triple wells. Doping engineering is needed to reduce the parasitic components [85]. The supply voltage of DTMOS is limited by the diode built-in potential in bulk silicon technology. The *pn* diode between source and body should be reverse biased. Hence, this technique is only suitable for ultra-low voltage (0.6V and below) circuits in bulk CMOS. Another way for dynamic threshold design is to control the body bias voltage dynamically through a bias-control circuit depending on the workload of the system. When the workload becomes less, the bias control circuit will change the body bias to increase the threshold to reduce the power [40].

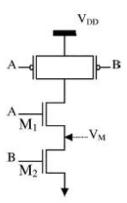

### 2.4.2.4 Leakage Reduction by Power Cut-Off

Instead of using low  $V_{DD}$  for active mode and high  $V_{DD}$  for standby mode, the power supply can be cut-off during the standby state and resumed during the active mode. This is called power cut-off technology. Two different power cut-off CMOS technologies have been proposed: *super cut-off CMOS* (SCCMOS) [37] and *zigzag super cut-off CMOS* (ZSCCMOS) [53].

Figure 2.10: Concept of SCCMOS

The SCCMOS scheme was proposed and demonstrated to achieve high speed and low standby current with sub-1V supply voltages. In Figure 2.10, the low- $V_{th}$  cut-off *p*MOS, M1, whose  $V_{th}$  is 0.1-0.2V, is inserted in series to the logic circuits consisting of low- $V_{th}$  MOSFETs. The gate voltage of M1,  $V_G$ , is grounded in an active mode to turn M1 on. When the logic circuits enter standby operation,  $V_G$  is overdriven to  $V_{DD}$ +0.4V to completely cut off the leakage current.

A problem associated with this scheme is that data can get lost during the long sleep period due to the leakage current. SCCMOS also suffers from a long wake-up time and a high current peak at the sleep-to-active transition. This is due to the virtual  $V_{DD}$  node being discharged (charged) during the sleep period and being charged (discharged) when returning to active mode. A *zigzag super cut-off CMOS* (ZSCCMOS) method was then proposed to improve the operating speed by eliminating the series-connected switches while achieving the relaxation of the high-voltage stress at the cut-off switch [53].

Tschanz *et al.* incorporated the power cut-off technology with the clock-gating scheme for leakage power reduction in a microprocessor [78]. The gated-clock signal is used to synchronize the power cut-off controls of the respective circuit blocks, so that not only dynamic power but also leakage power can be reduced when the circuit block is in standby mode.

### 2.4.2.5 Dynamic Power Gating Using the Shannon Expansion

Bhunia *et al.* proposed an active leakage reduction technique using supply gating [12]. They use the Shannon expansion to identify the idle part of the circuit and dynamically apply supply gating to those idle parts so that active leakage power is saved. Based on the Shannon expansion, each function  $f(x_1, x_2, ..., x_n)$  can be expanded into two parts based on variable  $x_i$ :

$$f(x_1, x_2, ..., x_n) = x_i CF_1 + x'_i CF_2$$

$$CF_1 = f(x_1, x_2, ..., x_i = 1, ..., x_n);$$

$$CF_2 = f(x_1, x_2, ..., x_i = 0, ..., x_n);$$

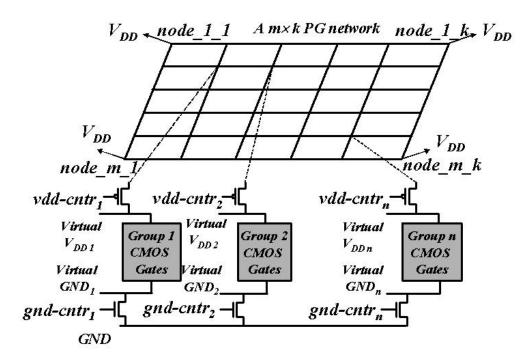

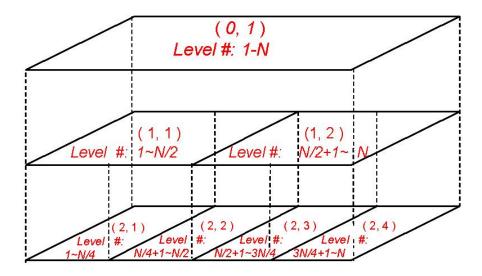

(2.13)