High Frequency Techniques for Advanced MOS Device Characterization

By

# Yun Wang

A Dissertation submitted to the

Graduate School- New Brunswick

Rutgers, The State University of New Jersey

In partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Professor Kin P. Cheung, Ph. D.

And approved by

New Brunswick, New Jersey

January, 2008

### ABSTRACT OF THE DISSERATATION

# High Frequency Techniques for Advanced MOS Device Characterization

by YUN WANG

Dissertation Director Professor Kin P. Cheung

Rapid advances in the semiconductor industry have led to the proliferation of electric devices and information technology (IT). Integrated circuits(IC) based upon silicon MOSFET's have been used in virtually every electronic device produced today. The competitiveness of this huge market urges an increased device performance with lower cost. Over the past three decades, it is fulfilled by reducing transistor gate lengths and oxide thickness with each new generation of manufacturing technology. The leading edge CMOS technology is currently at the 45nm node with physical gate length at 18 nm and an equivalent gate oxide thickness (EOT) of 0.9 nm. However, as

the device is miniaturized into the nanometer-scale regime nowadays, some challenges abound. Some challenges are new, some are just getting tougher and most of them will continue to become even more difficult to deal with for future generations. It is the world-wide effort to meet these challenges for sustaining the rapid growth of the industry. In this thesis, we will address a few of these challenges and offer some new approaches to get around them. Specifically, we introduce a new measurement technique to solve the precision problem in C-V measurement based on Time domain Reflectrometry(TDR). We also use the combination of experiment and theory to resolve the defect depth-profiling ambiguity associated with charge pumping measurement. Moreover, we find a new mode in transistor degradation that will become much more serious as the transistor size shrinks further. All these results represent a major and important advance which is also timely to the IC industry.

## Acknowledgements

I am grateful for this opportunity to acknowledge the people who have made this thesis proposal possible. First and foremost, I would like to thank my advisor Professor Kin.P. Cheung, who has introduced me to the world of research. It is an intellectually stimulating as well as exciting field. His endless enthusiasm and scientific knowledge continues to be a great inspiration to me. And I deeply appreciate the guidance and support he has given me over the years. In addition, I am very grateful for the collaborative opportunities I have with National Institutes of Standard and Technology (NIST). In particular, I must thank Dr. John Suehle, who is also one of my thesis committee members, for his kindness and help to provide me the facilities to do the NBTI experiment. Also the discussion with him has greatly increased the scope and importance of my thesis. I would also like to thank other committee members, those are, Dr.Lu, Dr.Sheng, for their continued guidance and encouragement. At the end, I am grateful to all my friends from Rutgers University, for being the surrogate family during the many years I stayed here and for their continued moral support. Finally, I am forever indebted to my father Dr. Wenbiao Wang, my mother Yunhong Lv and my wife Qiankun Sun for their understanding, endless patience and encouragement when it was most required.

#### Yun Wang

#### July 01, 2007

# **Table of Contents**

| i |

|---|

| v |

| r |

| K |

|   |

| 1 |

|   |

| 7 |

| 8 |

| 2 |

| 2 |

| 6 |

| 8 |

| 0 |

| 2 |

| 7 |

|   |

| 0 |

| 1 |

| 4 |

| 6 |

| 0 |

| 2 |

| 5 |

| 9 |

| 4 |

|   |

| Chapte | r 4: C-V measurement II                                            | 56  |

|--------|--------------------------------------------------------------------|-----|

| 4.1.   | Source of error in C-V measurement- Series Resistance              | 58  |

| 4.2.   | Source of Error in C-V measurement- Overlap Capacitance            | 60  |

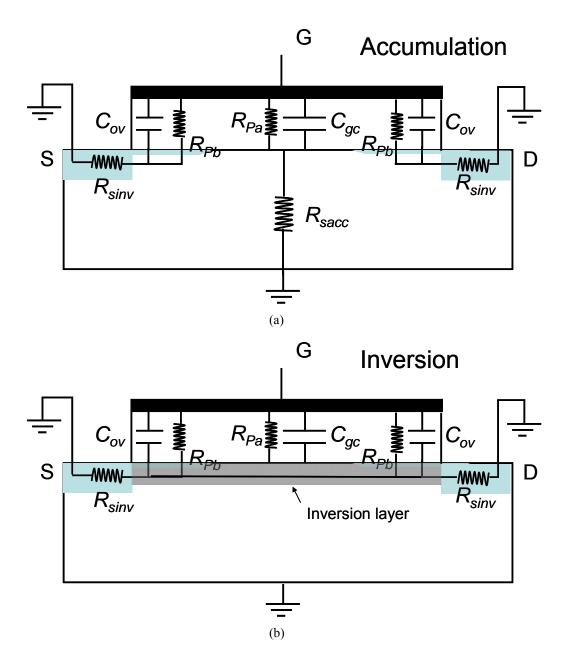

| 4.3.   | Proof of Existence of Overlap Capacitor                            | 63  |

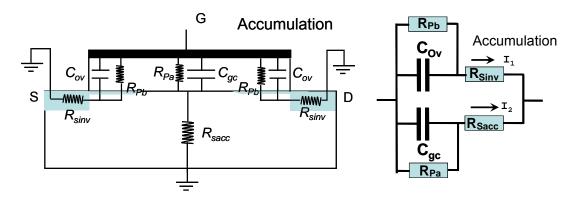

| 4.4.   | Accurate Model of MOSFET Including Overlap Capacitor               |     |

| 4.5.   | Basic Principle of Series Resistance Extraction                    | 72  |

| 4.6.   | Extraction of Series Resistance                                    | 76  |

| 4.7.   | Time Zero Determination and Related Error                          |     |

| 4.8.   | Extraction of Shunt Resistance R <sub>Pa</sub> and R <sub>Pb</sub> | 83  |

| 4.8.   | 1. Basic Principle                                                 |     |

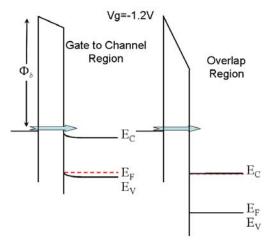

| 4.8.   | 2. Tunneling Current Model                                         | 85  |

| 4.8.   | 3. Determination of Shunt Resistance with Fitting                  | 87  |

| 4.9.   | Better Calibration Structure                                       |     |

| 4.10.  | Overlap Capacitance Extraction                                     | 95  |

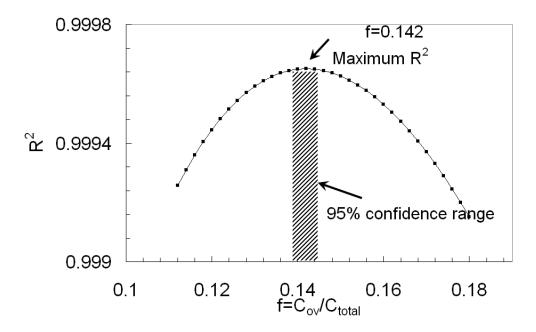

| 4.11.  | Accuracy of Overlap Capacitance Extraction                         |     |

| 4.12.  | Conclusion                                                         | 102 |

| Chapte | r 5: Frequency Dependent Charge-Pumping, How deep it probes        | 104 |

| 5.1.   | Frequency Dependent Charge Pumping                                 | 105 |

| 5.2.   | Controversy in Frequency Dependent Charge Pumping                  |     |

| 5.3.   | Basic Principle of Finding Interface Trap Filling Time             | 110 |

| 5.4.   | High Frequency CP Experiment Setup                                 | 112 |

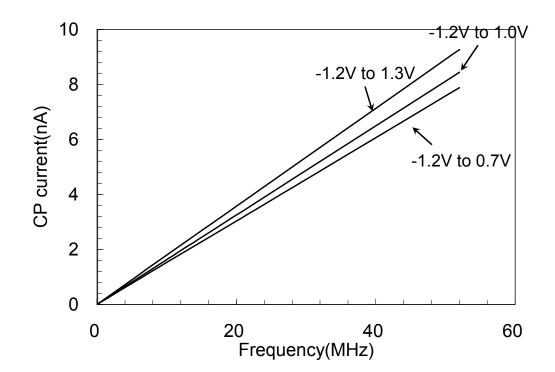

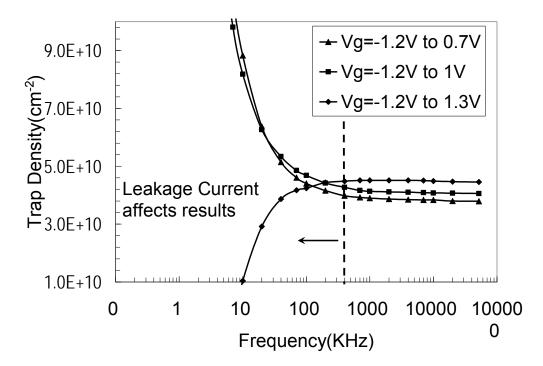

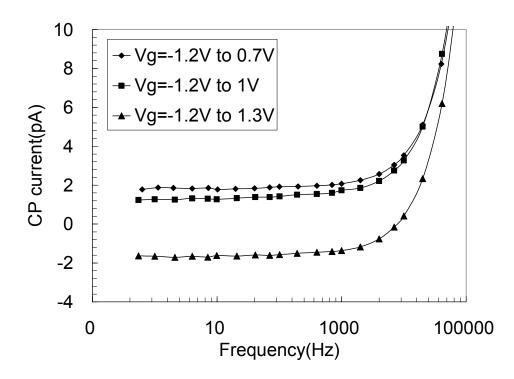

| 5.5.   | Charge Pumping Up to 50MHz                                         | 116 |

| 5.6.   | GHz Charge Pumping Results                                         | 122 |

| 5.7.   | Theoretical Model                                                  | 125 |

| 5.8.   | Examining Existing Theoretical Model                               | 131 |

| 5.9.   | New Cascade Filling Model                                          | 136 |

| 5.10.  | How deep does FDCP probe                                           | 141 |

| 5.11.  | Conclusion and Suggestion on Future Work                           | 144 |

| Chapter 6.1. | 6: Ballistic Phonon Enhanced NBTI<br>Basic Experimental Setup and Details |        |

|--------------|---------------------------------------------------------------------------|--------|

| 6.2.         | Drain Bias Dependent NBTI                                                 |        |

| 6.3.         | Compared to Literature                                                    |        |

| 6.4.         | Rule Out Possible CHC                                                     |        |

| 6.4.         | 1. Evidence I-Poor Fit with Exponential Function                          |        |

| 6.4.         |                                                                           |        |

| 6.4.         | •                                                                         |        |

| 6.5.         | Possible Explanation- Temperature from Localized Hot Spot                 | 161    |

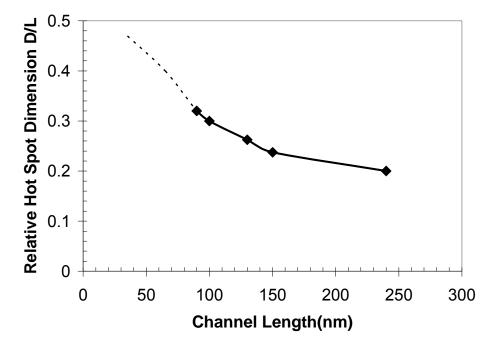

| 6.6.         | Physics of Localized Hot Spot Formation                                   | 166    |

| 6.7.         | Support of "Thermal Effect" - Channel Length Dependent NBTI               | 169    |

| 6.8.         | Support of "Thermal Effect" - Channel Width Dependent NBTI                | 174    |

| 6.9.         | Support of "Thermal Effect" - Drain Bias Frequency Dependent N            | BTI178 |

| 6.10.        | How high is the "temperature"?                                            |        |

| 6.11.        | Conclusion and Suggestion on Future Work                                  | 185    |

| Chapter      | 7: Conclusion and future Work                                             |        |

| Referen      | ice                                                                       | 190    |

| Append       | lix A: Introduction of Time Domain Reflectrometry (TDR)                   | 203    |

| A.1.         | Principle of TDR                                                          | 203    |

| A.2.         | Analytical Expression of TDR Voltage Response                             | 207    |

| A.3.         | TDR Voltage Response of Complex Load                                      | 209    |

| A.4.         | Measurement Factors                                                       |        |

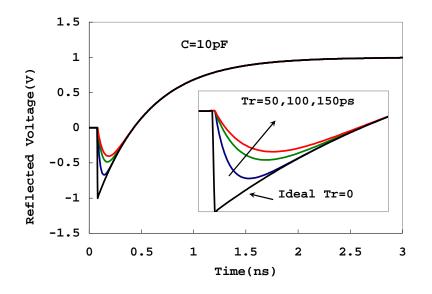

| A.4          | 1. System Rise Time                                                       |        |

| A.4          | 2. Reference Impedance                                                    | 216    |

| A.4          | 3. System Noise                                                           | 216    |

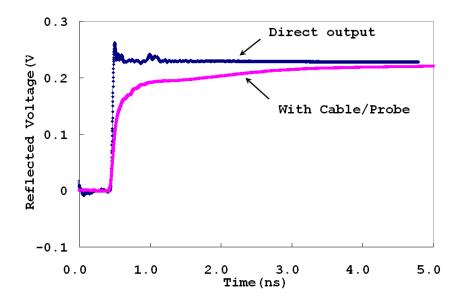

| A.4          | 4. Cable/probe/connector Losses                                           |        |

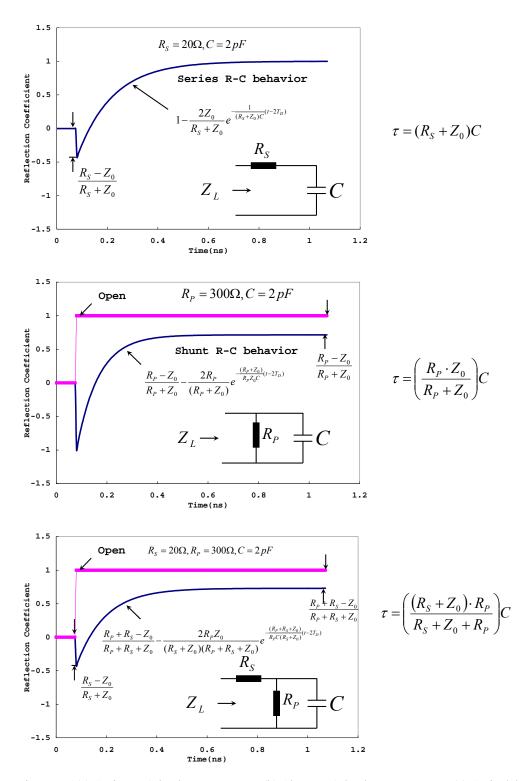

| Append | lix B: Derivation of TDR Capacitance             | 219 |

|--------|--------------------------------------------------|-----|

| B.1.   | Ideal Capacitor Load                             | 220 |

| B.2.   | Series R-C load                                  | 220 |

| B.3.   | Shunt R-C load                                   | 221 |

| B.4.   | Series/Shunt R-C model                           | 222 |

|        |                                                  |     |

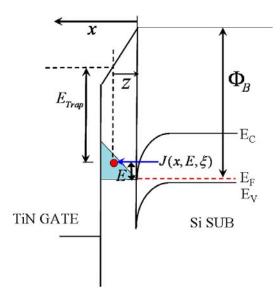

| Append | lix C: Derivation of Tunneling Front Model       | 224 |

| C.1.   | Physical Model                                   | 224 |

| C.2.   | Tunneling Probability for Single Dielectrics     | 225 |

| C.3.   | Tunneling Probability for Dual Layer Dielectrics | 226 |

| C.4.   | Tunneling Current Density                        |     |

| C.5.   | Tunneling Front Model (Field Free Case)          | 230 |

| C.6.   | Tunneling Front Model with Electrical Field      | 232 |

|        |                                                  |     |

| Author's Curriculum Vita |  |

|--------------------------|--|

|--------------------------|--|

### List of Figures and Tables

#### Chapter 2

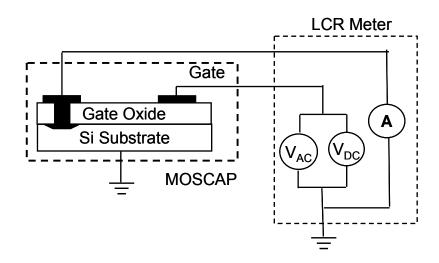

- Figure 2.3 Illustration circuit connection of conventional standard C-V measurement set up using LCR meter. AC signal superimposed on a DC voltage is employed on gate and resulting AC current is measured at substrate electrode. This figure is taken from reference [53]......13

Figure 2.7 Basic experimental setup for charge pumping.Picture is taken from reference 60. ....23

### Chapter 3

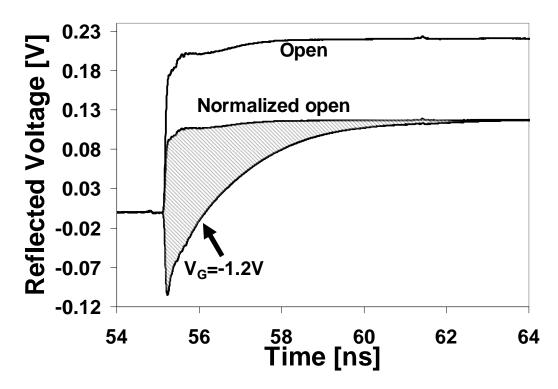

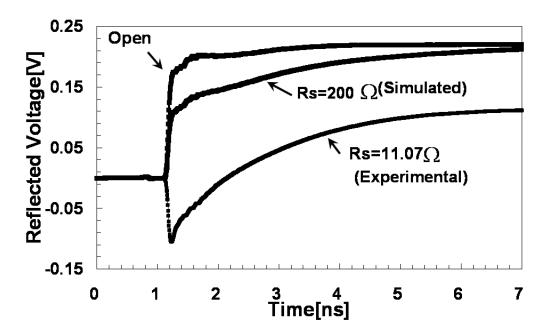

| Figure 3.1 Reflected waveforms from open circuit (reference), MOS capacitor (HfO2 ga               |

|----------------------------------------------------------------------------------------------------|

| dielectrics with EOT 1.2nm) at depletion ( $V_G = 0$ ). The shaded area represents the total store |

| charge in the depletion case. The insert is the equivalent circuit of the capacitor with th        |

| oxide                                                                                              |

|                                                                                                    |

Figure 3.5 Comparison of shunt resistance obtained by new TDR method and traditional current

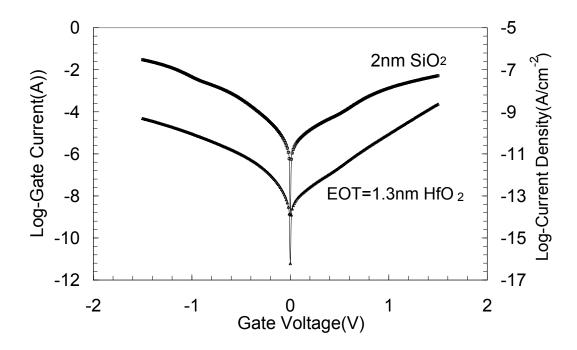

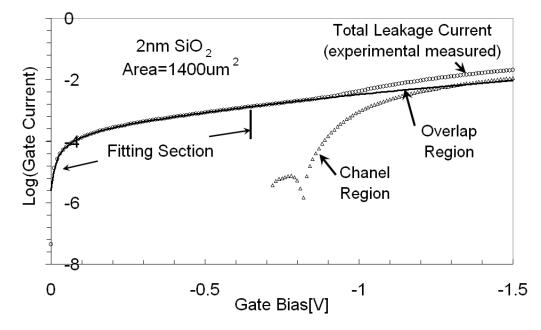

- Figure 3.6 Leakage Current as function of gate voltage is measured by 4156A. With the substrate/source/drain all grounded, gate current is obtained with the sweep of gate voltage. 2nm SiO<sub>2</sub> and EOT 1.2 nm HfO<sub>2</sub> MOS capacitor is measured respectively. After dividing the effective area 1400um<sup>2</sup>, the current density is obtained.......40

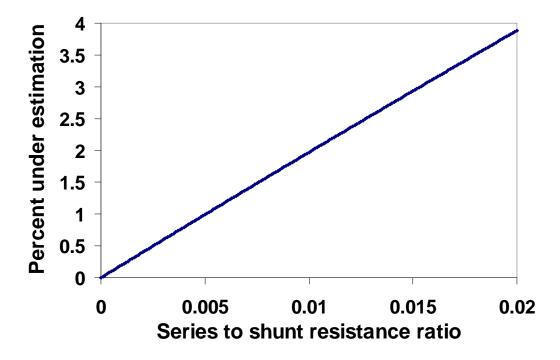

- Figure 3.8 The plot of the percent underestimation of the capacitance when using equation (3.4) to approximate the pre-integral factor M as a function of the  $R_S$  to  $R_P$  ratio......44

Table 3.2 Control Experiment with ceramic capacitor and different series resistance as load......51

Table 3.3 Control experiment with ceramic capacitor with different shunt resistance as load......52

Table 3.4 Control Experiment with ceramic capacitor with different shunt resistance and series resistance load.

52

#### Chapter 4

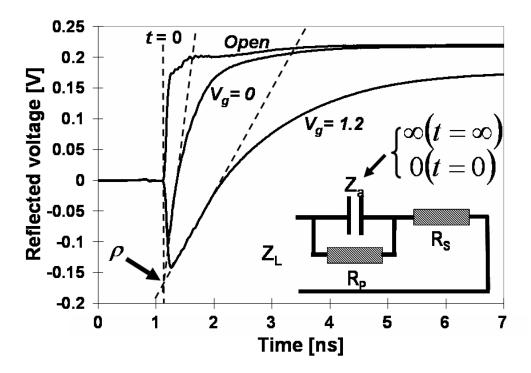

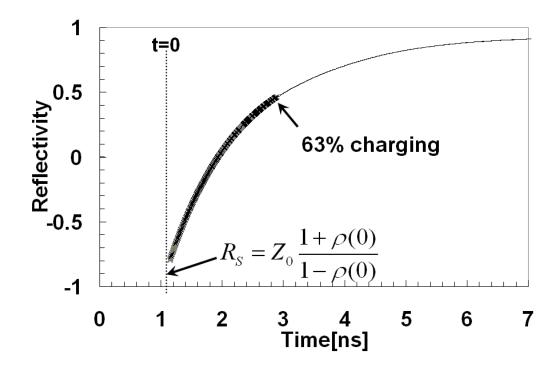

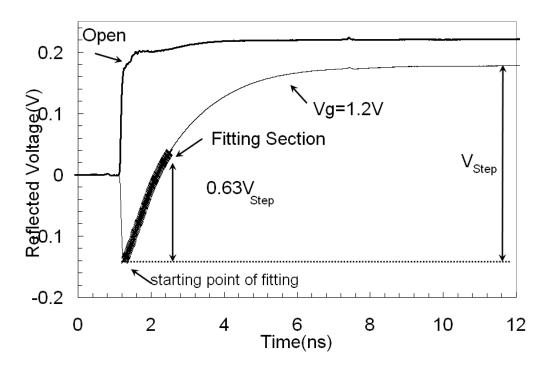

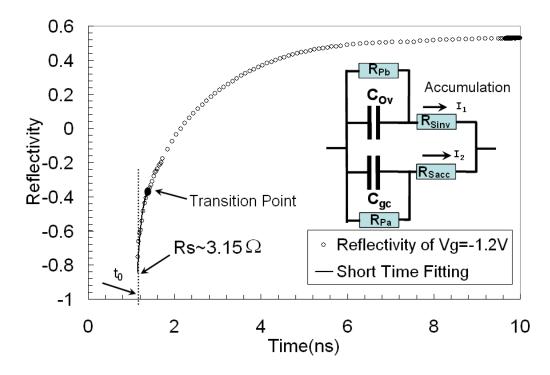

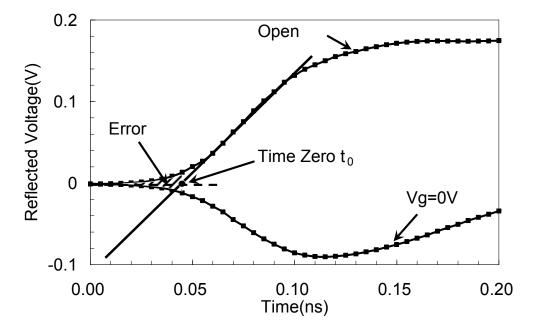

Figure 4.7 Reflectivity curve calculated by dividing the reflected voltage curve (charging curve)

by the open circuit reflection. The X curve is the fitting result extrapolated to time zero... 76

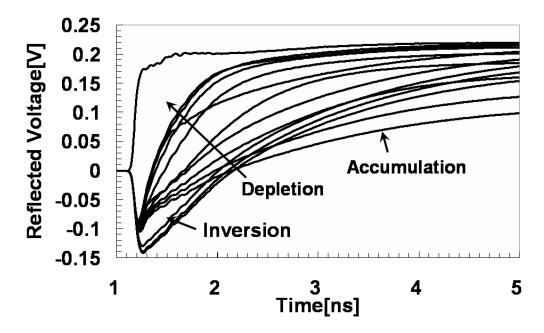

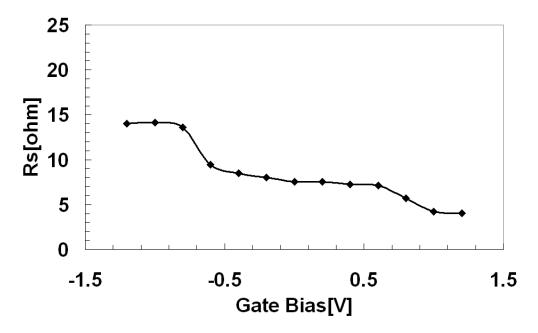

- Figure 4.12 Extracted series resistance as the function of gate bias for the SiO<sub>2</sub> capacitor with TiN gate. Insert: the as measured reflected voltage curve (charging curve) for all the bias conditions. In accumulation case, the substrate resistance is used as the series resistance.. 80

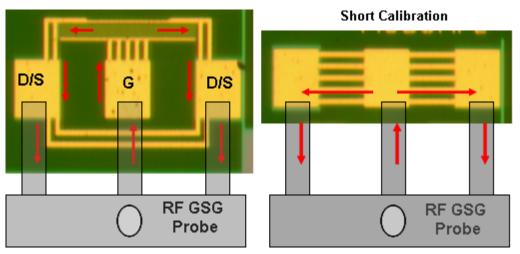

| Figure 4.17 Picture of device under test(left) and short calibration structure(right). The arrow represents for the current path during the test. Obviously, there is an addition length for the current to flow through in the device under test                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

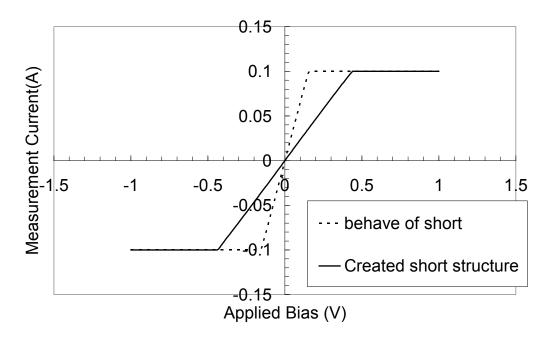

| Figure 4.18 I-V of short calibration structure and "created short" calibration structure by internationally hard break down DUT91                                                                                                                                                                                                        |

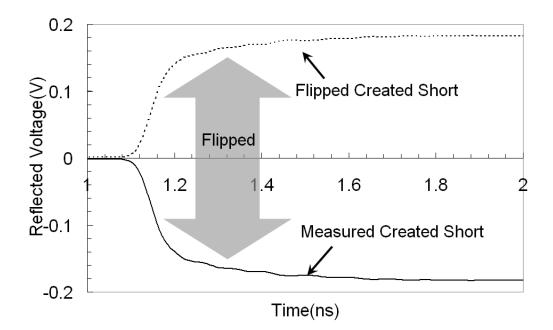

| Figure 4.19 The measured Reflected waveform of created short (solid line). It needs to be flipped first (dashed line) and then can be used as reference                                                                                                                                                                                  |

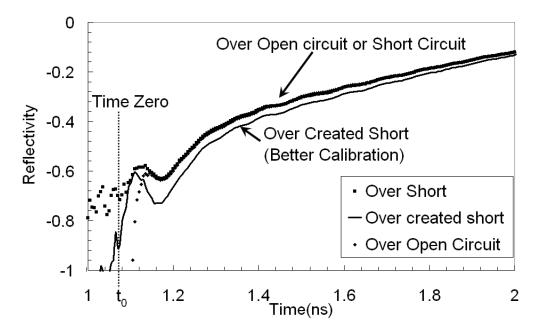

| Figure 4.20 The reflectivity obtained by dividing the measured reflected voltage of DUT over the one of flipped created short. The reflectivity extracted when the open or short circuit as calibration structure is also included for comparison                                                                                        |

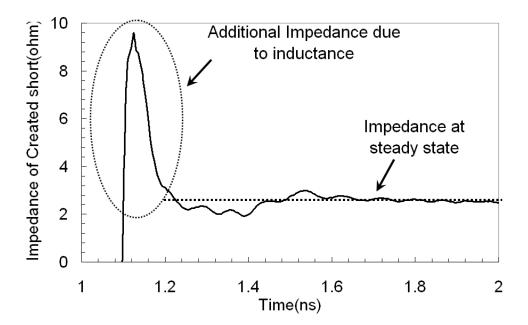

| Figure 4.21 Impedance of created short in time domain. The peak in this impedance comes from the inductance. It can be used to subtract from the impedance of DUT and then correct the effect of parasitic inductance                                                                                                                    |

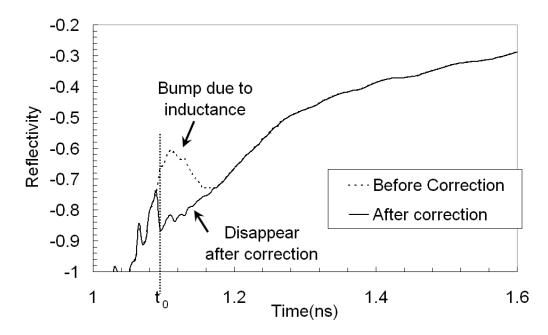

| Figure 4.22 The reflectivity of DUT after corrected with inductance. Obviously, the disappearance of bump indicates the success of correction procedure                                                                                                                                                                                  |

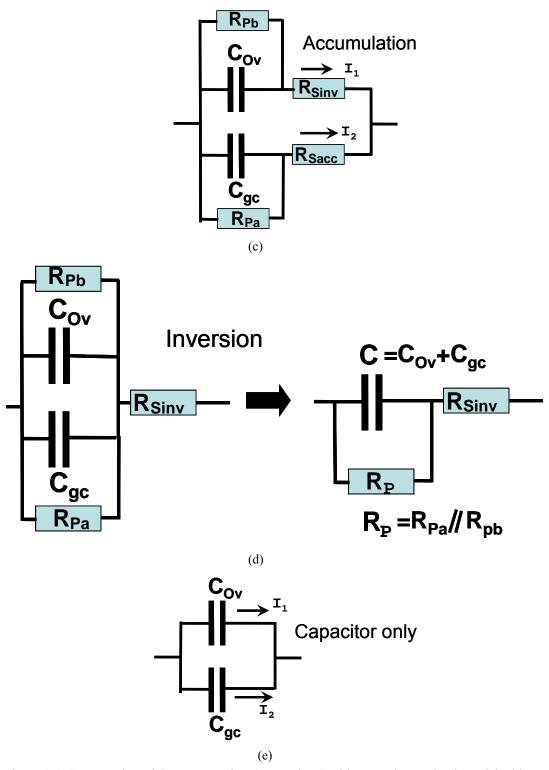

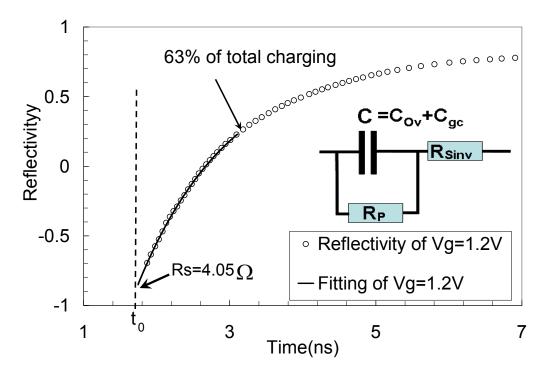

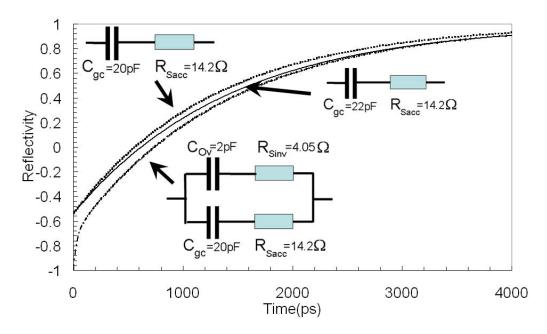

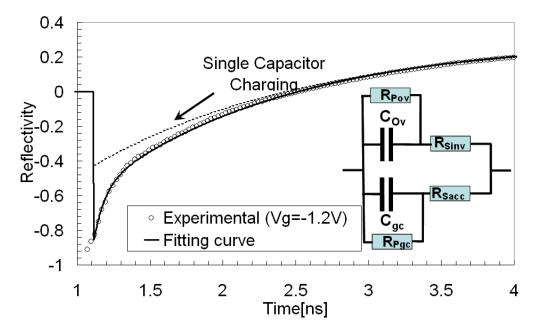

| Figure 4.23 Simulation of reflectivity of equivalent circuit with $R_{s,ac}=14.2\Omega$ , $R_{s,inv}=4.05\Omega$ , $C_{OV}=2pF$ $C_{gc}=20pF$ . For comparison, a single 20pF or 22pF capacitor charging is also shown.<br>On the long term, the two capacitors charge at the same rate and close to a 22pF capacitor (sum of those two) |

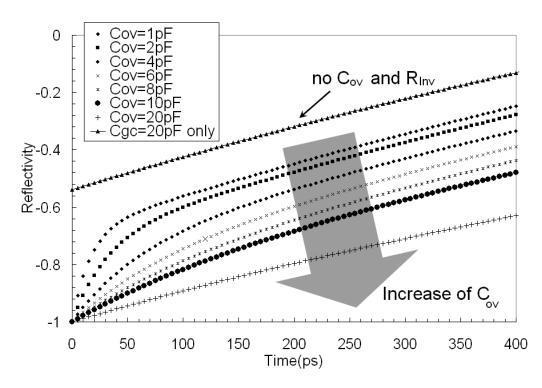

| Figure 4.24 Simulation of reflectivity with different overlap capacitance. Smaller overlap capacitance has more distinct charging time with channel capacitance. Therefore, shaper transition is observed                                                                                                                                |

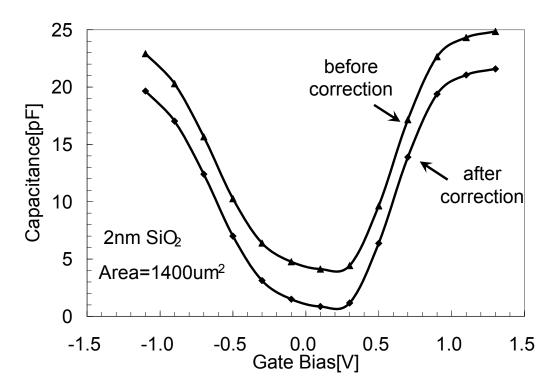

- Figure 4.26 The measured C-V curve for the 2 nm  $SiO_2$  capacitor with 1400  $\mu$ m<sup>2</sup> area (upper curve) and the corrected C-V curve (lower curve) after the removal of the overlap capacitance..101

### Chapter 5

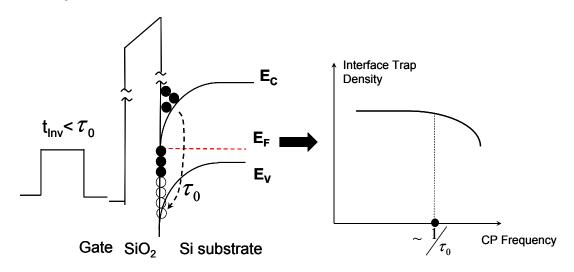

- Figure 5.3 Basic principle of finding interface filling time  $\tau_0$ . Fast gate pulse with inversion/accumulation time less than  $\tau_0$  is applied. Not all of all of the interface traps are filled and result in attenuation in trap density beyond certain frequency. Interface filling time can be identified by find the frequency where the trap density starts to decrease......112

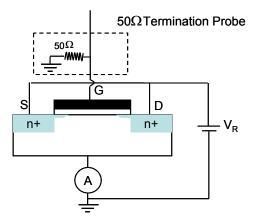

| Figure 5.4 | Experimental     | setup      | diagram   | of charge | pumping | measurement, | gate | of MOSF | ET is |

|------------|------------------|------------|-----------|-----------|---------|--------------|------|---------|-------|

| probe      | ed by specific : | $50\Omega$ | terminati | on probe  | •••••   |              |      |         | 113   |

- Figure 5.18 Illustration of what is the Pb center and how the strains are formed. The strain can be transferred and affect the bonding between atoms in three to four layers in three dimension.

| Figure 5.20 Illustration of interface trap distribution that can be considered to be continu     | iously  |

|--------------------------------------------------------------------------------------------------|---------|

| distributed in energy and over the transistor area                                               | 140     |

| Figure 5.21, The per step time and the total time required to cross the whole band gap (assuming | ; equal |

| energy steps) are plotted as a function of number of steps (energy levels) needed to cro         | oss the |

| band gap. A broad minimum of 11.8ps total time is evident                                        | 142     |

|                                                                                                  |         |

- Figure 5.22, Similar as Figures 5.13 and 5.14 except that the two-step CP model with a new  $\tau_0$ =10ps is used. The result is fairly similar to those in Figure 5.13 with a little shallower depth for the common frequency range.

# Chapter 6

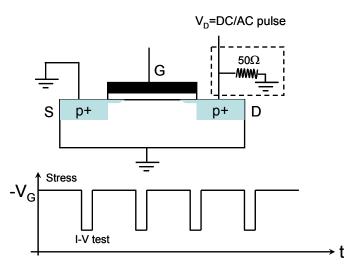

- Figure 6.1 The experimental set up for NBTI study with drain bias. The gate is stressed and interrupted after certain time to measure the device  $I_D$ -V<sub>G</sub> characteristics. The source and substrate are grounded while either a dynamic or static voltage is applied to drain. Here a 50 $\Omega$  terminated probe is used at drain to minimize the reflection of high speed signal.....148

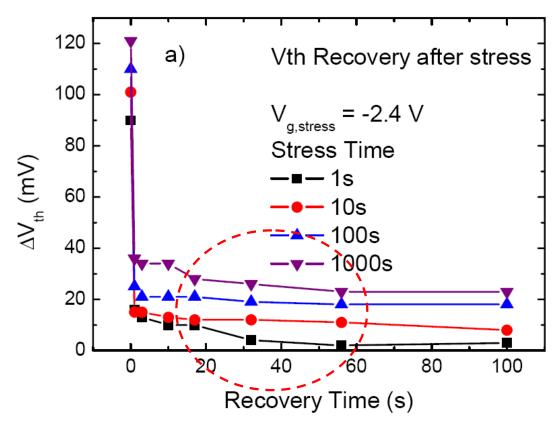

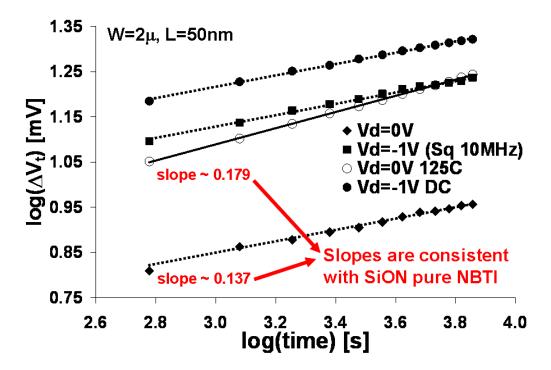

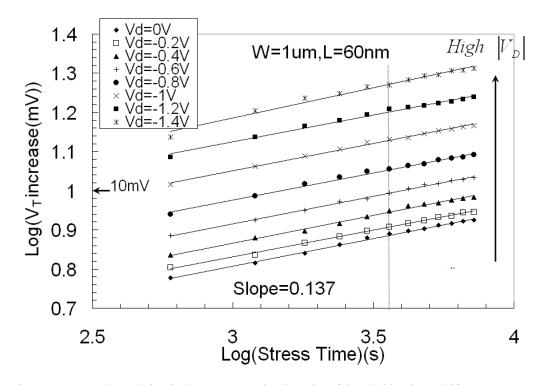

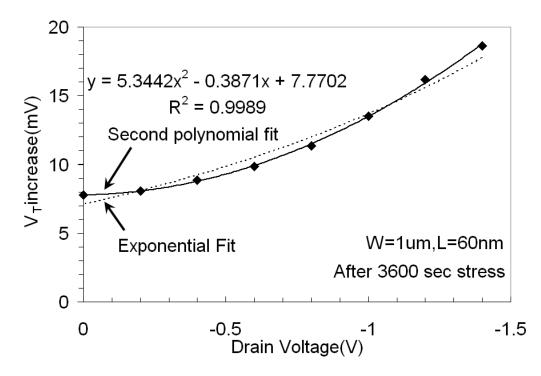

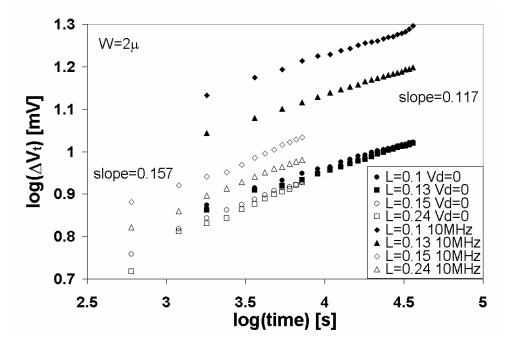

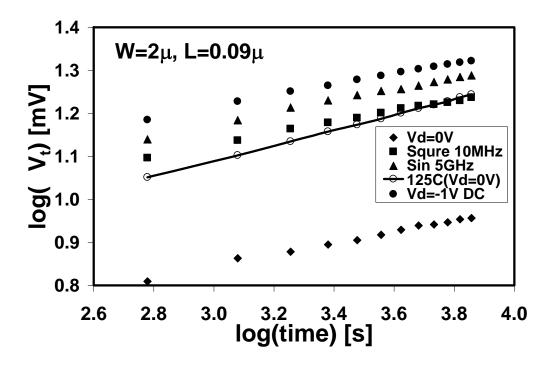

- Figure 6.3 Log-log plot of our NBTI results showing  $V_T$  shift versus time. Four traces are shown here. Two of them are normal NBTI(without drain bias) at different temperature 0C and 125C. The other two are NBTI with drain bias but room temperature. Both DC voltage and a pulse with 50% duty cycle drain bias condition are studied......151

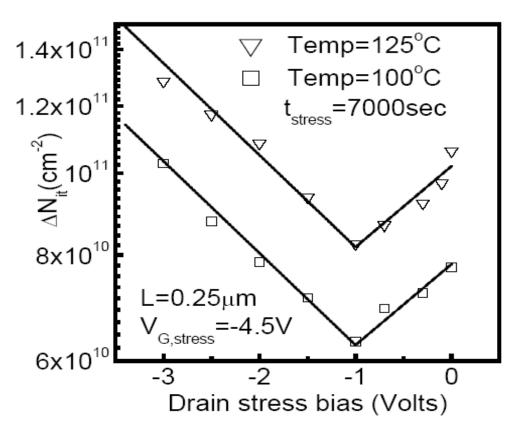

- Figure 6.4 The reported NBTI result with various drain bias. The turn around behavior is happened at  $V_D$ =-1V. The data is taken from reference [37].....154

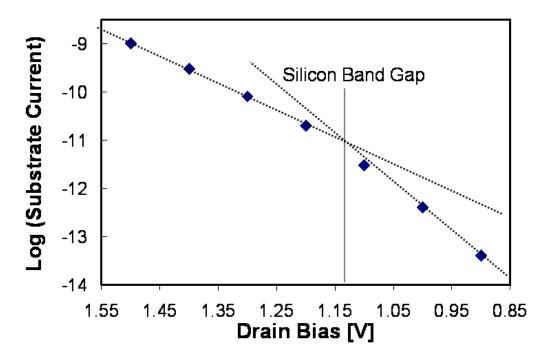

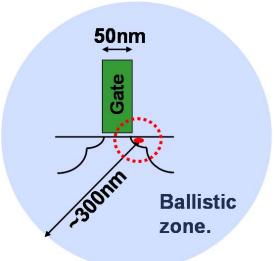

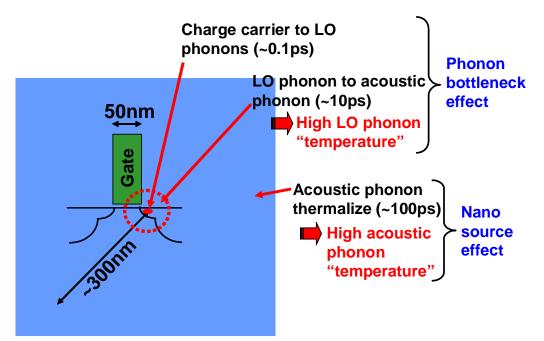

- Figure 6.9 The drain bias induced a heating source (red point in the figure) and localized hot spot (dashed circle) leading to high temperature in the channel......162

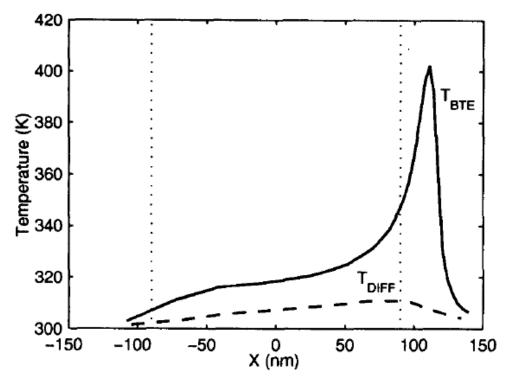

- Figure 6.10 Temperature distributions along the channel of a 180 nm MOSFET. The solid line represents the BTE solution averaged over the channel depth and the dashed line the diffusion theory prediction. The vertical dotted lines represent the metallurgical source and drain junctions, respectively. This figure is taken from [42].....163

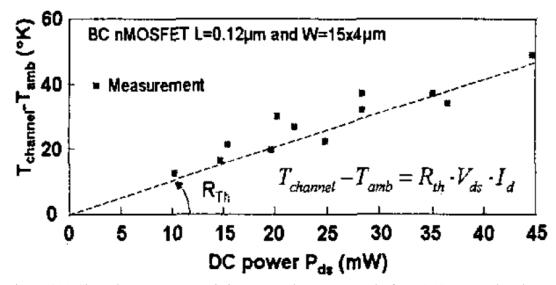

- Figure 6.11 Channel Temperature variation versus the power supply for a 0.12um gate length buried channel n-MOSFET SOI device. Figure is taken from reference [134].....167

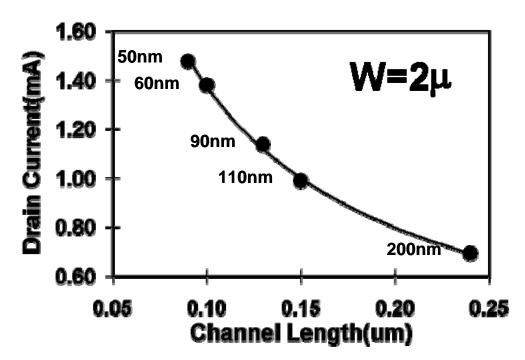

- Figure 6.15 NBTI (room temperature) as a function of channel length. Two sets of measurement conditions are used. One interrupts the stress at every 30 minuets interval. The other at 10

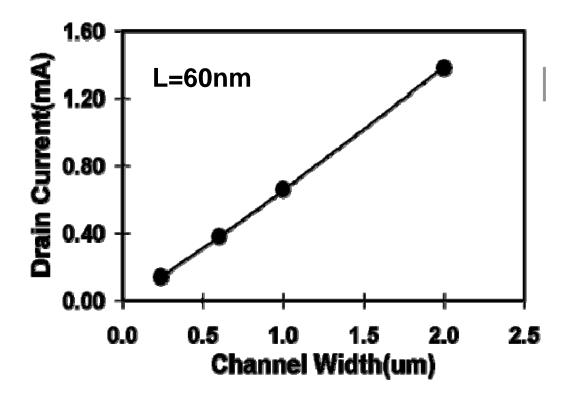

Figure 6.16 drain current as a function of different channel width from 0.25 µm to 2µm......174

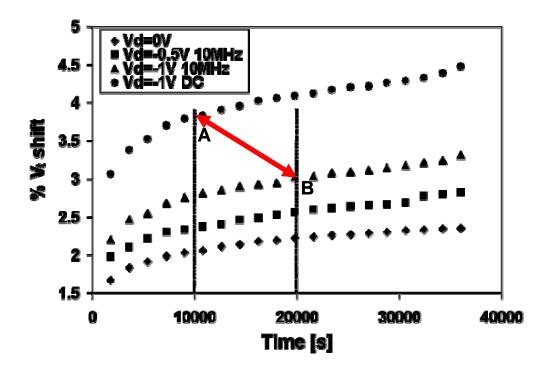

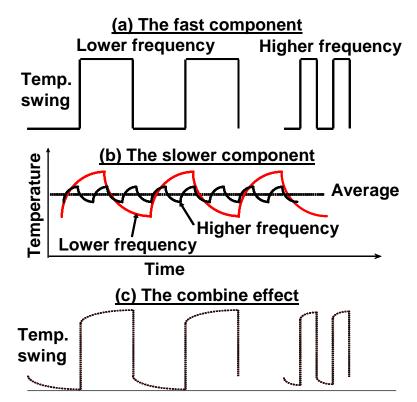

- Figure 6.21 With drain voltage modulated by a square wave. The channel temperature is modulated as well. (a) The fast component of temperature due to the hot-spot effect. The temperature response is so fast that it follows faithfully the drain bias. (b) The slow component of temperature due to heat diffusion. The lower the frequency, the more time for temperature build up during the ON cycle and more time for cooling during the OFF cycle. The temperature swing is larger for lower temperature. (c) The combined fast and slow temperature profile. The hot-spot effect is much larger than the heat diffusion effect......183

# Appendix

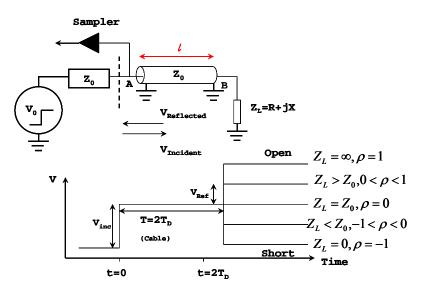

| Figure A.1 Basic TDR setup and TDR waveforms with resistive terminations205                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

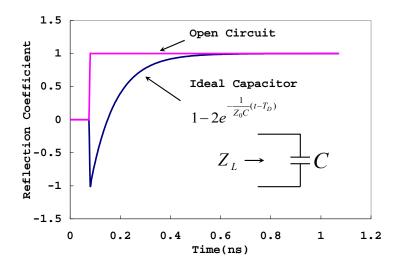

| Figure A.2 Simulated TDR response of Ideal 2pF capacitor                                                                                                         |

| Figure A.3(a) Series R-C load TDR response(b) Shunt R-C load TDR response (c) Series/Shunt<br>R-C load TDR response                                              |

| Figure A.4 TDR response of capacitor with different rise of incident step voltage215                                                                             |

| Figure A.5 cables and probe effect on TDR measurements                                                                                                           |

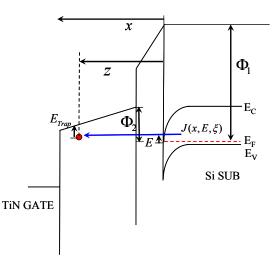

| Figure C.1 Energy diagram of n-channel MOS capacitor at inversion. Electrons at inversion have certain probability to tunnel into the traps located in the oxide |

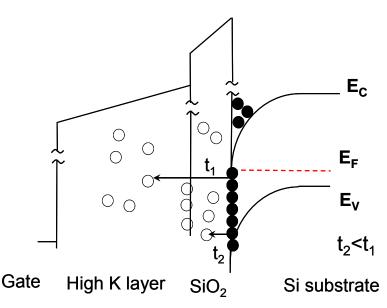

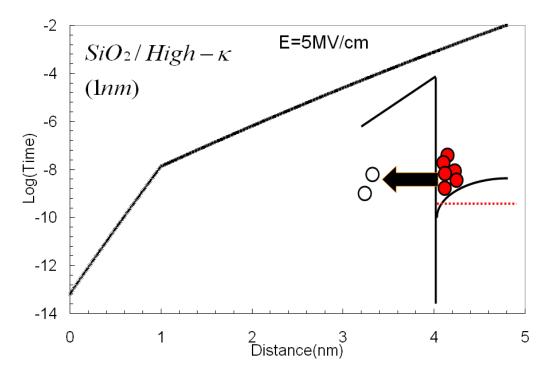

| Figure C.2 Energy band diagram of dual layer with SiO <sub>2</sub> /HfO <sub>2</sub> as gate dielectrics. Electrons at                                           |

| inversion can tunnel into the traps located in the bulk of high K layer                                                                                          |

# Chapter 1 Introduction

The steady downscaling of transistor dimensions over the past two decades has been the main stimulus to the growth of silicon integrated circuits (ICs) and the information industry [1]. The driving force behind the relentless downscaling of the MOSFET in integrated circuit is, as always, cost per function. Smaller size means more transistors per unit area and a chip can either be smaller or do more [2-3]. At the same time, performance must also be improved. To achieve that, the gate dielectric thickness must shrink as well [4-5]. However, as the gate oxide gets thinner, challenges are faced as well. At state-of-the-art 1.2nm EOT MOS devices, the gate oxide is so thin that leakage current reaches over 800A/cm<sup>2</sup> [3]. Even though the high  $\kappa$  dielectrics used in the recent 45nm technology alleviates the leakage current, it is still believed that the leakage current will be higher in the future device because of the aggressive scaling down of oxide thickness. Such high leakage causes many problems. Power dissipation is clearly a serious issue. Even basic device characterizations are suffering.

As basic and important as C-V measurement, high precision is not achievable when the leakage is too high. Some advances such as multi-frequency approach have helped [6], but can only go so far [7-8]. Extensive investigations have been carried out to search for a simple and accurate C-V measurement technique [6-19]. The Time Domain Reflectometry (TDR) method introduced in this work is a novel solution to this problem. With the TDR method, C-V measurement can be done with high precision and can be automated.

With power consumption problem associated with high gate leakage current, it is natural that the industry seeks alternative to the traditional SiO<sub>2</sub> gate dielectric [20-22]. Recently, high dielectric constant (high- $\kappa$ ) materials start as the gate oxide in 45 nm technology. However, the whole reason why silicon dominates the IC industry for many decades is that the thermally grown SiO<sub>2</sub> is an exceptionally good material for gate insulator. To replace SiO<sub>2</sub>, the high- $\kappa$  materials must also be low in defect density and can withstand high electrical stress. It represents a big challenge [12-14]. It is found that a high density of defects in these materials lead to undesired transport though the dielectrics and trapping-induced instabilities [23-25]. To point a direction for further manufacturing process improvement, it has become extremely important to characterize the defects and to study how new defects are created in them under electrical stress.

To that end, very few measurement techniques are at the disposal of scientists and engineers. Frequency dependent charge-pumping (FDCP) has emerged as the best candidate for the task [26-27]. However, even though the technique has been around for more than twenty years, the basic question of how deep does it probe has not been resolved yet. There are two camps of thought in the literature [28-29]. The differences in interpretation have led to an even more serious debate over whether new defects

can be created in the high-k materials under electrical stress. The implication in the reliability of high- $\kappa$  material is obvious and the resolution of this debate becomes urgent. In this work, we resolve this debate using a combination of experimental and theoretical approaches. Our result provides the first clarification of this important question.

The reliability of high- $\kappa$  gate dielectric is one of the many reliability issues that become more acute with scaled down MOSFETs. Another standout reliability issues in nanoscale MOSFET is the Negative Bias Temperature Instability (NBTI) of p-channel devices [30-33]. It has become much more worrisome because it gets worse rapidly when the gate oxide becomes thinner and nitrided oxide is used in the industry to combat boron penetration [34-36]. Pure NBTI for pMOS has already become the most serious reliability issue in current leading edge technology. The recent discovery that the NBTI degradation with a drain bias is even worse naturally pushes NBTI as the key reliability constraints for future device scaling [37-41]. The fact that the impact of drain bias increases with reduced channel length is even scarier. While it seems to be another issue associated with the ultrathin gate dielectric, the effect of the drain bias is not easy to explain.

Most of the studies of the drain bias effect on NBTI have been done at high enough drain voltage so that serious channel-hot-carrier (CHC) effect occurs [37-41]. Thus most explanations invoke either a NBTI enhanced CHC degradation or CHC

enhanced NBTI degradation. If that were the case, then the effect might not be so serious because the CHC effect for most advanced MOSFET is very minor at the operation voltage. However, another possible cause of this problem prompted us to look at this phenomenon at conditions that CHC is almost absent. We find that the drain bias enhanced NBTI is definitely a serious problem for advanced MOSFET in the nanoscale. Our results indicate that the cause comes from another nanoscale specific phenomenon, namely ballistic phonon effect [42-44]. While NBTI is exacerbated by the nanoscale gate dielectric, the drain bias effect, at least in our case, is also worsened by the nanoscale transistor channel length. This is a truly troublesome finding because it means a totally new mode of reliability degradation will exist. All temperature sensitive reliability issues of the transistor will be impacted and the impact will become more severe as the transistor shrinks further, particularly for high frequency operation.

Actually, high frequency application is another important area for these nanometer MOS devices to make their mark. Taking advantage of their excellent RF performance, these advanced MOS devices have been widely used for many microwave applications in areas of mobile communication and wireless networking [45-46]. At the same time, corresponding high frequency device measurement techniques are urgently demanded for properly characterizing their performances. However, a reliable high frequency measurement also requires a set of specific skills and instruments, which are not widely used in traditional device characterization. Absence

of careful consideration can easily cause measurement error and misinterpretation of results. For example, without specific design, when one launches a high speed pulse on a capacitor, some part of incident pulse is reflected back to source due to the impedance mismatch between the probe and capacitor. As a result, the actual voltage across the capacitor is much smaller than designated. These impedance mismatch issues are not important for traditional DC or low frequency measurements. However, as the measurement frequency gets higher enough, signal wavelength is reduced to be comparable with physical size of measurement components. Under that circumstance, all electrical components (such as cable, adaptor and probe) should be treated as a transmission line instead of a single wire and impedance match issue becomes a significant problem.

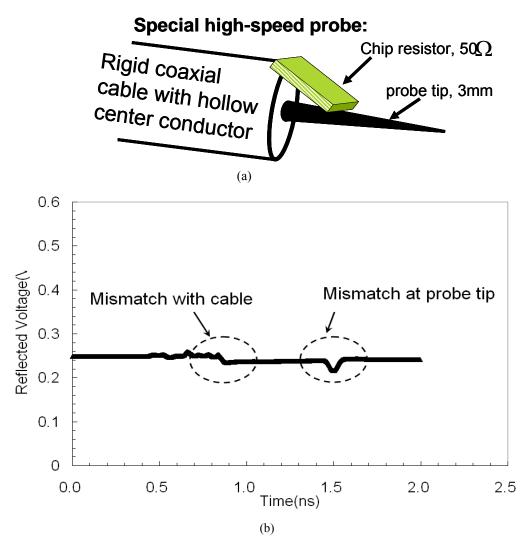

To get around this difficulty, we come up some solutions. In our study, we homely build a 50  $\Omega$  terminated high-speed probe. It matches the source output impedance as well as the cable characteristic impedance. It is allowed to launch a high speed signal (<20GHz) at DUT with reflection loss less than 1%. Based on that, we are able to implement the charge pumping over 1GHz with square wave for the first time. The new results clear the debate over probe depth in high K defect characterization. This specific probe is also used in the setup to study the dynamic drain bias frequency dependent NBTI effect, which helps to identify the impact of our new mode of reliability degradation.

Moreover, any design of reliable high frequency measurement setup requires a tool to evaluate the setup for further improvement. Time domain Reflectromety(TDR) is such a system that is well known for its capability to detect impedance at time domain and identify the location of impedance mismatch. Besides its help to high frequency measurement, it also offers solutions to some challenges in advanced MOS device characterization. With a simple capture of time domain impedance profile of MOS capacitor, C-V characteristics, series resistance and overlap capacitor can be extracted with great accuracy. This new technique is free of difficulties that met by traditional C-V methods and can be applicable to routine industrial test procedure.

## Chapter 2

## **Background and Literature Review**

In chapter 1, we provide a brief introduction as well as the main frame of this thesis. In this chapter, we will give some background about this thesis topic. We will address recent developments of advanced thin oxide MOS device as well as emerging challenges in device characterization. Specifically, we will first show why the aggressive scaling down of oxide thickness is evitable in section 2.1. We will further address what the problem for thin oxide device is and how they affect the device characterization such as C-V measurement. C-V measurement is the first of three parts in this thesis work and will be discussed in detail in chapter 4 and 5. In order to prepare the readers with enough background, section 2.2 describes the principle of conventional C-V method and its difficulty in the application of advanced thin oxide MOS device.

Since the high  $\kappa$  dielectrics has been released to be used as gate oxide in the state of art 45 nm node technology, its reliability becomes a big concern. Section 2.3 will address recent advance and the unsolved question- where is the trap increase after the electrical stress. The answer must turn to the charge pumping measurement. Therefore, its principle and application to detect traps in the oxide is reviewed in section 2.4. Even though the measurement technique sounds simple, the interpretation is controversial. This is exactly the role of the second part of this thesis work – answering the question: how deep does charge pumping probes.

Traps in the high  $\kappa$  dielectrics are one of the reliability concerns in the many. The current most serious one is negative bias temperature stability (NBTI). Section 2.5 will provides the basic background of NBTI. This knowledge is important for understanding third part of this thesis work – a new mode of NBTI.

The purpose of this chapter is to lay down enough knowledge or background for the reader to understand this thesis work. Those who are very familiar with related materials can skip this chapter and go directly to chapter 3.

#### 2.1. Thin Oxide MOS Device

The continuous growth in integrated circuit(IC) density and speed is the heart of the rapid growth of electronics. The electronics industry is now the largest industry in terms of output as well as employment in many nations. It will be no doubt that this big industry will continue playing more important role in economic, social and even political development throughout the world. This importance is the motivation as well as a formidable driving force that urges the continued rise in IC integration density and speed.

The rise in circuit density and speed has been accompanied by the scaling of

MOSFET's to lower the cost per function and meanwhile increase the performance and functionality of the circuits. Metal-oxide-semiconductor field-effect transistor (MOSFET) is the most important and fundamental building block of very-large-scale-integrated (VLSI) circuits today in IC industry. Ideally, a MOSFET has high drive current (when the gate electrode is biased to turn the transistor on) and low leakage current (when the gate electrode is biased to turn the transistor off).

Reduced size for density requires a short channel length and small channel width. At the same time, high circuit speed is achieved by the reduction of the gate insulator oxide thickness which leads to an enhancement of the MOSFET's current drive capability as well as a better control of the short channel effects.

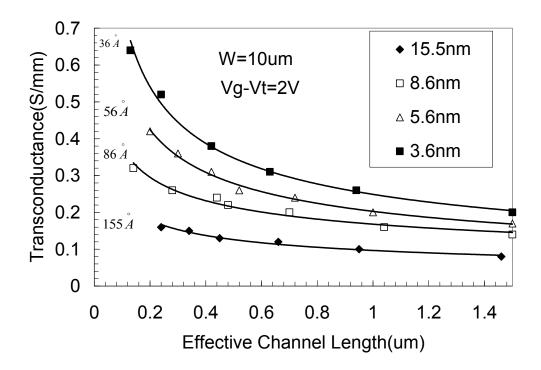

The transistor driving or saturation current  $I_{dsat}$  is an important parameter because it determines the time needed to charge and discharge the on chip capacitive loads. Thus, it impacts the product speed more than any other transistor parameter. This can be fulfilled by a short channel and high gate oxide field because the inversion layer charge density is proportional to the oxide field [4]. Practically, high drain current has been achieved by reducing the thickness of the gate dielectrics because  $I_{dsat}$  of a thin-oxide MOSFET can benefit more from channel length scaling, as shown in Figure 2.1 which is taken from Chenming Hu's paper [5]. As illustrated, scaling the channel length alone yields little increase in current from the 155  $\stackrel{\circ}{A}$  oxide thickness, far less than the textbook I/L dependence would predict. After all, even as L

approaches zero,  $I_{dsat}$  approaches a constant. In contrast, reducing the oxide thickness yields a considerable increase in  $I_{dsat}$  by increasing the oxide field and inversion charge density.

Figure 2.1 Experimental data reported by Chenming Hu [5] for MOSFET drain current versus effective channel length and gate oxide thickness. High oxide field not only increase MOSFET current, but also increase the benefit of shrinking the channel length. It is reported that the data is in good agreement with the theoretical prediction [4], although different from the textbook MOSFET model.

Consequently, motivated by the rise in circuit density and speed, advanced MOS device with thin gate oxide and short channel is highly demanded for pursuing device miniature and high driving current. Over the past three decades, transistor channel lengths and oxide thickness is reduced with each new generation of manufacturing technology. This trend is reflected in the International Technology Roadmap for Semiconductors (ITRS) [1]. Today the 45 nm channel length transistors are in mass

production with physical gate length down to 18 nm.

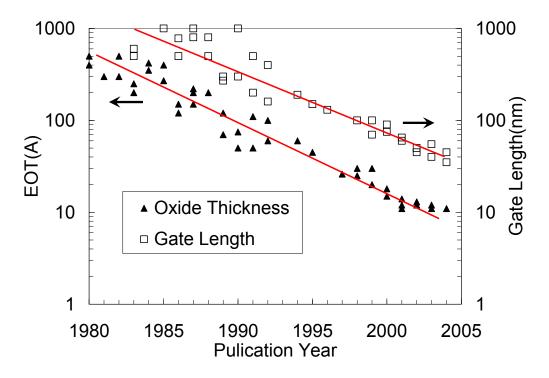

Figure 2.2 Scaling trend of gate oxide thickness over the past five technology generation from the 0.18um to 65nm node. Experimental data ( $L_{Gate}$ ) and equivalent oxide thickness (EOT) are collected from device papers presented at conference. When only inversion oxide thickness ( $T_{Inv}$ ) is provided in the literature, 8Å is subtracted from  $T_{Inv}$  to account for the additional capacitance component resulting from the poly depletion effect at the gate side and the quantum mechanical effect at the channel side. This figure is taken from reference [2].

Moreover, huge progress in gate oxide fabrication process has made it possible to realize ultra thin films with an acceptable thickness roughness and uniformity as well as a low defect density. As thin as 1.2nm EOT gate dielectrics are used in today's state-of-the-art complementary MOS (CMOS) technology, which corresponding to three to four layers of silicon atoms. Figure 2.2 illustrates the evolution of the technology nodes and gate oxide thickness as published over past two decades. It should be noticed that each update enhances the technology node every year.

#### 2.2. C-V Measurement and its Difficulty

With dielectrics as thin as few atomic layers, this level of nanotechnology brings the challenges. When the oxide is thin, substantial direct tunneling current flows from the gate to the channel even under low voltage at operating conditions. More badly, this leakage current is found to increase exponentially with the decreasing oxide thickness [47]. At 1.2nm EOT MOS device, the gate leakage current density exceeds 800 A/cm<sup>2</sup> [3]. With further scaling down of oxide thickness, a tunneling current density over few kA/cm<sup>2</sup> is very possible.

Such a high leakage current has a significant impact on device characterization techniques. Even the basic measurement such as Capacitor-Voltage(C-V) is affected and loses its accuracy. Many efforts have been made to seek a reliable technique to obtain accurate C-V characteristics under this high leakage current situation [6-19]. Unfortunately, all methods reported so far have certain constrains and limitations. No satisfactory solution has been found yet. That's our motivation here to introduce this new simple accurate C-V measurement technique using the TDR method. It offers a possible solution to current difficulties suffering in industry now.

#### 2.2.1. Standard C-V Characterization of MOS Capacitor

In MOS device characterization, MOS capacitor is a good test structure for its

simplicity. C-V characteristics refer to the capacitance(C) of MOS capacitor as the function of applied gate voltage (V). In addition to the capacitance values, a great deal of information about the MOS capacitor and oxide/semiconductor interface can be obtained. The C-V curve can be manipulated to extract the equivalent oxide thickness (EOT) [48-50] and effective mobility [51-52] from measured capacitance in the strong accumulation and inversion regime respectively. Besides that, interface traps [53-54]; substrate doping profiles [55-56] can be obtained as well. Therefore, accuracy is greatly demanded in C-V measurement because it is of significant importance for parameter extraction.

Figure 2.3 Illustration circuit connection of conventional standard C-V measurement set up using LCR meter. AC signal superimposed on a DC voltage is employed on gate and resulting AC current is measured at substrate electrode. This figure is taken from reference [53].

However, the available measurement techniques are not such wonderful for this important device characteristic. As shown in Figure 2.3, the existing method is typically fulfilled by applying a small AC signal (~10 to 50 mV) on top of the DC

bias across the structure and sensing the capacitive displacement current at the same frequency (75Hz to 1MHz). In order to do that, it is necessary to separate the AC current component (capacitive displace current) from DC component (leakage current). This is commonly performed using phase sensitive a LCR meter (such as HP 4285) or a lock in amplifier. Commonly, the phase and magnitude of the impedance is measured.

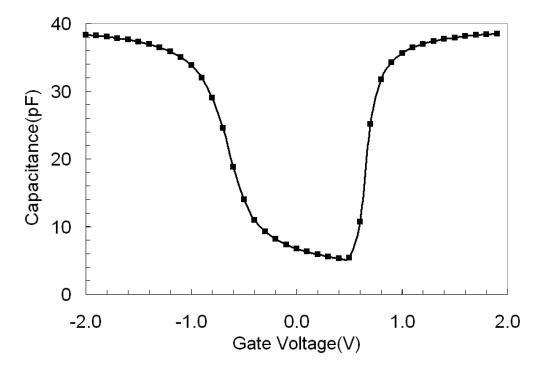

Figure 2.4 Simulation of ideal low frequency C-V using the CVC program [58]. At two ends of this voltage range, the shape of C-V is more flat and capacitance is high because either accumulation or inversion layer is formed. In the range of between, device is under depletion and capacitance is low.

Figure 2.4 shows ideally what a C-V curve would look like. This is a theoretical simulation of low frequency C-V using the CVC program developed by Professor John R. Hauser from North Carolina State University [58]. At very negative (below flat band voltage) gate bias, an accumulation layer of holes is formed at

oxide-semiconductor interface. While at very positive (above threshold voltage) gate bias, the electrons, which can respond to the slow change in low frequency capacitor voltage, builds an inversion layer at interface. At these two operation modes, the MOS capacitance is just oxide capacitance and exhibits itself as a flat line in C-V curve (Figure 2.4). When a gate voltage between the above two modes is applied, a space charge region is induced in the semiconductor. At this mode, the capacitance across depletion layer plays more important role and results in much smaller capacitance than oxide capacitance. Therefore, a decrease of capacitance is shown in C-V curve.

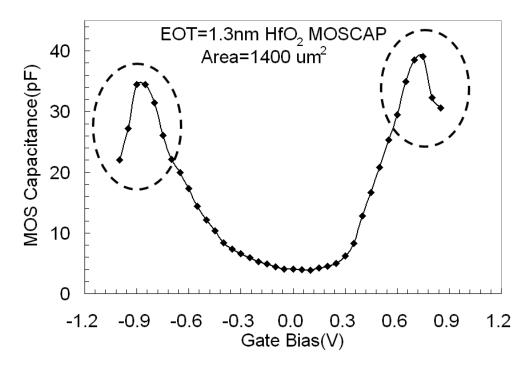

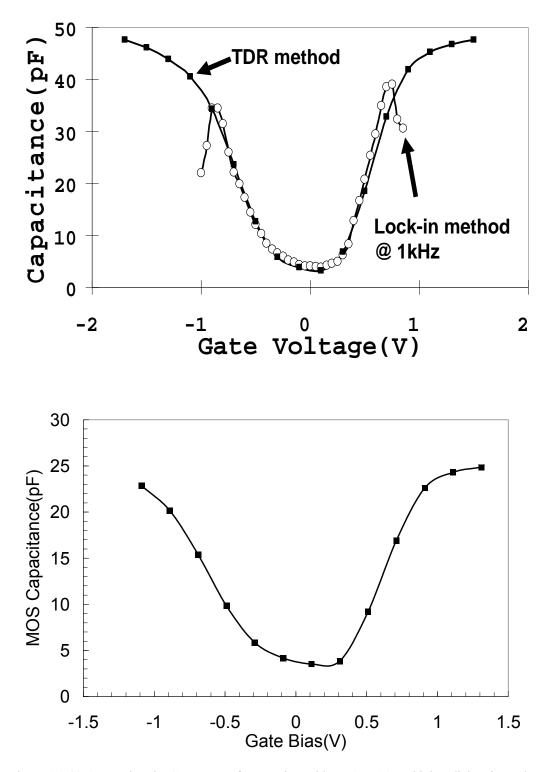

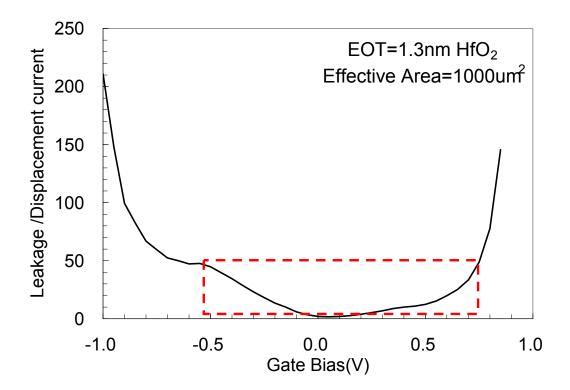

Figure 2.5 is the shape of expected C-V behavior. When the oxide gets thin, the existing measurement technique has problem in conveying results as expecting. Instead, it shows analogous behavior as shown in Figure 2.5. This is the C-V curve measured at EOT 1.3nm 1400 $\text{um}^2$  n-channel HfO<sub>2</sub> MOSCAP with lock in amplifier. Same oxide thickness of SiO<sub>2</sub> is much worse and has difficult in accurate measurement. This part of data is extracted at 1KHz which is considered as high frequency. The low frequency C-V behavior obtained here is due to the transistor-like designed test structure to provide inversion charge. The detail description of the test structure will be done at chapter 4.

The most of important sign in this data is the deviation of inversion and accumulation (two ends) part of C-V curve from the expectation. Instead of pretty constant with voltage, the capacitance significantly decreases. Similar phenomena are observed by many other research groups [6, 9-13]. For example, Yang *et al.* found that the

capacitance of 1.7 nm MOS capacitor depends on the measurement frequency and decreases with increasing gate bias [6]. Ahmed *et al.* noticed a faster roll-off of capacitance at strong inversion with the increasing channel length for sub 2nm oxide devices [10].

Figure 2.5 The measured C-V curve using conventional measurement techniques with lock in amplifier to detect phase and magnitude for EOT 1.3nm  $1400 \text{um}^2$  n-channel HfO<sub>2</sub> MOSCAP. Same oxide thickness of SiO<sub>2</sub> is much worse and has difficult in accurate measurement. Note that the C-V is anomalous at inversion and accumulation with sharply decreases of capacitance.

#### 2.2.2. Limitation of Conventional C-V Measurement

This anomalous behavior deprives the role of C-V as a basic characteristic for parameter extraction because the extraction like EOT and effective mobility is highly dependent on the accuracy of gate capacitance at accumulation and inversion region. It is believed to come from the shortness of measurement technique, specifically, from the limitation to handle high leakage current and series resistance.

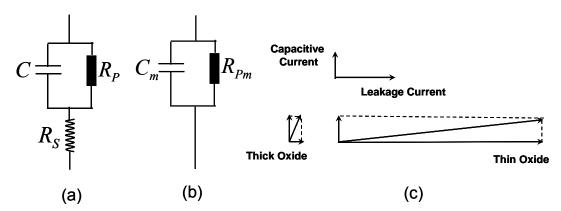

Figure 2.6 (a) three element equivalent circuits for leaky MOS capacitor, C is the measured capacitor,  $R_P$  represents the leakage current component,  $R_S$  is the series resistance. (b) Parallel circuit model used in conventional C-V measurement. It shows that the actual measurement yields a  $C_m$  (measured capacitance) in parallel with  $R_{Pm}$  (measured parallel resistance). (c) The current component in traditional C-V measurement, leakage current and capacitive current are 90 degrees out of phase. For the same capacitance with same amount of capacitive displacement current (the vertical component in the figure), the leakage current in thinner oxide is much larger. It may overwhelm the displacement current and the measurement technique will lose its accuracy.

To describe the exact reason, a simple three-element equivalent circuit, as shown in Figure 2.6(a), would be required to conceptually model the thin oxide MOS device [6]. In addition to measured capacitance *C* and series resistance  $R_s$  arising from the finite resistance of the source/drain contacts, inversion channel and gate material, a shunt resistance  $R_p = \partial V_g / \partial I_g$  due to the leakage current is also included [59]. As the gate oxide gets thin, leakage current increases exponentially. As a result, shunt resistance  $R_p$  reduces sharply and becomes comparable in magnitude to the series resistance  $R_s$ . So both shunt and series resistances are required for thin oxide MOS device.

In the conventional C-V measurement for these leaky thin oxide capacitors, it typically uses parallel circuit model in Figure 2.6(c). Compared to more accurate three elements equivalent circuit, we have seen that we can no longer directly relate the measured capacitance value  $C_m$  with that of the dielectric film *C* because of the significant contribution of the series resistance  $R_S$  [7]. At the leaky MOS device, series resistance  $R_S$  and shunt resistance  $R_P$  are comparable so that the capacitance test voltage is divided between the MOS capacitor *C* and the series resistance  $R_S$ . Less magnitude of voltage across the MOS capacitor results in smaller measured capacitance. This capacitance degradation becomes more severe at high gate bias region where the leakage current is high. Finally, it causes huge gate capacitance attenuation observed in Figure 2.5.

#### 2.2.3. Improvement and Limitation of C-V Technique for Thin Oxide

Being aware of the error in the conventional C-V measurement, many research groups have made efforts to find a correction procedure [6-19]. It can be seen from the three element equivalent circuit that, in order to obtain capacitance with high precision, the other two components  $R_S$ ,  $R_P$  should also be determined accurately. However, from a single measurement of impedance phase and magnitude, only two of these three parameters can be ascertained. Therefore, one more relation is required to extract all these three unknown components. This problem can be solved by measuring capacitor at two different frequencies as proposed by Yang and Hu [6]. With an additional measurement at a different frequency, all three parameters can be known.

Although, theoretically, this two-frequency model is correct, there are numerous limitations in practice. As illustrated in Figure 2.6(c), for the same capacitance with same amount of displacement current (the vertical component in the figure), the leakage current in thinner oxide is much larger. It may overwhelm the displacement current and instrument precision is mostly spent on accurate determination of the leakage current components.

As a result, a small error of the phase angle introduces a large error in the capacitance measurement. Nara *et al.* pointed out that the inevitable error in the measurement limits the usefulness of this method in ultra thin gate oxides [8]. Ghibaudo *et al.* showed that the measurement error caused by series resistance effect is amplified by the shunt resistance  $R_p$  and gets worse for thinner oxide [7]. Zhu *et al.* found that the dominant source of measurement error comes from  $R_S/R_p$  term, which becomes severe when oxide gets thinner [13].

To that end, many improvements have been made on the two frequency method to preserve its effectiveness [16-18]. For example, Luo et al. developed a four-element equivalent circuit which accounts for the parasitic capacitance [17]. Moreover, the finite channel resistance prompted some groups to use a distributed network to replace the three element model [10-13]. All these approaches share the same basic scheme –

the measurement of impedance is affected by both shunt and series resistance. Even more elaborated refinements and therefore complexities are introduced to cope with the increasing error associated with ultra thin gate oxide. This difficulty has led Teramoto et al. to try a new approach that relies on resonance [19]. As a result, all these difficulties have brought about a need for new measurement procedures which can account for both series and shunt resistance.

In chapter 3, we introduce a new simple accurate C-V measurement technique based on Time domain Reflectrometry (TDR). It completely solves the above problem and is very accurate even under leakage current as high as 5000A/cm<sup>2</sup>. Besides that, it can also accurately offers series resistance and overlap capacitance simultaneously which will be demonstrated in detail in Chapter 4.

# 2.3. High K Gate Dielectrics and its Reliability Issue

The difficulty in C-V measurement is not the only problem caused by such high leakage current. Power dissipation is another serious concern, even though leakage current is still negligible compared to transistor driving current. Typically, a standby power (when the transistor is off) within 100mW can be tolerated by today's high performance CMOS logic chips. With the typical 0.1 cm<sup>2</sup> active gate area per chip, the maximum tolerable gate leakage current would be of the order of 1 A/cm<sup>2</sup> for an operation voltage of 1 V.

Unfortunately, as the gate oxide is scaled down to 2nm, it has run into this off-power limitation [3]. To push oxide thickness further down, industry has introduced nitrogen in the growth of SiO<sub>2</sub> in 90/65 nm generation. In this way, a heavily nitrided SiON (oxynitride) films are formed to block boron diffusion reducing gate leakage. Besides the advance in the fabrication process, improvement is also made in circuit design area. More power tolerant chip-architecture IC designs as well as sophisticated power management schemes are developed. In recent logic circuit applications, these leaky advanced MOS devices are used in core of the chip for fast operation. The rest of functionality such as I/O voltage applications is implemented by thick oxide devices. In this way, the leaky gate active area can be reduced.

Although all these developments can help to somewhat extend the life of SiO<sub>2</sub> and push oxide thinner as to today's 1.2nm, it is clear that SiO<sub>2</sub> has approached its physical and electrical limits and leakage issue is the obstacle for further down scaling. To circumvent this impediment, it is natural that the industry seeks alternative gate dielectric as a replacement of SiO<sub>2</sub>. Fortunately, they found one. In the recent released 45 nm technology by Intel, Hf- based materials is used as gate oxide with dielectrics  $4\sim5$  times larger than pure SiO<sub>2</sub>. With these high- $\kappa$  dielectrics, leakage current is  $4\sim5$ times lower than 65 nm technology because the physical thickness of the gate stack can be increased while maintaining the same capacitance.

Meanwhile, these high  $\kappa$  materials do not have such good interface quality as thermal

grown SiO<sub>2</sub>. It is not surprising because SiO<sub>2</sub> has been used for more than 30 years. It offers so fantastic and tremendous important material and electrical properties, including a stable thermodynamic Si/SiO2 interface with low defect charge densities  $(10^{10} cm^{-2} eV^{-1})$  as well as superior electrical insulation and interfacial bonding properties. Like other transition metal oxides, the high  $\kappa$  material exhibits a high density of intrinsic electron traps in the material. Moreover, the SiO<sub>2</sub> buffer layer, usually formed between high  $\kappa$  film and silicon substrate to improve interface quality, is not as good as thermal grown SiO<sub>2</sub>. It also indicates large number of defects states.

Therefore, to correctly characterize these defects behavior under stress, it is of great importance to separate contributions from the traps in high  $\kappa$  film and in the interfacial SiO<sub>2</sub> layer. The results will help understanding the origin of these traps and point to the direction of further manufacturing process improvement. Among the very few measurement techniques available to fulfill this goal, the frequency dependent charge pumping (FDCP) is the best.

## 2.4. Frequency Dependent Charge Pumping(FDCP)

Among all the defect characterization methods, charge pumping (CP) technique [60-61] is proved to be the most successful and reliable one, because it is very simple to set up and shows, by far, the highest sensitivity ( $\sim 1 \times 10^9 cm^{-2} eV^{-1}$ ).

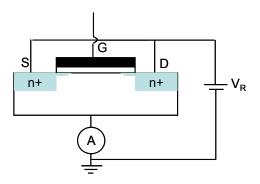

The basic experimental set-up to perform charge pumping measurements, as introduced by Brugler and Jespers [60], is illustrated in Figure 2.7 for the case of an n-channel MOS transistor. The gate of the MOSFET is connected to a pulse generator and a reverse bias is applied to the source and the drain junctions, while the substrate current is measured.

Figure 2.7 Basic experimental setup for charge pumping. Picture is taken from reference 60.

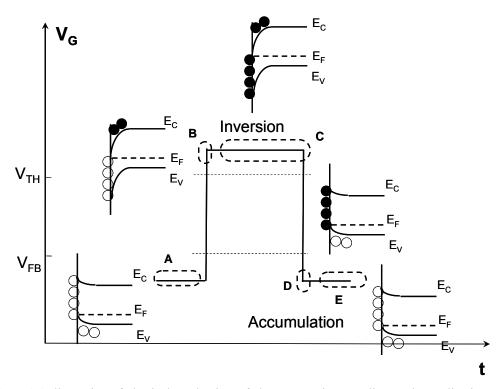

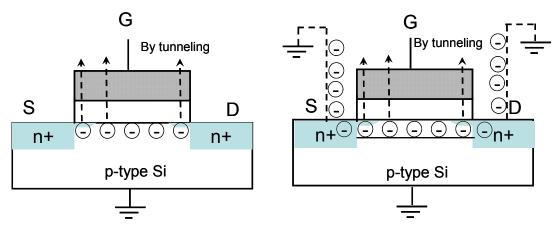

As illustrated in Figure 2.8, the basic idea of the charge pump technique is to rapidly switch a MOSFET from accumulation towards inversion and back forth. When the transistor is pulsed into inversion, electrons originating from the drain and source region get trapped in interface states (region C in figure). As the gate pulse is switched rapidly and drives the surface into accumulation, the mobile charge drifts back to the source and drain under the influence of the reverse bias, but the trapped electrons do not have sufficient time to get detrapped from the interface states (region D in figure). The trapped electrons will recombine with holes originating from the substrate (region E in figure). A similar process holds for the switching from accumulation (from region A to C). In this way, a net amount of charge is transferred ("pumped") from the bulk to the drain and source regions. By repeatedly switching

the gate voltage, a *RMS* average current can be measured at the substrate contact, which is directly proportional to the interface trap density, the transistor gate area, and the frequency of the gate pulses.

Figure 2.8 Illustration of physical mechanism of charge pumping. It relies on the application of a square waveform to the gate of the device which drives the device from accumulation into inversion and back to accumulation again. At region B, the device is just driven into inversion and interface states are still empty. At region C, after very short time of inversion, all the interface states are filled by the electrons from source/drain. At region D, accumulation just started and electrons are still trapped in interface states and have not enough time to escape it out. At region E, after certain time of accumulation, the interface states are emptied by the holes from substrate.. Solid circles represent electrons while empty ones are holes Solid circles in interface states means that they are filled with electrons while empty one means electrons are recombined by the holes. This picture is taken from reference 63.

This conventional charge pumping is mostly used to measure the interface state density. However, for the high  $\kappa$  dielectrics, besides interface states, large numbers of defects are also generated in the bulk of dielectrics. In addition, a lot of traps are also

presented at high  $\kappa$ /SiO<sub>2</sub> interface and bulk buffer SiO<sub>2</sub> because the quality of buffer SiO<sub>2</sub> layer is not so good. These oxide traps locate some distance away from the interface states and communicate with the semiconductor by electron tunneling from inversion layer or filled interface states (Figure 2.8). These slow oxide traps play an important role for the high  $\kappa$  dielectrics reliability such as threshold voltage shifts, mobility, transconductance degradation, bias temperature instability and dielectric breakdown [24]. Thus it becomes a big concern as well as the subject of an increasing interest

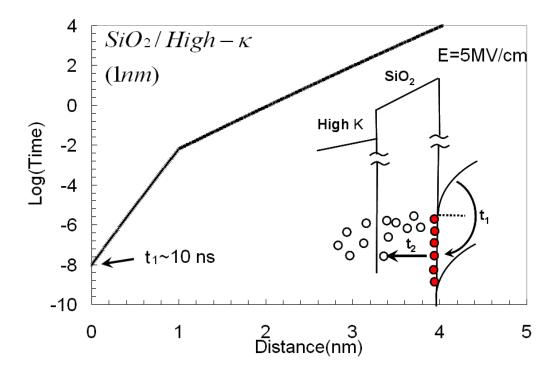

Figure 2.9 Illustration of filling defects in high  $K/SiO_2/Si$  MOS device. A large number of traps are generated in bulk of high K and buffer  $SiO_2$  as well high  $K/SiO_2$  interface. These traps away from interface can be filled by electron tunneling from filled interface states or inversion layer. It takes electrons longer time to tunnel and fill those traps that are far away. Solid circle represents electrons and empty ones are unfilled defects.

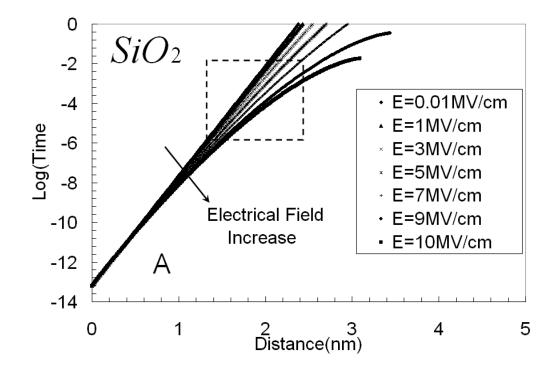

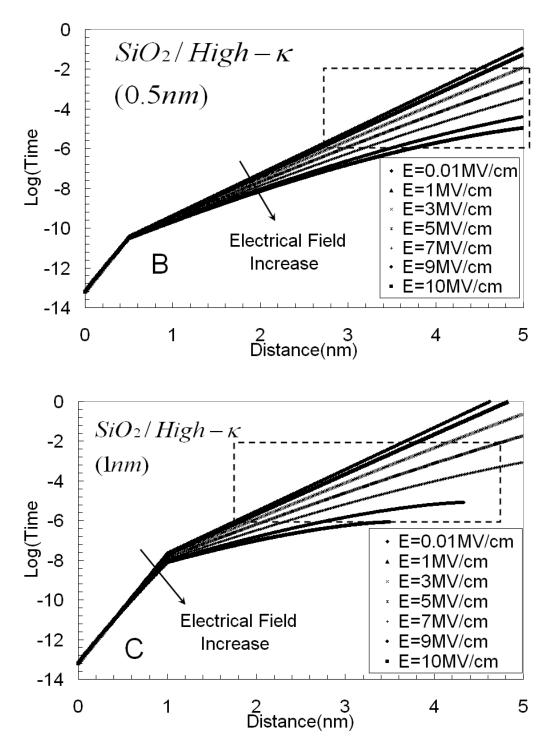

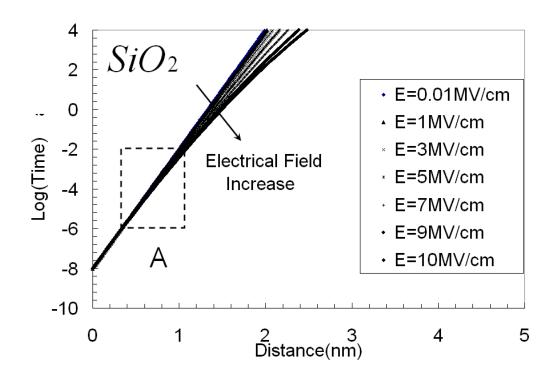

To that end, a new charge pumping technique, based on the evolution of the CP current as a function of frequency, has been developed to address depth profile of the electron traps. It is based on the mechanism that different locations of traps need

different time to fill. The traps locating further away from interface requires more time for electrons/holes to tunnel into and fill them (Figure 2.9). By varying the time allowed for electron tunneling the depth profile of traps can be obtained by detecting the trap density at a given time period. Experimentally, it is implemented by changing the gate square pulse frequency in charge pumping measurement.

When high frequency gate pulse is applied, only the interface traps are able to participate in the charge pumping process since there is insufficient time for electron to tunnel into the oxide traps further away. As the frequency is lowered, the applied gate pulse drives the device into inversion for longer time. Those traps within a tunneling distance appropriate for that particular frequency can also be filled and emptied by the tunneling in and out of electrons from interface states, leading to an increasing charge pumping current per cycle.

This frequency dependent charge-pumping (FDCP) method allows the assessment of spatial distributions of oxide traps. However, although this idea was reported by Declerck *et.al* more than 30 years ago [28], the theory behind it has only been improved recently. The probed depth in the dielectric as a function of CP frequency has become a controversial issue on the recent adaptation to study the defects in high  $\kappa$  gate dielectric stack. For the same experimental data, two different groups come up with two totally different conclusions [28, 29]. Who is right? How exactly deep does charge pumping probe? In chapter 5, we will use both experimental evidence and

theoretical model to answer this important question.

## 2.5. Negative Bias Temperature Instability(NBTI)

Besides the high  $\kappa$  reliability, Negative Bias Temperature Instability (NBTI) is another serious concern and becomes the number one reliability problem nowadays. NBTI is a degradation phenomenon in p-channel MOSFET, known since the late of 1960s on SiO<sub>2</sub> dielectrics. It has been observed that the application of negative gate bias on *p*-channel MOSFET causes instability of device behavior with time, such as an increase in the magnitude of threshold voltage ( $V_T$ ) and a reduction in device driving current ( $I_{DSAT}$ ) [30-32].

The involved physical mechanism is commonly admitted that under a constant gate voltage and an elevated temperature a build-up of positive charges occurs either at the interface Si/SiO2 or in the oxide layer leading to the reduction of MOSFET performances [34-35]. The kinetics of this effect is accelerated by temperature and the oxide electric field.

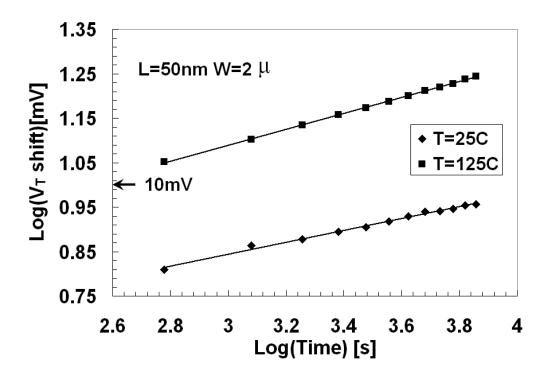

As shown in Figure 2.10, the NBTI induced  $V_T$  shift increases with stress time and could reach the level that hurts the logic function in the long term. Typically, for the modern devices operating at 1.2 V or below,  $V_T$  shifts on the order of 20-50 mV is considered to be very serious. The problem gets worse since this degradation are not uniform for pMOS and nMOS. The name of "negative bias" suggests that it occurs primarily in *p*-channel MOSFETs with negative gate voltage bias and appears to be negligible for positive gate voltage and for either positive or negative gate voltages in *n*-channel MOSFETs. In MOS circuits, it occurs most commonly during the "high" state of *p*-channel MOSFETs inverter operation. As a result, greater  $V_T$  shift in one transistor of a matched CMOS pair can cause functional failure in analog circuits and logic circuits that are sensitive to parameter mismatch.

Figure 2.10 Measured NBTI induced  $V_T$  shift versus time plotted in standard log-log form. The device under test is an advanced MOSFET from 90 nm technology with 2  $\mu$ m channel width and 50 nm physical gate lengths. Two different temperature conditions are used: room temperature (25 C) and elevated temperature (125 C). More VT shift is observed at higher temperature.

Moreover, the degradation is accelerated by temperature. As shown in Figure 2.10,  $V_T$  shift increases at higher temperature. Since most of device operates at elevated temperatures such as 125 C, this temperature dependent reliability issue becomes a

major reliability concern. With the recent relentless technology scaling down of oxide thickness, the concern becomes more serious because the degradation is also well known for its acceleration by increasing electrical field for thinner oxide [34].

In chapter 6, we will report a new mode of NBTI degradation – Ballistic Phonon Enhanced NBTI. It is a new finding and believed to be more serious for future transistors.

# Chapter 3

# **C-V measurement I**

# Capacitance Extraction with Very High Leakage Current using Time Domain Method

In previous chapter, it explains the difficulty in the C-V measurement nowadays. In this chapter, we will solve the problem and present a new C-V technique. The reason to put this as the first of three parts in this thesis is C-V measurement is one of the first electrical tests for a new device. From the measurement, one can find out the equivalent oxide thickness, flat band voltage, substrate doping and so on. It is so basic and widely used that a reliable and accurate technique is demanded. The need becomes more urgent recently because the existing famous method runs into problem.

People have done extensive searching process to find a good candidate [6-19]. However, the result is not satisfactory because of the high standard of the new technique. This new technique must be simple but accurate. In addition, it can also be automated so that it can be integrated into the routine device measurement on the production line. Most important of all, it must have the strong ability to handle the accuracy problem from the leakage current for the advanced MOS device. Moreover, the leakage current will become higher for future device and this new technique should also be able to deal with that. Fortunately, we find a good one and will be shown in this chapter in details. It is time domain reflectrometry(TDR) C-V method. It is based on a well known high frequency measurement technique called TDR with the commercial instrument available. It can provide accurate C-V result even under leakage current as high as 4000 A/cm<sup>2</sup>, which is sufficient enough for at least next few generations of CMOS technology. This method offers a simple and high precision measurement technique and can be automated and implemented as a routine device characterization procedure.

#### **3.1. Basic Principle**

The basic principle of the new technique could be viewed as a step function with very fast rise time propagating down a transmission line. Upon encountering a capacitor, part of the power passes through but most of it is reflected. The shape of the reflected step function, intuitively, must contain information about the capacitor. Naturally, one cannot recover the full information of the capacitor without a proper reference. However, once a well designed reference is available, this method allows an accurate description of the capacitor. The idea of sending step voltage and measuring the reflected voltage is so called Time domain reflectrometry(TDR).

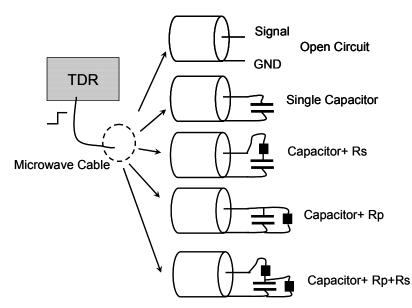

The step function generated by the TDR scope is very fast with 35ps rise time. It reached the device (capacitor) under test (DUT) through a bias-TEE (for DC bias) and a transmission line. Due to impedance mismatch between the transmission line and the capacitor, the step function is reflected back toward the scope which records it. By

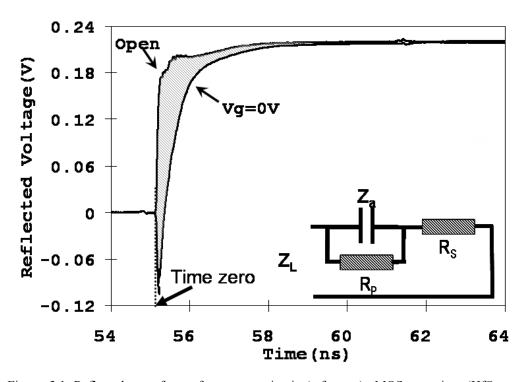

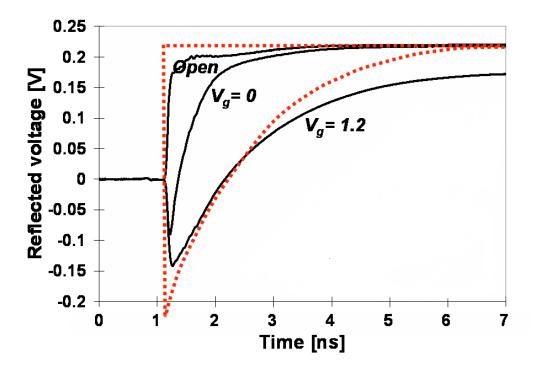

studying the reflected voltage waveform, much information can be obtained on the nature of the load. Of course, a reference is necessary and chosen to be an open circuit (let the probe floating). Figure 3.1 shows the reflected waveforms from an open circuit reference, a MOS capacitor in depletion. For detail description and explanation of TDR theory, please refer to Appendix A.

Figure 3.1 Reflected waveforms from open circuit (reference), MOS capacitor (HfO<sub>2</sub> gate dielectrics with EOT 1.2nm) at depletion ( $V_G = 0$ V). The shaded area represents the total stored charge in the depletion case. The insert is the equivalent circuit of the capacitor with thin oxide.

At any instant in time, the reflection coefficient is determined by the impedance mismatch:

$$\rho = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{3.1}$$

Where  $Z_0$  is the impedance of the transmission line which is typically 50  $\Omega$  in high-speed measurements;  $Z_L$  is the impedance of the DUT. For an open circuit,  $Z_L$

$=\infty$  and the reflection coefficient is 1. For the MOS capacitor, the equivalent circuit is in the insert of Figure 3.1. The impedance of a capacitor is a short circuit when the step function first arrives. As the capacitor charges up, it eventually becomes an open circuit. For the depletion case ( $V_g = 0V$ ), leakage current is negligible and  $R_P$  can be removed from the equivalent circuit. At the end of charging, the signal reaches the same level as open circuit.

The charging behavior of the capacitor is a measure of the stored charge in the capacitor. Intuitively, the area enclosed (shaded area) by the open circuit waveform and the capacitor charging waveform represents the total stored charge at the end of the voltage step. Mathematically, it can be vigorously shown that

$$C = \frac{1}{2Z_0 V_{step}} \int_0^\infty \left( V_{Open}(t) - V_{DUT}(t) \right) dt$$

(3.2)

Where  $V_{Open}(t)$  is the open circuit waveform;  $V_{DUT}(t)$  is the waveform from the DUT (the capacitor) and  $V_{Step}$  is the height of the step function. The detail derivation of equation (3.2) is shown in Appendix B. The integral represents the enclosed area of the two waveforms which is in agreement with our intuition. With Equation (3.2), capacitance can be obtained by measuring the reflected waveform of the capacitor and the open circuit. Following this principle, we implement it experimentally and here are the basic procedures as well as setups.

# 3.2. Experimental Setup and Test Structure

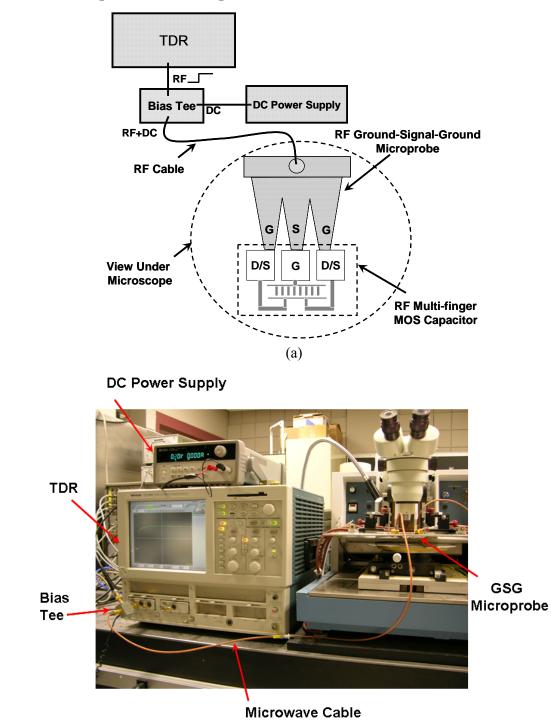

Figure 3.2(a) Basic illustration of building block of experimental setup in TDR based C-V measurement. (b) Picture of actual instruments and connections

Figure 3.2(a), (b) illustrates the block diagram and actual picture of experimental

setup for MOS capacitor C-V measurement using the TDR. A TDR scope which in our case is a Tektronix CSA8000 scope with 80E04 plug-in module is connected to the device-under-test (DUT) which is a RF-compatible MOS capacitor [14,16] through a Bias-TEE (Mini Circuit), a microwave cable and a microwave Ground-Signal-Ground probe (Cascade probe). A fast rise time (~35ps) step function with magnitude around 220mV is generated from the scope and reflection under different DC bias condition is recorded.

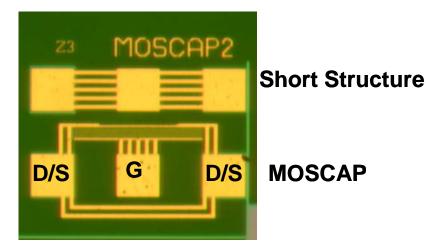

Figure 3.3 Picture of MOSCAP test structure, showing ground-signal-ground pads. It is taken under high magnification microscope

Our p-type substrate MOS capacitor test structure is supplied by the Sematech International Corp. Two wafers with same test structure but different type of gate dielectrics are used in this measurement. One is 2nm pure  $SiO_2$  while the other is HfO<sub>2</sub> with 1.2 nm EOT HfO<sub>2</sub> (~1nm buffer SiO<sub>2</sub>). This test structure is well designed. In this design, a large number of small capacitor elements are imbedded in a sea of highly doped material to lower the series resistance. The picture of a test structure taken under high magnification microscope is shown in Figure 3.3. The contact pad on the top surface at the wafer level is designed to permit one to use ground-signal-ground probe connection for high frequency measurement. Due to the physical limitation of device geometry associated with the process technology, the active area of the test structure is significantly distorted resulting in effective area around 1400  $\mu$ m<sup>2</sup> [14]. Moreover, short circuit calibration structures are also fabricated on the same wafer.

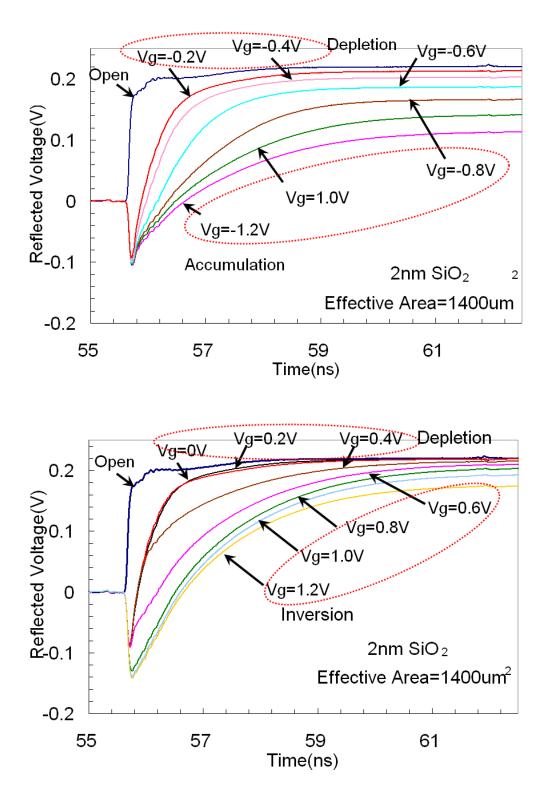

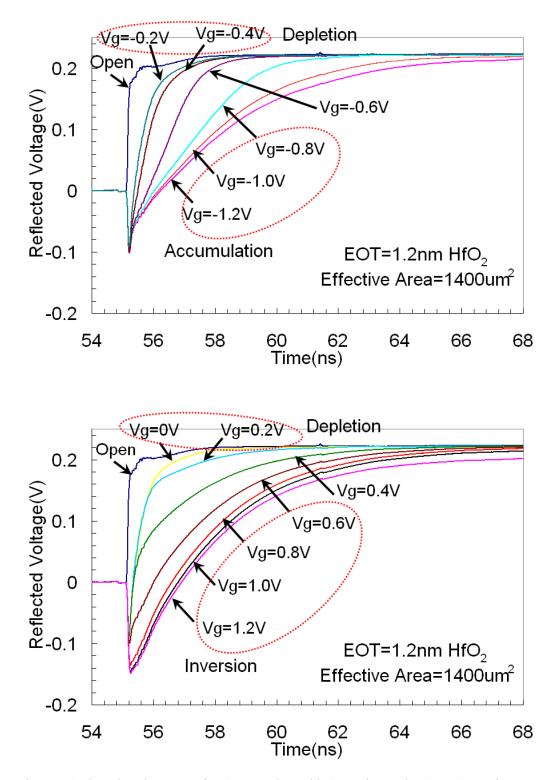

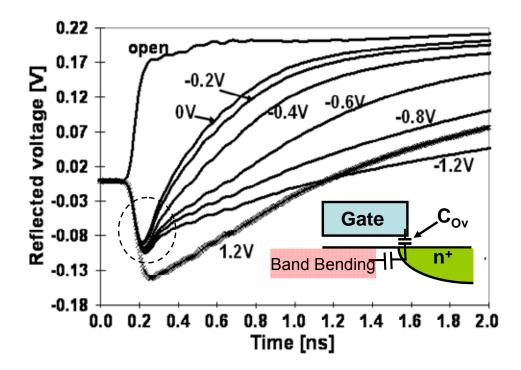

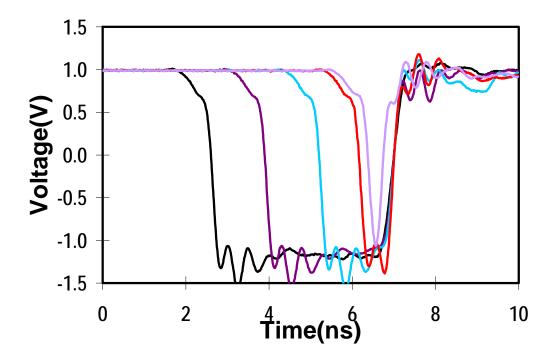

#### **3.3.** Time Domain Response of Leaky MOS Capacitor

With the above setup and test structure, we obtained the reflected voltage of this MOS capacitor under different gate bias ranging from -1.2V to 1.2V as shown in Figure 3.4. Under this range of gate bias, this capacitor operates under accumulation, depletion and strong inversion respectively. As it can be seen in Figure 3.4, the basic shape drops down initially and rises up to final steady state. It is because the impedance of a capacitor initially behaves as a short circuit when the step function first arrives. And it eventually becomes an open circuit as the capacitor charges up.

Moreover, in some bias condition (such as  $V_G$ =1.2V and -1.2V), the steady state of capacitor does not reach the same level of the open circuit. In Figure 3.4, it can be also seen that the final state of capacitor at some gate bias when it finished the charging has the voltage level less than open circuit. That is because the test structure used in this experiment is thin oxide device with pretty large leakage current when applied voltage is high.

Figure 3.4 Time domain curve of MOS capacitor with  $2nm SiO_2$  and EOT 1.2nm HfO<sub>2</sub> gate dielectrics. Positive and negative gate voltage cases are plotted in a separated way.

As a result, some charges get lost through leakage current and lead to lower final

voltage even though the capacitor is fully charged up. The higher leakage current, the more charges are lost resulting in lower final voltage level. Since the leakage current in MOS capacitor is gate bias-dependent, the similar trend can also be observed in the final voltage of TDR reflected waveforms (Figure 3.4). From that, we can even extract the leakage current and shunt resistance. The results are shown in Figure 3.5.

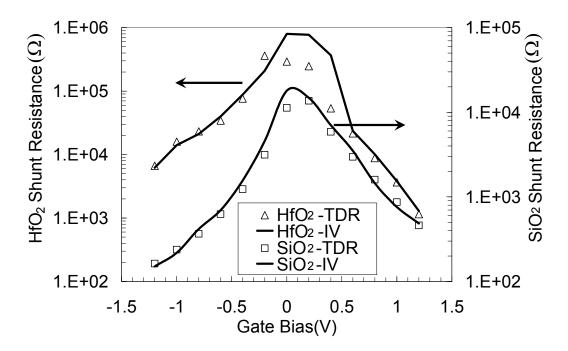

Figure 3.5 Comparison of shunt resistance obtained by new TDR method and traditional current voltage (I-V) measurement. The higher shunt resistance, the capacitor reaches close to open circuit at final steady state. As a result, the small noise causes deviation in extraction under high shunt resistance.

When the capacitor is fully charged, the impedance is  $Z_L = R_P + R_S$ . After we subtract the series resistance with the method that will be introduced in the chapter 4, we can obtain the extracted shunt resistance. Leakage current can also be obtained precisely with DC current-voltage measurement using the HP 4156A as shown in Figure 3.6. Figure 3.5 indicates that the shunt resistance extracted from both methods is basically consistent under high leakage current (low shunt resistance). For low leakage case, the final steady voltage of reflection waveform is so close to open circuit that noise hurts the accuracy of extraction.

Figure 3.6 Leakage current as function of gate voltage is measured by HP 4156A. With the substrate/source/drain all grounded, gate current is obtained with the sweep of gate voltage. 2nm  $SiO_2$  and EOT 1.2 nm HfO<sub>2</sub> MOS capacitor is measured respectively. After dividing the effective area 1400  $\mu$ m<sup>2</sup>, the current density is obtained.

## 3.4. Correction for Leakage Current

As shown in the Figure 3.4, for the MOS capacitor at inversion and accumulation, very high level of leakage current exists as the oxide is extremely thin. This is the source that lets the conventional method fail. In our new method, how could we deal with this problem?

It is found that this leakage current lowers the stored charge in the capacitor and manifests itself in time domain response as the shrink of enclosed area between the reflected waveform of the capacitor and open circuit. As a result, a correction procedure is required to account for that. In this case, the impedance  $Z_L$  when the capacitor is fully charge is equal to  $R_P + R_S = R_0$ . Since  $R_0$  is not very large, the reflection coefficient is much less than 1 and the charging curve never reaches the open circuit level. It can be shown that in this case, the capacitance is given by Equation (3.3) as following:

$$C = \frac{1}{2Z_0 V_{step}} M \int_0^\infty \left[ \left( \frac{R_0 - Z_0}{R_0 + Z_0} \right) V_{Open}(t) - V_{DUT}(t) \right] dt$$

(3.3)

where  $M = \frac{(R_0 + Z_0)^2}{R_p^2}$

This equation suggests that we can normalize the final level of the open circuit waveform to the final level of the reflected waveform from the capacitor. And then the capacitance can be extracted by integrating the enclosed area.

Figure 3.7 illustrate this normalization of the open circuit waveform and the resulting area enclosed. The enclosed area is obviously smaller than that of a leak-free capacitor. As shown in equation (3.3), the pre-integral factor M re-scales the enclosed area back to the actual area that would have been observed if there was no leakage current. Equation (3.3) can also be proved by the transmission theory and detail derivation can be referred in Appendix B.

Figure 3.7 The reference waveform is normalized so that the final voltage level is scaled down to the final level of the leaky capacitor. The shaded area enclosed by the normalized reference and the leaky capacitor is the total stored charge in the leaky capacitor scaled down by a factor  $M = \frac{(R_0 + Z_0)^2}{R_p^2}$ .

# **3.5.** Correction for Series Resistance

Besides the leakage current, series resistance is another source hurts the accuracy of C-V measurement. This can be easily avoided because our new method provides self-correction for series resistance, that is, no additional correction procedure is necessary. In the insert of Figure 3.1, we see that the series resistance  $R_S$  included in the equivalent circuit does not appear in equation (3.1). This can be understood by realizing that  $R_S$  not only slows down the charging process, but also modifies the effective impedance and therefore the reflected waveform's amplitude at every point

in time. This preserves the enclosed area which accounts for the change in stored charges due to the step voltage. This argument can also be proved mathematically as shown in Appendix B.

From the final voltage level of the reflected waveform, we can use equation (3.1) to calculate the value of  $R_0$ . To find  $R_P$ , we need to determine  $R_S$ . To do that, we note that at time zero the capacitor is a short circuit. The impedance at this point is simply  $R_{s}$ . If we have a perfect step function, then the reflection coefficient at time zero will give us  $R_S$  directly. In real situations, accurate extraction of  $R_S$  is still possible because the step function is accurately known from the open circuit waveform and the theoretical shape of the time dependent reflectivity curve is also known. The reflectivity curve can be recovered by fitting the experimental reflectivity data to the theoretical expression. The reflectivity at time zero can then be extracted by extrapolation. The procedure is straight forward but a number of potential error sources must be carefully dealt with. In chapter 4, we will demonstrate the exact procedure of implementing this idea to extract the series resistance. Here in a simple manner, we first show the C-V measurement without additional extraction of series resistance. More accurate but complicate C-V method taking account of series resistance as well as overlap capacitance will be shown in chapter 4.

When  $R_P >> R_S$ , the pre-integral fact *M* can be approximated as

$$M = \frac{\left(R_0 + Z_0\right)^2}{R_0^2}$$

(3.4)

By doing so we need not go through the trouble of extracting  $R_s$  and the TDR method becomes extremely simple. The resulting capacitance is an under estimation of the real value. Figure 3.8 shows the percent error as a function of  $R_s$  to  $R_P$  ratio. Typical  $R_s$  values are in the tens of Ohms.  $R_P$  needs to be at least 200 times larger for 1% accuracy. The approximation can be satisfied for most capacitors except for those with extremely high leakage.

Figure 3.8 The plot of the percent underestimation of the capacitance when using equation (3.4) to approximate the pre-integral factor M as a function of the  $R_S$  to  $R_P$  ratio.

Figure 3.8 also serves to indicate how accurate  $R_S$  needs to be measured. If one replaces  $R_S$  with  $\Delta R_S$  in the ratio (horizontal axis), the result is basically unchanged. Thus if we want 1% accuracy, then the  $\Delta R_S$  to  $R_P$  ratio need to be less than 0.005. Since  $R_S$  is typically much smaller than  $R_P$  to begin with, even a rough estimate of  $R_S$ is enough to achieve high accuracy using equation (3.3). For example, if  $R_S = 10\Omega$ , then 1% accuracy in CV measurement can be achieved with  $R_P$  as small as 20 $\Omega$ , which is 4000A/cm<sup>2</sup> for our 1400  $\mu$ m<sup>2</sup> capacitors.

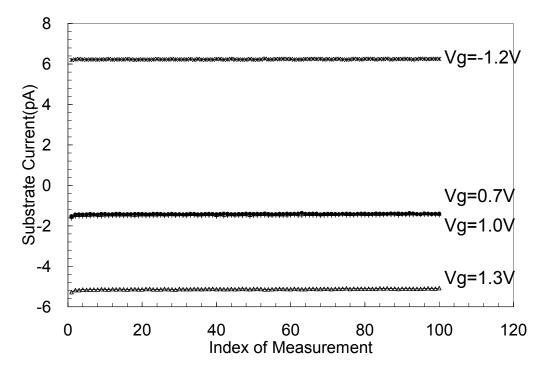

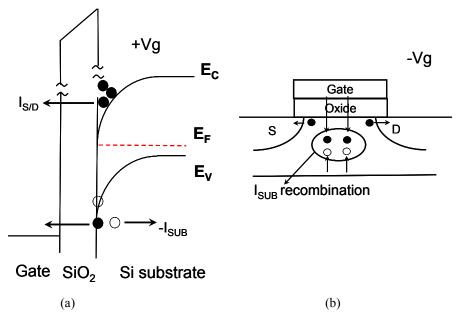

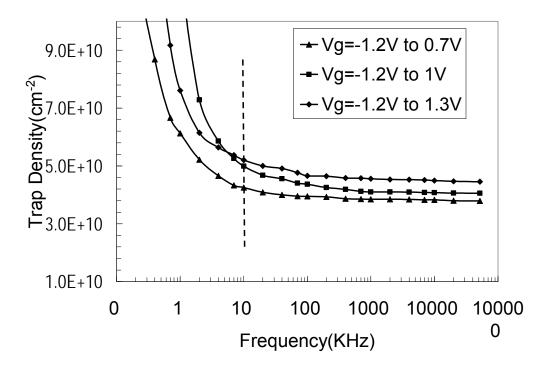

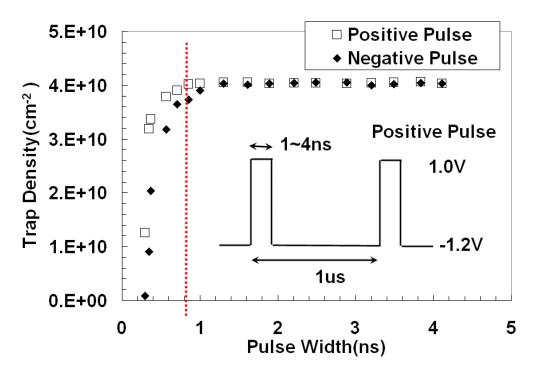

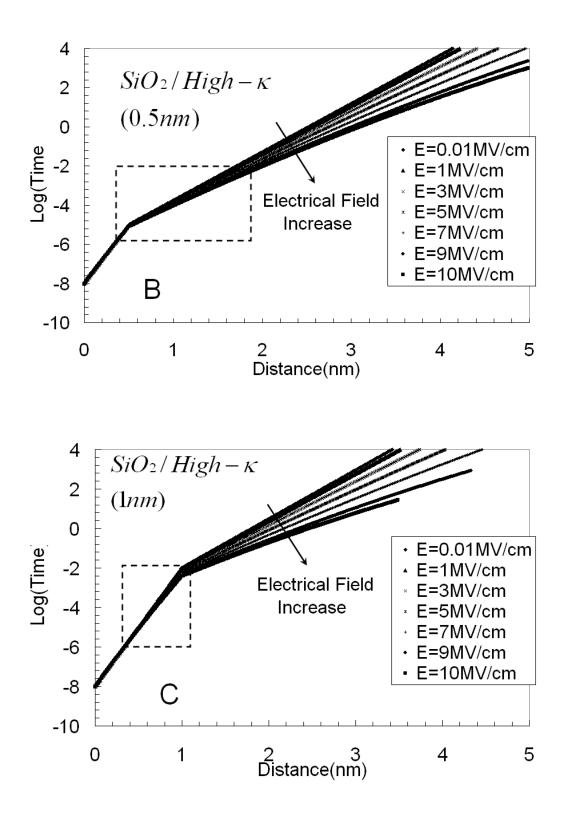

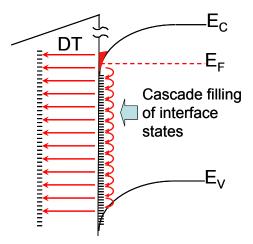

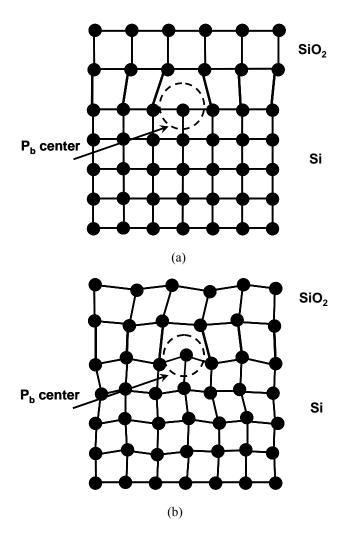

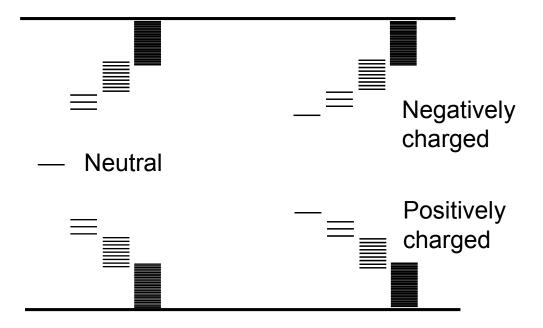

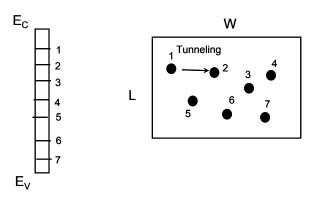

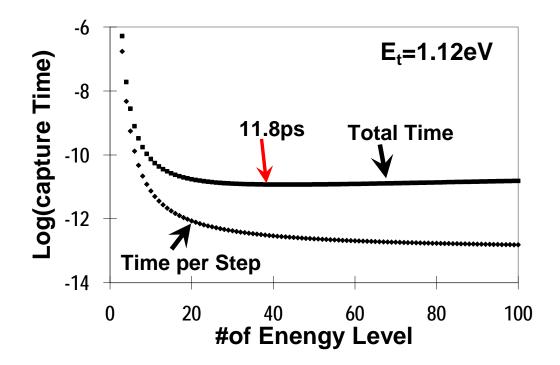

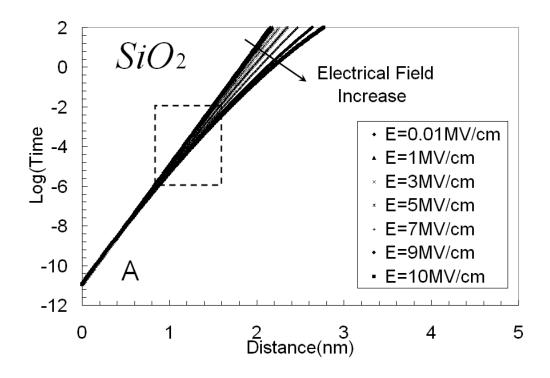

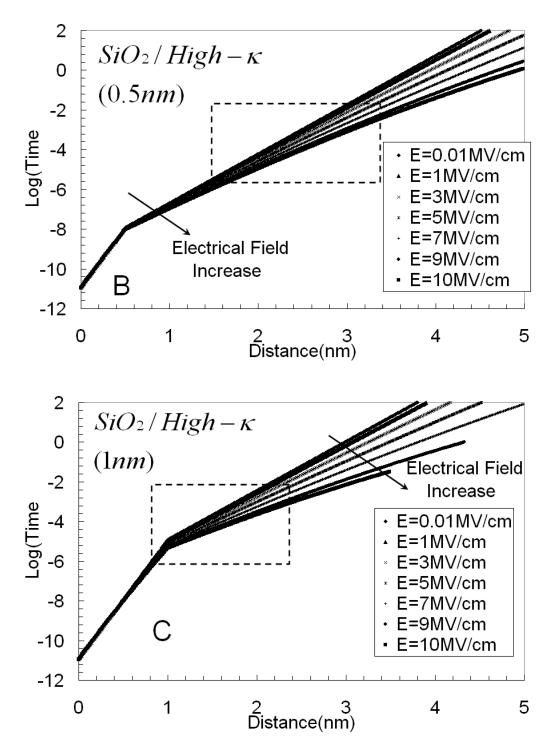

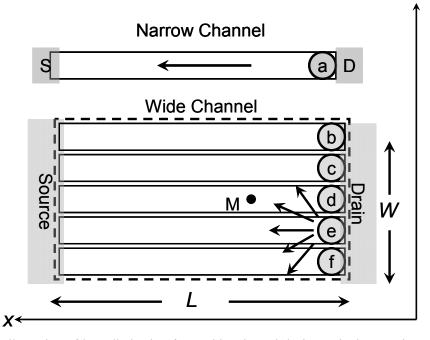

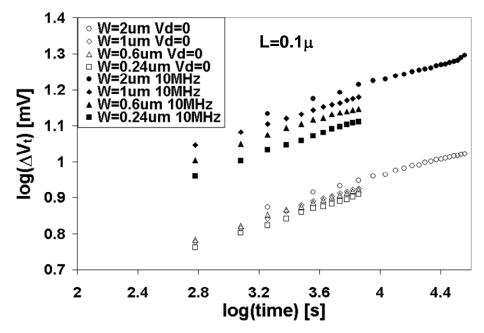

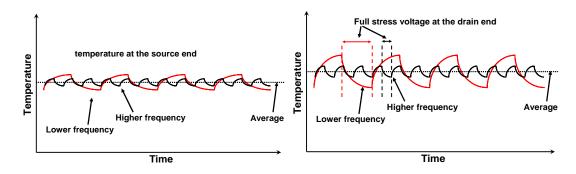

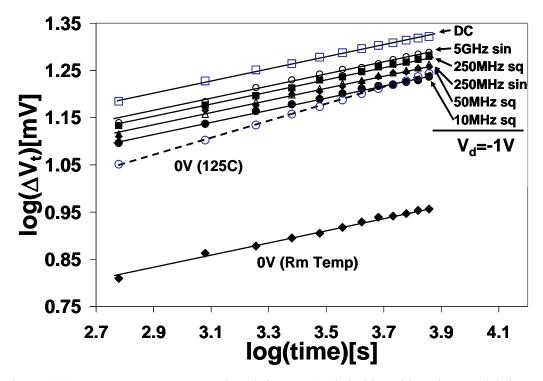

## 3.6. Extracted C-V Characteristics