# JITTER REDUCTION CIRCUITS TO REDUCE THE BIT-ERROR RATE OF HIGH-SPEED SERIALIZER-DESERIALIZER (SERDES) CIRCUITS

## BY HARI VIJAY VENKATANARAYANAN

A dissertation submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Doctor of Philosophy Graduate Program in Electrical and Computer Engineering Written under the direction of Prof. Michael L. Bushnell and approved by

> New Brunswick, New Jersey January, 2008

### ABSTRACT OF THE DISSERTATION

# Jitter Reduction Circuits to Reduce the Bit-Error Rate of High-Speed Serializer-Deserializer (SERDES) Circuits

# by Hari Vijay Venkatanarayanan Dissertation Director: Prof. Michael L. Bushnell

A new jitter reduction technique is proposed for reducing the timing jitter in a serializer-deserializer (SERDES) circuit. The technique involves transmit and receive side jitter reducer circuits made of only 14 and 20 transistors, respectively. They reduce the jitter in the clock generated by the phase-locked-loop (PLL) at the transmit side, and the jitter between the recovered clock and the serial data at the receive side. The jitter reducers are designed using 70 nm Berkeley Predictive process models and tested with various types of input jitter. In the case of the transmit side jitter reducer, the jitter is reduced, on average, by 62.24%. The performance of the jitter reducer is compared with the adaptive PLL technique proposed by Xia *et al.* [39] in terms of the peak-to-peak jitter reduction. The peak-to-peak jitter is reduced, on average, by 45.51% using the transmit side jitter reducer. For the receive side jitter reducer, the jitter is reduced, on average, by 35.88%. The SERDES circuit is then tested for its jitter performance under three conditions: (1) no jitter reducers are present, (2) the receive side jitter reducer is present and (3) both transmit and receive side jitter reducers are present. In each of these cases, the *bit-error rate* (BER) is computed probabilistically and is shown to improve from  $8.3 \times 10^{-2}$  to  $6.44 \times 10^{-20}$ , for input RMS *periodic jitter* (PJ) of 71.77 ps. Finally, a SERDES test scheme is used to test the jitter reducers for their stuck-at faults and then to perform the receiver jitter tolerance and BER tests.

## Acknowledgements

I am grateful to Prof. Michael L. Bushnell for taking me as his student and for guiding me in my endeavors. I am thankful to him for his support in the successful completion of my doctoral research. In my six years as a graduate student, I was able to hone my skills through his mentorship, and finally, I would like to thank him for providing me the financial support that helped me in concentrating on my research.

I would like to thank my sister Sunitha and my brother-in-law Karthik for providing me moral support and also my friends: Giri, Ashok, Bharath, Rajamani, Omar, Krishna and Karthikeya. I would also like to thank my fellow lab mates: Baozhen, Roy, Aditya, Sharanya, Raghuveer and Shiva for providing a healthy environment for research.

I would also like to thank Dr. Tapan J. Chakraborty for providing valuable advice for my doctoral research. Last but not the least, I would like to thank the CAIP staff members for providing support in running the various tools in our laboratory.

# Dedication

To my parents, sister, brother, niece and friends

# Table of Contents

| $\mathbf{A}$ | bstra | ct     |                                                                                                         | ii  |

|--------------|-------|--------|---------------------------------------------------------------------------------------------------------|-----|

| A            | cknov | wledge | ments                                                                                                   | iv  |

| D            | edica | tion . |                                                                                                         | V   |

| Li           | st of | Tables | 5                                                                                                       | xi  |

| Li           | st of | Figure | es                                                                                                      | xii |

| 1.           | Intr  | oducti | on                                                                                                      | 1   |

|              | 1.1.  | Motiva | ation                                                                                                   | 3   |

|              |       | 1.1.1. | Problems with SERDES                                                                                    | 3   |

|              |       | 1.1.2. | Problems with PLL Circuit in Microprocessors and Wireless                                               |     |

|              |       |        | Transceivers                                                                                            | 4   |

|              |       | 1.1.3. | Why Do We Need a New Jitter Reduction Technique?                                                        | 4   |

|              | 1.2.  | Proble | em Statement                                                                                            | 4   |

|              | 1.3.  | Origin | al Contribution of the Dissertation                                                                     | 5   |

|              | 1.4.  | Summ   | ary of Results                                                                                          | 5   |

|              | 1.5.  | Organ  | ization of the Dissertation                                                                             | 5   |

| 2.           | Con   | cepts  | on Serializer-Deserializer (SERDES) and Phase-Locked                                                    |     |

| Lo           | oop ( | PLL)   | Circuits and Timed Boolean Functions                                                                    | 6   |

|              | 2.1.  | SERD   | $ES - Introduction \dots \dots$ | 6   |

|              | 2.2.  | SERD   | ES Architecture                                                                                         | 7   |

|              |       | 2.2.1. | Transmit Section                                                                                        | 9   |

|              |       | 2.2.2. | Receive Section                                                                                         | 11  |

|    | 2.3.  | SERD   | ES Design Features                                                | 11 |

|----|-------|--------|-------------------------------------------------------------------|----|

|    |       | 2.3.1. | Jitter Performance                                                | 11 |

|    |       | 2.3.2. | Power and Area                                                    | 12 |

|    |       | 2.3.3. | SERDES Test                                                       | 13 |

|    | 2.4.  | Phase- | -Locked Loop – Introduction                                       | 13 |

|    |       | 2.4.1. | Operation of PLL Circuit                                          | 15 |

|    |       |        | 2.4.1.1. Analysis of PLL Circuit in Locked Condition $\therefore$ | 16 |

|    | 2.5.  | Buildi | ng Blocks of PLL Circuit                                          | 18 |

|    |       | 2.5.1. | Phase/Frequency Detector and Charge Pump                          | 18 |

|    |       | 2.5.2. | Gilbert Cell as Phase Detector                                    | 19 |

|    |       | 2.5.3. | Voltage Controlled Oscillator                                     | 21 |

|    |       |        | 2.5.3.1.~ LC Cross Coupled Voltage Controlled Oscillator .        | 21 |

|    | 2.6.  | Delay- | Locked Loop                                                       | 22 |

|    | 2.7.  | Timed  | l Boolean Functions – Introduction                                | 24 |

|    |       | 2.7.1. | Modeling Timing Behaviors                                         | 26 |

|    |       | 2.7.2. | Circuit Formulation                                               | 27 |

|    | 2.8.  | Summ   | ary                                                               | 28 |

| 3. | Jitte | er Fun | damentals – Reduction and Testing                                 | 29 |

|    | 3.1.  | Jitter | Fundamentals                                                      | 29 |

|    |       | 3.1.1. | Random Jitter                                                     | 31 |

|    |       | 3.1.2. | Deterministic Jitter                                              | 32 |

|    |       |        | 3.1.2.1. Duty-cycle Distortion (DCD) Model                        | 33 |

|    |       |        | 3.1.2.2. Periodic Jitter (PJ) Model                               | 33 |

|    |       | 3.1.3. | Eye Diagram                                                       | 34 |

|    |       | 3.1.4. | Bit-Error-Rate (BER)                                              | 34 |

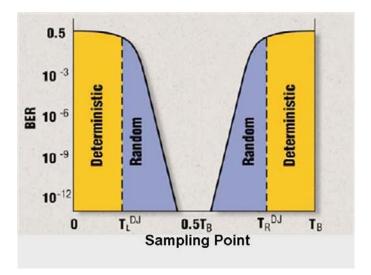

|    |       | 3.1.5. | Bath Tub Curve                                                    | 35 |

|    |       | 3.1.6. | Jitter Tolerance and Jitter Transfer                              | 37 |

|    | 3.2.  | PLL J  | itter Reduction Techniques                                        | 37 |

|    |      | 3.2.1.       | Phase-L    | ocked Loop Architecture for Adaptive Jitter Opti-     |          |

|----|------|--------------|------------|-------------------------------------------------------|----------|

|    |      |              | mization   | 1                                                     | 37       |

|    |      | 3.2.2.       | Jitter M   | inimization in Digital Transmission Using Dual Phase- |          |

|    |      |              | Locked 1   | Loops                                                 | 39       |

|    |      | 3.2.3.       | A Low J    | itter Phase-Locked Loop Based on a New Adaptive       |          |

|    |      |              | Bandwic    | lth Controller                                        | 41       |

|    |      | 3.2.4.       | Other Ji   | tter Reduction Techniques                             | 42       |

|    | 3.3. | Variou       | ıs Test Te | echniques for SERDES and Jitter                       | 43       |

|    |      | 3.3.1.       | Jitter Te  | est with External Test Equipment                      | 43       |

|    |      |              | 3.3.1.1.   | BER Estimation for Serial Links Based on Jitter       |          |

|    |      |              |            | Spectrum and Clock Recovery Characteristics           | 43       |

|    |      |              | 3.3.1.2.   | Extraction of Peak-to-Peak and RMS Sinusoidal         |          |

|    |      |              |            | Jitter Using an Analytic Signal Method                | 46       |

|    |      |              | 3.3.1.3.   | Jitter Spectral Extraction for Multi-Gigahertz Sig-   |          |

|    |      |              |            | nal                                                   | 48       |

|    |      | 3.3.2.       | Jitter B   | IST                                                   | 50       |

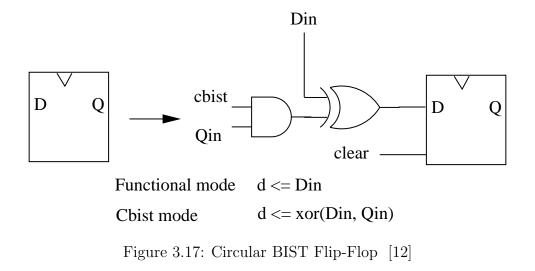

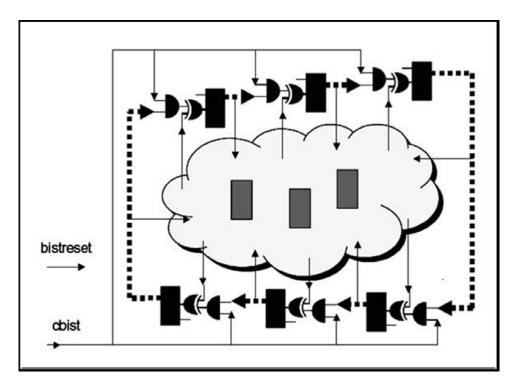

|    |      |              | 3.3.2.1.   | Circular BIST Testing the Digital Logic within a      |          |

|    |      |              |            | High Speed SERDES                                     | 50       |

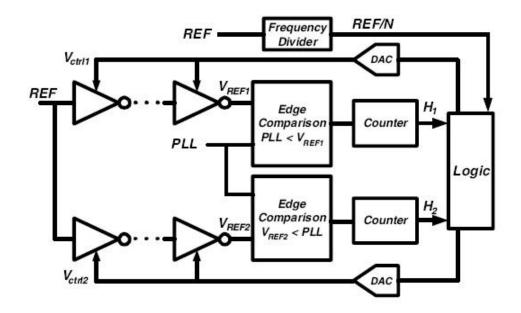

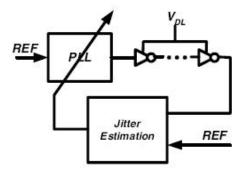

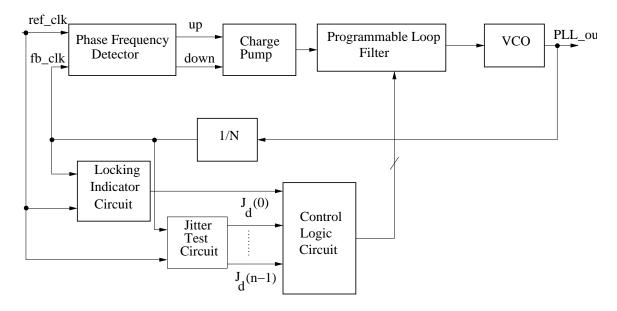

|    |      |              | 3.3.2.2.   | Automated Calibration of Phase Locked Loop with       |          |

|    |      |              |            | On-Chip Jitter Test                                   | 53       |

|    |      |              | 3.3.2.3.   | On-Chip Jitter Measurement Using a Dual-Channel       |          |

|    |      |              |            | Undersampling Time Digitizer                          | 54       |

|    |      | 3.3.3.       | Other S    | ERDES and Jitter Test Solutions                       | 55       |

|    |      | 3.3.4.       | Summar     | у                                                     | 56       |

| 4  | NT   | <b>T</b> •44 | . D. J     |                                                       | - 7      |

| 4. |      |              |            | tion Technique                                        | 57       |

|    | 4.1. |              |            | n Technique for the Transmit Side Phase-Locked        | ξO       |

|    |      | -            |            |                                                       | 58<br>60 |

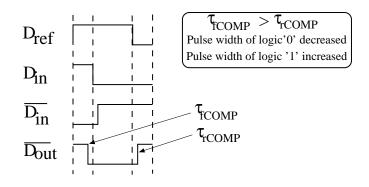

|    |      | 4.1.1.       | Process    | of Jitter Reduction                                   | 60       |

|    |      | 4.1.2. Mathematical Theory with Examples 6                                                                              | 60 |

|----|------|-------------------------------------------------------------------------------------------------------------------------|----|

|    |      | 4.1.3. Architecture of Jitter Reduction Circuit 6                                                                       | 3  |

|    |      | $4.1.3.1. Inversion \dots 6$                                                                                            | 64 |

|    |      | 4.1.3.2. Jitter Reduction $\ldots \ldots $ | 68 |

|    |      | 4.1.3.3. Reference Signal Generation                                                                                    | '3 |

|    |      | 4.1.4. Optimized Jitter Reduction Circuit                                                                               | '3 |

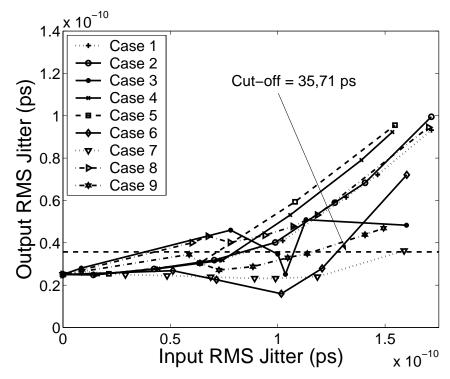

|    | 4.2. | Results for Transmit Side Jitter Reducer                                                                                | 82 |

|    |      | 4.2.1. Testing the Tx Jitter Reducer with Input Jitter 8                                                                | 82 |

|    |      | 4.2.1.1. Analysis                                                                                                       | 33 |

|    |      | 4.2.2. Comparison with Adaptive PLL Technique                                                                           | 36 |

|    |      | 4.2.3. Phase Delay Introduced by the Jitter Reducer Circuit –                                                           |    |

|    |      | Compensation                                                                                                            | 87 |

|    | 4.3. | Summary                                                                                                                 | 88 |

| 5. | SEF  | DES with Transmit and Receive Side Jitter Reducers 8                                                                    | 39 |

|    | 5.1. | Jitter Reduction Technique for the Receive Side Clock and Data                                                          |    |

|    |      | Recovery Circuits                                                                                                       | 39 |

|    |      | 5.1.1. Problem with the Clock and Data Recovery Circuit 9                                                               | 0  |

|    |      | 5.1.2. Process of Jitter Reduction and Jitter Reduction Circuit . 9                                                     | 90 |

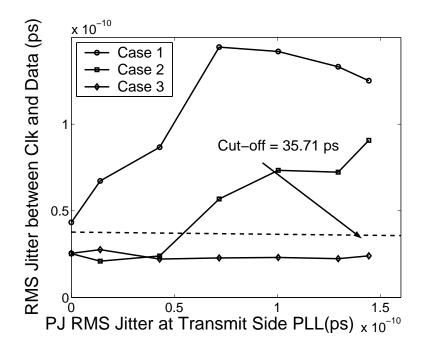

|    | 5.2. | Results for Receive Side Jitter Reducer                                                                                 | )6 |

|    |      | 5.2.1. Analysis                                                                                                         | )6 |

|    | 5.3. | Jitter Performance of SERDES with Tx and Rx Jitter Reducers $.$ 9                                                       | 9  |

|    |      | 5.3.1. BER Analysis                                                                                                     | 9  |

|    | 5.4. | Summary                                                                                                                 | )1 |

| 6. | Circ | uit Design Issues and Testing                                                                                           | )2 |

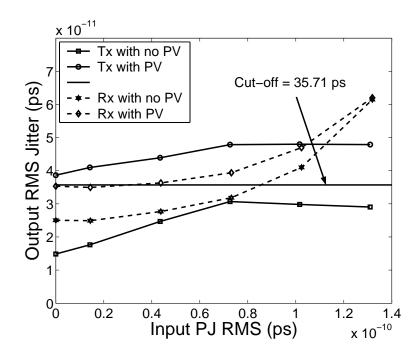

|    | 6.1. | Monte Carlo Analysis and Process Variation Parameters 10                                                                | 12 |

|    | 6.2. | Conditions on the Timing Delays Due to Process Variations $\ldots$ 10                                                   | )3 |

|    | 6.3. | Optimal Transistor Width                                                                                                | 14 |

|    | 6.4. | Tx and Rx Jitter Reducers under Process Variations 10                                                                   | )4 |

| 6.5. Layout and Parasitics $\ldots \ldots 1$    | .05 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6. Pole-Zero Analysis                                                                                                                    | .07 |

| 6.7. Phase Noise Analysis                                                                                                                  | .20 |

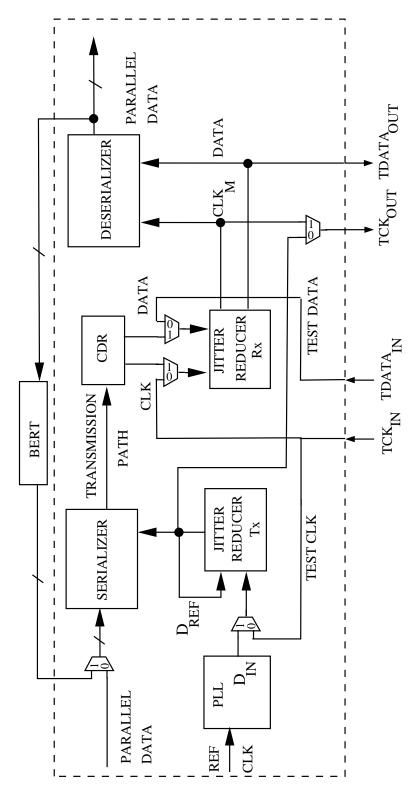

| 6.8. Test Architecture for SERDES                                                                                                          | .21 |

| 6.8.1. Testing the Tx and Rx Jitter Reducers                                                                                               | .21 |

| 6.8.2. Receiver Jitter Tolerance Test                                                                                                      | .28 |

| 6.8.3. Probabilistic BER Test                                                                                                              | .28 |

| 6.9. Summary                                                                                                                               | .29 |

| 7. Conclusion and Future Work                                                                                                              | .30 |

| 7.1. Conclusion $\ldots \ldots 1$ | .30 |

| 7.1.1. Applications $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                            | .32 |

| 7.2. Future Work                                                                                                                           | .33 |

| 7.2.1. Jitter Testing $\ldots \ldots 1$                       | .33 |

| Appendix A. User's Guide                                                                                                                   | .35 |

| A.1. Circuit Design                                                                                                                        | 35  |

| A.2. Circuit Testing 1                                                                                                                     | 35  |

| References                                                                                                                                 | .37 |

| Vita                                                                                                                                       | 41  |

# List of Tables

| 4.1. | W/L Ratios of All the Transistors in the Optimized Jitter Reduc-     |     |

|------|----------------------------------------------------------------------|-----|

|      | tion Circuit                                                         | 81  |

| 4.2. | Input Jitter Types for Tx Jitter Reducer                             | 82  |

| 4.3. | Peak-to-Peak Jitter Reduction by the New and Adaptive PLL            |     |

|      | Techniques $[39]$                                                    | 86  |

| 5.1. | $W\!/L$ Ratios of All the Transistors in the Receive Side Jitter Re- |     |

|      | duction Circuit                                                      | 94  |

| 5.2. | Input Jitter Types for Rx Jitter Reducer                             | 95  |

| 5.3. | Three Cases of SERDES Jitter Reducers                                | 99  |

| 6.1. | Optimal Transistor Width                                             | 104 |

| 6.2. | Transmit Side PLL without Tx Jitter Reducer – Values of Poles        |     |

|      | and Zeros                                                            | 107 |

| 6.3. | Transmit Side PLL with Tx Jitter Reducer – Values of Poles and       |     |

|      | Zeros                                                                | 113 |

| 6.4. | Receive Side PLL without Rx Jitter Reducer – Values of Poles and     |     |

|      | Zeros                                                                | 116 |

| 6.5. | Receive Side PLL with Rx Jitter Reducer – Values of Poles and        |     |

|      | Zeros                                                                | 117 |

| 6.6. | Transistor Fault Testing for the Tx and Rx Jitter Reducers           | 127 |

# List of Figures

| 1.1. SERDES Block Diagram [21]                                                 | 1  |

|--------------------------------------------------------------------------------|----|

| 2.1. SERDES in Serial Data Communications [9]                                  | 7  |

| 2.2. Functional Blocks of SERDES [9]                                           | 8  |

| 2.3. A Clock and Data Recovery Circuit                                         | 8  |

| 2.4. 3b/4b Encoding Table                                                      | 9  |

| 2.5. 5b/6b Encoding Table                                                      | 10 |

| 2.6. Parallel SERDES Cores Driven by the Same PLL Circuit Clock [9]            | 12 |

| 2.7. Basic PLL Architecture [16]                                               | 13 |

| 2.8. Response of a PLL to an Input Analog Signal of Varying Fre-               |    |

| quency $[10]$                                                                  | 15 |

| 2.9. Response of a PLL to a Phase Step [16]                                    | 17 |

| 2.10. PFD with Charge Pump [30]                                                | 18 |

| 2.11. Gilbert Phase Detector with Input and Output Waveforms $\left[10\right]$ | 19 |

| 2.12. CMOS Gilbert Cell [30]                                                   | 20 |

| 2.13. A Ring Oscillator Using Five Digital Inverters [16]                      | 21 |

| 2.14. LC Cross Coupled VCO [10] $\ldots$                                       | 22 |

| 2.15. Delay-Locked Loop Generating Clock Edges [16]                            | 23 |

| 2.16. Modeling with TOF                                                        | 24 |

| 2.17. Modeling with TBF's $[19]$                                               | 26 |

| 2.18. An Example Circuit for TBF [19]                                          | 27 |

| 3.1. Timing Jitter [28]                                                        | 30 |

| 3.2. Jitter Classification [28]                                                | 30 |

| 3.3. Eye Diagram [5]                                                           | 34 |

| 3.4. Bit Error Rate [28]                                                       | 35 |

| 3.5. Bathtub Curve [5]                                               | 36 |

|----------------------------------------------------------------------|----|

| 3.6. Jitter Estimation Circuit [38]                                  | 38 |

| 3.7. System Architecture [38]                                        | 38 |

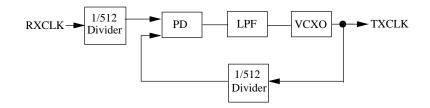

| 3.8. Block Diagram of PLL De-Jitter Circuit [33]                     | 39 |

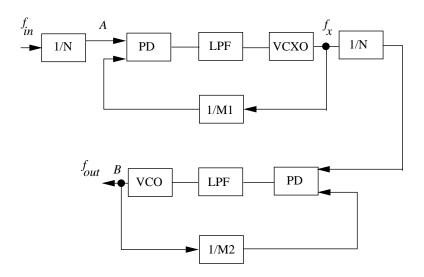

| 3.9. Proposed De-Jitter Circuit Using Two Cascaded PLL Circuits [33] | 40 |

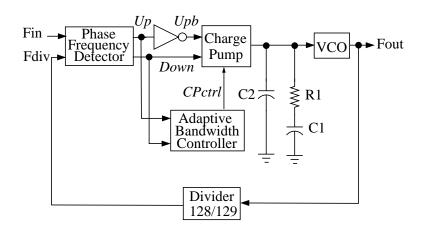

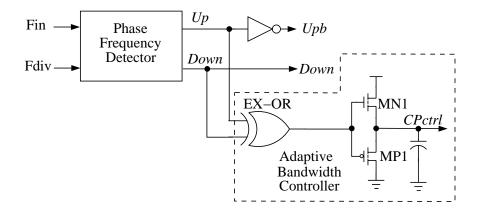

| 3.10. Block Diagram of the Proposed PLL Circuit [15]                 | 41 |

| 3.11. Adaptive Bandwidth Controller Circuit [15]                     | 42 |

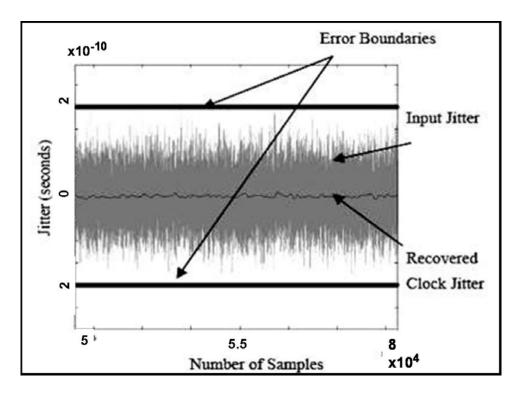

| 3.12. The Input Jitter and the Recovered Clock [14]                  | 43 |

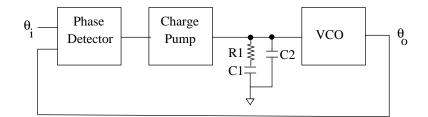

| 3.13. The Clock and Data Recovery Circuit [14]                       | 45 |

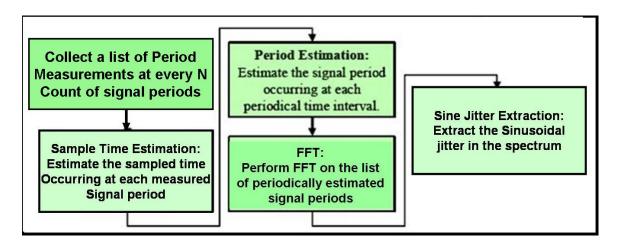

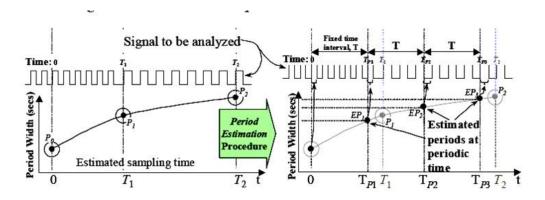

| 3.14. Simplified Technique Flow Overview [26]                        | 48 |

| 3.15. Estimate the Sampled Time of Each Measured Period $\ [26]$     | 49 |

| 3.16. Estimate the Signal Periods at Periodic Time Interval $[26]$   | 50 |

| 3.17. Circular BIST Flip-Flop [12]                                   | 51 |

| 3.18. Circular BIST Path [12]                                        | 52 |

| 3.19. The Adaptive PLL $[39]$                                        | 53 |

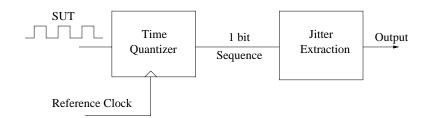

| 3.20. Single-Channel Architecture for Jitter Measurement [8]         | 54 |

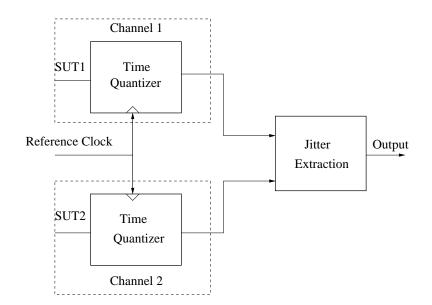

| 3.21. Test Architecture of a Dual-Channel Configuration [8]          | 55 |

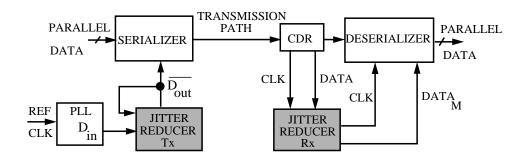

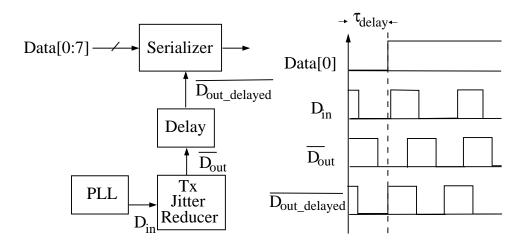

| 4.1. SERDES with Jitter Reduction Circuits                           | 57 |

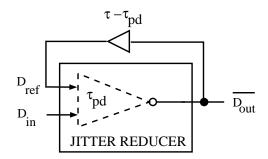

| 4.2. Jitter Reducer with Reference Signal $\overline{D_{out}}$       | 58 |

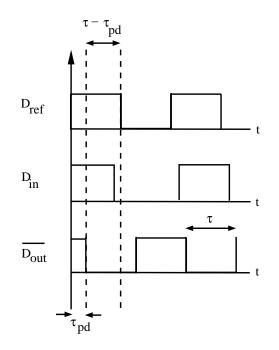

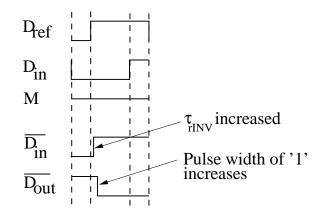

| 4.3. Jitter Reducer – Timing Waveforms                               | 59 |

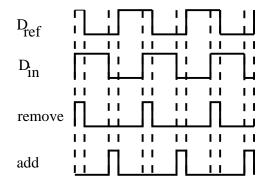

| 4.4. Add and Remove Pulses                                           | 60 |

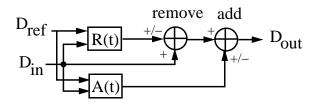

| 4.5. Signal Flow Graph of the Jitter Reducer                         | 61 |

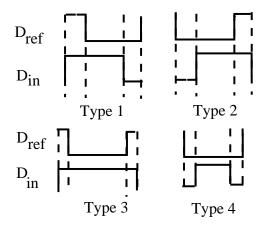

| 4.6. Four Types of Jitter Conditions                                 | 61 |

| 4.7. $D_{in}$ and $D_{ref}$ Phase in Three Time Regions              | 62 |

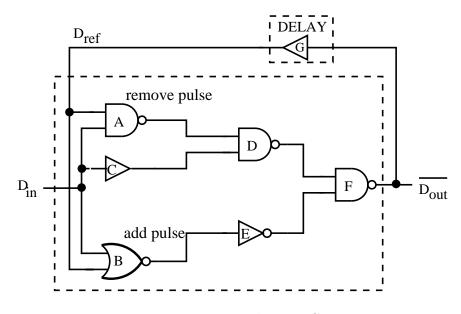

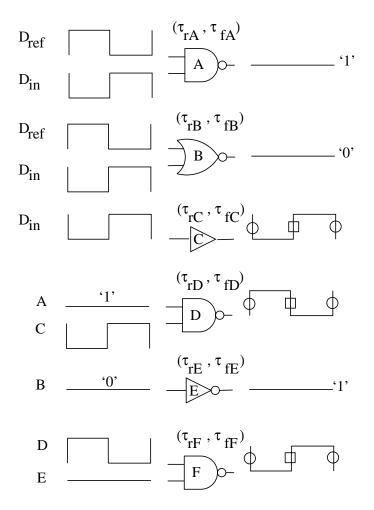

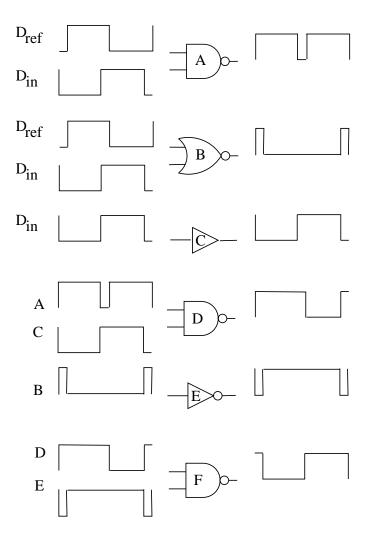

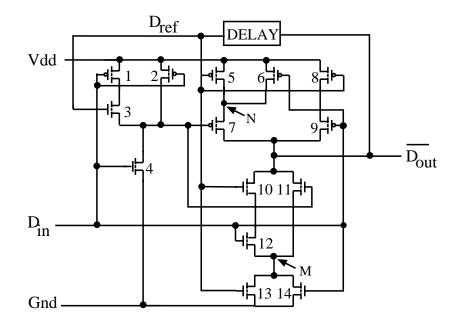

| 4.8. Jitter Reduction Circuit                                        | 64 |

| 4.9. Gate Outputs – Non-Zero Delay Case                              | 65 |

| 4.10. Case $1 - D_{in}$ Leading $D_{ref}$                            | 67 |

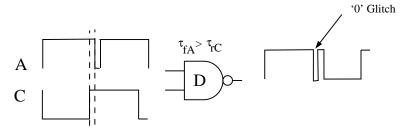

| 4.11. A Glitch at the Output of Gate D for Case 1                    | 68 |

| 4.12. A Glitch at the Output of Gate F for Case 1                    | 68 |

| 4.13. | Case $2 - D_{in}$ Lagging $D_{ref}$                                            | 69  |

|-------|--------------------------------------------------------------------------------|-----|

| 4.14. | A Glitch at the Output of Gate D for Case 2                                    | 70  |

| 4.15. | A Glitch at the Output of Gate F for Case 2                                    | 70  |

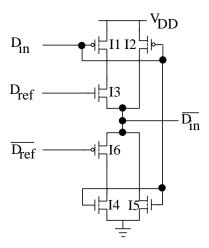

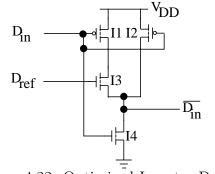

| 4.16. | Optimized Jitter Reduction Circuit                                             | 74  |

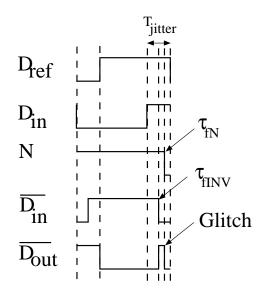

| 4.17. | Optimized Jitter Reduction Circuit – $D_{in}$ is leading $D_{ref}$             | 75  |

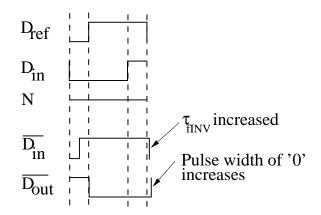

| 4.18. | Removal of the Glitch by Increasing the Inverter Falling Delay                 | 76  |

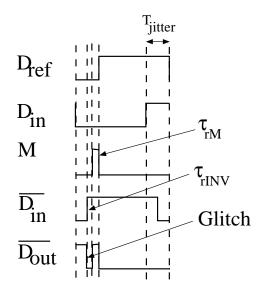

| 4.19. | Glitch Occurring at the Output $\overline{D_{out}}$ Due to the Nodal Voltage M | 77  |

| 4.20. | Removal of the Glitch by Increasing the Inverter Rising Delay                  | 78  |

| 4.21. | New Inverter Design                                                            | 79  |

| 4.22. | Optimized Inverter Design                                                      | 80  |

| 4.23. | Jitter Transfer Function of Tx Jitter Reducer for Various Input                |     |

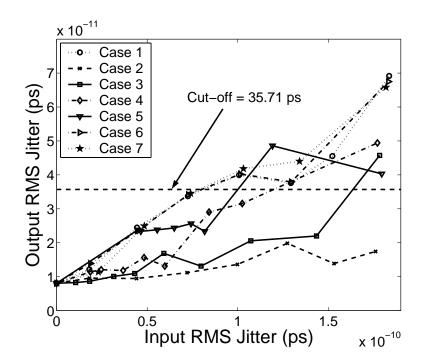

|       | Jitter Types                                                                   | 84  |

| 4.24. | Tx Jitter Reducer Phase Delay Compensation                                     | 87  |

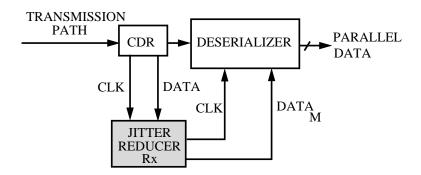

| 5.1.  | Receive Side Jitter Reducer in the SERDES Circuit                              | 89  |

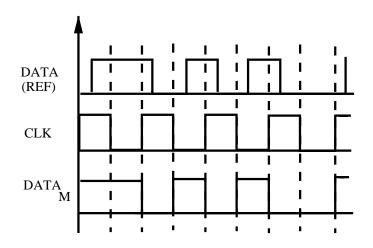

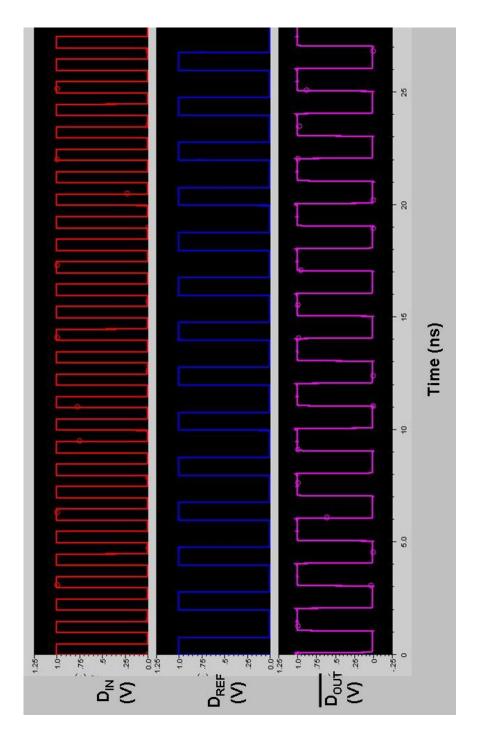

| 5.2.  | Timing Waveform for Receive Side Jitter Reduction                              | 90  |

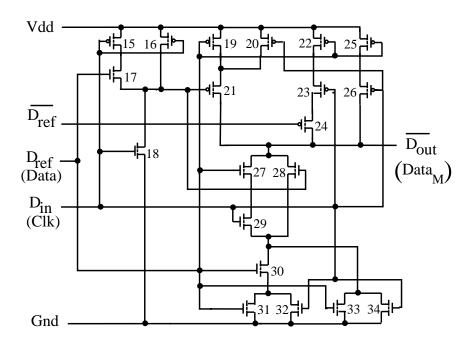

| 5.3.  | Receive Side Jitter Reduction Circuit                                          | 91  |

| 5.4.  | Receive Side Jitter Reduction Circuit – A Case for DCD Jitter                  | 92  |

| 5.5.  | Jitter Transfer Function of the Rx Jitter Reduction Circuit                    | 96  |

| 5.6.  | Total Jitter Transfer Function with the Tx and Rx Jitter Reducers              | 100 |

| 6.1.  | Jitter Transfer Function of the Tx and Rx Jitter Reducers under                |     |

|       | Process Variations                                                             | 105 |

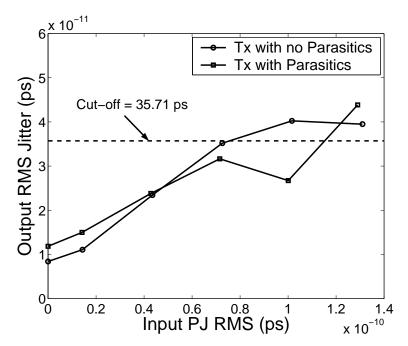

| 6.2.  | Jitter Transfer Function of the Tx Jitter Reducer with Parasitic               |     |

|       | Capacitances                                                                   | 106 |

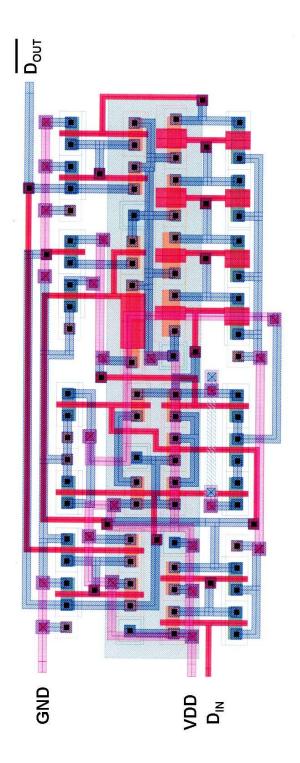

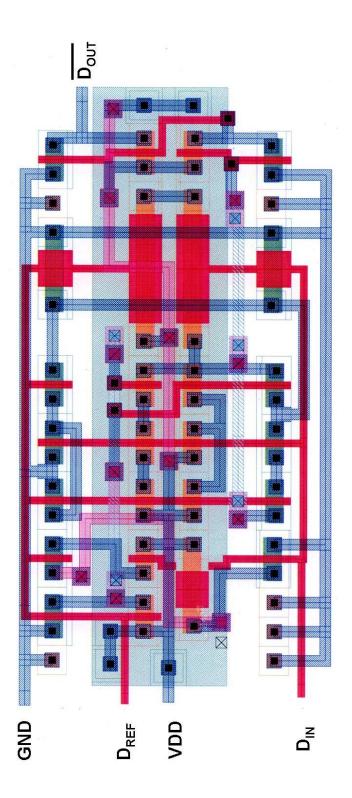

| 6.3.  | Tx Jitter Reducer Layout                                                       | 108 |

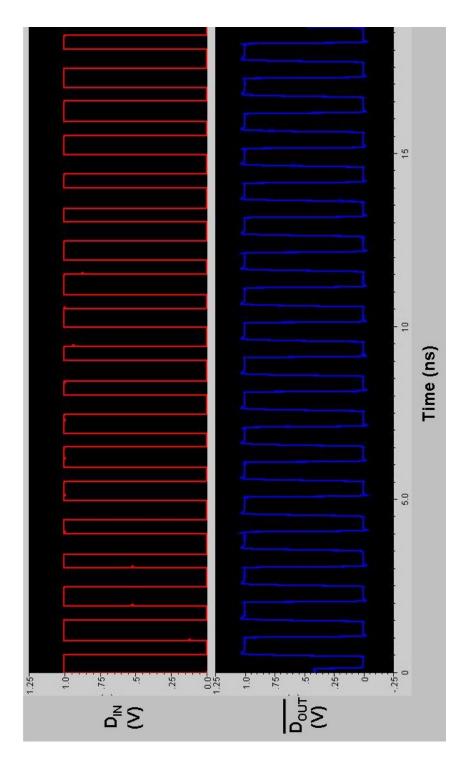

| 6.4.  | Periodic Jitter Reduction by Tx Jitter Reducer                                 | 109 |

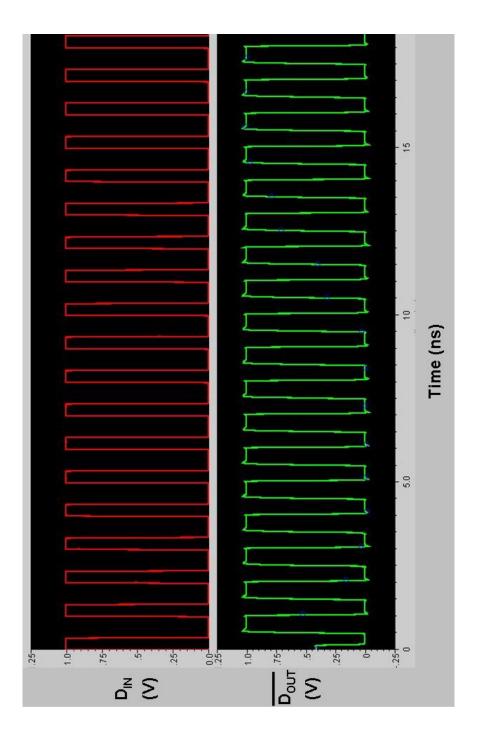

| 6.5.  | DCD Jitter Reduction by Tx Jitter Reducer                                      | 110 |

| 6.6.  | Rx Jitter Reducer Layout                                                       | 111 |

| 6.7.  | DCD Jitter Reduction by Rx Jitter Reducer                                      | 112 |

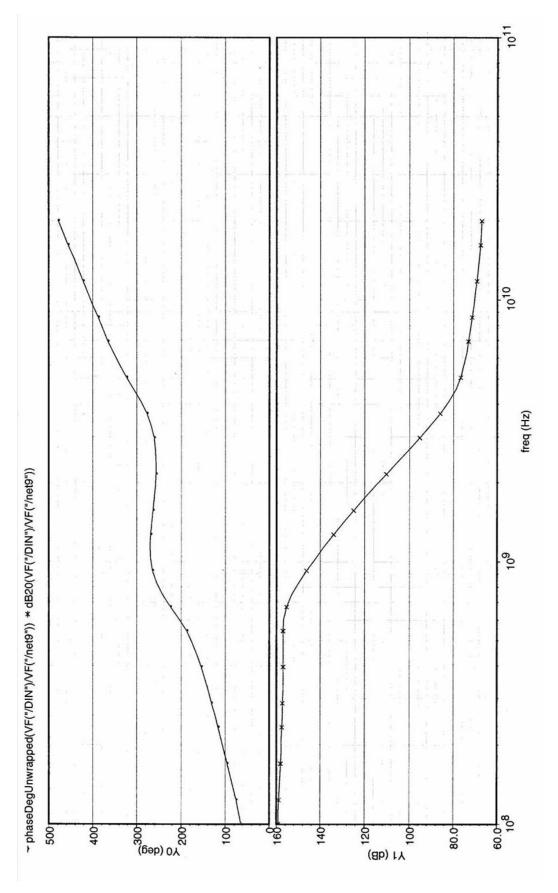

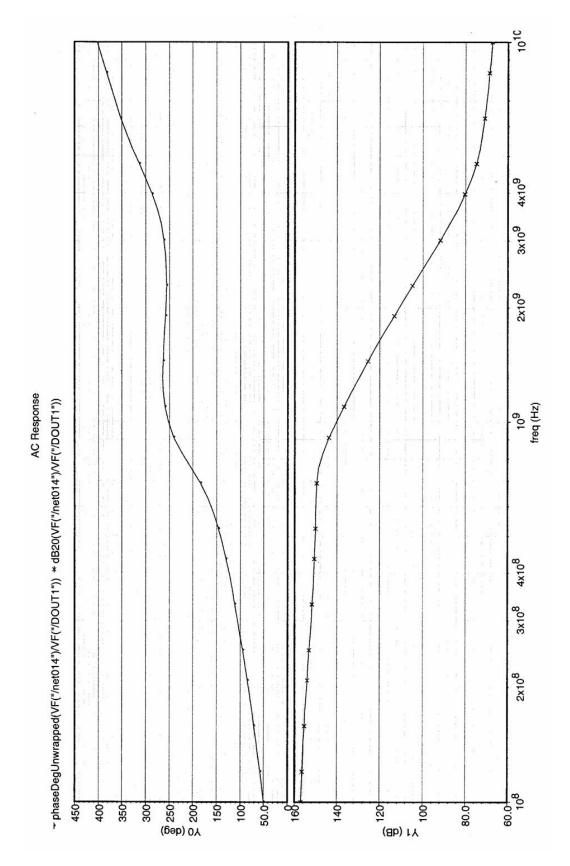

| 6.8.  | Magnitude and Phase Response of the Transmit Side PLL without       |       |

|-------|---------------------------------------------------------------------|-------|

|       | the Tx Jitter Reducer                                               | 114   |

| 6.9.  | Magnitude and Phase Response of the Transmit Side PLL with the      |       |

|       | Tx Jitter Reducer                                                   | 115   |

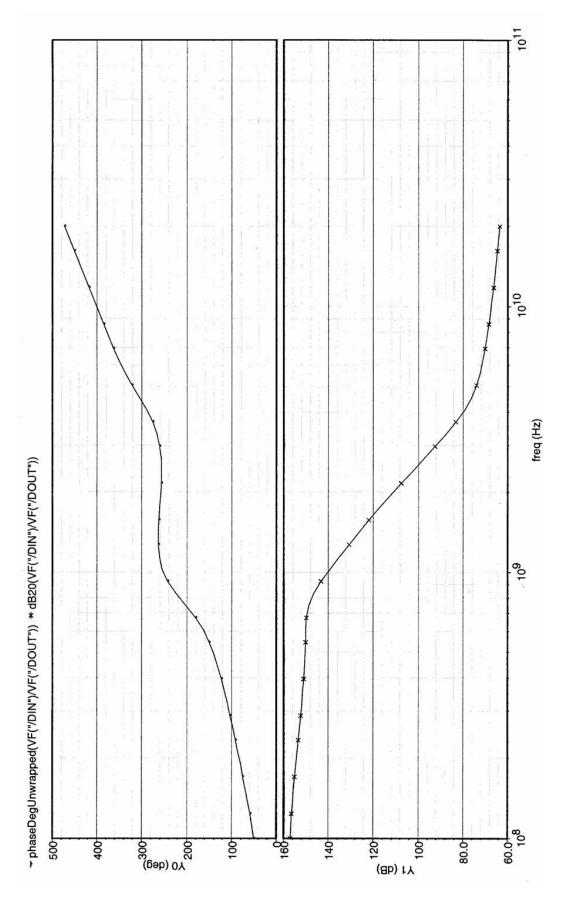

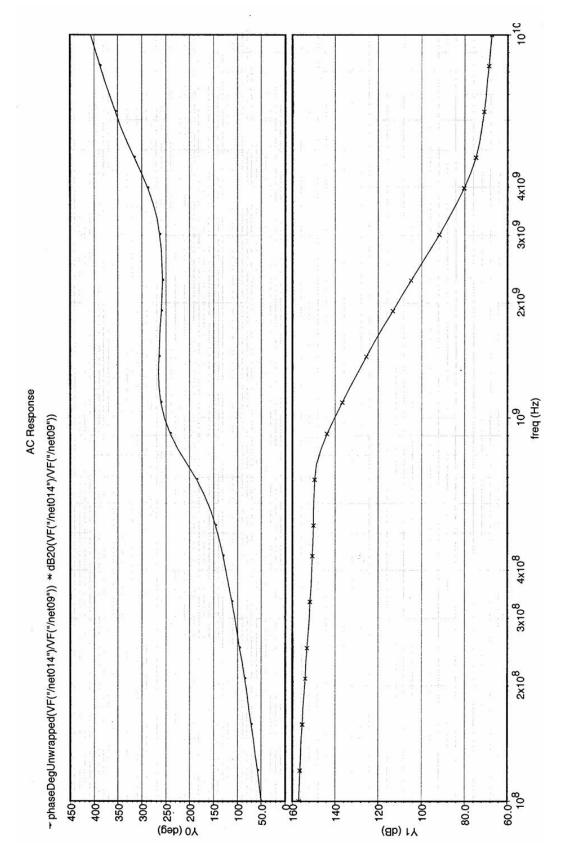

| 6.10. | . Magnitude and Phase Response of the Receive Side PLL without      |       |

|       | the Rx Jitter Reducer                                               | 118   |

| 6.11. | . Magnitude and Phase Response of the Receive Side PLL with the     |       |

|       | Rx Jitter Reducer                                                   | 119   |

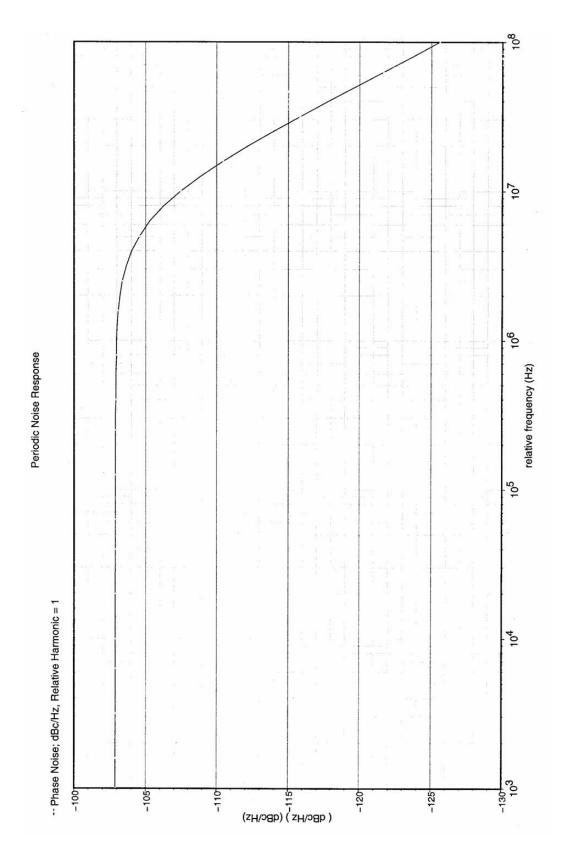

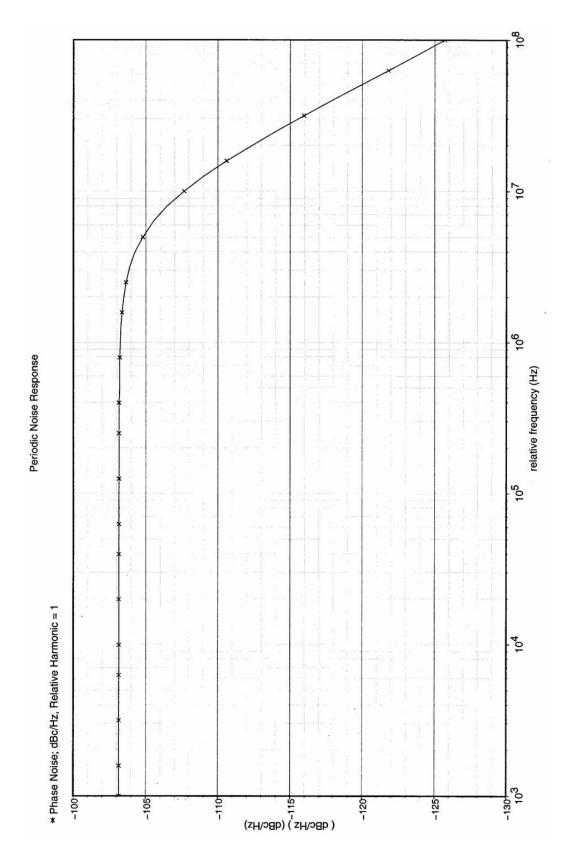

| 6.12. | . Phase Noise at the Output of the PLL Circuit at the Transmit Side | e 122 |

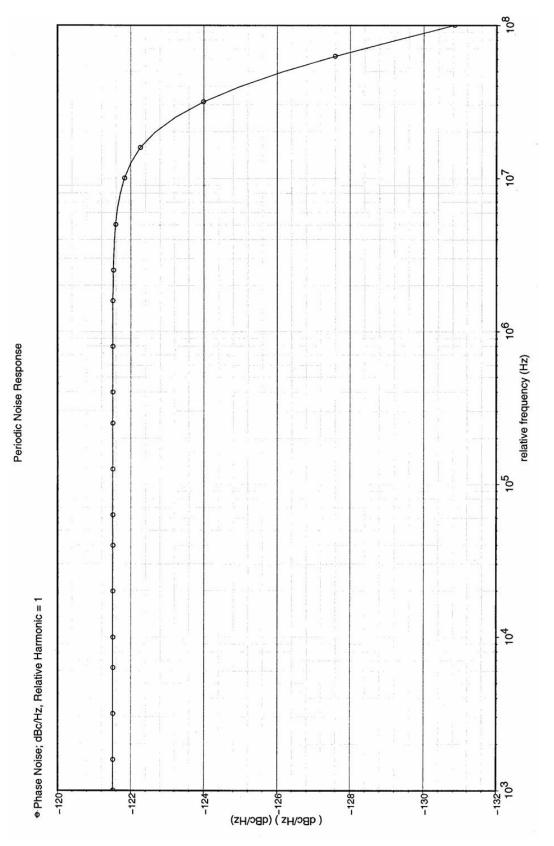

| 6.13. | . Phase Noise at the Output of the Jitter Reduction Circuit at the  |       |

|       | Transmit Side                                                       | 123   |

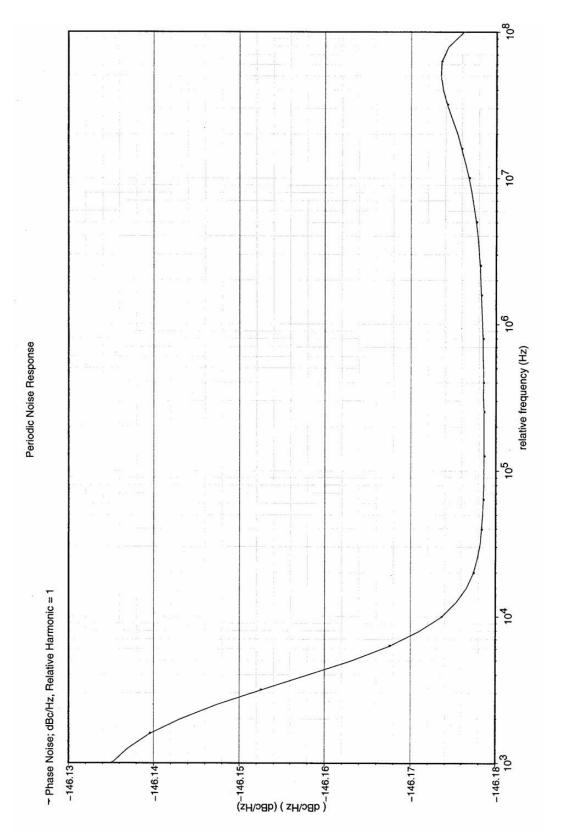

| 6.14  | . Phase Noise at the Output of the PLL Circuit at the Receive Side  | 124   |

| 6.15. | Phase Noise at the Output of the Jitter Reduction Circuit at the    |       |

|       | Receive Side                                                        | 125   |

| 6.16  | Testing the SERDES                                                  | 126   |

# Chapter 1 Introduction

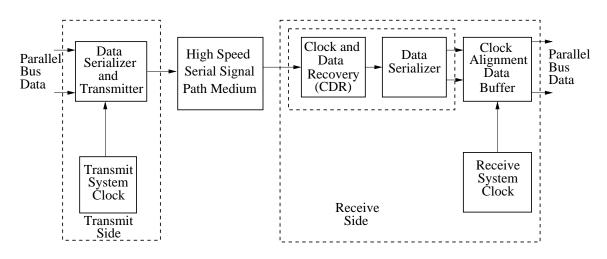

SERDES is a high-speed serial data link. A growing number of *application specific integrated circuits* (ASICs) and programmable *integrated circuits* (ICs) provide integrated SERDES interfaces [21]. A typical high-speed serial data link is shown in Figure 1.1. Its purpose is to quickly and reliably transfer data from one physical location to another. The data, often in parallel bus form, is serialized to a single high-speed signal. This signal is transferred across a path medium that is ideally a high quality transmission line path to the new location. Included in SERializer and DESerializer functions are embedded clock and *clock-data recovery* (CDR) circuitry, needed to create a high-speed serial path.

Figure 1.1: SERDES Block Diagram [21]

At the receive end of the path, a *clock and data recovery* (CDR) circuit receives the signal and extracts a properly timed bit clock from the data flow. The data signal is then deserialized down to a lower speed parallel data interface. Chip-to-chip communication had previously been almost exclusively a parallel domain [6]. The amount of logic needed to serialize and deserialize far outweighed any savings that come from pin count reduction. But, with deep sub-micron geometry, an incredible amount of logic can be achieved in a very small area of silicon. SERDES can be included on parts for a very low silicon cost. Add to that the ever increasing need for I/O bandwidth, and SERDES quickly becomes the logical choice for moving any significant amount of data chip-to-chip. Consider the following benefits of SERDES chip-to-chip communication:

- Pin Count: Smaller, cheaper packages.

- Pin Count: Fewer layers and pins on *printed circuit board* (PCB) assemblies.

- Smaller Packages: Smaller, cheaper boards and more compact designs.

- Simultaneous Switching Output (SSO): When multiple output drivers switch simultaneously, they induce a voltage drop in the chip/package power distribution [4]. The simultaneous switching momentarily raises the ground voltage within the device relative to the system ground. This apparent shift in the ground potential to a non-zero value is known as simultaneous switching noise (SSN) or, more commonly, ground bounce. The ground bounce voltage is related to the inductance present between the device ground and the system ground. Problems may arise when this ground bounce gets transferred to the outside through output buffers driving a logic low value. If the bounce is higher than the  $V_{IL}$  threshold of the input being driven, there is a possibility that the glitch will be recognized as a legal logic '1'. Fewer pins and differential signaling eliminate the SSO problem.

- Power: Usually a high-speed serial link will use less power than a parallel link. This is especially true of some of the actively biased/terminated high-speed parallel standards such as *high-speed transistor logic* (HSTL).

- Control Lines Included: Often a parallel interface needs a few lines for

control and enable in addition to the data lines. Serial links have enabling and control capabilities built into most protocols.

A phase locked loop (PLL) is used to keep time for the serializer deserializer pair [1]. The PLL is internal to each device and is required to lock to the input clock frequency, perform the correct multiplication factor and maintain its output with minimal jitter. Jitter is the deviation of a signal's timing event from its intended (ideal) occurrence in time. A PLL is used because of its inherent feedback path allowing constant correction if a minor change is seen in the input signal edge position or period. To understand the SERDES technology, it is important to have a basic understanding of how a PLL operates. All SERDES PLLs have an input frequency and an internal core frequency that needs to be synchronized with this frequency. The internal frequency is responsible for the serialization timing. For, without the PLL running, data compression is not possible. There are several key factors to keep in mind for PLL operation: the time it takes to lock, the power consumed, the resolution of each loop correction factor and the effect that jitter has on the circuit.

### 1.1 Motivation

#### 1.1.1 Problems with SERDES

The main problem in SERDES is *jitter*, the time deviation of the actual signal transition from the expected. The *phase locked loop* (PLL) at the transmit side of the SERDES generates a fast clock signal, which has timing jitter. When this clock signal drives the serializer, the jitter is passed on to the serial data. More jitter is added to the serial data as it propagates through the transmission path. At the receive end the CDR circuit does not properly track the jitter present in the received serial data signal. As a result, when the data is sample using the recovered clock from CDR unit, it results in bit errors.

# 1.1.2 Problems with PLL Circuit in Microprocessors and Wireless Transceivers

On a broader spectrum, the clock signals generated by the PLL circuits in microprocessors and wireless transceivers suffer from the same timing jitter problem. In the case of microprocessors, it affects the synchronization of the various signals in microprocessors with the jittered clock signal and in the case of wireless transceivers, the problem is similar to that of the SERDES circuit, i.e., a wrong data bit is latched resulting in bit-errors.

# 1.1.3 Why Do We Need a New Jitter Reduction Technique?

A jitter reduction technique was proposed by Tian Xia *et al* [39]. In this work a jitter test circuit was employed to monitor the PLL jitter performance. A digital control unit was used to calibrate the loop filter parameters dynamically to reduce jitter. The drawback in this technique is the chip area overhead, which consists of capacitors and digital counters. Apart from this there are several other techniques that try to reduce the jitter in the signal generated by the PLL circuit by modifying its loop bandwidth dynamically. The main problem with this is that the settling time of the PLL circuit is affected. To overcome this problem, we need to propose a circuit that reduces jitter in the PLL signal externally.

### **1.2** Problem Statement

Our goal is to design a jitter reduction circuit for the transmit side PLL, which determines the jitter present and reduces it using only a few logic gates. At the receive side, we propose to extend the idea to reduce the jitter between the recovered clock and data signal by aligning the serial data with the clock. The proposed hardware should have very little area overhead.

### **1.3** Original Contribution of the Dissertation

The main contribution of this work is the jitter reduction methodology that basically uses the concept of error estimation and reduction. For the transmit side, the error is estimated using the jittered clock signal and the looped-back signal and for the receive side, the error is estimated using the recovered clock and the incoming serial data signal. The reduction is based on the notion of pulse shaping, where the jittered signal pulse shape is changed according to the reference signal. The accuracy of pulse shaping depends on how accurate the reference signal is.

### 1.4 Summary of Results

In the case of the transmit and the receive side jitter reducer, the jitter is reduced, on average, by 62.24% and 35.88%, respectively and also the BER computed probabilistically is improved from  $8.3 \times 10^{-2}$  to  $6.44 \times 10^{-20}$ .

### 1.5 Organization of the Dissertation

The dissertation is organized as follows. The introduction about the new jitter reduction work is given in Chapter 1, where the problem is defined. The prior work is split into two chapters. The SERDES architecture and the PLL circuitry are explained in Chapter 2. In Chapter 3, various jitter reduction and testing schemes are explained. The jitter reduction technique for the transmit side is explained with results in Chapter 4 and in Chapter 5 the jitter reduction technique for the receive side and the performance of the SERDES circuit in the presence of both the transmit and the receive side jitter reducers are explained. In Chapter 6, the circuit design issues are addressed and also a SERDES test scheme is presented. Finally, Chapter 7 gives the conclusion and future work.

## Chapter 2

# Concepts on Serializer-Deserializer (SERDES) and Phase-Locked Loop (PLL) Circuits and Timed Boolean Functions

### 2.1 SERDES – Introduction

As data rates reach more than 1 Gb/s its becoming difficult to transmit data across multi-drop parallel bus such as the PCI or PCI-X [9] buses. The primary problem is the tolerance in timing skew between parallel wires in these bus standards. To overcome the problem, the parallel bus standards are being replaced by their serial equivalent, such as PCI Express. Timing skew [3] is a problem that can occur on many kinds of computer buses. When signals are transmitted down parallel paths, they will not arrive at exactly the same time due to unavoidable variations in wire transmission properties and transistor sizing, but the signals will arrive close to each other in time. As the frequencies of these circuits increase, this variation will become more and more erratic. If the timing skew is large enough, the clock signal may arrive while the data signal is still transitioning between the previous and current values. If this happens, it will be impossible to determine what value was transmitted from the detected value, resulting in a bit-error. The timing skew arises in parallel buses due to cross talk and signal reflections in the wires, which are very difficult to control at higher frequencies.

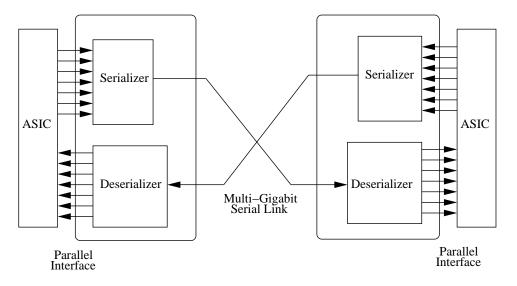

In the serial bus, a device called *serializer-deserializer* (SERDES) is used to transmit and receive data over a serial link. The SERDES can be either a standalone device or an ASIC. In essence, a SERDES is a serial transceiver that converts parallel data into a serial data stream on the transmitter side and converts the

Figure 2.1: SERDES in Serial Data Communications [9]

serial data back into parallel data on the receiver side. The timing skew problem encountered in a parallel bus is solved by embedding the clock signal into the data stream. Since there is no separate clock signal in a serial bus, timing skew between clock and data no longer exists. As a result, a serial bus can usually operate at much higher data rate than a parallel bus in a comparable system environment. Figure 2.1 shows a typical *application specific integrated circuit* (ASIC) application where a SERDES circuit is used. The SERDES serializer and deserializer circuits are placed in the transmit and receive sides of the ASIC, respectively.

### 2.2 SERDES Architecture

Figures 2.2 and 2.3 show the functional blocks of the SERDES designed for PCI Express and a simple CDR circuit used in the receive side of the SERDES. The parallel data is encoded into serial data using the 8b/10b encoding scheme, where the lower 5 bits are converted into a 6-bit group and the upper 3 bits into a 4-bit group. These groups are concatenated to form 10-bit code word. The 8b/10b encoding is used for DC balancing, i.e., to maintain an equal number of one's and zero's in the transmitted data stream. The data symbols are often referred to as Dxx.y, where xx ranges from 0 - 31 and y from 0 - 7 [2]. Because 8b/10b

Figure 2.2: Functional Blocks of SERDES [9]

Figure 2.3: A Clock and Data Recovery Circuit

| encoding uses 10-bit | t symbols to encode | e 8-bit words, each o | of the 256 possible 8-bit |

|----------------------|---------------------|-----------------------|---------------------------|

| words can be encode  | ed in two different | ways, one the bit-wi  | ise inverse of the other. |

| Input<br>HGF |     | RD = -1 | RD = +1 |

|--------------|-----|---------|---------|

|              |     | fghj    |         |

| D.x.0        | 000 | 1011    | 0100    |

| D.x.1        | 001 | 10      | 001     |

| D.x.2        | 010 | 01      | 101     |

| D.x.3        | 011 | 1100    | 0011    |

| D.x.4        | 100 | 1101    | 0010    |

| D.x.5        | 101 | 10      | 010     |

| D.x.6        | 110 | 01      | 10      |

| D.x.P7       | 111 | 1110    | 0001    |

| D.x.A7       | 111 | 0111    | 1000    |

Figure 2.4: 3b/4b Encoding Table

Figures 2.4 and 2.5 show the tables for both 3b/4b and 5b/6b encoding, where RD- and RD+ represent the two different ways for encoding and RD- is the bit-wise inverse of RD+.

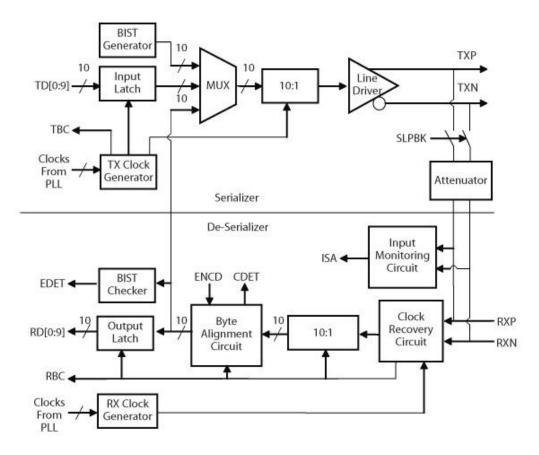

#### 2.2.1 Transmit Section

The transmit side of the SERDES consists of the *built-in self-test* (BIST) generator, a 10-to-1 multiplexer (10:1) and a line driver. The BIST pattern generator is used to generate various test patterns to perform system level and diagnostic tests. The multiplexer converts the 10-bit parallel data to serial data and is driven by a high speed clock generated using an analog *phase-locked loop* (PLL) circuit. The PLL takes a low frequency clock signal from a crystal oscillator as a reference input. The PLL has to generate a clock signal that has very low jitter in it. For the PCI Express, the amount of jitter allowed is 120ps for a clock period of 400ps. The serial data is then transmitted using a line driver across a  $100\Omega$  differential

| Input |       | RD = -1 | RD = +1 | Input |       | RD = -1 | RD = +1 |

|-------|-------|---------|---------|-------|-------|---------|---------|

|       | EDCBA | abcdei  |         |       | EDCBA | abcdei  |         |

| D.00  | 00000 | 100111  | 011000  | D.16  | 10000 | 011011  | 100100  |

| D.01  | 00001 | 011101  | 100010  | D.17  | 10001 | 100011  |         |

| D.02  | 00010 | 101101  | 010010  | D.18  | 10010 | 010011  |         |

| D.03  | 00011 | 110001  |         | D.19  | 10011 | 110010  |         |

| D.04  | 00100 | 110101  | 001010  | D.20  | 10100 | 001011  |         |

| D.05  | 00101 | 101     | 1001    | D.21  | 10101 | 101010  |         |

| D.06  | 00110 | 011001  |         | D.22  | 10110 | 011010  |         |

| D.07  | 00111 | 111000  | 000111  | D.23  | 10111 | 111010  | 000101  |

| D.08  | 01000 | 111001  | 000110  | D.24  | 11000 | 110011  | 001100  |

| D.09  | 01001 | 100101  |         | D.25  | 11001 | 100110  |         |

| D.10  | 01010 | 010101  |         | D.26  | 11010 | 010110  |         |

| D.11  | 01011 | 110100  |         | D.27  | 11011 | 110110  | 001001  |

| D.12  | 01100 | 001101  |         | D.28  | 11100 | 001110  |         |

| D.13  | 01101 | 101100  |         | D.29  | 11101 | 101110  | 010001  |

| D.14  | 01110 | 011100  |         | D.30  | 11110 | 011110  | 100001  |

| D.15  | 01111 | 010111  | 101000  | D.31  | 11111 | 101011  | 010100  |

|       |       |         |         | K.28  |       | 001111  | 110000  |

Figure 2.5: 5b/6b Encoding Table

terminated printed circuit board (PCB) trace.

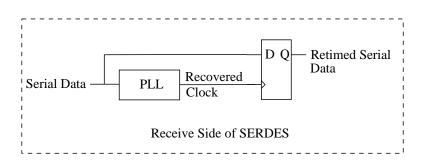

### 2.2.2 Receive Section

At the receive side there is an input monitoring circuit that senses the differential line to find whether the differential voltage is greater than 175mV. For the receive section to be idle the differential signal should be less than 65mV according to the PCI Express specification. The received data is retimed with the clock recovered using the *clock and data recovery* (CDR) circuit. The PCI Express allows a timing jitter of 60% of the input bit time. The CDR circuit has to have a bandwidth wide enough to track this timing jitter or should filter out the high frequency jitter. Once the data is retimed, the serial data is latched into the demultiplexer using the high speed recovered clock. The demultiplexer then uses a low frequency clock that has a constant phase relation with the high speed recovered clock to provide the parallel data, which is at its original speed. A byte alignment circuit is used to align the encoded data at its 8b/10b encoded byte boundaries. During the encoding process the original serial data is appended with special start and stop bits. The alignment circuit looks for these special characters and aligns the parallel data with these special characters and transmits the aligned data to the ASIC. In the test mode the parallel data is compared with the expected data for performing the diagnostic tests.

## 2.3 SERDES Design Features

### 2.3.1 Jitter Performance

A good SERDES design is judged based on its jitter performance. The PCI Express allows a maximum jitter of 120ps for the serializer and 240ps for the deserializer, for a clock period of 400ps. A small jitter in the serializer output means that the received data will have a low *bit error rate* (BER). The serializer jitter is mainly due to the high-speed clock generated from the PLL circuit. The

PLL jitter has to be reduced using an on-chip jitter tracking circuit that monitors the loop bandwidth and tunes it accordingly to reduce the jitter in the clock generated. At the receive side the jitter performance is judged by the jitter present in the incoming the serial data. The clock recovered by the CDR circuit retimes the serial data, so a bit error will occur if either the clock or data is too early or late. Therefore, a good jitter reduction mechanism should reduce the timing jitter between the clock and data signal.

#### 2.3.2 Power and Area

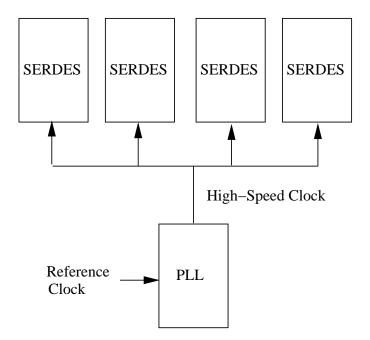

In applications where there are multiple SERDES cores, each requiring its own PLL circuit to generate the fast clock, power and area can be saved by driving a group of SERDES cores in parallel using the same PLL circuit as shown in Figure 2.6.

Figure 2.6: Parallel SERDES Cores Driven by the Same PLL Circuit Clock [9]

At the receive side, to reduce power and area, instead of using a PLL circuit, a *delay-locked loop* (DLL) circuit can be used. The DLL circuit uses a *voltage*  controlled delay line (VCDL) to change the frequency of its local clock signal so that it is phase locked to the incoming data signal. The DLL circuit requires a high-speed clock for its operations. Both the serializer and the deserializer can uses the same PLL circuit that generates the high-speed clock, thereby reducing the area and power.

### 2.3.3 SERDES Test

The current *automatic test equipment* (ATE) available can operate at 1.5GHz, but are not capable of testing the SERDES cores at the required speed, which is either 10Gb/s for Ethernet or 40Gb/s for synchronous optical network (SONET). So, the ASIC designers provide BIST pattern generators that generate pseudo random bit sequence (PRBS) patterns and the corresponding pattern checker. To perform the jitter tolerance test at the receive side, the PRBS pattern is looped back to the receiver through an on-chip or external jitter injection circuit. The receiver is now tested with this input jittered signal and the jitter transfer function is determined.

### 2.4 Phase-Locked Loop – Introduction

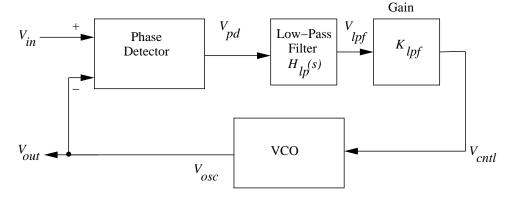

Figure 2.7: Basic PLL Architecture [16]

Figure 2.7 shows the basic architecture of a PLL circuit [16], which consists of a phase detector, a low-pass filter, a gain stage, and a *voltage controlled oscillator* (VCO). The phase detector produces an output proportional to the phase difference of the input and the feedback signal. The low-pass filter extracts an average voltage, which is amplified by the gain stage to give the control voltage for the VCO.

Let  $V_{in}$  be an input sinusoidal signal. The phase detector is a analog multiplier with a relationship given by:

$$V_{pd} = K_M V_{in} V_{osc} \tag{2.1}$$

where  $V_{osc}$  is the VCO output and  $K_M$  is the multiplication constant. Let  $V_{in}$  and  $V_{osc}$  be given as follows:

$$V_{in} = E_{in}\sin(\omega t) \tag{2.2}$$

$$V_{osc} = E_{osc}\sin(\omega t - \phi_d) \tag{2.3}$$

The term  $\phi_d$  represents the phase difference between the input and the oscillator signal and the reason for having 90° phase shift is that when the phase difference is zero, the average output of the phase detector is zero. The output of the phase detector is given by the following equation:

$$V_{pd} = K_M V_{in} V_{osc} = K_M E_{in} E_{osc} \sin(\omega t) \cos(\omega t - \phi_d)$$

(2.4)

Using a trigonometric identity, we have:

$$V_{pd} = K_M \frac{E_{in} E_{osc}}{2} [\sin(\phi_d) + \cos(2\omega t - \phi_d)]$$

(2.5)

The function of the low-pass filter is to remove the high frequency component and the output of the low-pass filter is given as follows:

$$V_{lpf} = K_{lpf} V_{pd} \tag{2.6}$$

where  $K_{lpf}$  is the gain of the low-pass filter. The VCO control voltage is then given as follows:

$$V_{cntl} = K_{lpf} K_M \frac{E_{in} E_{osc}}{2} \sin(\phi_d)$$

(2.7)

For small  $\phi_d$ , the control voltage is approximated as follows:

$$V_{cntl} = K_{lpf} K_{pd} \phi_d \tag{2.8}$$

From the above equation we see that the control voltage is directly proportional to the phase difference, and the constant  $K_{pd}$  is given as follows:

$$K_{pd} = K_M \frac{E_{in} E_{osc}}{2} \tag{2.9}$$

## 2.4.1 Operation of PLL Circuit

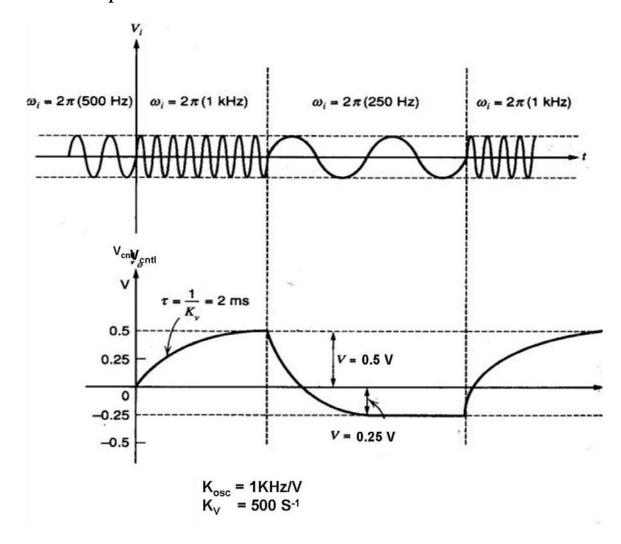

Figure 2.8: Response of a PLL to an Input Analog Signal of Varying Frequency [10]

Assume that the phase difference  $\phi_d$  is initially zero and that the input signal is locked with the VCO signal frequency. As the input signal frequency increases, it starts to lead the feedback signal and the phase detector produces an average positive voltage that is filtered by the low pass filter and is applied to the VCO, thereby increasing its frequency. The opposite happens when the input signal frequency reduces, producing an average negative voltage. The VCO reduces its frequency accordingly. The oscillator's output frequency is given as follows:

$$\omega_{osc} = K_{osc} V_{cntl} + \omega_{fr} \tag{2.10}$$

where  $\omega_{fr}$  is the free-running frequency of the VCO when its control voltage is zero and  $K_{osc}$  is a constant relating the change in frequency to control voltage. The control voltage is now given as:

$$V_{cntl} = \frac{\omega_{in} - \omega_{fr}}{K_{osc}} \tag{2.11}$$

where  $\omega_{in}$  is the frequency of the input signal, which is equal to the frequency of the oscillator output ( $\omega_{osc}$ ). Finally the phase difference is determined as follows:

$$\phi_d = \frac{V_{cntl}}{K_{lp}K_{pd}} = \frac{\omega_{in} - \omega_{fr}}{K_{lp}K_{pd}K_{osc}}$$

(2.12)

Figure 2.8 shows the response of the PLL circuit to a varying analog input signal. For a VCO free-running frequency of 500KHz and an input signal frequency of 500KHz, the corresponding control voltage is zero. As the input signal frequency increases to 1KHz, the control voltage also increases to 0.5V to increase the VCO frequency and when the input signal frequency reduces to 250KHz, the control voltage changes by -0.75V from its previous point to decrease the VCO frequency. The time constant  $\tau$  is 2ms, which is the inverse of the loop bandwidth  $K_v$ , which in turn is the product  $K_{pd}K_{lp}K_{osc}$ .

#### 2.4.1.1 Analysis of PLL Circuit in Locked Condition

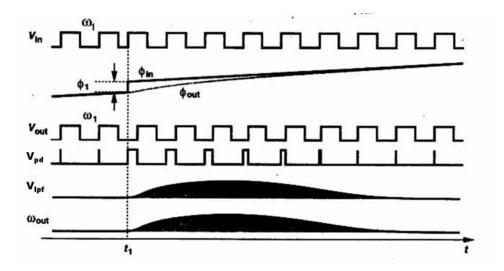

Consider a PLL in the locked condition [16] and assume the input and output waveform can be expressed as follows:

$$V_{in}(t) = V_A \cos \omega_1 t \tag{2.13}$$

$$V_{out}(t) = V_B \cos(\omega_1 t + \phi_o) \tag{2.14}$$

Figure 2.9: Response of a PLL to a Phase Step [16]

where  $\phi_o$  is the static phase error. Suppose as shown in Figure 2.9, the input has a phase step of  $\phi_1$  at  $t = t_1$ , then the total input phase at  $t_1$  is given as follows:

$$\phi_{in} = \omega_1 t + \phi_1 u (t - t_1)^2 \tag{2.15}$$

Since the output of the LPF  $(V_{lpf})$  does not change instantaneously, the VCO initially continues to oscillate at  $\omega_1$ . The growing phase difference between the input and the output then creates wide pulses at the output of the PD  $(V_{pd})$ , forcing  $V_{lpf}$  to rise gradually. As a result, the VCO frequency begins to change, attempting to minimize the phase error. The loop is not locked during the transient phase because the phase error varies with time. Since  $\phi_{in}$  has changed by  $\phi_1$ , the variation in the VCO frequency is such that the *area* under  $\omega_{out}$  provides an additional phase of  $\phi_1$  in  $\phi_{out}$ ;

$$\int_{t_1}^{\infty} \omega_{out} dt = \phi_1 \tag{2.16}$$

Thus, when the loop settles, the output becomes equal to:

$$V_{out}(t) = V_B \cos[\omega_1 t + \phi_o + \phi_1 u(t - t_1)]$$

(2.17)

Consequently, as shown in Figure 2.9,  $\phi_{out}$  gradually approaches  $\phi_{in}$ .

### 2.5 Building Blocks of PLL Circuit

In this section, we will see how to design a phase/frequency detector with a charge pump to generate the control voltage and a voltage controlled oscillator.

## 2.5.1 Phase/Frequency Detector and Charge Pump

Figure 2.10: PFD with Charge Pump [30]

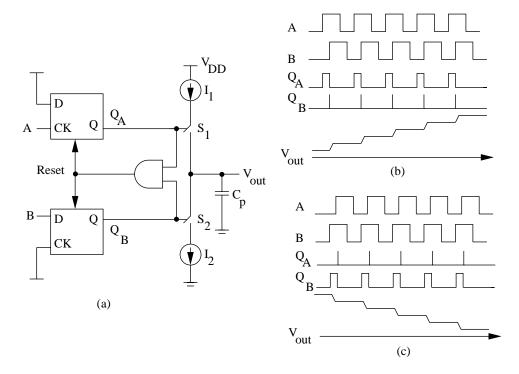

The phase/frequency detector (PFD) is implemented using sequential logic as shown in Figure 2.10(a) [30]. When signal A is leading B or when its frequency is higher than the frequency of the signal B as shown in Figure 2.10(b), the signal  $Q_A$  goes high and remains high as long B is not rising. When signal B rises, momentarily both  $Q_A$  and  $Q_B$  are high and at that instant the reset signal goes high and both  $Q_A$  and  $Q_B$  are reset. The opposite is true when either the signal A is lagging signal B or has a lower frequency than B as shown in Figure 2.10(b) then, first the signal  $Q_B$  goes high and when signal A rises, both  $Q_B$  and  $Q_A$  are high. At this instant the reset signal goes high and resets both  $Q_B$  and  $Q_A$ . The width of the signals  $Q_A$  and  $Q_B$  depends on the phase difference  $\phi_A - \phi_B$ . The signals  $Q_A$  and  $Q_B$  are known as UP and DOWN signals and they control the flow of charge across the capacitor  $C_p$ . The UP signal controls the switch  $S_1$ and the DOWN signal controls the switch  $S_2$ .  $I_1$  and  $I_2$  are current sources that either supply a constant current to charge the capacitor  $C_p$  or draw a current from the capacitor, thereby discharging it. The timing waveform shows both the cases where either A is leading or lagging B. The pulse  $Q_A$  or  $Q_B$  is proportional to the phase difference and for that period either the switch  $S_1$  or  $S_2$  is turned on, the current from the current source  $I_1$  charges the capacitor or the charge in the capacitor is discharged through the current source  $I_2$  producing the step voltage  $V_{out}$ .

## 2.5.2 Gilbert Cell as Phase Detector

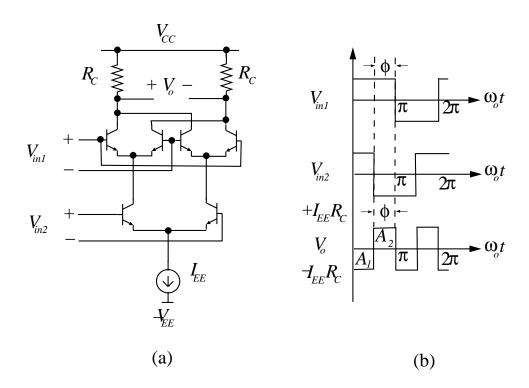

Figure 2.11: Gilbert Phase Detector with Input and Output Waveforms [10]

In frequency translation, signals at two different frequencies are applied to the two inputs of the Gilbert cell, and the sum or the difference frequency component is taken from the output [10]. If unmodulated signals of identical frequency  $\omega_o$  are applied to the two inputs, the circuit behaves as a phase detector (Figure 2.11(a)) and produces an output whose DC component is proportional to the phase difference between the two inputs. For example, consider the two input waveforms in Figure 2.11(b), which are applied to the Gilbert cell. The DC component of the output waveform is given by:

$$V_{average} = \frac{1}{2\pi} \int_0^{2\pi} V_o(t) d(\omega_o t)$$

(2.18)

$$= \frac{-1}{\pi} (A_1 - A_2) \tag{2.19}$$

where  $A_1$  and  $A_2$  are as shown in Figure. Thus,

$$V_{average} = -\left[I_{EE}R_C\frac{(\pi-\phi)}{\pi} - I_{EE}R_C\frac{\phi}{\pi}\right]$$

(2.20)

$$= I_{EE}R_C\left(\frac{2\phi}{\pi} - 1\right) \tag{2.21}$$

Figure 2.12 shows the equivalent CMOS Gilbert cell.

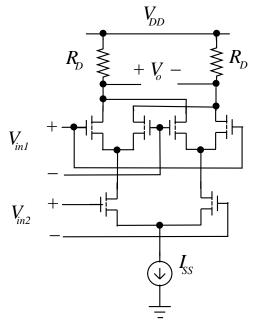

Figure 2.12: CMOS Gilbert Cell [30]

### 2.5.3 Voltage Controlled Oscillator

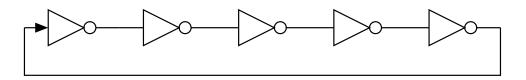

Figure 2.13 shows the most common way of implementing a VCO using digital inverters. These five inverters form a ring oscillator whose frequency of oscillation can be controlled by a voltage. Each of the n inverters offer a 90° phase shift at unity gain frequency, and is guaranteed to provide a 180° phase shift when the gain of the oscillator is greater than unity. Thus, according to the Barkhausen

Figure 2.13: A Ring Oscillator Using Five Digital Inverters [16]

criteria [16] the ring oscillator will start to oscillate with a frequency given as follows:

$$f_{osc} = \frac{1}{T} = \frac{1}{2n\tau_{inv}} \tag{2.22}$$

where T is the time period of the periodic signal and  $\tau_{inv}$  is the inverter delay. Thus the free running frequency of the oscillator can be changed by changing the number of inverter stages used.

#### 2.5.3.1 LC Cross Coupled Voltage Controlled Oscillator

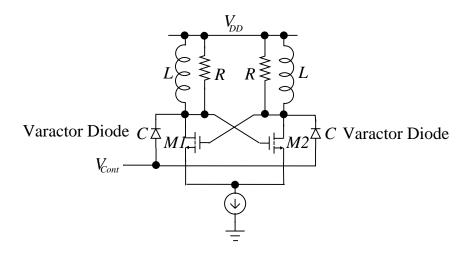

Figure 2.14 shows the LC cross-coupled voltage controlled oscillator and it consists of two cascaded *common source* (CS) stages [10]. The load for each stage is made of an inductor L, a *variable capacitor* (varactor) C and a resistor R [10]. At the resonance frequency given by the following equation:

$$f_{osc} = \frac{1}{2\pi\sqrt{LC}} \tag{2.23}$$

the phase shift due to the inductor L is canceled by the phase shift of the capacitor C and so, at resonance, the total phase shift around the loop is 360° with each CS stage contributing a 180° phase shift. According to the Barkhausen criteria,

Figure 2.14: LC Cross Coupled VCO [10]

the circuit starts oscillating at resonance if the gain of the circuit is greater than 1, i.e., the following condition must be satisfied:

$$gm_1 R gm_2 R \ge 1 \tag{2.24}$$

where  $gm_1$  and  $gm_2$  are the transconductances of transistors M1 and M2, respectively. The frequency of oscillation can be changed by changing the value of the capacitance C and hence, a varactor (reverse biased pn junction diode) is used. The capacitance value can be changed according to the following equation:

$$C_{var} = \frac{C_o}{\left(1 + \frac{V_R}{\phi_B}\right)^m} \tag{2.25}$$

where  $C_o$  is the zero-bias value,  $V_R$  the reverse-bias voltage,  $\phi_B$  the built-in potential of the junction and m a value typically between 0.3 and 0.4. The control voltage  $V_{cont}$  is used to change the reverse-bias voltage  $V_R$  of the varactor, thereby changing the capacitance C and the frequency of oscillation

### 2.6 Delay-Locked Loop

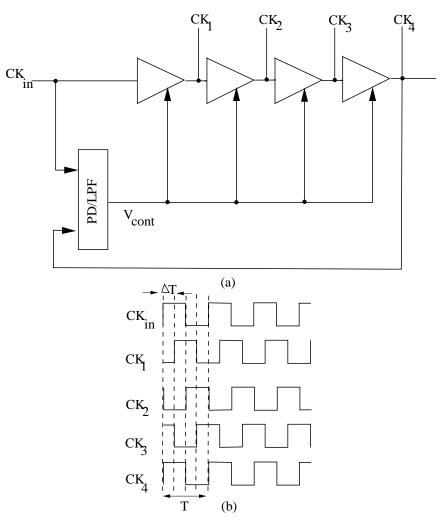

Figure 2.15(a) shows the block diagram of a delay-locked loop used for generating four clock signals, each separated by  $\Delta T$  seconds from a reference clock signal [16].

The same four clock signals can be generated using a PLL circuit, but the noise in the clock signals will be difficult to minimize as compared to the noise in the clock signals generated by the DLL circuit. Primarily this is because the PLL has

Figure 2.15: Delay-Locked Loop Generating Clock Edges [16]

a internal oscillator whose noise is recirculated back to the input, whereas in the case of the DLL the noise in the input disappears once the clock signal reaches the output and is not recirculated. The other major difference is that, since the DLL has no internal oscillator, it cannot be used in frequency synthesis, i.e., it cannot generate signals of frequency other than the input reference signal frequency and it can be used only to generate phase shifted signals. The timing waveform in Figure 2.15(b) shows that each of the four clock edges  $CK_1, CK_2, CK_3$  and  $CK_4$  are shifted by a time period of  $\Delta T$  seconds from each other. The clock edge  $CK_4$

is in phase with the reference clock signal  $CK_{in}$ . The delay  $\Delta T$  varies due to temperature and process variations and therefore, to perfectly control the delay, the fourth clock signal is looped back as in a PLL circuit to a phase detector.

The phase detector determines the phase error and accordingly produces a proportional voltage, which is low-pass filtered and applied to each of the buffers producing the respective clock signals. The buffers are built using simple inverter gates, whose delay is varied by varying their drain current. So, as the control voltage changes, the drain current also changes and so the delay of each stage changes. The DLL circuit borrows the principle of phase error detection and correction from the PLL operation. The individual stages used in the DLL circuit are known as the *voltage controlled delay line* (VCDL).

### 2.7 Timed Boolean Functions – Introduction

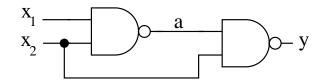

In this section two models for representing the timing information of the digital circuits are presented. McCluskey was the first to use Boolean expressions alongwith the timing information to represent a given circuit and the model is known as a *transient output function* (TOF) [25].

Figure 2.16: Modeling with TOF

Consider Figure 2.16, where the TOF of the circuit is given below:

$$y(t) = (x_1(t - \tau_{x_1ay}) \cdot x_2(t - \tau_{x_2ay})) + \overline{x_2(t - \tau_{x_2y})}$$

(2.26)

where  $\tau_{x_1ay}$ ,  $\tau_{x_2ay}$  and  $\tau_{x_2y}$  are the delays of the paths  $x_1ay$ ,  $x_2ay$  and  $x_2y$ .

The second model known as the *timed Boolean function* (TBF) was proposed by Lam and Brayton [19] and they extended the work done by McCluskey. In our new jitter reduction work explained in Chapter 4, we use the same notation used by Brayton to derive the timed Boolean expressions for our proposed circuits, since it is simple and easy to understand. The timing formalism proposed by Brayton has time as an argument and has the following properties:

- 1. This formalism representing the circuit at a particular time t gives the output values of the circuit at t.

- This formalism reduces to the ordinary Boolean function for the circuit at t greater than or equal to the settling time of the circuit.

Consider a buffer with equal rising and falling delay. Let x(t) and y(t) represent the input and the output of the buffer at time t, respectively, and  $\hat{x}$  and  $\hat{y}$  represent the steady state input and output, respectively. The output and the input of the buffer are related through the equation y(t) = x(t-d), implying that the buffer delays the input by d, which is the settling time of the buffer. If the last transition at the input occured at t = 0, then after delay d, y(t) = x(t-d) involves the input at  $t \ge d$ , i.e., the steady state input and hence, for  $t \ge d$ , y(t) = x(t-d) reduces to the ordinary Boolean function, namely,  $\hat{y} = \hat{x}$

The definition for the timed Boolean function is given below:

- 1. A binary signal space B(t) is a collection of mappings  $f : R \to B$ , where R is the set of real numbers and B = 0, 1.

- 2. A TBF is any function with domain  $B^n(t)$  and range B(t). TBF F:  $B^n(t) \to B(t)$  satisfies the following properties:

- The identity function F (i.e.,  $F(v)(t) = v(t), v(t)\epsilon B(t)$ ) is a TBF.

- If  $G(t) : B^{n1}(t) \to B(t)$  and  $H(t) : B^{n2}(t) \to B(t)$  are TBF's, then,  $\overline{G}, G \cdot H$ , and G + H are also TBF's.

- If F(t) is a TBF, then, for any function φ : R<sup>n</sup> → R, F(φ) is also a TBF.

### 2.7.1 Modeling Timing Behaviors

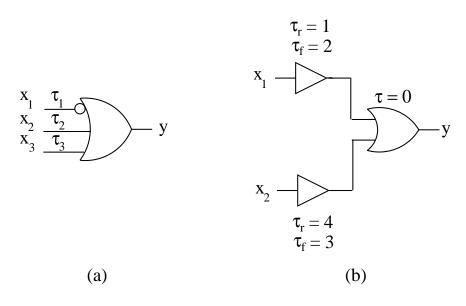

The TBF of a given circuit is obtained by first decomposing the complex gates into simple gates and deriving their TBF representations. A few examples are given below:

Figure 2.17: Modeling with TBF's [19]

1. Gates characterized by a single delay for each input-output pair: In this case, a gate's delay is modeled by the delays of input-output pairs. The complex gate in Figure 2.17(a) has three inputs; input  $x_i$  has a delay  $\tau_i$  to the output, both rising and falling. This gate is modeled by the following TBF:

$$y(t) = \overline{x_1}(t - \tau_1) + x_2(t - \tau_2) + x_3(t - \tau_3)$$

(2.27)

2. Buffer with different rising and falling delays: Let  $\tau_r$  and  $\tau_f$  be the rising and the falling delay of a buffer. The TBF for the buffer with rising delay greater than the falling delay  $(\tau_r > \tau_f)$  is given as follows:

$$y(t) = x(t - \tau_r) \cdot x(t - \tau_f) \tag{2.28}$$

For the case  $\tau_r < \tau_f$ , the TBF is given as follows:

$$y(t) = x(t - \tau_r) + x(t - \tau_f)$$

(2.29)

3. Gates with different rising and falling delays for each input-output pair: In Figure 2.17(b) an OR gate is shown with two inputs: input  $x_1$  has a rising delay of 1 and a falling delay of 2, while input  $x_2$  has a rising delay of 4 and a falling delay of 3. The buffer modeling input 1 has the following TBF:

$$x_1(t-1) + x_1(t-2) \tag{2.30}$$

and the buffer modeling input 2 has the following TBF:

$$x_2(t-4) \cdot x_2(t-3) \tag{2.31}$$

Therfore, the OR gate has the following TBF:

$$y(t) = x_1(t-1) + x_1(t-2) + x_2(t-4) \cdot x_2(t-3)$$

(2.32)

### 2.7.2 Circuit Formulation

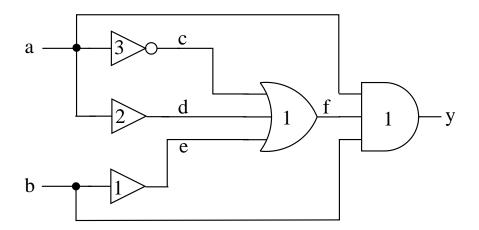

Figure 2.18: An Example Circuit for TBF [19]

Once all of the components are represented by TBF's, the TBF for the circuit can be derived by indentifying the timed variables corresponding to the ports connected to the same net. Consider Figure 2.18, where the TBF at node f is obtained by composing the TBf's of the inverter and the buffers with that of the OR gate. Thus the TBF at f is:

$$f(t) = a(t-3) + \overline{a}(t-4) + b(t-2)$$

(2.33)

The TBF at node y is obtained by composing the TBF at f with that of the AND gate giving:

$$y(t) = a(t-1)b(t-1)f(t-1)$$

(2.34)

$$= a(t-1)b(t-1)(a(t-4) + \overline{a}(t-5) + b(t-3))$$

(2.35)

### 2.8 Summary

In this section various building blocks of the PLL circuit were explained with figures and examples showing how the PLL circuit captures and locks onto a reference signal and also the SERDES architecture was explained. In addition, the formulation of a circuit with timing information using timed Boolean functions was also explained.

# Chapter 3 Jitter Fundamentals – Reduction and Testing

In a multi-gigabit SERDES, its jitter performance is one of the most important parameters for judging the robustness of the design since the bit error rate is directly affected by the jitter performance [9]. For the serializer, a small amount of jitter means that it is less likely that a bit error will occur when the data is received by the Deserializer. There are many factors that can affect a Serializer's output jitter but the key is to keep the high-speed clock that is used for clocking out the serial data as jitter-free as possible. On the receiver side, the deserializer's jitter performance is judged by the maximum amount of jitter riding on the incoming data stream that it can tolerate. Since the received data is retimed by latching the data with the recovered clock, a bit error can occur only if either the clock or data is too early or late. So, in general the deserializer's input jitter tolerance can be improved by making the clock less likely to be early or late and/or making the data less likely to be early or late. In other words, the jitter on the recovered clock and the received data has to be reduced.

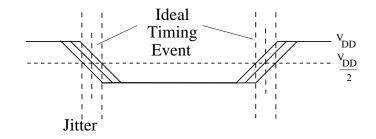

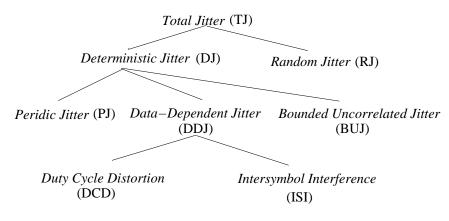

### 3.1 Jitter Fundamentals

Jitter is the deviation of a signal's timing event from its intended (ideal) occurrence in time, as shown in Figure 3.1. Jitter is expressed in absolute time or normalized to a *unit interval* (UI). A UI is the ideal or average time duration of a single bit or the reciprocal of the average data rate [28]. *Total jitter* (TJ) has two subcategories, *deterministic jitter* (DJ) and *random jitter* (RJ). The classification of TJ is shown in Figure 3.2. The TJ's *probability density function* (PDF) is equal

Figure 3.1: Timing Jitter [28]

to the convolution of its RJ and DJ components.

Figure 3.2: Jitter Classification [28]

DJ in turn comprises several subcomponents [28]. Sinusoidal jitter or periodic jitter (PJ) refers to periodic variations of signal edge positions over time. Possible causes of PJ are electromagnetic interference sources such as power supplies. Bounded uncorrelated jitter (BUJ) is typically due to coupling, for example, from adjacent data-carrying links or on-chip random logic switching. Data-dependent jitter (DDJ) corresponds to a variable jitter that depends on the bit pattern transmitted on the link under test. DDJ does not describe jitter induced by crosstalk resulting from coupling with other signal paths. DDJ in turn has two subcomponents. The first DDJ subcomponent, duty-cycle distortion (DCD), describes a jitter amounting to a signal having unequal pulse widths for high and low logic values. Causes of DCD can be voltage offsets between the differential inputs, and

differences between the system's rise and fall times. The second DDJ subcomponent, *intersymbol interference* (ISI) is a most common type of jitter that occurs in a typical wireless communication environment. The data from the transmitter is distorted due to the bandwidth limitation of the channel. The ISI depends on the transmitted bit pattern. With ISI, the timing of each edge of the transmitted signal depends on the bit pattern preceding this edge. Different edge patterns have different frequency components. Fast-changing edge patterns behave as highfrequency signals; slow-changing edge patterns behave as slow-frequency signals. Because of the channel's filtering effects, different edge patterns propagate at different speeds through the channel. The difference in propagation speeds cause bits to smear into adjacent bits, resulting in ISI.

### 3.1.1 Random Jitter

RJ comes from device noise sources, for example, thermal effects and flicker [28]. An example of device noise is shot noise, which is related to a transistor's fluctuation in current flow. Thermal noise is a component of device noise. Electron scattering causes thermal noise when electrons move through a conducting medium and collide with silicon atoms or impurities in the lattice. Higher temperatures result in greater atom vibration and increased chances of collisions. *Flicker noise*, or 1/frequency noise, results from the random capture and emission of carriers from oxide interface traps, which affects carrier density in a transistor. Engineers commonly model RJ by the Gaussian distribution function:

$$J_{RJ}(x) = \frac{1}{\sigma\sqrt{2\pi}} e^{-\frac{(x)^2}{2\sigma^2}}$$

(3.1)

where  $J_{RJ}(x)$  denotes the RJ PDF,  $\sigma$  is the standard deviation of the Gaussian distribution and x is the time displacement relative to the ideal time position. Hence, a Gaussian RJ is completely specified by a single parameter – its standard deviation.

### 3.1.2 Deterministic Jitter

DJ arises from the interaction of different system components [28]. Its major causes include electromagnetic interference, crosstalk, signal reflection, driver slew rate, skin effects and dielectric loss. Electromagnetic interference is the interference from radiated or conducted energy that comes from other devices or systems. Such radiation can induce currents on signal wires and power rails, and alter the signal voltage biases or the reference voltages. Impedance mismatch between the cables or traces and a terminating resistor contributes to signal reflections. As a signal propagates and reaches the receiver, part of the signal energy reflects back toward the transmitter. It is possible to estimate the percentage of reflected energy relative to signal energy. Mismatches in the terminating resistance cause electrons to literally bounce back to the transmitter. This corrupts the succeeding bits and reduces the signal-to-noise ratio. The reflected signal energy bounces back and forth until it dissipates completely. As it bounces, it adds to the original signal out of phase, resulting in jitter.

Above a certain frequency, transmitting conductors experience a skin effect. This is a phenomenon whereby at high frequencies conductor self-inductance causes the current flow to concentrate on the surface of a conducting medium. The onset frequency is a function of the conductor's cross-sectional area, impedance and other material physical parameters. The skin effect increases the conductor's resistance because of the reduction in effective cross-sectional area and leads to increased attenuation of a signal's high-frequency contents. The results are longer rise and fall times, and degraded signal amplitudes. Dielectric loss results from the delay of polarization in the dielectric material when it is subject to a changing electric field. In an ideal lossless material, the current leads the voltage by 90 degrees. But in real material, the delay in polarization creates a phase lag between the external electric field and the resonating molecules, which leads to a phase difference in current, thus causing a power loss. Above some frequencies, dielectric losses dominate skin effect losses because dielectric losses are proportional to

the frequency, while skin effect losses are proportional to the frequency's square root.

The signal slew rate depends on the signal driver's ability to drive its load. A strong driver can provide a fast slew rate and drive higher-frequency signals. When a high-frequency signal's driver is weak, the signal at the opposite end of the wire might not have enough time to rise or fall to the desired signal high or low value.

#### 3.1.2.1 Duty-cycle Distortion (DCD) Model

The sum of two  $\delta$  functions can represent the jitter due to DCD.

$$J_{DCD}(x) = \frac{\delta(x - \frac{W}{2})}{2} + \frac{\delta(x - \frac{W}{2})}{2}$$

(3.2)

where  $J_{DCD}(x)$  is the DCD PDF, W is the peak-to-peak DCD magnitude, and x is the time displacement relative to the ideal time position. The two  $\delta$  functions represent the rising and falling edges of the signal. The magnitude of each  $\delta$ function is 1/2 because the equation assumes that there are equal numbers of rising and falling transitions in the transmitted signal.

#### 3.1.2.2 Periodic Jitter (PJ) Model

A summation of cosine functions with different phases and amplitudes provides a model for PJ:

$$PJ(t) = \sum_{i=0}^{N} A_i \cos(\omega_i t + \theta_i)$$

(3.3)

where PJ(t) denotes the total periodic jitter, N is the number of cosine components (tones),  $A_i$  is the corresponding amplitude,  $\omega_i$  is the corresponding angular frequency, t is the time and  $\theta_i$  is the corresponding phase. The following equation describes the PDF of a single-tone PJ:

$$J_{PJ}(x) = \begin{cases} \frac{1}{\pi\sqrt{A^2 - x^2}} & |x| < A\\ 0 & |x| \ge A \end{cases}$$

(3.4)

where A is the amplitude of the PJ sinusoidal component and x is the time displacement relative to the ideal position. Assume that there is only PJ in the signal. The resulting jitter PDF will then have a concave shape because there will be a higher proportion of samples having jitter magnitudes closer to the sinusoidal peaks than those with smaller jitter magnitudes.

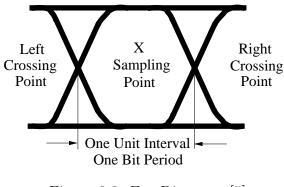

### 3.1.3 Eye Diagram

Figure 3.3: Eye Diagram [5]

The most fundamental intuitive view of jitter is provided by the eye diagram [5]. An eye diagram is a composite view of all bit periods of a captured waveform superimposed upon each other. In other words, the waveform trajectory from the start of period 2 to the start of period 3 is overlaid on the trajectory from the start of period 1 to the start of period 2, and so on for all bit periods. Figure 3.3 shows an idealized eye diagram, very straight and symmetrical with smooth transitions (left and right crossing points), and a large, wide-open eye to provide an ideal location to a sample a bit. At this point the waveform should have settled to its high or low value and is least likely to result in a bit error.

### **3.1.4** Bit-Error-Rate (BER)

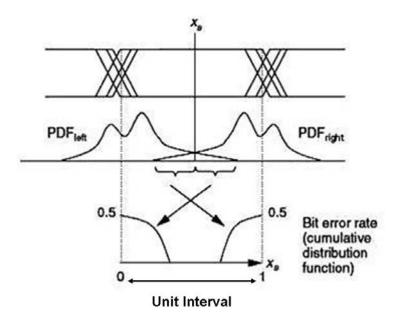

BER is the *cumulative distribution function* (CDF) of the TJ PDFs of the left and right eye crossings over the time interval in which a bit error occurs. In

Figure 3.4: Bit Error Rate [28]