# DIAGNOSIS AND ERROR CORRECTION FOR A FAULT-TOLERANT ARITHMETIC AND LOGIC UNIT FOR MEDICAL MICROPROCESSORS

### BY VARADAN SAVULIMEDU VEERAVALLI

A thesis submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Master of Science Graduate Program in Electrical and Computer Engineering Written under the direction of Prof. Michael L. Bushnell

and approved by

New Brunswick, New Jersey October, 2008

# ABSTRACT OF THE THESIS

# Diagnosis and Error Correction for a Fault-Tolerant Arithmetic and Logic Unit for Medical Microprocessors

# by Varadan Savulimedu Veeravalli Thesis Director: Prof. Michael L. Bushnell

We present a fault tolerant *Arithmetic and Logic Unit* (ALU) for medical systems. Real-time medical systems possess stringent requirements for fault tolerance because faulty hardware could jeopardize human life. For such systems, checkers are employed so that incorrect data never leaves the faulty module and recovery time from faults is minimal. We have investigated information, hardware and time redundancy. After analyzing the hardware, the delay and the power overheads we have decided to use time redundancy as our fault tolerance method for the ALU.

The original contribution of this thesis is to provide single stuck-fault error correction in an ALU using *recomputing with swapped operands* (RESWO). Here, we divide the 32-bit data path into 3 equally-sized segments of 11 bits each, and then we swap the bit positions for the data in chunks of 11 bits. This requires multiplexing hardware to ensure that carries propagate correctly. We operate the ALU twice for each data path operation – once normally, and once swapped. If there is a discrepancy, then either a bit position is broken or a carry propagation

circuit is broken, and we diagnose the ALU using diagnosis vectors. First, we test the bit slices without generating carriers – this requires three or four patterns to exercise each bit slice for stuck-at 0 and stuck-at 1 faults. We test the carry chain for stuck-at faults and diagnose their location – this requires two patterns, one to propagate a rising transition down the carry chain, and another to propagate a falling transition. Knowledge of the faulty bit slice and the fault in the carry path makes error correction possible by reconfiguring MUXes. It may be necessary to swap a third time and recompute to get more data to achieve full error correction.

The hardware overhead with the RESWO approach and the reconfiguration mechanism of one spare chunk for every sixteen chunks for the 64-bit ALU is 78%. The delay overhead for the 64-bit ALU with our fault-tolerance mechanism is 110.96%.

# Acknowledgements

I would like to express my gratitude to everyone who has helped me complete this degree. I am thankful to Prof. Michael Bushnell whose cooperation and encouragement made this work possible. Dr. Bushnell guided me throughout the project and helped me complete it successfully. I would also like to thank Prof. Tapan Chakraborty for his encouragement and help with this project.

I would also like to acknowledge my parents for their support throughout my graduate school years. They stood by me through thick and thin and I would have never achieved anything in my life without their persisting motivation and hard work.

I would like to thank all my friends Aditya, Roystein, Sharanya, Hari Vijay, Rajamani, Omar and Raghuveer. I would especially like to thank the technical staff William Kish and Skip Carter for their support.

# Dedication

To my parents Charumathy and Padmanaban, my grandparents Naryanan and Chellam, my sister Srikrupa, my brother Vignesh, and all my teachers.

# Table of Contents

| Abstract                                           | ii  |

|----------------------------------------------------|-----|

| Acknowledgements                                   | iv  |

| Dedication                                         | v   |

| List of Tables                                     | xi  |

| List of Figures                                    | cii |

| 1. Introduction                                    | 1   |

| 1.1. Contribution of this Research                 | 2   |

| 1.2. Motivation and Justification of this Research | 3   |

| 1.3. Snapshot of Results of the Thesis             | 6   |

| 1.4. Roadmap of the Thesis                         | 7   |

| 2. Prior Work                                      | 8   |

| 2.1. Coding Theory                                 | 9   |

| 2.2. Self-Checking Circuits                        | 10  |

| 2.3. Error-Detecting and Error-Correcting Codes    | 11  |

| 2.3.1. Two-Rail Checker (TRC)                      | 11  |

| 2.3.2. Berger Codes                                | 12  |

| 2.3.3. Hamming Codes                               | 13  |

| 2.3.3.1. Hamming Distance                          | 14  |

| 2.3.3.2. Single Error Correcting Code              | 15  |

| 2.3.4. Reed Solomon (RS) Codes                     | 16  |

|        |          | 2.3.4.1.   | Architectures for Encoding and Decoding Reed |    |

|--------|----------|------------|----------------------------------------------|----|

|        |          |            | Solomon Codes                                | 17 |

|        |          | 2.3.4.2.   | Encoder Architecture                         | 17 |

|        |          | 2.3.4.3.   | Decoder Architecture                         | 18 |

|        | 2.3.5.   | Residue    | Codes                                        | 19 |

|        | 2.3.6.   | IBM's R    | esearch on Error Correcting Codes            | 21 |

| 2.4.   | Hardw    | vare Redu  | ndancy                                       | 22 |

|        | 2.4.1.   | Duplicat   | tion of the Hardware                         | 22 |

|        | 2.4.2.   | Triple M   | lodular Redundancy                           | 22 |

| 2.5.   | Time 1   | Redundar   | ncy                                          | 25 |

|        | 2.5.1.   | Recomp     | uting with Shifted Operands (RESO)           | 26 |

|        | 2.5.2.   | Recomp     | uting with Alternating Logic                 | 27 |

|        | 2.5.3.   | Recomp     | uting with Swapped Operands (RESWO)          | 29 |

| 2.6.   | Fault    | Diagnosis  |                                              | 30 |

| 2.7.   | Summ     | ary – Bes  | t of Prior Methods                           | 31 |

| 3. Fau | lt-Tole  | erant Teo  | chnique for an ALU – Implementation Study    |    |

| and Ju | stificat | tion       |                                              | 32 |

| 3.1.   | Archit   | ecture of  | the ALU                                      | 32 |

|        | 3.1.1.   | Adders     |                                              | 34 |

|        |          | 3.1.1.1.   | Brent-Kung Adder                             | 35 |

|        |          | 3.1.1.2.   | Kogge-Stone Adder                            | 35 |

|        |          | 3.1.1.3.   | Sklansky Adder                               | 35 |

|        | 3.1.2.   | Multipli   | ers                                          | 36 |

|        |          | 3.1.2.1.   | Booth Encoding Multiplier                    | 37 |

|        |          | 3.1.2.2.   | Wallace Tree Multiplication                  | 38 |

|        |          | 3.1.2.3.   | Dadda Tree Multiplication                    | 39 |

| 3.2.   | Justifi  | cation for | Recomputing Using Swapped Operands for Fault |    |

|        | Tolera   | nce        |                                              | 40 |

|     |      | 3.2.1. | Why Inf    | ormation Redundancy Is Not Useful                                                                   | 40 |

|-----|------|--------|------------|-----------------------------------------------------------------------------------------------------|----|

|     |      | 3.2.2. | Why Ha     | rdware Redundancy Is Not Useful                                                                     | 42 |

|     |      | 3.2.3. | Why the    | e other Time-redundancy Mechanisms Are Not Useful                                                   | 43 |

|     | 3.3. | Result | s          |                                                                                                     | 43 |

|     | ъ.   | •      |            |                                                                                                     |    |

|     |      | -      |            | Using RESWO and Test Vectors and Recon-                                                             | 10 |

| fig |      |        |            | Correction                                                                                          | 46 |

|     | 4.1. | Diagn  | osis Meth  | od                                                                                                  | 46 |

|     |      | 4.1.1. | Fault Di   | $\operatorname{ctionary}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 47 |

|     |      | 4.1.2. | Diagnosi   | s Tree                                                                                              | 47 |

|     |      | 4.1.3. | Why We     | e Use a Diagnosis Tree                                                                              | 48 |

|     | 4.2. | Comp   | arison wit | h Alternative Methods                                                                               | 48 |

|     |      | 4.2.1. | Impleme    | entation of Diagnosis for ALU                                                                       | 48 |

|     |      |        | 4.2.1.1.   | Design the ALU as One Piece                                                                         | 49 |

|     |      |        | 4.2.1.2.   | Design the ALU with Reconfigurable 4-bit ALU                                                        |    |

|     |      |        |            | Chunks                                                                                              | 49 |

|     |      |        | 4.2.1.3.   | Design the ALU with Reconfigurable 2-bit ALU                                                        |    |

|     |      |        |            | Chunks                                                                                              | 49 |

|     |      |        | 4.2.1.4.   | Design the Boolean, Addition, Subtraction and                                                       |    |

|     |      |        |            | Shifting Operations Using Reconfigurable 2-bit ALU                                                  |    |

|     |      |        |            | Chunks. Design the Multiplier Separately                                                            | 50 |

|     |      |        | 4.2.1.5.   | Design the Boolean, Addition, Subtraction and                                                       |    |

|     |      |        |            | Shifting Operations Using Reconfigurable 1-bit ALU                                                  |    |

|     |      |        |            | Chunks. Design the Multiplier Separately                                                            | 52 |

|     |      | 4.2.2. | Minimal    | Test Set for 100% Fault Detection                                                                   | 52 |

|     | 4.3. | Result |            |                                                                                                     | 55 |

|     |      |        |            |                                                                                                     |    |

| 5.  | Opt  | imal F | Reconfigu  | aration Scheme for the ALU                                                                          | 57 |

|     | 5.1. | Recon  | figuration | Analysis                                                                                            | 57 |

|     | 5.2. | Recon  | figuration | Schemes                                                                                             | 58 |

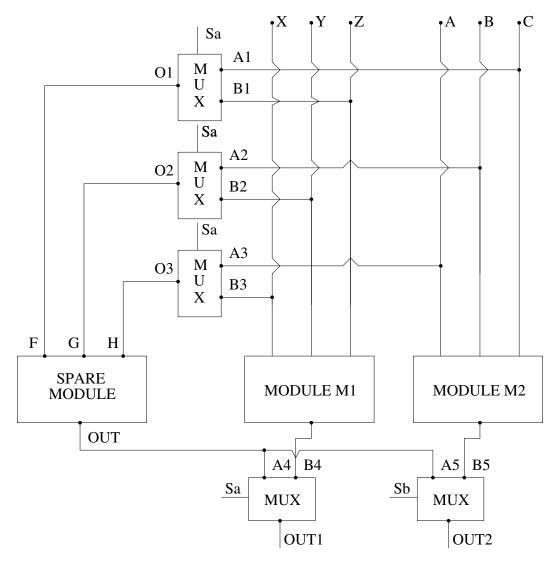

|              |       | 5.2.1. For Every Two Chunks Provide One Spare Chunk              | 59 |

|--------------|-------|------------------------------------------------------------------|----|

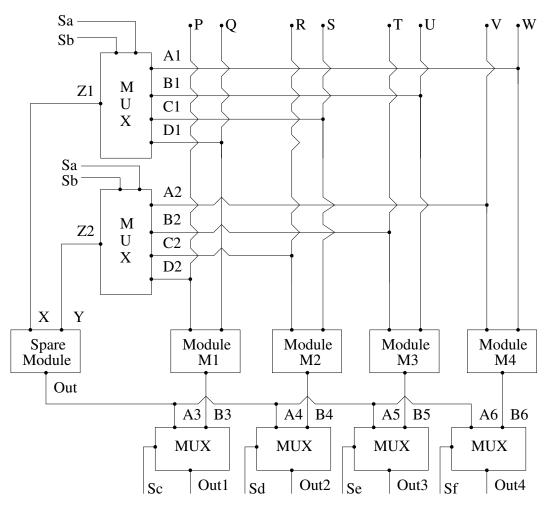

|              |       | 5.2.2. For Every Four Chunks Provide One Spare Chunk             | 61 |

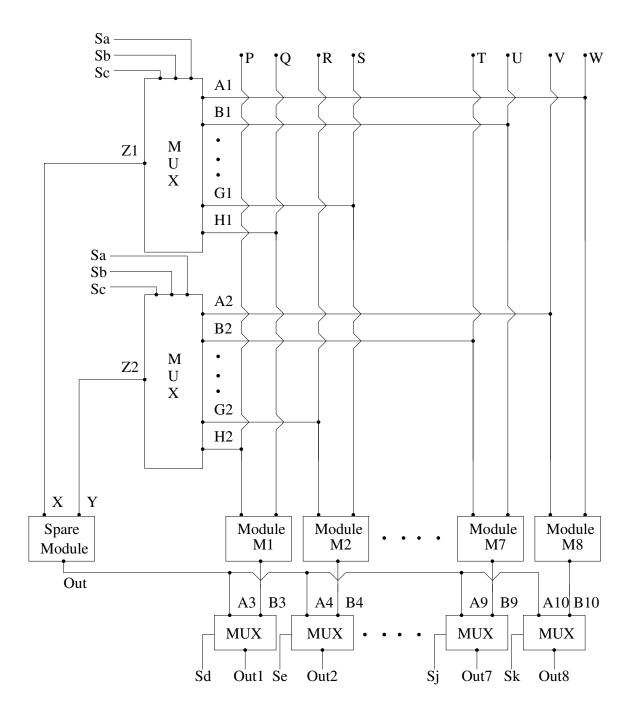

|              |       | 5.2.3. For Every Eight Chunks Provide One Spare Chunk            | 63 |

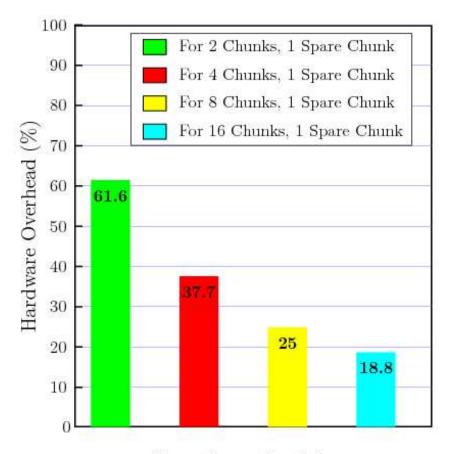

|              |       | 5.2.4. For Every Sixteen Chunks Provide One Spare Chunk $\ldots$ | 65 |

|              | 5.3.  | Hardware Overheads of Different Types of Reconfiguration Schemes |    |

|              |       | 66                                                               |    |

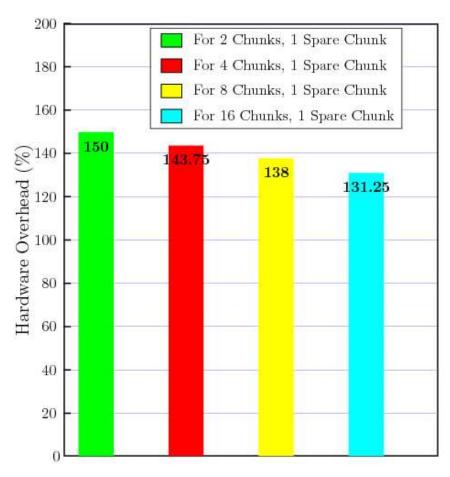

|              |       | 5.3.1. ALU Without Multiplier                                    | 66 |

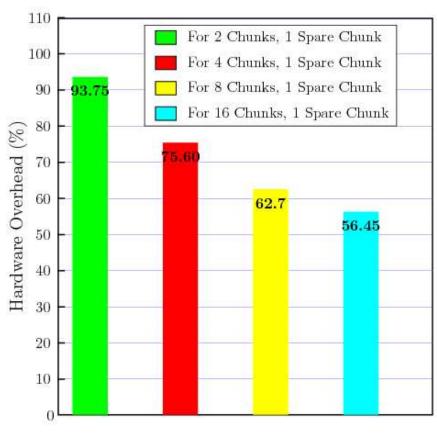

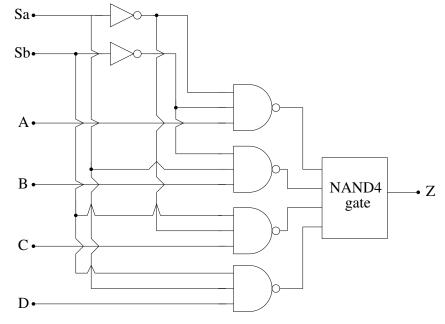

|              |       | 5.3.2. Booth Encoder                                             | 68 |

|              |       | 5.3.3. Booth Selector                                            | 70 |

|              |       | 5.3.4. Full Adder and Half Adder                                 | 70 |

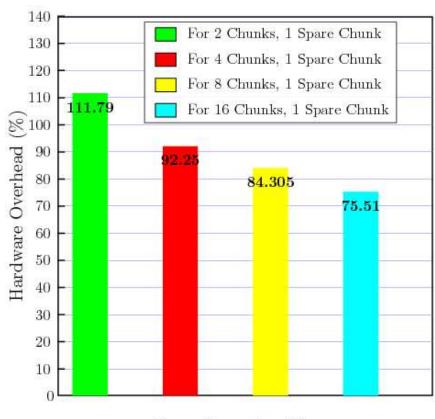

|              |       | 5.3.5. Carry Propagation Adder                                   | 74 |

|              | 5.4.  | Results                                                          | 74 |

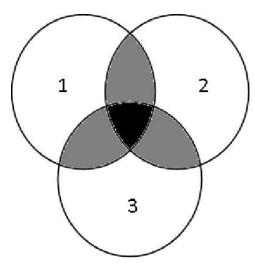

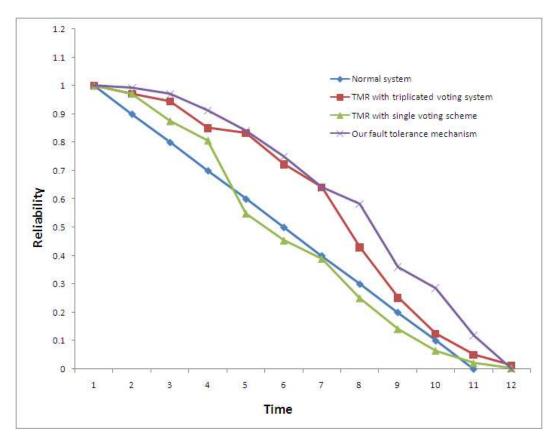

| 6.           | Reli  | iability Analysis                                                | 78 |

|              | 6.1.  | TMR with Single Voting Mechanism                                 | 78 |

|              | 6.2.  | TMR with Triplicated Voting Mechanism                            | 79 |

|              | 6.3.  | Our Fault-Tolerance Mechanism                                    | 80 |

|              | 6.4.  | Results                                                          | 83 |

| 7.           | Con   | clusions and Future Research                                     | 84 |

|              | 7.1.  | Statement of Original Ideas                                      | 84 |

|              | 7.2.  | Comparison of Our Scheme                                         | 85 |

|              |       | 7.2.1. TMR Single Voting Mechanism                               | 85 |

|              |       | 7.2.2. TMR Triplicated Voting Mechanism                          | 86 |

|              |       | 7.2.3. Residue Codes and RESWO Checkers as Fault-Tolerance       |    |

|              |       | Mechanisms                                                       | 86 |

|              | 7.3.  | Statement of Results                                             | 87 |

|              | 7.4.  | Benefits of Our Scheme                                           | 89 |

|              | 7.5.  | Future Work Directions                                           | 90 |

| $\mathbf{R}$ | efere | nces                                                             | 91 |

| Appendix A. Validation of ALU Design                           | 97  |

|----------------------------------------------------------------|-----|

| Appendix B. Validation of Fault-Tolerance Method               | 100 |

| Appendix C. Validation of Reconfiguration Method               | 103 |

| Appendix D. Reliability Analysis Calculations                  | 107 |

| Appendix E. Testing of the ALU with the Reconfiguration Mecha- | •   |

| nism                                                           | 117 |

# List of Tables

| 1.1. | Diagnosis Vectors for Booth Encoded Dadda Tree Multiplier $\ . \ .$ . | 6   |

|------|-----------------------------------------------------------------------|-----|

| 2.1. | Hardware Overhead of Berger Code                                      | 12  |

| 2.2. | Types of Hamming Code                                                 | 16  |

| 3.1. | Results for a 16-bit ALU                                              | 44  |

| 3.2. | RESWO Implementation for Different Architectures of the ALU .         | 44  |

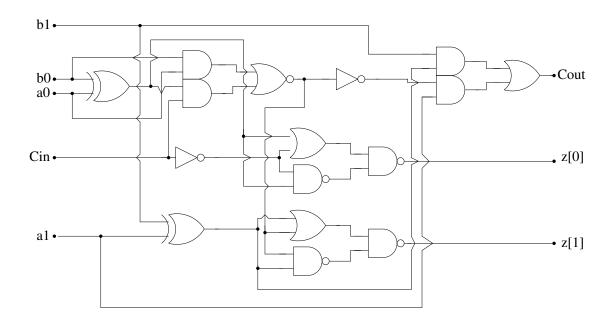

| 4.1. | Test Vectors for the Booth Selector Circuit                           | 53  |

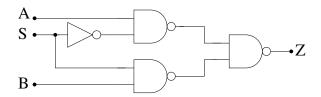

| 4.2. | Test Vectors for the Full Adder Circuit                               | 54  |

| 4.3. | Test Vectors for the Half Adder Circuit                               | 55  |

| 4.4. | Diagnosis Vectors for Different Diagnosis Implementations             | 55  |

| 4.5. | Diagnosis Vectors for Booth Encoded Dadda Tree Multiplier $\ . \ .$   | 56  |

| 6.1. | Reliability for TMR with Single Voting Mechanisms                     | 80  |

| 6.2. | Reliability for TMR with Triplicated Voting Mechanisms $\ . \ . \ .$  | 81  |

| 6.3. | Reliability for our Fault-Tolerance Mechanism                         | 82  |

| 7.1. | Diagnosis Vectors for Booth Encoded Dadda Tree Multiplier             | 88  |

| C.1. | Reconfiguration of the 64-bit ALU                                     | 104 |

| D.1. | Reliability Analysis                                                  | 115 |

| E.1. | Fault Coverage of Different Circuits                                  | 119 |

# List of Figures

| 1.1.  | Variation of SER with Technology                                      | 4  |

|-------|-----------------------------------------------------------------------|----|

| 2.1.  | Typical Diagram of a System with an Error Correcting Code             | 10 |

| 2.2.  | Logic Diagram of a TRC                                                | 11 |

| 2.3.  | Block Diagram of Berger Code                                          | 12 |

| 2.4.  | Block Diagram of Check Bit Generator for 7 Information Bits $\ . \ .$ | 13 |

| 2.5.  | Block Diagram of Hamming Code                                         | 14 |

| 2.6.  | Diagram for Hamming Distance                                          | 15 |

| 2.7.  | Block Diagram of System with Reed Solomon Code                        | 16 |

| 2.8.  | Typical Block Diagram of Reed Solomon Encoder                         | 18 |

| 2.9.  | Typical Block Diagram of Reed Solomon Decoder                         | 18 |

| 2.10. | . Block Diagram of System with Duplication of Hardware Mechanism      | 23 |

| 2.11. | . Triple Redundancy as Originally Envisaged by Von Neumann            | 23 |

| 2.12. | . Triple Modular Redundant Configuration                              | 24 |

| 2.13. | . Time Redundancy for Permanent Errors                                | 26 |

| 2.14. | Structure of RESO System                                              | 27 |

| 2.15. | . Structure of Recomputing with Alternating Logic System              | 28 |

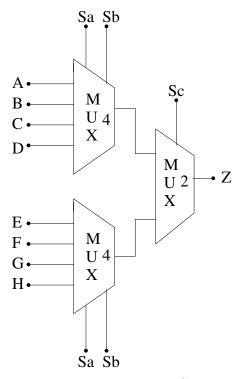

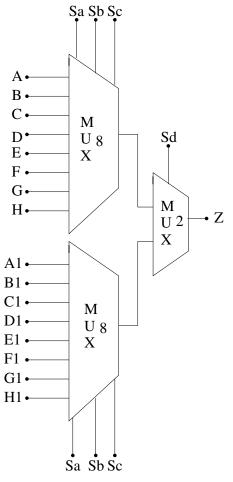

| 2.16. | Structure of RESWO System                                             | 29 |

| 3.1.  | Sklansky Tree Adder                                                   | 36 |

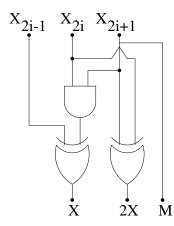

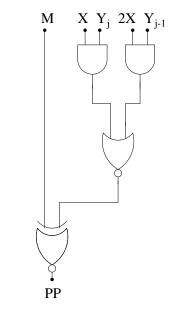

| 3.2.  | Radix-4 Booth Encoder and Selector                                    | 37 |

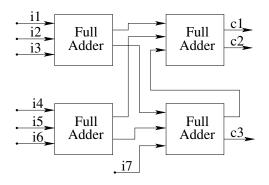

| 3.3.  | Wallace Tree Multiplier                                               | 39 |

| 3.4.  | Dadda Tree Multiplier                                                 | 40 |

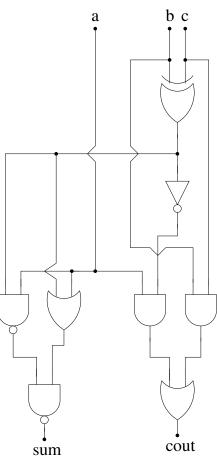

| 4.1.  | Booth Selector Circuit                                                | 53 |

| 4.2.  | Full Adder Circuit                                                    | 53 |

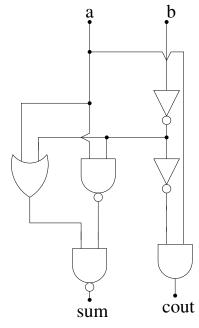

| 4.3. | Half Adder Circuit                                               | 54  |

|------|------------------------------------------------------------------|-----|

| 5.1. | Reconfiguration Scheme – For Every Two Chunks Provide One        |     |

|      | Spare Chunk                                                      | 60  |

| 5.2. | Reconfiguration Scheme – For Every Four Chunks Provide One       |     |

|      | Spare Chunk                                                      | 61  |

| 5.3. | Reconfiguration Scheme – For Every Eight Chunks Provide One      |     |

|      | Spare Chunk                                                      | 64  |

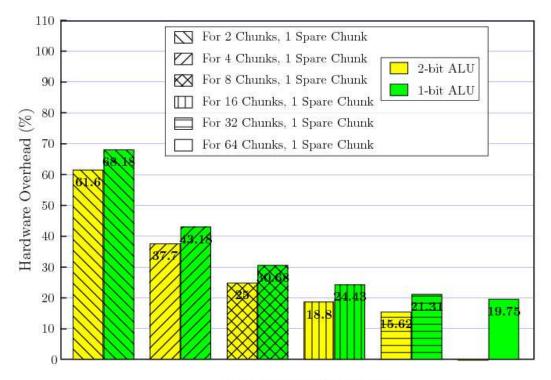

| 5.4. | Hardware Overhead of 2-bit ALU Chunks with Different Reconfig-   |     |

|      | uration Schemes                                                  | 66  |

| 5.5. | Hardware Overhead Comparison of 2-bit ALU and 1-bit ALU Chunks   |     |

|      | with Different Reconfiguration Schemes                           | 67  |

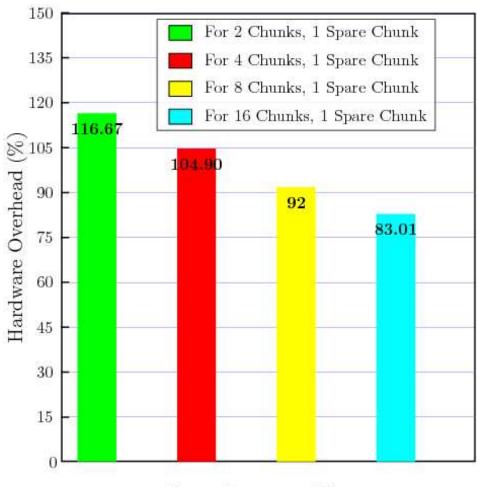

| 5.6. | Hardware Overhead of Booth Encoder with Different Reconfigura-   |     |

|      | tion Schemes                                                     | 69  |

| 5.7. | Hardware Overhead of Booth Selector with Different Reconfigura-  |     |

|      | tion Schemes                                                     | 71  |

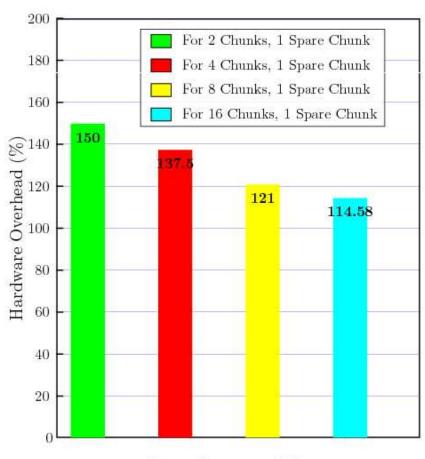

| 5.8. | Hardware Overhead of Full Adder with Different Reconfiguration   |     |

|      | Schemes                                                          | 72  |

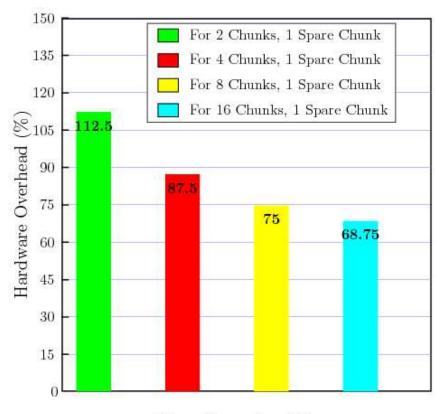

| 5.9. | Hardware Overhead of Half Adder with Different Reconfiguration   |     |

|      | Schemes                                                          | 73  |

| 5.10 | . Hardware Overhead of Carry Propagation Adder with Different    |     |

|      | Reconfiguration Schemes                                          | 75  |

| 5.11 | . Hardware Overhead of the 64-bit ALU (Including the Multiplier) |     |

|      | with Different Reconfiguration Schemes                           | 76  |

| 6.1. | Venn Diagram of Triple Modular Redundant System                  | 79  |

| 6.2. | Reliability of Different Fault-Tolerance Mechanisms              | 83  |

| D.1. | Full Adder Circuit                                               | 108 |

| D.2. | Half Adder Circuit                                               | 109 |

| D.3. | Booth Encoder Circuit                                            | 110 |

| D.4. | Booth Selector Circuit                                           | 110 |

| D.5. | Carry Propagation  | Circuit |       | <br> | <br> | • | <br>• |  | • | • | 111 |

|------|--------------------|---------|-------|------|------|---|-------|--|---|---|-----|

| D.6. | 2:1 MUX Circuit    |         |       | <br> | <br> | • |       |  |   | • | 112 |

| D.7. | 4:1 MUX Circuit    |         |       | <br> | <br> | • |       |  |   | • | 112 |

| D.8. | 8:1 MUX Circuit    |         |       | <br> | <br> | • |       |  |   |   | 113 |

| D.9. | 16:1 MUX Circuit   |         |       | <br> | <br> |   |       |  |   |   | 114 |

| E.1. | Fault Coverage for | the ALU | • • • | <br> | <br> | • |       |  |   |   | 117 |

# Chapter 1 Introduction

The role of electronics in every branch of science has become pivotal. Integrated circuits, digital and analog, are used extensively in applications ranging from medical to home-automation. System reliability has been a major concern since the dawn of the electronic digital computer age [61]. As the scale of integration increased from small/medium to large and to today's very large scale, the reliability per basic function has continued its dramatic improvement [24]. Due to the demand for enhanced functionality, the complexity of contemporary computers, measured in terms of basic functions, rose almost as fast as the improvement in the reliability of the basic component. Secondly, our dependence on computing systems has grown so great that it becomes impossible to return to less sophisticated mechanisms. Previously, reliable computing has been limited to military, industrial, aerospace, and communications applications in which the consequence of computer failure had significant economic impact and/or loss of life [3, 41]. Today even commercial applications require high reliability as we move towards a cashless/automated life-style. Reliability is of critical importance in situations where a computer malfunction could have catastrophic results. Reliability is used to describe systems in which it is not feasible to repair (as in computers on board satellites) or in which the computer is serving a critical function and cannot be lost even for the duration of a replacement (as in flight control computers on an aircraft) or in which the repair is prohibitively expensive. Systems that tolerate failures have been of interest since the 1940's [45] when computational engines were constructed from relays.

#### 1.1 Contribution of this Research

The main aim of this research is to come up with a new fault-tolerant scheme for an *Arithmetic and Logic Unit* (ALU), with a better hardware and power overhead compared to the current fault tolerance techniques. In order to achieve this, we will employ single stuck-fault error correction in an ALU using *recomputing with swapped operands* (RESWO). Here, we divide the 32-bit data path into 3 equallysized segments of 11 bits each, and then we swap the bit positions for the data in chunks of 11 bits. This requires multiplexing hardware to ensure that carries propagate correctly. We operate the ALU twice for each data path operation – once normally, and once swapped. If there is a discrepancy, then either a bit position is broken or a carry propagation circuit is broken, we diagnose the ALU using special diagnosis vectors. Knowledge of the faulty bit slice and the fault in the carry path makes error correction possible.

A diagnosis test is characterized by its diagnostic resolution, defined as the ability to get closer to the fault. When a failure is indicated by a pass/fail type of test in a system that is operating in the field, a diagnostic test is applied. We have employed different types of diagnosis mechanisms for the ALU. We found that the best diagnosis mechanism for the 64-bit ALU is designing the Boolean, addition, subtraction and shifting operations with thirty two reconfigurable 2bit ALU chunks and designing the multiplier separately. We had to split the multiplier into identical bit slices of Booth encoders, Booth selectors, full adders, half adders and carry propagation adders. It was easy to reconfigure the multiplier once it was split into identical bit slices.

If a fault is detected and a permanent failure located, the system may be able to reconfigure its components to replace the failed component or to isolate it from the rest of the system [24]. The component may be replaced by backup spares. We employed different reconfiguration schemes for the 64-bit ALU. We decided that the best reconfiguration mechanism for the 64-bit ALU is to use one spare chunk for every sixteen chunks. The reconfiguration mechanism of one spare chunk for every sixteen chunks can correct up to four faults, provided that they are not in the same sixteen-bit chunk.

### **1.2** Motivation and Justification of this Research

The reason for the use of the fault-tolerant design is to achieve a reliability or availability that cannot be attained by the fault-intolerant design. The main argument against the use of fault-tolerance techniques in computer systems has been the cost of redundancy. High performance general-purpose computing systems are very susceptible to transient errors and permanent faults. As performance demand increases, fault tolerance may be the only course to building commercial systems. The most stringent requirement for fault-tolerance is in real time control systems, where faulty computation could jeopardize human life or have high economic impact. Computations must not only be correct, but recovery time from faults must be minimized. Specially designed hardware must be employed with fault-tolerance mechanisms so that incorrect data never leaves the faulty module.

As the dimensions and operating voltages of electronic devices are reduced to satisfy the ever-increasing demand for higher density and low-power, their sensitivity to radiation increases dramatically. A soft error arises in the system upon exposure to high energy radiation (cosmic rays,  $\alpha$  particles, neutrons, etc.). In the past, soft errors were primarily a concern only in space applications. Significant single event upsets (SEUs) arise due to  $\alpha$  particle emissions from minute traces of radioactive elements in packaging materials [7]. Even though SEUs are the preponderant phenomenon, there are important instances in which multiple event upsets occur. Multiple event upsets are those where an incident heavy ion can cause a SEU in a string of memory cells, in a microcircuit, that happen to lie physically along the penetration ion track. The problem gets severe and recurrent with shrinking device geometry. Shorter channel lengths mean fewer number of charge carriers, resulting in a smaller value of critical charge. The critical charge of a memory array storage cell is defined as the largest charge that can be injected without changing the cell's logic state. SEUs were initially associated with small and densely packed memories, but are now commonly observed in combinational circuits and latches. Exponential growth in the amount of transistors in microprocessors and digital signal processors has led the *soft error rate* (SER) to increase with each generation, with no end in sight. The most effective method of dealing with soft errors in memory components is to use additional circuits for error detection and correction.

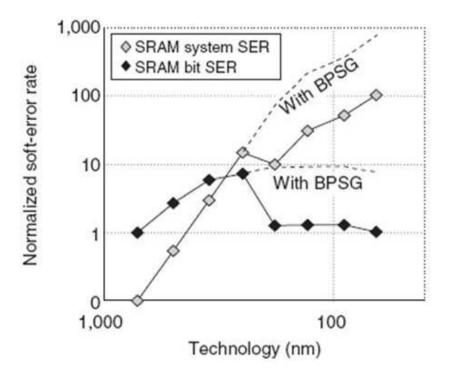

Figure 1.1: Variation of SER with Technology [8]

Figure 1.1 illustrates the variation of soft-error rate with respect to chip technology [8]. This trend is of great concern to chip manufacturers since SRAM constitutes a large part of all advanced integrated circuits today. The soft-error rate is measured in units of *failures in time* (FITs). One FIT is equivalent to one failure in 1 billion  $(10^9)$  operational hours.

As the complexity of microelectronic components continues to increase, design

and reliability engineers will need to address several key areas to enable advanced SoC (System-on-a-chip) products in the commercial sector. The first challenge will be to develop improved and more accurate system level modeling of soft errors including not just device and component failure rates but architectural and algorithmic dependencies as well [9]. With these improved models, the next challenge will be to develop optimized memory and logic mitigation designs that offer a good balance between performance and robustness against soft errors and *single energy transients* (SETs). The last challenge will be the development of viable commercial fault-tolerant solutions that will render complex systems relatively insensitive to soft errors at the operation level.

Fault tolerance is no longer an exotic engineering discipline rather than it is becoming as fundamental to computer design as logic synthesis. Designs will be compared and contrasted not only by their cost, power consumption, and performance but also by their reliability and ability to tolerate failures. These countermeasures never come for free and impact the cost of system being developed. Also, the resulting system will be slower and may feature an increased block size. There will always be a trade–off between cost, efficiency and fault-tolerance and it will be a judgment call by designers, developers and users to choose which of these requirements best suit their needs.

We need a better fault-tolerance mechanism for the ALU that has the hardware overhead lower than 100% because the current fault-tolerance mechanisms have the hardware overhead more than 200%. In this research our top priority is the hardware overhead, then the power and the delay overheads. There is no fault-tolerance mechanism that can handle both the transient errors and the permanent errors. Our main goal here is to come up with a fault-tolerance mechanism than can handle both the hard and the soft errors with a hardware overhead not more than 100%.

#### **1.3** Snapshot of Results of the Thesis

We used time redundancy as the fault-tolerance mechanism for the ALU after a very brief analysis. We chose *REcomputing with SWapped Operands* (RESWO) as it had 5.3% lower hardware, 9.06% lower power and 3.26% lower delay overheads than *Recomputing with Alternating Logic*. The RESWO approach has been shown to be less expensive, particularly when the complexity of individual modules of the circuit is high. Once a fault is detected in the ALU using the RESWO approach we diagnose the ALU with diagnosis vectors and locate the fault.

When there is a discrepancy in the circuit (either a bit position is broken or a carry propagation circuit is broken), we diagnose the ALU using special diagnosis vectors. We have implemented different diagnosis mechanisms for the ALU. After a very brief analysis we found that the best diagnosis mechanism for the 64-bit ALU is designing the Boolean, addition, subtraction and shifting operations with thirty two reconfigurable 2-bit chunks and designing the multiplier separately. We had to split the multiplier into identical bit slices of Booth encoders, Booth Selectors, full adders and carry propagation adders.

| Architecture                 | Number of         |

|------------------------------|-------------------|

|                              | Diagnosis Vectors |

| 2-bit ALU without Multiplier | 22                |

| Booth Encoder                | 7                 |

| Booth Selector               | 4                 |

| Full Adder                   | 5                 |

| Half Adder                   | 4                 |

| Carry Propagation Adder      | 7                 |

Table 1.1: Diagnosis Vectors for Booth Encoded Dadda Tree Multiplier

Once the fault is located we have to reconfigure the circuit and remove the faulty part. We developed different reconfiguration mechanisms for the 64-bit ALU. After analyzing all the reconfiguration mechanisms we decided to use one spare chunk for every sixteen chunks as our reconfiguration mechanism because it has a much lower hardware overhead of 78% (2.49% of this overhead is for the

RESWO checkers) compared to the hardware overheads of TMR with single voting mechanism (201.87%) and TMR with triplicated voting mechanism (207.5%) and an error correction rate of 6.25%.

Reliability analysis showed that our fault-tolerance mechanism is better than the current fault-tolerant mechanisms. If the reliability of all the sub-modules of the 64-bit ALU with fault-tolerance mechanism is 90%, then the entire system reliability is 99.99%.

#### 1.4 Roadmap of the Thesis

This thesis is organized as follows. In Chapter 2 we survey the related work. In this chapter we present a detailed introduction to the different fault-tolerant techniques (error detecting and error correcting codes), diagnosis and reconfiguration. The next chapter describes the architecture and the most optimum fault-tolerant mechanism for the *Arithmetic and Logic Unit* ALU. Chapter 4 explains the different implementations of diagnosis mechanisms with an analysis and results. Chapter 5 describes the different implementations of reconfiguration mechanisms with a brief analysis and results. Chapter 6 explains the reliability of different fault-tolerance mechanisms. Chapter 7 concludes this thesis. The first section gives us the essence of the work and the last section discusses the directions for this work in the future.

# Chapter 2 Prior Work

In fault tolerance, we will discuss prior work focusing on *information*, *hardware* and *time* redundancy. First, we will review the work that has been done in the area of fault tolerance. Then we will discuss the different fault-tolerant mechanisms. Later we will discus the work done in diagnosis and reconfiguration of *Arithmetic* and Logic Units (ALUs).

Systems that tolerate failures have been of interest since the 1940's when computational engines were constructed from relays. Fault detection provides no tolerance to faults, but gives warning when they occur [45]. If the dominant form of faults is transient/intermittent, recovery can be initiated by a retry invoked from a previous checkpoint in the system at whose time the system state was known to be good. Design errors, whether in hardware or software, are those caused by improper translation of a concept into an operational realization [2, 4, 6, 38]. The three major axes of the space of fault-tolerant designs are: system application, system structure, and fault-tolerant technique employed [60]. The most stringent requirement for fault tolerance is in real-time control systems, where faulty computation could jeopardize human life or have high economic impact [56]. Computations must not only be correct, but recovery time from faults must be minimized. Specially designed hardware is employed with concurrent error detection so that incorrect data never leaves the faulty module [43].

Major error-detection techniques include *duplication* (frequently used for random logic) and *error detecting codes* [36]. Recovery techniques can restore enough of the system state to allow a process execution to restart without loss of acquired information. There are two basic approaches: *forward* and *backward* recovery.

Forward recovery attempts to restore the system by finding a new state from which the system can continue operation. Backward recovery attempts to recover the system by rolling back the system to a previously saved state, assuming that the fault manifested itself after the saved state. Forward error recovery, which produces correct results through continuation of normal processing, is usually highly application-dependent [53]. Backward recovery techniques require some redundant process and state information to be recorded as computations progress. Error detection and correction codes have proven very effective for regular logic such as memories and memory chips have built-in support for error detection and correcting codes [36, 40, 51]. With the ever-increasing dominance of transient and intermittent failures, retry mechanisms will be built into all levels of the system as the major error-recovery mechanism [3, 41]. Fault tolerance is no longer an exotic engineering discipline; rather, it is becoming as fundamental to computer design as logic synthesis. Designs will be compared and contrasted not only by their cost, power consumption, and performance but also by their reliability and ability to tolerate failures [61].

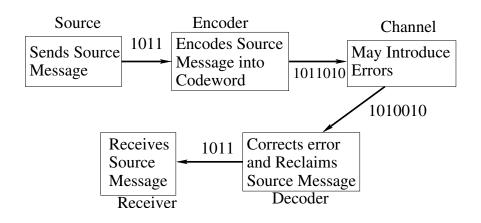

## 2.1 Coding Theory

A stream of source data, in the form of zeros and ones, is being transmitted over a communications channel, such as telephone line [12]. How can we tell that the original data has been changed, and when it has, how can we recover the original data? Here are some easy things to try: Do nothing. If a channel error occurs with probability p, then the probability of making a decision error is p. Send each bit 3 times in succession. The bit gets picked by a majority voting scheme. If errors occur independently, then the probability of making a decision error is  $3p^2 - 2p^3$ , which is less than p for p < 1/2. Generalize the above; Send each bit n times and choose the majority bit. In this way, we can make the probability of making a decision error arbitrarily small, but communications are inefficient in terms of transmission rate. From the above suggestion we see the basic elements of encoding of data: Encode the *source information*, by adding additional information, sometimes referred to as *redundancy*, which can be used to detect, and perhaps correct, errors in transmission. The more redundancy we add, the more reliably we can detect and correct errors but the less efficient we become at transmitting the source data.

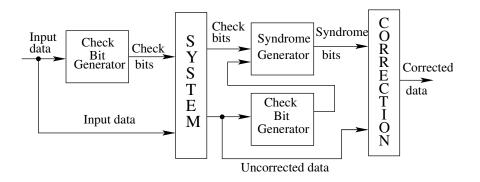

Figure 2.1: Typical Diagram of a System with an Error Correcting Code

# 2.2 Self-Checking Circuits

- Definition I: A combinational circuit is self-testing for a fault set F if and only if for every fault in F, the circuit produces a non-codeword output during normal operation for atleast one input code word [40, 63, 65]. Namely, if during normal circuit operation any fault occurs, this property guarantees an error indication.

- Definition II: A combinational circuit is Strongly-Fault-Secure (SFS) for a fault set F iff, for every fault in F, the circuit never produces an incorrect output code-word [26, 65].

- Definition III: A combinational circuit is Self-Checking circuit SCC for a fault set F iff, for every fault n F, the circuit is both self-testing and strongly fault secure [13, 63, 65].

## 2.3 Error-Detecting and Error-Correcting Codes

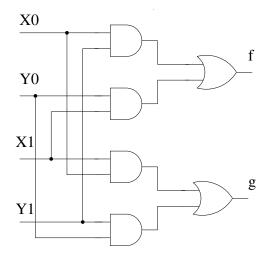

## **2.3.1** Two-Rail Checker (TRC)

A one bit output is insufficient for a *Totally Self-Checking* (TSC) circuit since a stuck-at-fault on the output resulting in the "good" output could not be detected [36, 40, 51, 65]. The output of a TSC circuit is typically encoded using a two rail (1-out-of-2) code. The checker is said to be TSC circuit iff, under the fault

Figure 2.2: Logic Diagram of a TRC

models:

- 1. The output of the checker is 01 or 10 whenever the input is a code word (strongly-fault-secure property).

- 2. The output is 00 or 11 whenever the input is not a code word (*code-disjoint* property).

- 3. Faults in the checker are detectable by test inputs that are code words and, under fault-free condition, for at least two inputs X and Y, the checker outputs are 01 and 10, respectively.

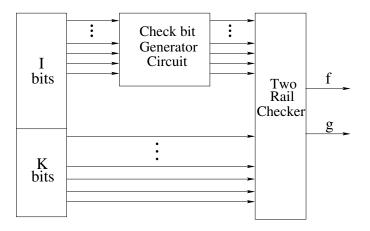

## 2.3.2 Berger Codes

Berger codes are perfect error detection codes in a *completely asymmetric channel*. A completely asymmetric channel is one in which only one type of error occurs, either only zeros converted to ones or only ones converted to zeros. They are separable codes [10]. The Berger code counts the number of 1's in the word and expresses it in binary. It complements the binary word, and appends the count to the data. Berger codes are optimal systematic AUED (*All Unidirectional Error*)

Figure 2.3: Block Diagram of Berger Code

| Information | Check      | Overhead |

|-------------|------------|----------|

| Bits $(k)$  | Bits $(c)$ |          |

| 4           | 3          | 0.7500   |

| 8           | 4          | 0.5000   |

| 16          | 5          | 0.3125   |

| 32          | 6          | 0.1875   |

| 64          | 7          | 0.1094   |

| 128         | 8          | 0.0625   |

| 256         | 9          | 0.0352   |

| 512         | 10         | 0.0195   |

Table 2.1: Hardware Overhead of Berger Code

Detecting) codes [36, 40, 51]. A code is optimal if it has the highest possible information rate (i.e., c/n). A code is systematic if there is a generator matrix for the code. It is optimal because the check symbol length is minimal for the Berger

code compared to all other systematic codes. Less logic is required to implement the Berger check error detection. It detects all unidirectional bit errors, i.e, if

Figure 2.4: Block Diagram of Check Bit Generator for 7 Information Bits

one or more ones turn into zeros it can be identified, but at the same time, zeros converted into ones cannot be identified. If the same number of bits flips from one to zero as from zero to one, then the error will not be detected. If the number of data bits is k, then the check bits (c) are equal to  $\log_2(k+1)$  bits. Hence, the overhead is  $\log_2((k+1)/k)$ . These codes have been designed to be separable codes that are also perfect error detection codes in a completely asymmetric channel [10]. The major purpose has been to demonstrate that this unique feature of the fixed weight codes can also be achieved with separable codes so that advantage may be taken of the asymmetry of a channel while still maintaining the flexibility and compatibility associated with separable codes.

### 2.3.3 Hamming Codes

The study is given in consideration of large scale computing machines in which a large number of operations must be performed without a single error in the end result [33]. In transmission from one place to another, digital machines use codes that are simply sets of symbols to which meanings or values are attached [36, 40, 51]. Examples of codes that were designed to detect isolated errors are numerous; among them are the highly developed 2-out-of-5 codes used extensively

in common control switching systems and in the Bell Relay Computers. The codes

Figure 2.5: Block Diagram of Hamming Code

used are called systematic codes. Systematic codes may be defined as codes in which each code symbol has exactly n binary digits, where m digits are associated with the information while the other k = n - m digits are used for error detection and correction [32]. Application of these codes may be expected to occur first only under extreme conditions. How to construct minimum redundancy codes is shown in the following cases:

- 1. Single error detecting codes

- 2. Single error correcting codes

- 3. Single error correcting plus double error detecting codes.

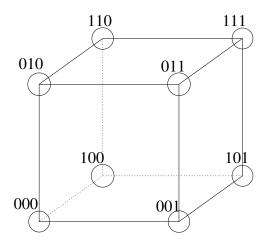

#### 2.3.3.1 Hamming Distance

The Hamming distance  $(H_d)$  of a code, the distance between 2 binary words, is the number of bit positions in which they differ. Example: For 1001000 to 1011001, the Hamming distance is 2. Codes 000 and 001 differ by 1 bit so  $H_d$  is 1. Codes 000 and 110 differ by 2 bits so  $H_d$  is 2. A  $H_d$  of 2 between two code words implies that a single bit error will not change one code word into the other. Codes 000 and 111 differ by 3 bits so  $H_d$  is 3. A  $H_d$  of 3 can detect any single or double bit error. If no double bit errors occur, it can correct a single bit error.

Figure 2.6: Diagram for Hamming Distance

#### 2.3.3.2 Single Error Correcting Code

There are k information positions of n positions. The c remaining positions are check positions: c = n - k. The value of c is determined in the encoding process by even parity checks. Each time the assigned and observed value of parity checks agree, we write a 0, else we write a 1. Written from right to left, the c 0's and 1's gives the checking number. The checking number gives the position of any single error. The checking number describes k + c + 1 different things.

$$2c \ge k + c + 1 \tag{2.1}$$

First parity check: 1's for the first binary digit from the right of their binary representation. Second parity check: 1's for the second binary digit from the right of their binary representation. Third parity check: 1's for the third binary digit from the right of their binary representation. Parity checks decide the position of the information and check bits.

A subset with minimum  $H_d = 5$  may be used for:

- 1. Double error correction, with of course, double error detection.

- 2. Single error correction plus triple error detection.

- 3. Quadruple error detection.

| Minimum  | Meaning                                            |

|----------|----------------------------------------------------|

| Distance |                                                    |

| $H_d$    |                                                    |

| 1        | Uniqueness                                         |

| 2        | Single error detection                             |

| 3        | Single error correction                            |

| 4        | Single error correction and double error detection |

| 5        | Double error correction                            |

Table 2.2: Types of Hamming Code

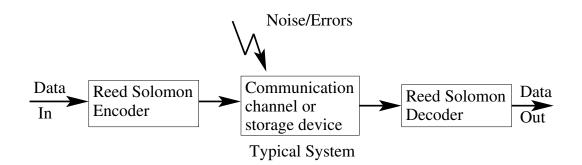

## 2.3.4 Reed Solomon (RS) Codes

*Reed Solomon* (RS) codes have introduced ideas that form the core of current commonly used error correction techniques [55]. Reed Solomon codes are used for Data Storage, Data Transmission, Wireless or Mobile Communications, Satellite communications and *Digital Video Broadcasting* (DVB). A Reed Solomon encoder

Figure 2.7: Block Diagram of System with Reed Solomon Code

takes a block of digital data and adds extra *redundancy* bits. Errors occur during transmission or storage [54, 73]. A Reed Solomon decoder processes each block and attempts to correct errors and recover [15]. The number and type of errors that can be corrected depends on the characteristics of the code. A RS code is specified as RS(n,k) with s-bit symbols. It takes k data symbols of s bits each and adds parity symbols to make an n-bit symbol. The Reed Solomon decoder can correct up to t symbols that contain errors in a code word, where 2t = n - k. The minimum code word length (n) for a RS code is  $n = 2^s - 1$ . A large value of t means that a large number of errors can be corrected, but requires more computational power than a small value of t. Sometimes error locations are known in advance, and those errors are called *erasures*. When a code word is decoded there are three possible outcomes:

- If 2s + r < 2t (s errors, r erasures) then the original transmitted code word will always be recovered.

- The decoder will detect that it cannot recover the original code word and indicate this fact.

- The decoder will misdecode and recover an incorrect code without any indication.

The probability of each of three possibilities depends on the particular Reed Solomon code and on the number and distribution of errors.

#### 2.3.4.1 Architectures for Encoding and Decoding Reed Solomon Codes

The codes are based on a specialized area of mathematics known as Galois fields. The encoder or decoder needs to carry out arithmetic operations and it requires special hardware to implement. This code word is generated using a special polynomial of the form:

$$g(x) = (x - \alpha^{i}) (x - \alpha^{i+1}) \dots (x - \alpha^{i+2t})$$

(2.2)

The code word is constructed using:

$$c(x) = g(x) i(x) \tag{2.3}$$

where g(x) is the generator polynomial, i(x) is the information block, c(x) is the valid code word and  $\alpha$  is the primitive element of the field.

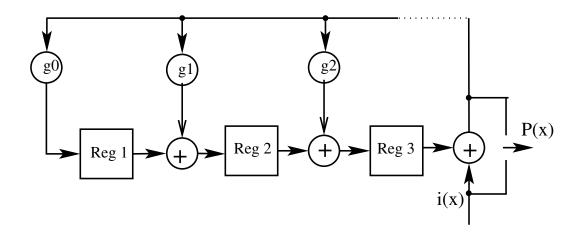

#### 2.3.4.2 Encoder Architecture

The 2t parity symbols in a systematic RS [44] code word are given by:

$$p(x) = i(x) (x^{n} - k) (g(x))$$

(2.4)

Figure 2.8: Typical Block Diagram of Reed Solomon Encoder

#### 2.3.4.3 Decoder Architecture

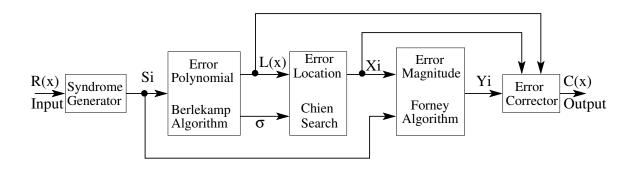

The received code word r(x) is the original (transmitted) code word c(x) plus errors e(x), i.e., r(x) = c(x) + e(x). A Reed Solomon code word has 2t syndromes that depend only on errors [50]. A syndrome can be calculated by substituting the 2t roots of the generator polynomial g(x) into r(x). Finding the symbol error locations involves solving simultaneous equations with t unknowns. Several fast algorithms are available to do this. The error locator polynomial is done using the Berlekamp Massey algorithm or Euclid's algorithm [11, 12]. Roots of the polynomial are done using the Chien search algorithm [21]. Symbol error values are analyzed using the Forney algorithm [29].

Figure 2.9: Typical Block Diagram of Reed Solomon Decoder

The properties of Reed-Solomon codes make them especially well-suited to applications where errors occur in bursts. This is because it does not matter to the code how many bits in a symbol are in error – if multiple bits in a symbol are corrupted it only counts as a single error. Conversely, if a data stream is not characterized by error bursts or drop-outs but by random single bit errors, a Reed-Solomon code is usually a poor choice. RS codes have huge amounts of hardware and take many clock cycles to encode or decode a stream of data. The RS code increases the data path width to three times the hardware of an ALU, additional hardware is needed for the RS encoder and decoder, and it takes twelve clock cycles to encode the data. In designing fault-tolerance for ALUs huge amounts of hardware and delay overhead cannot be afforded. Hence, RS codes cannot be used as a fault-tolerance technique for a microprocessor.

### 2.3.5 Residue Codes

Residue codes are separable codes and in general have been used to detect errors in the results produced by arithmetic operations [70]. A *residue* is simply defined as the remainder after a division. An introduction to residue arithmetic computation will now be given. The residue of X modulo m, denoted  $||X||_m$  is the least positive remainder when an integer X (a variable operand) is divided by another integer m (the modulus operator, normally built into the computer in some way). X and m are assumed positive here, although this restriction is readily removable. A symbolic statement of this condition is

$$X = m \left[\frac{X}{m}\right] + \|X\|_m \tag{2.5}$$

where the meaning of the square brackets is that the integer quotient [X/m] is the largest integer less than or equal to the improper fraction X/m. In consequence of this definition of  $||X||_m$ , inherently:

$$0 \le \|X\|_m \le m - 1 \tag{2.6}$$

Evidently  $||X||_m$  must be the smallest positive integer which can be expressed as X - Am, where A is an integer. Equation 2.5 is the "fundamental identity" of residue arithmetic; despite the use of specialized notation, all it states is the familiar algebraic fact that one integer divided by another yields a quotient and a remainder that are also integers.

Residue Number System (RNS) arithmetic and Redundant Residue Number System (RRNS) based codes as well as their properties are reviewed [30, 70]. RNS-based arithmetic exhibits a modular structure that leads naturally to parallelism in digital hardware implementations. The RNS has two inherent features, namely, the carry-free arithmetic and the lack of ordered significance amongst the residue digits. These are attractive in comparison to conventional weighted number systems, such as, for example, the binary weighted number system representation. The first property implies that the operations related to the different residue digits are mutually independent and hence the errors occurring during addition, subtraction and multiplication operations, or due to the noise induced by transmission and processing, remain confined to their original residue digits. In other words, these errors do not propagate and hence do not contaminate other residue digits due to the absence of a carry forward [20, 22, 28]. The abovementioned second property of the RNS arithmetic implies that redundant residue digits can be discarded without affecting the result, provided that a sufficiently high dynamic range is retained by the resultant reduced-range RNS system, in order to unambiguously describe the non-redundant information symbols. As it is well known in VLSI design, usually so-called systolic architectures are invoked to divide a processing task into several simple tasks performed by small, (ideally) identical, easily designed processors. Each processor communicates only with its nearest neighbor, simplifying the interconnection design and test, while reducing signal delays and hence increasing the processing speed. Due to its carry-free property, the RNS arithmetic further simplifies the computations by decomposing a problem into a set of parallel, independent residue computations.

The properties of the RNS arithmetic suggest that a RRNS can be used for selfchecking, error-detection and error-correction in digital processors. The RRNS technique provides a useful approach to the design of general-purpose systems, capable of sensing and rectifying their own processing and transmission errors [37, 70]. For example, if a digital receiver is implemented using the RRNS having sufficient redundancy, then errors in the processed signals can be detected and corrected by the RRNS-based decoding. Furthermore, the RRNS approach is the only one where it is possible to use the very same arithmetic module in the very same way for the generation of both the information part and the parity part of a RRNS code word. Moreover, due to the inherent properties of the RNS, the residue arithmetic offers a variety of new approaches to the realization of digital signal processing algorithms, such as digital modulation and demodulation, as well as the fault-tolerant design of arithmetic units. It also offers new approaches to the design of error-detection and error-correction codes.

### 2.3.6 IBM's Research on Error Correcting Codes

Arrays, data paths and control paths were protected either by parity or *Error Correcting Codes* (ECCs). High coverage error checking in microprocessors is implemented and done by duplicating chips and comparing the outputs. Duplication with comparison is, however, adequate only for error detection. Detection alone is inadequate for S/390, which singularly requires dynamic CPU recovery [64]. G3, G4 and G5 are various IBM file server models. The G5 server delivers this with a (72, 64) Hamming code (it can correct upto 5 simultaneous errors in the memory). For G3 and G4 servers, a code with 4-bit correction capability (S4EC) was implemented. It was not necessary to design a (78, 64) code, which could both correct one 4-bit error and detect a second 4-bit error [68]. The (76, 64) S4EC/DED ECC implemented on G3 and G4 servers is designed to ensure that all single bit failures of one chip, occurring in the same double word, as well as a 1-4 bit error on a second chip are detected. G5 returns to single bit per chip ECC and is therefore able to again use a less costly (72, 64) SEC/DED code and still protect the system from catastrophic failures caused by a single array-chip failure. The 9121 processor cache uses an ECC scheme, which corrects all single-bit errors and detects all double bit errors within a single byte. The Power-4 (a power PC machine) error-checking mechanisms, including parity, ECC, and control checks, have three distinct but related attributes. Checkers provide data integrity. Checkers initiate appropriate recovery mechanisms from bus retry based on parity error detection, to ECC correction based on hardware detection of a non-zero syndrome in ECC logic, to firmware executing recovery routines based on parity detection [16]. Recovery from soft errors in the power L2 and L3 caches is accomplished by standard single-error-correct, double error detect Hamming ECCs.

## 2.4 Hardware Redundancy

#### 2.4.1 Duplication of the Hardware

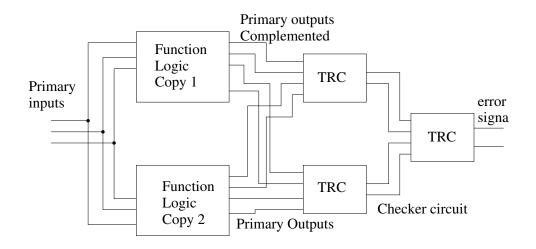

TSC circuits use hardware redundancy. For a given combinational circuit we synthesize a duplicate circuit and logic for the TSC comparator [47, 67]. The original part of the circuit has true, while its copy has complemented output values. Whenever the natural and complementary outputs differ from each other, or whenever a fault affects one of the self-checking TRC checkers, the error signal reports the presence of faults. The procedure for generating logic for the TSC comparator is adapted to the number of signals to be compared. Finally, the duplicated logic and the TSC equality comparator are technology mapped to VLSI IC's.

### 2.4.2 Triple Modular Redundancy

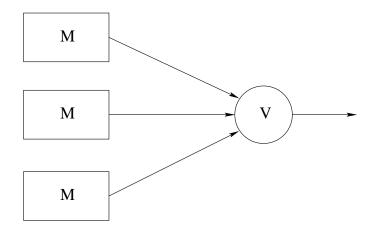

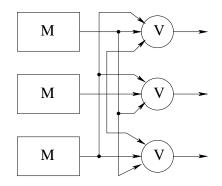

To explain triple-modular redundancy, it is first necessary to explain the concept of triple redundancy as originally envisaged by Von Neumann [46]. The concept is illustrated in Figure 2.11 given below, where the three boxes labeled M are identical modules or black boxes, which have a single output and contain digital

Figure 2.10: Block Diagram of System with Duplication of Hardware Mechanism

equipment. (A black box may be a complete computer, or it may be a much less complex unit, for example, an adder or a gate.) The circle labeled V is called a majority organ by Von Neumann. In here it will be called a voting circuit because it accepts the input from the three sources and delivers the majority opinion as an output. Since the outputs of the M's are binary and the number of inputs is odd, there is bound to be an unambiguous majority opinion. The reliability of

Figure 2.11: Triple Redundancy as Originally Envisaged by Von Neumann

the redundant system illustrated in Figure 2.11 is now determined as a function of the reliability of one module, R, assuming the voting circuit does not fail. The

redundant system will not fail if none of the three modules fails, or if exactly one of the three modules fails. It is assumed that the failures of the three modules are independent. Since the two events are mutually exclusive, the reliability R of the redundant system is equal to the sum of the probabilities of these two events. Hence,

$$R = R_M^3 + 3R_M^2 (1 - R_M) = 3R_M^2 - 2R_M^3$$

(2.7)

Several observations can be made regarding the above equation. Note that application of this type of redundancy does not increase the reliability if  $R_M$  is less than 0.5. This is an example of the general truth that reliability, even by the use of redundancy, cannot be obtained if the redundancy is applied at a level where the non-redundant reliability is very low. The closer  $R_M$  is to unity, the more advantageous the redundancy becomes. In particular, the slope of the curve for the redundant case is zero at  $R_M = 1$ . Thus, when  $R_M$  is very near unity, R departs from unity only by a second-order effect. A non-redundant system is one which

Figure 2.12: Triple Modular Redundant Configuration

fails if any single element in the system fails [23, 42]. The exponential failure law for non-redundant systems has been justified for a wide class of complex systems for periods of observation that are short compared with the mean-time-to-failure of an individual component. Although most of the analysis that follows is valid for any type of dependency of the non-redundant reliability on operating time, it is interesting to examine the specific case where the non-redundant reliability is a decaying exponential of the operating time, i.e., where:

$$R_M(t) = e^{-ft} = e^{-t/MTF} (2.8)$$

In this formula f is a constant, called the failure rate; and MTF is its reciprocal, called *mean-time-to-failure*. The reliability of the triple redundant system is now given by

$$R(t) = 3 e^{-2t/MTF} - 2 e^{-3t/MTF}$$

(2.9)

Note that for t > MTF, which is the range of time,  $R < R_M$ . This means that triple redundancy at the computer level should not be used to improve reliability in this case. To obtain improvement in reliability by the use of triple redundancy, we require t < MTF. This can be achieved in the present situation by breaking the computer into many modules, each of which is much more reliable than the entire computer. If these triply redundant modules are now reconnected to assemble an entire *triple-modular-redundant* (TMR) computer, an over-all improvement in the reliability of the computer will be achieved.

### 2.5 Time Redundancy

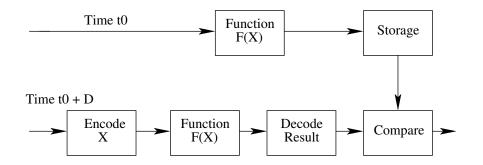

The basic idea of time redundancy is the repetition of computations in ways that allow errors to be detected [1, 40, 52]. To allow time redundancy to be used to detect permanent errors, the repeated computations are performed differently, as illustrated in Figure 2.13. During the first computation of time  $t_0$ , the operands are unmodified and the results are stored for later comparison. During the second computation at time  $t_0 + \Delta$ , the operands are modified in such a way that permanent errors resulting from faults in F(X) have a different impact on the results and can be detected when the results are compared to those obtained during the first computation. The basic concept of this form of time redundancy is that the same hardware is used multiple times in differing ways such that comparison of the results obtained at the two times will allow error detection.

Figure 2.13: Time Redundancy for Permanent Errors

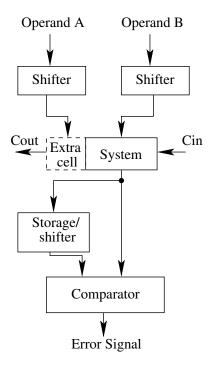

### **2.5.1** Recomputing with Shifted Operands (**RESO**)

Let the function unit F be an ALU, the coding function c be a left shift operation, and the decoding function  $c^{-1}$  be a right shift operation [48]. Thus, c(x) = leftshift of x and  $c^{-1}(x) =$ right shift of x. With a more precise description of c, e.g., logical or arithmetic shift, by how many bits, what gets shifted in and so forth, it can be shown that for most typical operations of an ALU,  $c^{-1}(F(c(x))) = F(x)$ . During the initial computation step the operands are passed through the shifter unshifted and then they are input to the ALU. The result is then stored in a register unshifted. During the recomputation step, the operands are shifted left and then input to the ALU. The result is right shifted and then compared with the contents of the register. A mismatch indicates an error in computation. This is one way of detecting error using recomputing with shifted operands. The other way of detecting error using RESO is as follows. Here we input the unshifted operands during the first step as before, but we left shift the result and then store it in the register. In the second step, we input the left shifted operands to the ALU and then compare the output directly with the register. An inequality signals an error. The penalty paid for using RESO is that all of the components of the system must be extended to accommodate the arithmetic shift. For example to perform the addition of 32-bit operands using a one-bit shift, the adder and the shift registers are required to be 33 bits and the storage register and the comparator to be 34 bits. In many applications, the penalty may be even more

Figure 2.14: Structure of RESO System

severe [5, 31]. For example, in a semi-custom design environment, the smallest available entity may be a four-bit adder, in which case the need for an extra bit in the adder would require providing the extra bits.

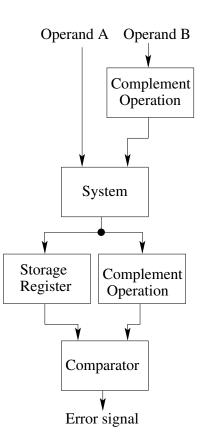

### 2.5.2 Recomputing with Alternating Logic

Let the function unit F be an ALU, the coding function c be a complement operation, and the decoding function  $c^{-1}$  be a complement operation [58]. Thus, c(x) = complement of x and  $c^{-1}(x) =$  complement of x. With a more precise description of c, it can be shown that for most typical operations of an ALU,  $c^{-1}(F(c(x))) = F(x)$ . During the initial computation step the operands are passed through the complementation operator uncomplemented and then they are input to the ALU. The result is then stored in a register uncomplemented. During the recomputation step, the operands are complemented and then input to the ALU. The result is complemented and then compared with the contents of the register. A mismatch indicates an error in computation. This is one way of

Figure 2.15: Structure of Recomputing with Alternating Logic System

detecting error using recomputing with alternating logic. The primary difficulty with complementation is that the function, F(x), must be a self-dual to allow error detection to occur. In many cases, 100% hardware redundancy is required to create a self-dual function from some arbitrary function [19, 27, 35, 72].

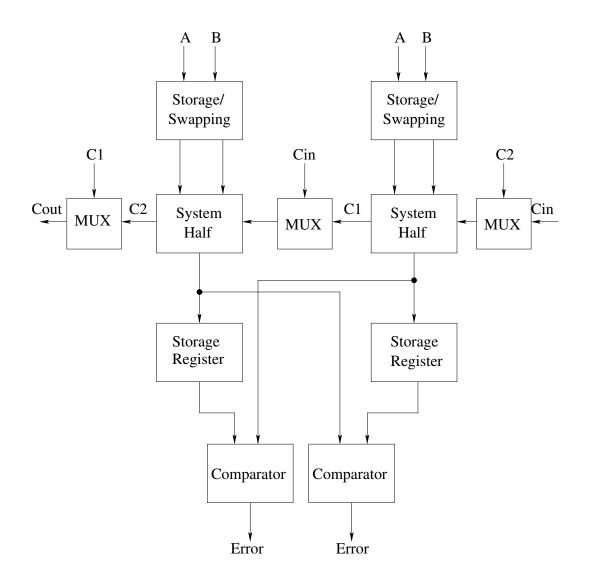

Figure 2.16: Structure of RESWO System

### 2.5.3 Recomputing with Swapped Operands (RESWO)

RESWO is a variation of the RESO technique [34, 57]. The encoding and decoding functions are swapping the upper and lower halves of each operand. At time t the

computations are performed using unmodified operands. At time  $t + \Delta t$ , however, the upper and lower halves of each operand are swapped, and the computations are repeated. A mismatch indicates an error in computation. The RESWO approach has been shown to be less expensive, particularly when the complexity of individual modules of the circuit is high [59]. This has an advantage of being quick and easy to implement.

### 2.6 Fault Diagnosis

Diagnosis is the process of locating the fault present within a given fabricated copy of the circuit [18]. For some digital systems, each fabricated copy is diagnosed to identify the faults so as to make the decisions about repair. The objective of diagnosis is to identify the root cause behind the common failures or performance problems to provide the insights on how to improve the chip yield and/or performance. A diagnostic test is designed for fault isolation or diagnosis. Diagnosis refers to the identification of a faulty part. A diagnosis test is characterized by its diagnostic resolution, defined as the ability to get closer to the fault. When a failure is indicated by a pass/fail type of test in a system that is operating in the field, a diagnostic test is applied. For an effective field repair, this test must have a diagnostic resolution of the Lowest Replaceable Unit (LRU). For a computer system that LRU may be a part such as a memory board, hard drive or keyboard. The diagnostic test must identify the faulty part so that it can be replaced. The concepts of fault dictionary and diagnostic tree are relevant to any type of diagnosis. The disadvantage of a fault dictionary approach is that all tests must be applied before an inference can be drawn. Besides, for large circuits, the volume of data storage can be large and the task of matching the test syndrome can also take a long time. It is extremely time consuming to compute a fault dictionary.

An alternative procedure, known as the diagnostic tree or fault tree, is more efficient. In this procedure, tests are applied one at a time. After the application of a test, a partial diagnosis is obtained. Also, the test to be applied next is chosen based on the outcome of the previous test. The depth of the diagnostic tree is the number of tests on the longest path from the root to any leaf node. It represents the length of the diagnostic process in the worst case. The presence of several shorter branches indicates that the process may terminate earlier in many cases. The maximum depth of the diagnostic tree is bounded by the total number of tests, but it can be less than that also. Misdiagnosis is also possible with the diagnostic tree. The notable advantage of the diagnostic tree approach is that the process can be stopped any time with some meaningful result. If it is stopped before reaching a leaf node, a diagnosis with reduced resolution results. In the fault dictionary method, any early termination makes the dictionary look up practically impossible.

### 2.7 Summary – Best of Prior Methods

So far, we have seen most of the fault-tolerant design techniques in the literature. Our motive is to come up with a fault-tolerant design technique that can correct errors. Berger codes, two-rail checkers and duplication of hardware mechanisms are not useful because they can only detect errors. Hamming codes can correct single-bit to multi-bit errors. Reed-Solomon codes can also correct multi-bit errors at a time but the hardware architecture is very complex. Residue codes can correct errors but the hardware needed for correcting one bit is huge. We can correct as many errors as we want by modifying the architecture for these codes. All these fault-tolerant design techniques have their own merits and de-merits. Triple modular redundancy also can correct errors, if at any given time only one hardware module is broken. Time redundancy mechanisms explained above cannot correct errors, they can only detect errors. So, we cannot really say in general which is the best-fault tolerance technique. But, the Hamming code, Reed Solomon codes and Residue codes are the best error correcting fault-tolerance techniques compared with other fault-tolerant techniques in the literature.

### Chapter 3

## Fault-Tolerant Technique for an ALU – Implementation Study and Justification

The goal of this work is to implement error correction with 100% hardware overhead and at most 100% delay overhead. We decided to analyze the different fault-tolerant techniques in the literature. We analyzed the hardware redundancy, the information redundancy and the time redundancy methods. After analyzing, we discovered that we cannot achieve fault-tolerance with 100% hardware overhead using hardware or information redundancy. Even the Reed-Solomon and the Residue codes required more than 100% hardware to implement fault-tolerance. So, we decided to use time redundancy as our fault-tolerance mechanism for the ALU. In order to choose the best time redundancy mechanism, we had to compare the hardware, the delay and the power overhead of the different mechanisms. Based on these criteria we decided to use *Recomputing Using Swapped Operands* as our fault-tolerance mechanism.

### 3.1 Architecture of the ALU

An Arithmetic-Logic Unit (ALU) is the part of the Central Processing Unit (CPU) that carries out arithmetic and logic operations on the operands in computer instruction words. In some processors, the ALU is divided into two units, an arithmetic unit (AU) and a logic unit (LU). Typically, the ALU has direct input and output access to the processor controller, main memory (random access memory or RAM in a personal computer), and input/output devices. Inputs and outputs flow along an electronic path that is called a bus. The input consists of

an instruction word that contains an operation code (sometimes called an "OP CODE"), one or more operands and sometimes a format code. The operation code tells the ALU what operation to perform and the operands are used in the operation. The output consists of a result that is placed in a storage register and settings that indicate whether the operation was performed successfully. In general, the ALU includes storage places for input operands (operands that are being added), the accumulated result and shifted results. The flow of bits and the operations performed on them in the subunits of the ALU is controlled by gated circuits. The gates in these circuits are controlled by a sequence logic unit that uses a particular algorithm or sequence for each operation code. In the arithmetic unit, multiplication and division are done by a series of adding or subtracting and shifting operations. There are several ways to represent negative numbers. In the logic unit, one of 16 possible logic operations can be performed, such as comparing two operands and identifying where bits do not match. The design of the ALU is obviously a critical part of the processor and new approaches to speeding up instruction handling are continually being developed. In computing, an ALU is a digital circuit that performs arithmetic and logic operations. An ALU must process numbers using the same format as the rest of the digital circuit. For modern processors, that almost always is the two's complement binary number representation. Early computers used a wide variety of number systems, including one's complement, sign-magnitude format, and even true decimal systems, with ten tubes per digit. ALUs for each one of these numeric systems had different designs, and that influenced the current preference for two's complement notation, as this is the representation that makes it easier for the ALUs to add and subtract. Most of a processor's operations are performed by one or more ALUs. An ALU loads data from input registers, executes the operation and stores the result into output registers. ALUs can perform the following operations:

- 1. Integer arithmetic operations (addition, subtraction and multiplication)

- 2. Bitwise logic operations (AND, NOT, OR, XOR), and

Bit-shifting operations (shifting a word by a specified number of bits to the left or right).

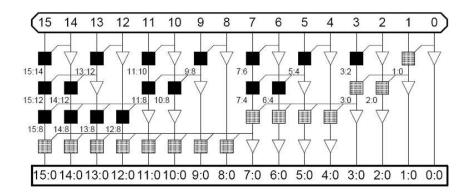

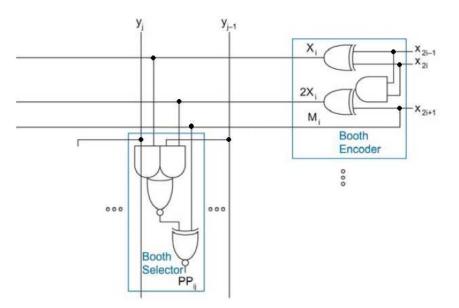

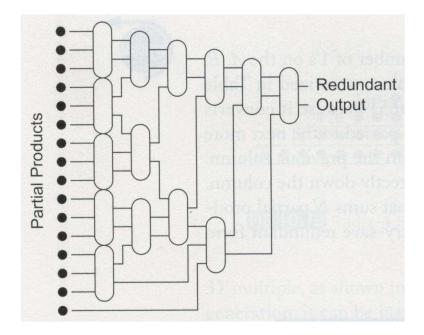

We implemented a Sklansky tree adder [62] for addition and subtraction instead of Brent-Kung [17] or Kogge-Stone [39] trees. We chose it because it has the fewest wires and minimum logic depth. The Sklansky adder topology is the most energy efficient compared to the other two adders [49] in the 90*nm* technology. We implemented Booth-encoding [14] to reduce the partial products of the multiplier and for adding the partial products we used a Wallace Tree [69]. We used the radix-4 Booth encoding scheme for the ALU. For the *Carry Propagation Adder* (CPA) at the final stage of the Wallace tree, we reused the Sklansky adder designed for addition.

### 3.1.1 Adders

Addition forms the basis of many processing operations, from counting to multiplication to filtering. As a result, adder circuits that add two binary numbers are of great interest to digital system designers. An extensive, almost endless, assortment of adder architectures serve different speed/area requirements. The simplest design is the ripple-carry adder in which the carry-out of one bit is simply connected as the carry-in of the next, but, in the carry propagation adders, the carry-out influences the carry into all subsequent bits. Faster adders look ahead to predict the carry-out of a multi-bit group. Long adders use multiple levels of lookahead structures for even more speed. For wide adders, the delay of carry-lookahead adders becomes dominated by the delay of passing the carry through the lookahead stages. This delay can be reduced by looking ahead across the lookahead blocks. In general, one can construct a multi-level tree of lookahead structures to achieve delay that grows with  $\log N$ . There are many ways to build the lookahead tree that offer tradeoffs among the number of stages of logic, the number of logic gates, the maximum fanout on each gate, and the amount of wiring between the stages. Three fundamental trees are the Brent-Kung, Sklansky

and Kogge-Stone architectures.

### 3.1.1.1 Brent-Kung Adder

The *Brent-Kung* tree computes prefixes for 2-bit groups. These are used to find prefixes for 4-bit groups, which in turn are used to find prefixes for 8-bit groups and so forth. The prefixes then fan back down to compute the carries-in to each bit. The tree requires  $2(\log_2 N) - 1$  stages. The fanout is limited to 2 at each stage.

#### 3.1.1.2 Kogge-Stone Adder

The Kogge-Stone tree achieves both  $(\log_2 N)$  stages and fanout of 2 at each stage. This comes at the cost of many long wires that must be routed between stages. The tree also contains more *Propagate* and *Generate* cells; while this may not impact the area if the adder layout is on a regular grid, it will increase power consumption.

#### 3.1.1.3 Sklansky Adder

The *Sklansky* tree reduces the delay to  $(\log_2 N)$  stages by computing intermediate prefixes along with the large group prefixes. This comes at the expense of fanouts that double at each level: The gates fanout to [8,4,2,1] other columns. These high fanouts cause poor performance on wide adders unless the gates are appropriately sized or the critical signals are buffered before being used for the intermediate prefixes. Transistor sizing can cut into the regularity of the layout because multiple sizes of each cell are required, although the larger gates can spread into adjacent columns. Note that the recursive doubling in the Sklansky tree is analogous to the conditional-sum adder. The conditional-sum adder performs carry-select starting with group of 1-bit and recursively doubling to N/2bits.

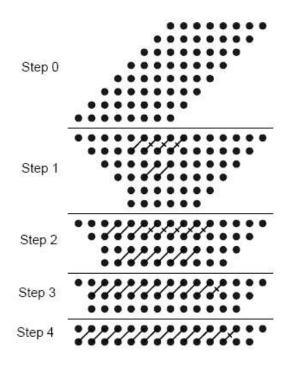

Figure 3.1: Sklansky Tree Adder [62]