# DEVELOPMENT OF 4H-SIC HIGH VOLTAGE UNIPOLAR POWER SWITCHING

# DEVICES

by

# PETRE ALEXANDROV

A Dissertation submitted to the

Graduate School-New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Graduate Program in

Electrical and Computer Engineering

written under the direction of

Professor Jian H. Zhao

and approved by

New Brunswick, New Jersey

October, 2009

## ABSTRACT OF THE DISSERTATION

#### Development of 4H-SiC High Voltage Unipolar Power Switching Devices

#### By PETRE ALEXANDROV

Dissertation Director: Professor Jian H. Zhao

4H-SiC is a promising material for switching high power and high temperature device applications. The superior properties of SiC, such as wider band-gap and higher value of critical electric field allow significant reduction in device on-resistance compared to Si power devices of similar voltage ratings. In addition the excellent thermal conductivity of SiC alleviates the device cooling requirements and allows design of smaller and more efficient systems. Several advantages of the unipolar power switches over the bipolar switches make them desirable for fast switching applications. Voltage-controlled normally-off devices are particularly attractive for practical applications because of simpler gate-drive circuitry. The advantages of the vertical JFET device being free of the problems related to oxide reliability, as compared to the MOSFET, recognize it as an excellent candidate for high power, high temperature switching applications.

Device designs for normally-off and normally-on unipolar switches with blocking voltages from 400V to 11kV are proposed, based on a pure vertical trenched and implanted structure. Two different junction termination structures (junction termination

extension and guard rings) are designed and successfully implemented. A fabrication process is designed to achieve a simple and reliable self-aligned fabrication process. The fabrication challenges are discussed and ways to improve the process are identified. Three different devices were designed and fabricated.

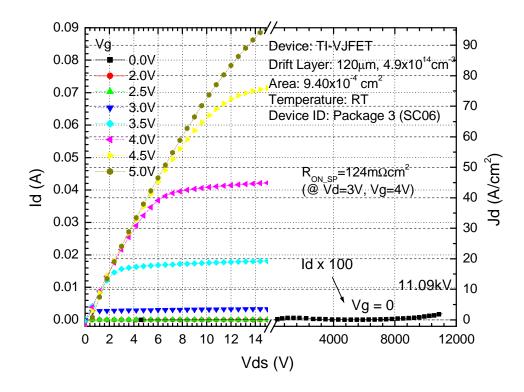

The world's first normally-off 4H-SiC TIVJFET with a blocking voltage of 11kV was demonstrated, showing low specific on-resistance of  $124m\Omega.cm^2$ .

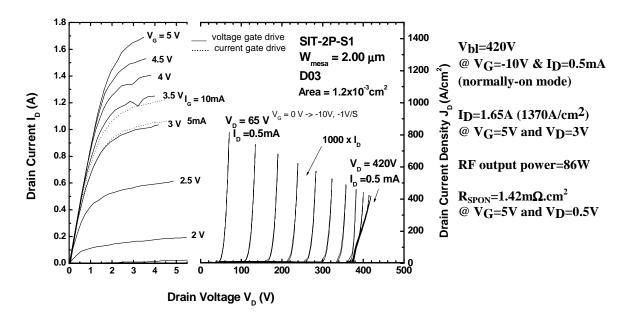

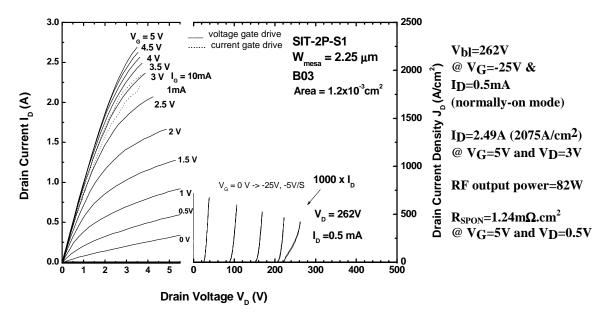

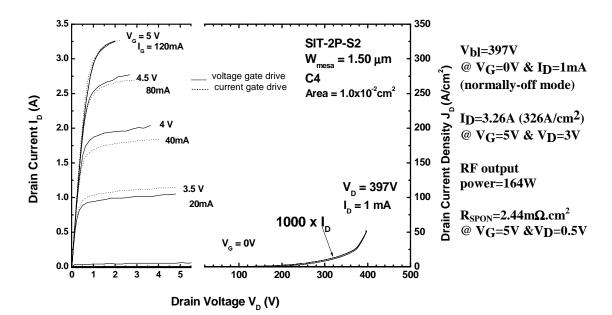

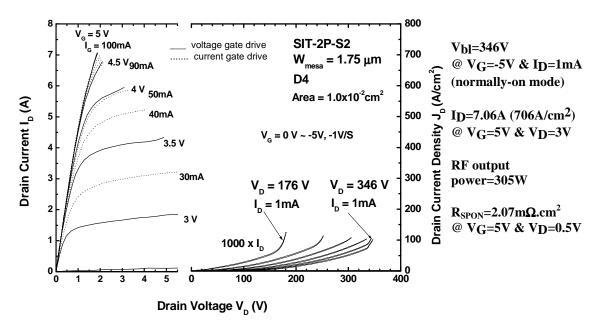

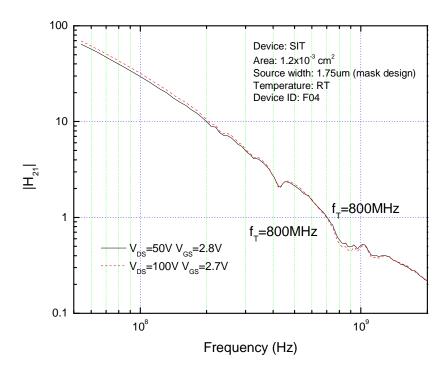

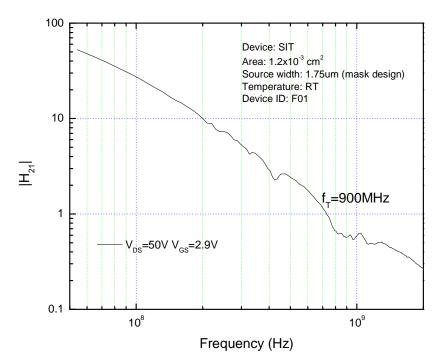

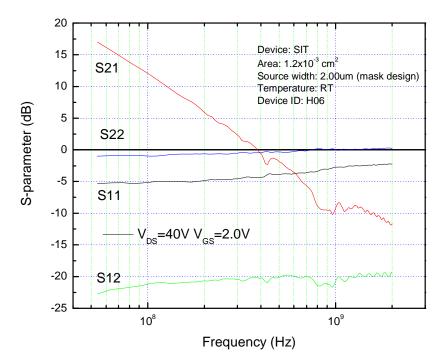

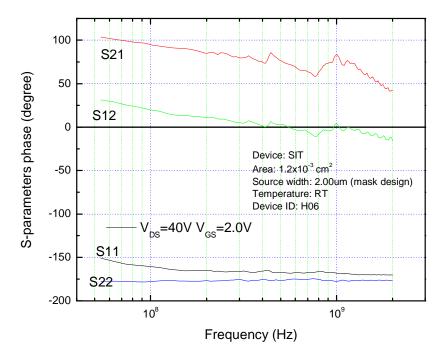

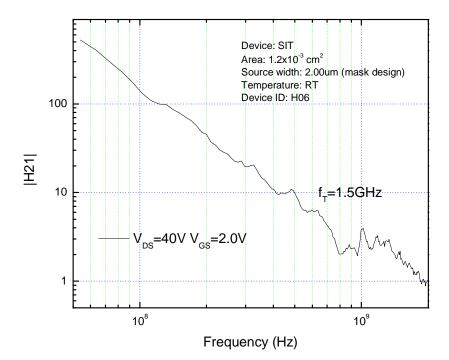

Normally-off and normally-on 4H-SiC High Frequency TIVJFETs with blocking voltages up to 400V were demonstrated. 3.3A-397V normally-off capability was achieved for a single die, corresponding to a high power of 1310 W/die. This corresponds to a class B operation RF power of 164W for a single die. Cut-off frequency  $f_T$ = 0.9 to 1.5 GHz was reached.

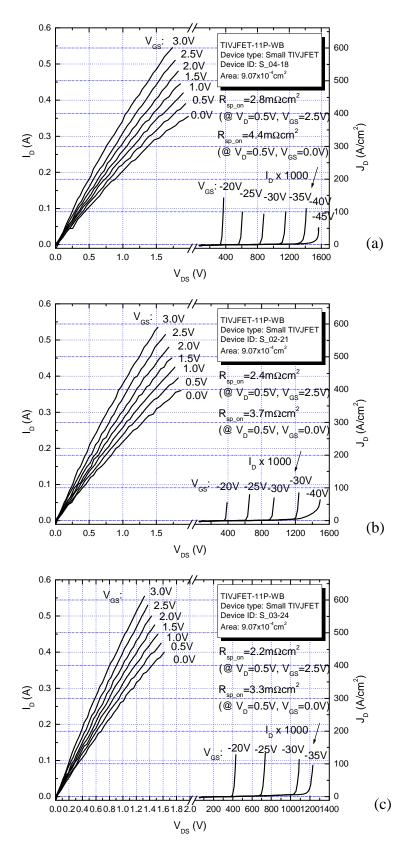

In the 1200V class devices a normally-on 4H-SiC TIVJFET with guard ring termination and substantially simplified processing was also demonstrated. The highest blocking voltage achieved was 1562V with a specific on-resistance of  $2.8 \text{m}\Omega.\text{cm}^2$  at  $V_{DS}=0.5\text{V}$  and  $V_{GS}=2.5\text{V}$  and a current gain of 1495. The lowest specific on resistance achieved was  $2.2 \text{m}\Omega.\text{cm}^2$  at  $V_{DS}=0.5\text{V}$  and  $V_{GS}=2.5\text{V}$  and a current gain of 1495. The lowest specific on resistance blocking voltage of 1232V.

# ACKNOWLEDGEMENTS

I would like to express my deep gratitude to Professor Jian H. Zhao, my thesis advisor, for his guidance and constant support. I would like to also thank Prof. Wei Jiang, Prof. Moncef Tayahi of the department and Dr. Maurice Weiner of United Silicon Carbide, Inc. for their critical reading of this thesis.

I would like to thank Dr. Xueqing Li of United Silicon Carbide, Inc. for providing valuable device simulations. I would also like to thank Dr. Yongxi Zhang for the invaluable discussions. I would like to acknowledge the contribution of Mr. Ming Su for the initial survey of silicide contact process. This research was supported by funding provided by United Silicon Carbide, Inc.

Finally, I wish to express my heartfelt thanks to my wife and children for their understanding, patience, support and sacrifice.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

| ABSTRACTi                                                       | i |

|-----------------------------------------------------------------|---|

| ACKNOWLEDGEMENTSiv                                              | V |

| CHAPTER 1. INTRODUCTION                                         | 1 |

| 1.1. Silicon Carbide Material Overview for Power Electronics    | 1 |

| 1.2. Power Switching Devices – Alternatives and Current Status  | 4 |

| 1.2.1. Unipolar vs. Bipolar Power Devices                       | 4 |

| 1.2.2. Unipolar Power Devices – MOSFET vs. JFET                 | 5 |

| 1.2.3. JFET – A Better Choice for High Temperature Power Device | 7 |

| 1.3. Objectives of the Proposed Ph.D Thesis Research            | ) |

| CHAPTER 2. BASIC TIVJFET STRUCTURE AND PROCESS DESIGN           | 2 |

| 2.1. Basic TIVJFET Structure Design12                           | 2 |

| 2.1.1. Unit Cell Design                                         | 2 |

| 2.1.2. Drift Layer Design                                       | 3 |

| 2.1.3. Junction Termination Design                              | 5 |

| 2.1.4. Vertical Channel Design                                  | 2 |

| 2.2. Process Design                                             | 3 |

| 2.2.1. Major Fabrication Steps                                  | 3 |

| 2.2.2. Critical Fabrication Steps – Challenges and Improvements | 3 |

| CHAPTER 3. NORMALLY-OFF HIGH VOLTAGE (11KV) TIVJFET             | 1 |

| 3.1. Device and Process Design                                  | 1 |

| 3.1.1. Unit Cell Design                                         | 1 |

| 3.1.2. Device Layout and Photomask Design                       | 2 |

| 3.1.3. Process Design                                                                                                                                                                                                                                                                                                              |                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 3.2. Fabrication                                                                                                                                                                                                                                                                                                                   |                                                                       |

| 3.2.1. Source Mesa Formation                                                                                                                                                                                                                                                                                                       |                                                                       |

| 3.2.2. Gate and Termination Formation by P+ Implantation and Dopant                                                                                                                                                                                                                                                                | Activation                                                            |

| Annealing                                                                                                                                                                                                                                                                                                                          |                                                                       |

| 3.2.3. Junction Termination Formation                                                                                                                                                                                                                                                                                              |                                                                       |

| 3.2.4. Surface Passivation                                                                                                                                                                                                                                                                                                         | 40                                                                    |

| 3.2.5. Source and Drain Contact Formation                                                                                                                                                                                                                                                                                          | 40                                                                    |

| 3.2.6. Gate Contact Formation                                                                                                                                                                                                                                                                                                      | 41                                                                    |

| 3.2.7. Trench Filling Planarization and Source Metal Overlay                                                                                                                                                                                                                                                                       |                                                                       |

| 3.3. Characterization                                                                                                                                                                                                                                                                                                              | 44                                                                    |

| CHAPTER 4. NORMALLY-OFF AND NORMALLY-ON HIGH FREQ                                                                                                                                                                                                                                                                                  | UENCY                                                                 |

|                                                                                                                                                                                                                                                                                                                                    |                                                                       |

| TIVJFETS WITH A BLOCKING VOLTAGE OF 400V                                                                                                                                                                                                                                                                                           | -                                                                     |

|                                                                                                                                                                                                                                                                                                                                    |                                                                       |

| TIVJFETS WITH A BLOCKING VOLTAGE OF 400V                                                                                                                                                                                                                                                                                           | <b>48</b>                                                             |

| <b>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</b> 4.1. Device and Process design                                                                                                                                                                                                                                                     | <b>48</b><br>48<br>48                                                 |

| <b>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</b> 4.1. Device and Process design         4.1.1. Unit Cell Design                                                                                                                                                                                                                     | <b>48</b><br>48<br>48<br>48<br>48<br>49                               |

| <ul> <li><b>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</b></li> <li>4.1. Device and Process design</li></ul>                                                                                                                                                                                                                         | <b>48</b><br>48<br>48<br>48<br>49<br>52                               |

| <ul> <li><b>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</b></li> <li>4.1. Device and Process design</li></ul>                                                                                                                                                                                                                         | <b>48</b><br>48<br>48<br>48<br>49<br>52<br>56                         |

| <ul> <li><b>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</b></li> <li>4.1. Device and Process design</li></ul>                                                                                                                                                                                                                         | <b>48</b><br>48<br>48<br>48<br>49<br>52<br>56<br>56                   |

| <ul> <li>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</li> <li>4.1. Device and Process design</li> <li>4.1.1. Unit Cell Design</li> <li>4.1.2. Device Layout and Photomask Design</li> <li>4.1.3. Process Design</li> <li>4.2. Fabrication</li> <li>4.2.1. Alignment Marks Formation</li> </ul>                                        | <b>48</b><br>48<br>48<br>48<br>49<br>52<br>52<br>56<br>56<br>56<br>57 |

| <ul> <li>TIVJFETS WITH A BLOCKING VOLTAGE OF 400V</li> <li>4.1. Device and Process design</li> <li>4.1.1. Unit Cell Design</li> <li>4.1.2. Device Layout and Photomask Design</li> <li>4.1.3. Process Design</li> <li>4.2. Fabrication</li> <li>4.2.1. Alignment Marks Formation</li> <li>4.2.2. Drain Trench Formation</li> </ul> | <b>48</b><br>48<br>48<br>49<br>52<br>56<br>56<br>56<br>56<br>55<br>57 |

| 4.2.6. Junction Termination Extension (JTE)                                                                                                                                                                                                                                                                                    | 64             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.2.7. Surface Passivation                                                                                                                                                                                                                                                                                                     | 66             |

| 4.2.8. Gate Contact Formation                                                                                                                                                                                                                                                                                                  | 67             |

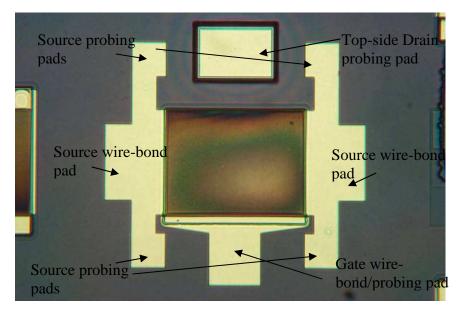

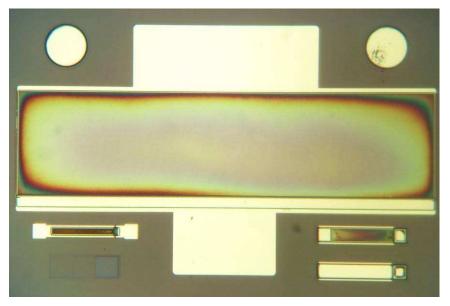

| 4.2.9. Top-side and Bottom-side Drain Contact Formation                                                                                                                                                                                                                                                                        | 69             |

| 4.2.10. Source Contact Formation                                                                                                                                                                                                                                                                                               | 70             |

| 4.2.11. Ohmic Contacts Annealing                                                                                                                                                                                                                                                                                               | 71             |

| 4.2.12. Trench Filling Planarization and Metal Overlay Formation                                                                                                                                                                                                                                                               | 72             |

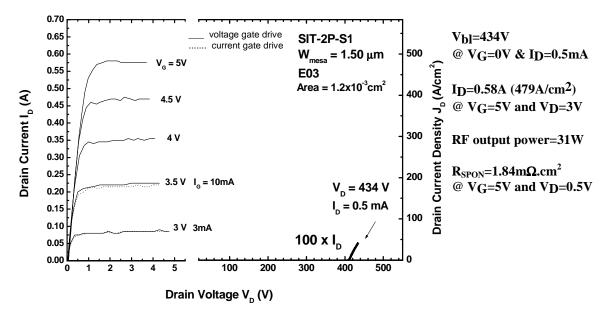

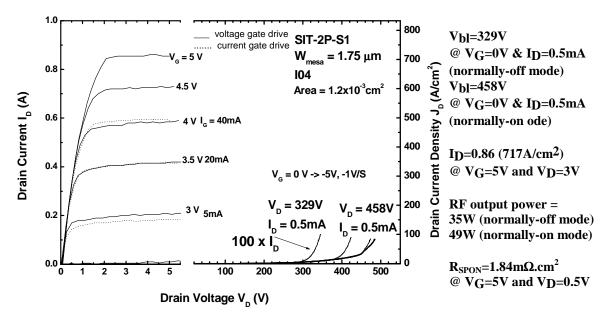

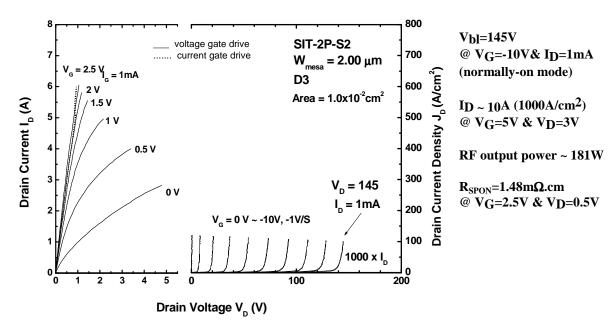

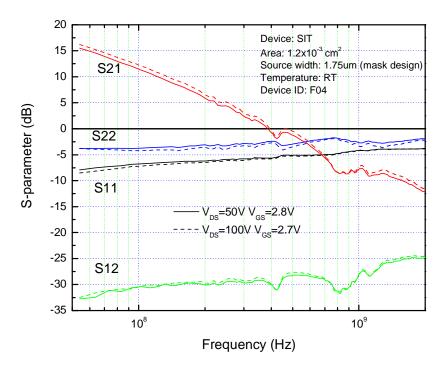

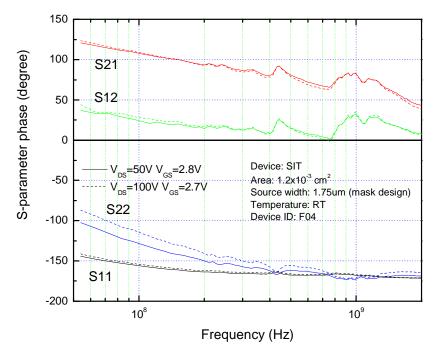

| 4.3. Characterization                                                                                                                                                                                                                                                                                                          | 75             |

| 4.3.1. Characterization under DC Conditions                                                                                                                                                                                                                                                                                    | 75             |

| 4.3.2. RF Small Signal Characterization of Fabricated HF-TIVJFETs                                                                                                                                                                                                                                                              |                |

| CHAPTER 5. NORMALLY-ON TIVJFET WITH A BLOCKING VOL                                                                                                                                                                                                                                                                             | FAGE OF        |

|                                                                                                                                                                                                                                                                                                                                |                |

| 1200V                                                                                                                                                                                                                                                                                                                          |                |

| <ul><li><b>1200V</b></li><li>5.1. Device and Process design</li></ul>                                                                                                                                                                                                                                                          |                |

|                                                                                                                                                                                                                                                                                                                                | 86             |

| 5.1. Device and Process design                                                                                                                                                                                                                                                                                                 | 86<br>86       |

| <ul><li>5.1. Device and Process design</li><li>5.1.1. Unit Cell Design</li></ul>                                                                                                                                                                                                                                               | 86<br>86<br>87 |

| <ul> <li>5.1. Device and Process design</li> <li>5.1.1. Unit Cell Design</li> <li>5.1.2. Floating Guard Ring Termination Design</li> </ul>                                                                                                                                                                                     |                |

| <ul> <li>5.1. Device and Process design</li> <li>5.1.1. Unit Cell Design</li> <li>5.1.2. Floating Guard Ring Termination Design</li> <li>5.1.3. Device Layout and Photomask Design</li> </ul>                                                                                                                                  |                |

| <ul> <li>5.1. Device and Process design</li> <li>5.1.1. Unit Cell Design</li> <li>5.1.2. Floating Guard Ring Termination Design</li> <li>5.1.3. Device Layout and Photomask Design</li> <li>5.1.4. Process Design</li> </ul>                                                                                                   |                |

| <ul> <li>5.1. Device and Process design</li> <li>5.1.1. Unit Cell Design</li> <li>5.1.2. Floating Guard Ring Termination Design</li> <li>5.1.3. Device Layout and Photomask Design</li> <li>5.1.4. Process Design</li> <li>5.2. Fabrication</li> </ul>                                                                         |                |

| <ul> <li>5.1. Device and Process design</li></ul>                                                                                                                                                                                                                                                                              |                |

| <ul> <li>5.1. Device and Process design</li> <li>5.1.1. Unit Cell Design</li> <li>5.1.2. Floating Guard Ring Termination Design</li> <li>5.1.3. Device Layout and Photomask Design</li> <li>5.1.4. Process Design</li> <li>5.2. Fabrication</li> <li>5.2.1. Source Mesa Formation</li> <li>5.2.2. Gate Implantation</li> </ul> |                |

| 5.2.6. Gate Metal Overlay Formation104                                    |

|---------------------------------------------------------------------------|

| 5.2.7. Trench Filling Planarization and Source Metal Overlay Formation107 |

| 5.3. Characterization                                                     |

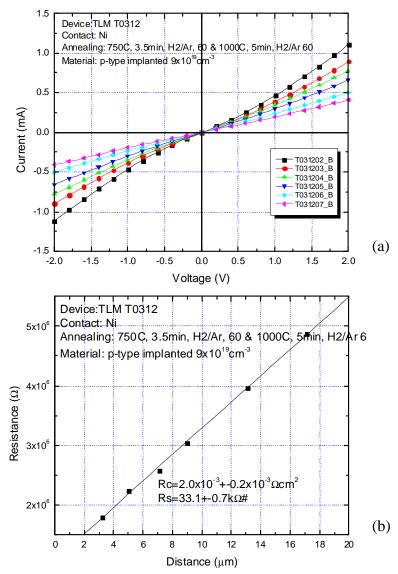

| 5.3.1. TLM Test Pattern Characterization109                               |

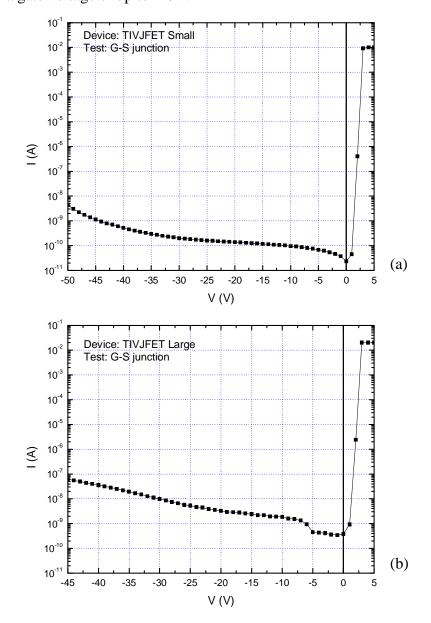

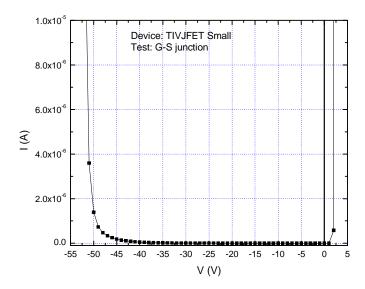

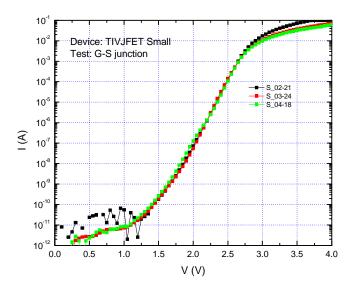

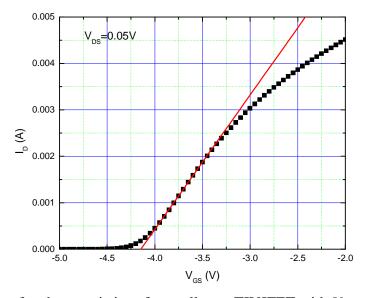

| 5.3.2. Gate-Source Junction Characterization110                           |

| 5.3.3. JFET Blocking and Forward Conduction Characterization112           |

| 5.3.4. Blocking Voltage Mapping116                                        |

| 5.3.5. Specific On-resistance                                             |

| 5.3.6. JFET Threshold Voltage and Vertical Channel Width Uniformity123    |

| CHAPTER 6. SUMMARY AND FUTURE WORK SUGGESTIONS 127                        |

| 6.1. Summary                                                              |

| 6.2. Future Work Suggestions                                              |

| 6.2.1. Design Improvement                                                 |

| 6.2.2. Process Improvement                                                |

| REFERENCES131                                                             |

| CURRICULUM VITA                                                           |

## **CHAPTER 1. INTRODUCTION**

## **1.1. Silicon Carbide Material Overview for Power Electronics**

Silicon is the main material used in semiconductor industry. It is readily available, well studied and its processing technology is mature. However, devices based on Si are not able to operate at temperatures above 200°C because of excessive junction leakage currents. This limitation becomes even more severe when high operating temperatures are combined with high-power, high-frequency and high-radiation environment. High-temperature circuit operation is desired for use in various applications, such as aerospace applications, nuclear power instrumentation, space exploration, and automotive electronics. Wide band-gap materials have to be used in order to build devices, capable of operation at higher temperatures. Some of the main materials of interest for such applications are silicon carbide (SiC), gallium nitride (GaN), aluminum nitride (AlN) and diamond.

SiC has several advantages over other wide-bandgap semiconductors at the present time. Properties such as large breakdown electric field strength (10 times that of Si), large saturated electron drift velocity, small dielectric constant, reasonably high electron mobility and high thermal conductivity (about 3.3 times that of Si and better than copper) make SiC an attractive candidate for fabricating power devices with reduced power losses and die size. Table 1.1 shows the key physical properties of some important semiconductors.

| Material | E <sub>G</sub><br>(eV) | n <sub>i</sub><br>(cm <sup>-3</sup> ) | Е <sub>г</sub> | $\begin{array}{c} \mu_n \\ (cm^2/V \cdot s) \end{array}$ | $\begin{array}{c} \mu_{p} \\ (cm^{2}/V \cdot s) \end{array}$ | E <sub>C</sub><br>(MV/cm) | v <sub>sat</sub><br>(10 <sup>7</sup> cm/s) | λ<br>(W/cm·K) |

|----------|------------------------|---------------------------------------|----------------|----------------------------------------------------------|--------------------------------------------------------------|---------------------------|--------------------------------------------|---------------|

| Ge       | 0.66                   | 2.4×10 <sup>13</sup>                  | 16.0           | 3900                                                     | 1900                                                         | 0.1                       | 0.5                                        | 0.6           |

| Si       | 1.12                   | 1.5×10 <sup>10</sup>                  | 11.8           | 1350                                                     | 450                                                          | 0.3                       | 1.0                                        | 1.5           |

| GaAs     | 1.42                   | $1.8 \times 10^{6}$                   | 12.8           | 8500                                                     | 400                                                          | 0.4                       | 2.0                                        | 0.5           |

| 3C-SiC   | 2.36                   | 6.9                                   | 9.6            | 800                                                      | 320                                                          | 2.0                       | 2.0                                        | 4.9           |

| 6H-SiC   | 3.0                    | 2.3×10 <sup>-6</sup>                  | 9.7            | 400  c<br>85(⊥c)                                         | 90                                                           | 3.0                       | 2.0                                        | 4.9           |

| 4H-SiC   | 3.23                   | 8.2×10 <sup>-9</sup>                  | 9.7            | 960(∥c)<br>800(⊥c)                                       | 120                                                          | 3.0                       | 2.0                                        | 4.9           |

| GaN      | 3.39                   | 1.9×10 <sup>-10</sup>                 | 9.0            | 900                                                      | 200                                                          | 3.3                       | 2.5                                        | 1.3           |

| AlN      | 6.1                    | ~10 <sup>-31</sup>                    | 8.7            | 300                                                      | 14                                                           | 1.3-1.8                   | 1.8                                        | 2.5           |

| Diamond  | 5.5                    | 1.6×10 <sup>-27</sup>                 | 5.5            | 2200                                                     | 1800                                                         | 5.6                       | 2.7                                        | 20.0          |

Table 1.1. Physical properties for selected semiconductor materials [1, 2, 3].

From a technological point of view there is an advantage for SiC having a similar chemistry to that of the silicon, which gives immediate access to well-known device processing techniques. Perhaps the most important technological advantage of SiC is the ability to grow thermal oxide for use as device passivation layers, gate dielectrics, and as mask in processing. Another very important advantage is the commercial availability of SiC substrates (currently 4-inch wafers are available).

Various Figure-of-Merit (FOM) coefficients based on material parameters have been introduced to compare different semiconductor materials for high voltage, high frequency applications (Table 1.2. [3, 4]). Johnson FOM can be used to compare devices for high frequency signal amplifiers; Keyes FOM is suitable for high-speed switches comparison; Baliga FOM is for unipolar low frequency power devices; and Baliga high frequency FOM is for unipolar high frequency power switches. An important power device FOM is

$V_{BR}^2/R_{ON\_SP}$ , which is related with BFOM by  $\varepsilon_r \mu_n E_C^3 = \frac{1}{\varepsilon_0} \frac{V_{BR}^2}{R_{ON\_SP}}$ , and is commonly used

to compare the DC performance of power transistors. Huang FOMs are more useful from

an application point of view. HFOMs include Huang Material FOM (HMFOM) for evaluation of both conduction and switching losses, Huang Chip Area FOM (HCAFOM) for comparison of chip areas, and Huang Thermal FOM (HTFOM) for the junction temperature variation.

Based on FOMs comparison, 4H-SiC is the best material among the SiC polytypes and is expected to outperform silicon substantially for high voltage switching applications. GaN shows comparable mobility, breakdown field, and saturation velocity as SiC but lower by more than a factor of 3 thermal conductivity than SiC, which corresponds to worse FOMs related with thermal conductivity. In addition, GaN has a direct bandgap, resulting in a short minority carrier life time, which is undesirable for bipolar device operation. Another disadvantage for GaN compared to SiC at present time is several orders of magnitude higher defect density in GaN materials. AlN has one of the largest bandgaps, however the growth of defect free AlN crystals is seriously problematic. Diamond has superior physical, chemical and electrical properties, compared to any other material. However, taking advantage of diamond's excellent properties is limited by the unavailability of large area high quality diamond substrates and the fact that only p-type diamond is available at present. Based on all of the above considerations 4H-SiC is currently the best choice for power switching applications.

| Material | Johnson<br>JFOM<br>$(E_C v_{sat} / 2\pi)^2$ | $\frac{\text{Keyes}}{\text{KFOM}}$ $\lambda \sqrt{v_{sat} / \varepsilon_r}$ | Baliga<br>BFOM<br>$\varepsilon_r \mu E_c^3$ | Baliga high<br>frequency<br>BHFFOM<br>$\mu E_c^2$ | Huang<br>Material<br>HMFOM<br>$E_C \sqrt{\mu}$ | Huang Chip<br>Area<br>HCAFOM<br>$\varepsilon_r E_c^2 \sqrt{\mu}$ | Huang<br>Tempera-<br>ture<br>HTFOM<br>$\lambda/(\varepsilon_r E_c)$ |

|----------|---------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------|------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|

| Si       | 1                                           | 1                                                                           | 1                                           | 1                                                 | 1                                              | 1                                                                | 1                                                                   |

| Ge       | 0.028                                       | 0.24                                                                        | 0.15                                        | 0.32                                              | 0.57                                           | 0.26                                                             | 0.9                                                                 |

| GaAs     | 7                                           | 0.45                                                                        | 16                                          | 11                                                | 3.3                                            | 4.8                                                              | 0.2                                                                 |

| 3C-SiC   | 178                                         | 5.1                                                                         | 143                                         | 26                                                | 5.1                                            | 28                                                               | 0.6                                                                 |

| 6H-SiC   | 400                                         | 5.1                                                                         | 244                                         | 30                                                | 5.4                                            | 45                                                               | 0.4                                                                 |

| 4H-SiC   | 400                                         | 5.1                                                                         | 585                                         | 71                                                | 8.4                                            | 69                                                               | 0.4                                                                 |

| GaN      | 756                                         | 1.6                                                                         | 677                                         | 81                                                | 9.0                                            | 75                                                               | 0.1                                                                 |

| Diamond  | 2540                                        | 32                                                                          | 4940                                        | 568                                               | 23.8                                           | 207                                                              | 1.5                                                                 |

Table 1.2. Figures-of-Merit (FOM) normalized to Si [2, 4]

# **1.2.** Power Switching Devices – Alternatives and Current Status

#### **1.2.1.** Unipolar vs. Bipolar Power Devices

The main types of power switching devices include Bipolar Junction Transistor (BJT), Thyristor, Insulated Gate Bipolar Transistor (IGBT), Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), and Junction Field Effect Transistor (JFET). Based on the type of current carriers utilized they can be divided into two types – bipolar and unipolar. Bipolar devices such as BJT and IGBT employ majority and minority carriers. They have the advantage that due to minority carrier injection during operation, conductivity modulation could be realized to reduce the device on-resistance and forward voltage drop. However, the minority carrier charge stored during the device on-state has to be removed by recombination during switching to off-state, which leads to increased switching times and switching losses. Furthermore bipolar devices in SiC currently have the problem of forward voltage shift caused by the stacking faults migration in SiC under high current density operation [14]. Unipolar devices use only majority carriers, so they do not suffer from the problems related to minority carrier storage and hence offer faster switching speeds and reduced switching losses. Therefore a unipolar switch would be the device of choice for fast switching applications. According to a recent detailed modeling study SiC unipolar power switches have an advantage in comparison to bipolar power switches at voltages up to 20kV when switching frequency is above 800Hz for a device junction temperature of 175°C [5]. In silicon over a certain voltage range the IGBT is the preferred type of switching device. If silicon IGBTs can be replaced by unipolar SiC switches, the switching losses could be radically reduced [6]. Due to SiC higher critical electric field unipolar devices in SiC have ten times lower resistivity compared to unipolar silicon devices. For a given on-resistance SiC switching devices are much smaller and offer very low input and output capacitances. Therefore for application where Si MOSFETs are used, benefits are possible from using SiC unipolar switches by reduction of parasitic capacitances.

#### **1.2.2. Unipolar Power Devices – MOSFET vs. JFET**

Among the unipolar devices there are two types of power devices - MOSFET and JFET. MOSFET is the most popular unipolar power switching device. Power MOSFETs are designed to be in normally off, i.e. in the off state with no bias applied to the gate. In a MOSFET the current flows through a thin surface channel formed by applying an appropriate bias at the gate, which is insulated from the semiconductor. A critical characteristic of the device is the quality of the semiconductor-oxide interface. In silicon carbide this interface contains high density of carbon related surface states, which results in low electron mobility at the channel surface. Substantial progress has been made in the development of SiC MOSFET. 4H-SiC MOSFET with low on-resistance of 1.8 m $\Omega$ cm<sup>2</sup> and a blocking voltage of 660 V has been reported with very fast switching speed (rise time of 19 ns and a fall time of 39 ns) [7]. However, the reliability of SiC MOSFETs at high temperatures and high electric field is a key concern [11,12]. An intrinsic disadvantage of SiC is the smaller conduction band discontinuity for the SiC-oxide interface compared to Si-oxide [10]. Moreover if the higher breakdown filed of SiC is to be utilized, the oxide would be subjected to an even larger stress. This would lead to threshold voltage instability, due to carrier trapping in the gate oxide, and premature oxide breakdown, especially at high temperatures. The use of a MOSFET at higher temperature is limited due to the exponential influence of the temperature on the device life time [8]. A recent work [11] suggest that 4H-SiC double implanted MOSFETs (DIMOSFETs) have at least more than two orders of magnitude less Mean Time To Failure (MTTF) than MOS capacitors on n-type 4H-SiC, which indicates that reliability for operation up to 300°C will be nearly impossible.

JFETs on the other hand are free of gate oxide and use only p-n junctions in the active device area where high electric field stress occurs and so are not subject to oxide related reliability issues. Therefore JFETs can fully exploit the high temperature capability of SiC in a voltage controlled switching device. Another benefit of the JFET is that the threshold voltage is practically independent of temperature, (the pinch-off voltage  $V_p$  is determined by the channel doping and its geometry  $V_p = \frac{q \cdot N_D \cdot a^2}{2 \cdot \varepsilon_s} - V_{bi}$ , where  $N_D$  is the

channel doping, q is the electron charge, a is the half of the channel height and  $\varepsilon_s$  is the SiC permittivity). The change in the built in-voltage  $V_{bi}$  with temperature can be

neglected for  $V_p >> V_{bi}$ . In MOSFETs several temperature dependent factors result in a decrease of the threshold voltage with temperature

$$V_T = \sqrt{\frac{4.\varepsilon_s \cdot k.T.N_A \cdot \ln(N_A/n_i)}{\varepsilon_{ox}/t_{ox}}} + \frac{2.k.T}{q} \ln \frac{N_A}{n_i} - \frac{Q_{ss}(T)}{C_{ox}}, \text{ where } k \text{ is the Boltzmann constant,}$$

$N_A$  is the acceptor concentration in the channel region,  $n_i$  is the intrinsic concentration,  $\varepsilon_{ox}$  the permittivity of the oxide,  $t_{ox}$  is the oxide thickness,  $Q_{ss}$  is the interface charge and  $C_{ox}$  the oxide capacitance.

#### **1.2.3. JFET – A Better Choice for High Temperature Power Device**

Based on the above comparison at this point the JFET has a clear advantage over the MOSFET. As serious work is being done to solve different problems in the MOSFET, it might be improved in the future, however the JFET will still remain the device of choice for high temperature and harsh environment applications [8]. Experimental results show that 4H-SiC JFETs have a very wide temperature range of operation. 4H-SiC JFETs have been characterized at high temperatures up to 450°C [15] and down to cryogenic temperatures of 30K [16]. 4H-SiC JFETs have also demonstrated feasibility of at least 500h life at 500°C [17]. A DC-DC converter using 4H-SiC JFETs and 4H-SiC Schottky diodes was tested at ambient temperature up to 400°C [18]

Regarding the device structure, there are two main types of JFET – Lateral (LJFET), where the source, gate and drain terminals are all one side of the wafer and Vertical (VJFET), where the source and gate terminals are on the front side of the wafer and the drain terminal is placed on wafer backside. The VJFET structure allows higher cell packing density, and hence can achieve lower on-resistance. The LJFET structure, even

though offering lower packing density, has a clear advantage for realizing power integrated circuits.

Based on operation JFETs could be classified as normally-on (conducts high drain current at zero gate bias) or normally-off (blocks high drain-to-source voltage at zero gate bias). Normally-off structure is preferred from application point of view, as it ensures safe system operation. In a normally-off structure the channel has to be designed narrow enough to be pinched off at zero gate bias and at the same time to have e reasonable onresistance, which requires a precise control of the channel width. This leads to relatively smaller technology process windows and makes the process more challenging.

On the other hand normally-on JFETs can deliver lower on-resistance and are even desirable in certain applications. The disadvantage of the normally-on device can be overcome in applications by using a cascode configuration composed of a low voltage Si MOSFET and the high voltage SiC JFET [8, 12], however for this configuration the high temperature performance of the composed device will be limited by the Si MOSFET. A more attractive solution is a JFET cascode switch, based on SiC only. Such a switch has been demonstrated by combining a low-voltage normally-off SiC JFET, used as the controlling device, in series with a high-voltage normally-on SiC JFET, capable of blocking over 1000V with a specific on-resistance of 3.6 m $\Omega$ cm<sup>2</sup>, which could be operated at temperatures over 150°C [17]. Unfortunately for this solution the process challenges related to realizing high current normally-off SiC JFET will still be in effect.

High voltage normally-off SiC JFET can be more easily realized by combining a lateral, low voltage, normally-off JFET structure with a vertical normally-on, high-voltage structure [19-22]. However, the fabrication of this type of JFET is more

complicated and a low specific on-resistance is more difficult to achieve, compared to a pure lateral or vertical structure. The best results achieved with this kind of structure are 5.3kV 4H-SiC SEJFET with specific on-resistance (Rsp\_on) of  $69m\Omega cm^2$  [21] and a 4,340V,  $40m\Omega cm^2$  normally-off 4H-SiC VJFET [22].

Based on the above considerations a vertical JFET type is the most interesting for power device application, as it offers higher packing density than the lateral type, has a potential to achieve very low on-resistance and is simpler to realize than a combined lateral plus vertical structure.

Different approaches have been used to realize a vertical JFET structure. A SiC static induction transistors (SITs) was fabricated using e-beam lithography and vertical implantation [23, 24]. One disadvantage of this SIT structure is that because of the implantation scattering effect, the vertical channel does not have a uniform channel width. Another disadvantage is that longer channel length is difficult to achieve because it is determined by the implantation depth, which is limited by the ion implanter energy capability. Typical commercial implanters provide several hundred kiloelectron-volt ion implantations, and megaelectron-volt ion implantations, required to form a reasonably long vertical channel, have a very limited availability.

Another way to realize a vertical JFET structure uses the epitaxial regrowth approach [25, 26]. A very low on-resistance of  $1.0 \text{m}\Omega.\text{cm}^2$  with a blocking voltage of 700V was achieved using a buried gate structure [25]. Another device achieved and 1270V, and  $1.21 \text{m}\Omega.\text{cm}^2$ . However, the buried-gate SIT is likely to have issues during switching operation because the relatively long p-type buried gate without metal has a much larger resistance and, hence, a much larger gate RC time, compared to a vertical structure with

ohmic contact metal close to the p-gate region surrounding the channel. Also the fabrication process for this type of JFET is more complicated as it requires epitaxial regrowth in the middle of the processing.

The third type of a VJVET structure is the Trenched and Implanted VJFET (TIVJFET). It is simple to fabricate, as no epitaxial re-growth is needed, and it can achieve low specific on-resistance [27]. Normally-off performance can be achieved with a scalable design from 1.7kV to 14kV [28]. Normally-off 4H-SiC TIVJFET was reported, with R<sub>SP\_ON</sub> of  $3.6m\Omega.cm^2$  and blocking voltage of 1726V, corresponding to a figure of-merit (FOM) (V<sub>B</sub><sup>2</sup>/R<sub>SP\_ON</sub>) of 830 MW/cm<sup>2</sup>, which is 28 times better than the state-of-the-art silicon Cool-MOS power devices [29]. The first reported VJFET in the 10kV class is a TIVJFET and the highest blocking voltage reported for a TIVJFET is 11.1 kV with R<sub>SP\_ON</sub> of 124 m $\Omega$ cm<sup>2</sup> [30, 31]. Therefore the Trenched and Implanted VJFET structure is a very attractive approach to realize low on-resistance and high voltage power switching devices using a relatively simple fabrication process.

## **1.3.** Objectives of the Proposed Ph.D Thesis Research

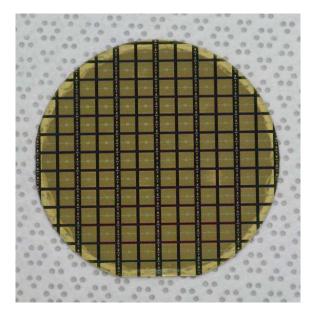

The objective of the proposed research is to develop unipolar power switches with blocking voltages from 300V to >10kV and low on-resistance. Normally-off and normally-on structures will be designed based on the TIVJFET concept. An 11kV normally-off TIVJFET will be designed and fabricated. A normally-off and normally-on 400V High Frequency TIVJFET (HF-TIVJFET) will be designed and fabricated. A normally-on 1.2kV TIVJFET will be designed and fabricated. Two different junction termination approaches (Junction Termination Extension and Guard Rings) will be investigated. Completely self-aligned method for defining source and gate contacts will

11

be pursued. Critical processing issues will be investigated in details and improved. A main goal of this work is to develop a simple and robust process to fully exploit the advantages of the TIVJFET structure.

# CHAPTER 2. BASIC TIVJFET STRUCTURE AND PROCESS DESIGN

# 2.1. Basic TIVJFET Structure Design

# 2.1.1. Unit Cell Design

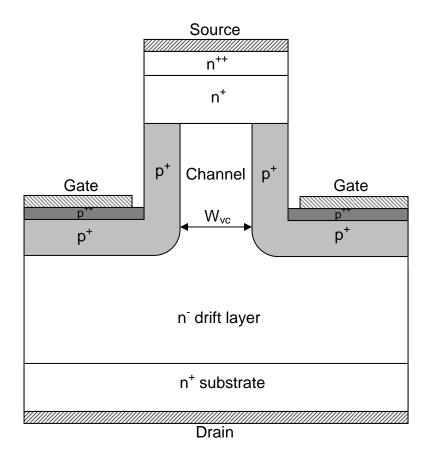

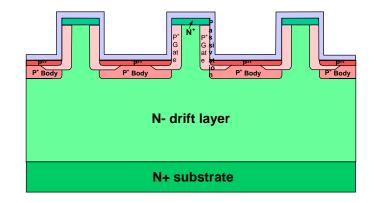

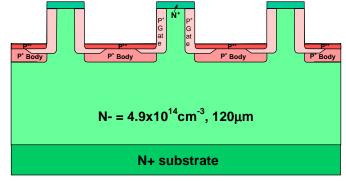

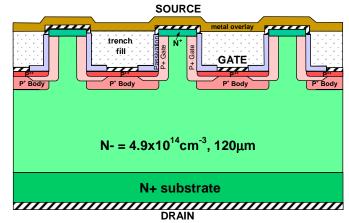

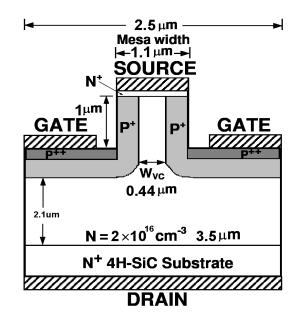

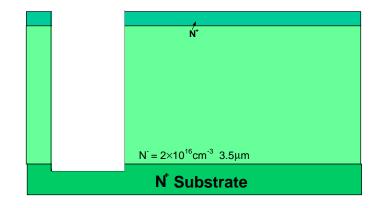

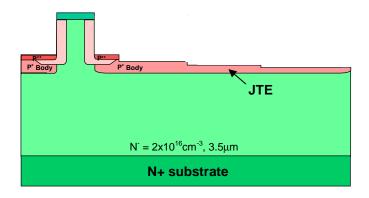

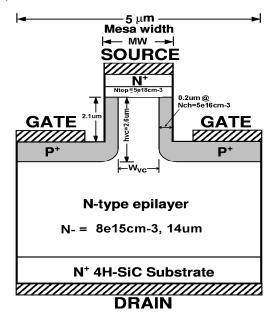

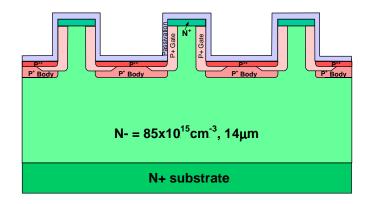

A cross sectional view of a unit cell TIVJFET structure is shown on Figure 2.1.

Figure 2.1. Unit Cell Structure of TIVJFET structure.

The wafer structure consists of three n-doped epitaxial layers. The upper heavily doped (>1×10<sup>19</sup>cm<sup>-3</sup>) n++ epilayer is used to create the source ohmic-contact. The next n+ epilayer is slightly more lightly doped to  $2-8\times10^{18}$ cm<sup>-3</sup>. It serves to define the vertical boundary of the gate-source p-n junction and provides a process margin for the planarization process used to fabricate the device. The third epilayer is used to form the

vertical channel and to support the voltage. Its thickness and doping are designed so that the device can support the required voltage. A vertical channel is formed by etching source mesas and implanting the gate. Normally-off or normally-on structures can be formed by choosing a vertical channel width. For a normally-off device the width of the channel is designed to be completely depleted at zero gate bias to ensure normally-off behavior. For a normally-on device channel is designed to be open at zero gate-to-source bias and its width is chosen so that it can be closed by applying a reasonable negative voltage to the gate with respect to the source. The width of the gate trench is chosen to be the minimum allowed by the fabrication process in order to maximize source-to-gate area ratio and device current density. The device is designed to be able to operate in a large temperature range from 70K to 600K. Since the vertical channel will become more "open" at higher temperature than at lower temperature due to the decrease of the p-n junction built-in voltage with temperature, the design should be performed at the highest temperature.

#### 2.1.2. Drift Layer Design

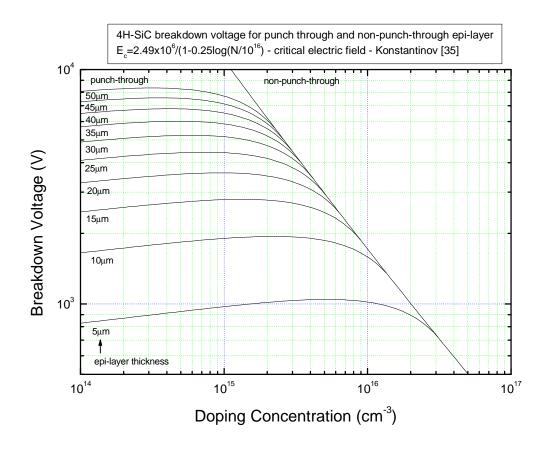

The breakdown voltage of the TIVJFET structure depends on the semiconductor critical field (electric field at which avalanche multiplication of current carriers by impact ionization will occur), epilayer doping, epilayer thickness, and device edge termination. Therefore epilayer doping and thickness can be determined from the desired breakdown voltage under parallel plane avalanche breakdown conditions. The desired epilayer doping is the maximum doping that will sustain the specified breakdown voltage. The relationship for the epilayer doping is [34]:

$$N_D = \frac{\varepsilon_s E_C^2}{2qV_B} \tag{2.1}$$

where  $E_C$  is the semiconductor critical field and  $V_B$  is the breakdown voltage.

The epilayer thickness is the reverse bias depletion region width at the breakdown voltage. The relationship for the epilayer thickness is [34]:

$$t_{epi} = \frac{2V_B}{E_C} \tag{2.2}$$

For 4H-SiC the critical field dependence on the doping concentration is described by [35]:

$$E_{C} = \frac{2.49 \times 10^{6}}{1 - \frac{1}{4} \log_{10} \left( \frac{N_{D}}{10^{16}} \right)}$$

(2.3)

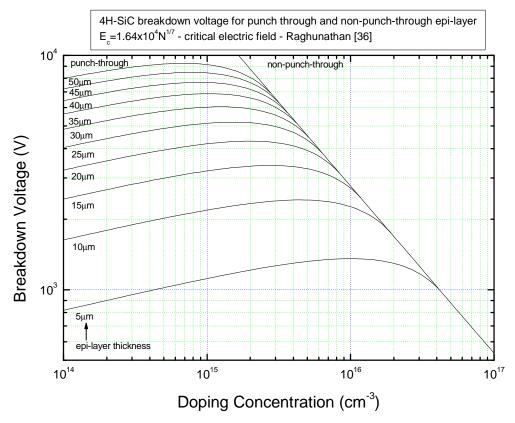

According to other authors [36] the critical field dependence on the doping concentration for 4H-SiC is:

$$E_c = 1.64 \times 10^4 N_D^{1/7} \tag{2.4}$$

Alternative epilayer doping and thickness can be used, based on the punchthrough concept. The punch-through structure has a smaller thickness to support the same voltage as a non-punch-through structure and thus can provide a lower on-resistance and a reduced wafer cost. The breakdown voltage of a punch-through diode can be calculated using the expression:

$$V_{PT} = E_C t_{PT} - \frac{1}{2} \frac{q N_{Dpt} t^2_{PT}}{\varepsilon_s}$$

(2.5)

where  $V_{PT}$  is the punch-through voltage,  $t_{PT}$  is the punch-through layer thickness.

The drift layer doping and thickness to support a desired voltage are calculated using equations (2.1-2.5). Results are shown on Figure 2.2-2.3 and can be used for choosing the right epilayer thickness and doping concentration. The values of the parameters will depend on the critical electric field chosen for the calculations. The two different models shown above give different numbers for the breakdown voltage and epilayer thickness.

Figure 2.2. Breakdown voltage vs. doping concentration for non-punch-through and punch-through 4H-SiC epilayers, based on Konstantinov's critical electric field [35].

Figure 2.3. Breakdown voltage vs. doping concentration for non-punch-through and punch-through 4H-SiC epilayers, based on Raghunathan's critical electric field [36].

# **2.1.3. Junction Termination Design**

In practice it is not possible to achieve the theoretically predicted avalanche breakdown voltage, because of two-dimensional and three-dimensional field crowding at contact and junction edges. Edge termination is necessary to reach the parallel plane breakdown voltage. Many different types of edge terminations have been used for power devices [33] including beveled edges, field plates, floating metal rings, p-type floating filed rings, junction termination extension. The most commonly used termination methods are these that use planar junctions, because they are compatible with the planar fabrication technology. Up to 80% of the ideal breakdown voltage could be achieved using floating field rings, and up to 95% using junction termination extension. For SiC, with its high

critical field, the last two techniques, which do not rely on dielectrics, should be the best choice.

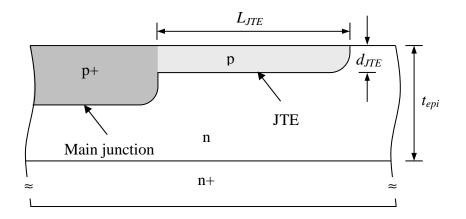

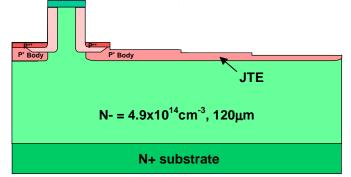

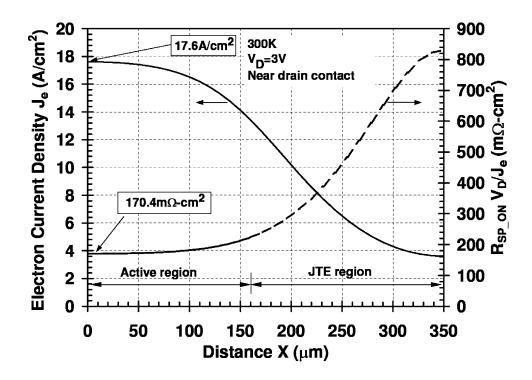

#### **2.1.3.1. Junction Termination Extension (JTE)**

Junction termination extension (JTE) technique [33] can give almost parallel plane breakdown voltage (up to 95%). It is convenient, because no complicated photolithography steps are needed and the amount of introduced charge can be precisely controlled by ion implantation. JTE region should be totally depleted at the required blocking voltage applied. Key parameters of JTE are the length  $L_{JTE}$ , the depth  $d_{JTE}$  and the doping concentration  $N_{JTE}$ . A schematic view of a p-n junction with JTE region is shown on Figure 2.4.

The length should be chosen to be larger than the epilayer thickness in order to reduce the field at the surface by supporting the same voltage with larger depletion width. However it should not be much larger than the epilayer thickness in order to save valuable wafer space. The implanted dose  $D = N_{JTE}d_{JTE}$  is determined by the maximum electric filed and is equal to  $\frac{\varepsilon_s E_c}{q}$ . If we express it in terms of the epilayer parameters it is:  $D = N_D t_{epi}$ , where  $N_D$  and  $t_{epi}$  are the epilayer doping and thickness respectively. Once we choose the dose, we can decide about  $d_{JTE}$  and  $N_{JTE}$ . Numerical analysis shows that for a given doping level of the junction extension, the breakdown voltage increases and then decreases, going through a maximum when the depth of the junction extension increases [37, 38].

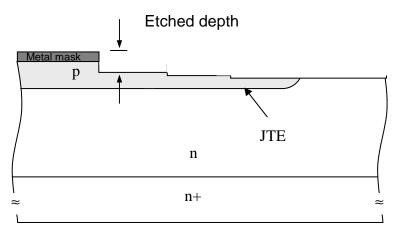

One problem with the JTE structure in SiC is the uncertainty in p-dopants activation, which can lead to ineffectiveness of the termination. A practical approach to realize a JTE structure is to implant it together with the gate and then remove as much of the implanted thickness as needed to achieve the right charge balance. This reduces the number of photomasks needed, saves one implantation step and eliminates the uncertainty in the p-dopant activation efficiency, as the actual JTE charge can be adjusted by etching after implantation and dopant activation. A multiple-zone JTE structure is more effective than a single-zone JTE. A three-zone JTE structure was chosen to be implemented. Figure 2.5 shows a schematic view of the JTE structure. The different zones are formed by additional etching steps.

Figure 2.5. Three-zone JTE structure, realized by implantation and subsequent surface etching.

There are two additional issues with JTE. First, the presence of surface charge over the implanted region can strongly affect the electric field distribution. This can cause high electric field to arise at the surface and wide variation of breakdown voltage from device to device. Second, the high electric field near the surface can cause excessive leakage current flow. In order to reduce the surface charge the semiconductor surface needs to be properly passivated.

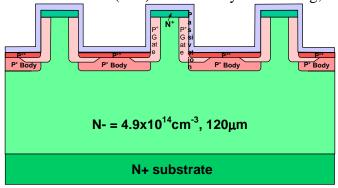

#### **2.1.3.2. Floating Guard Rings**

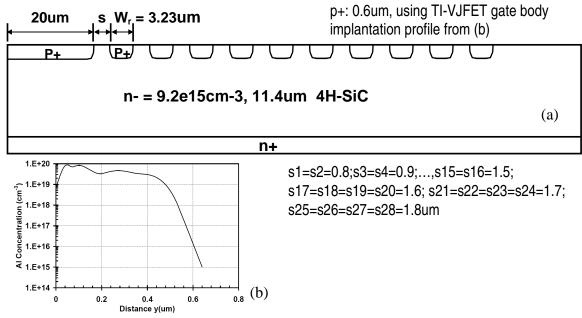

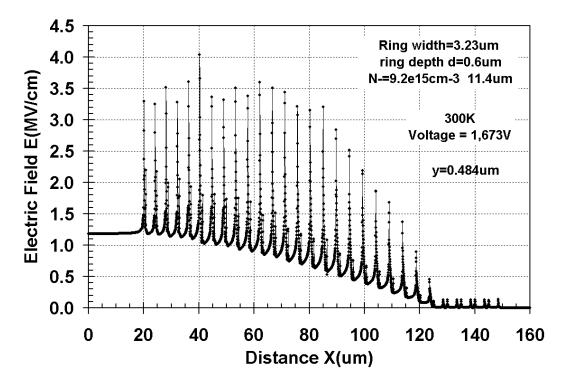

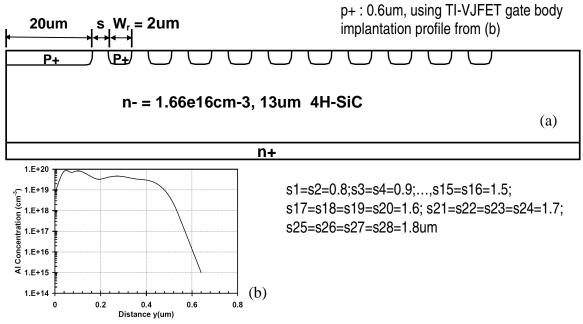

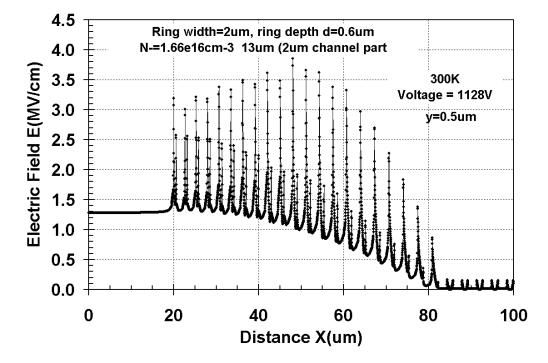

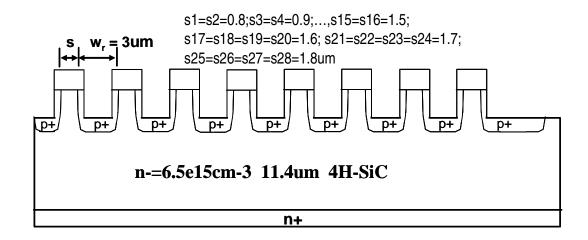

JTE is a very good termination technique as it can achieve breakdown voltage that is as close as possible to the theoretical limit. It, however, has the disadvantages of more complicated practical realization and sensitivity to surface charge. In order to simplify the fabrication process guard ring termination was also designed. The guard rings can be implanted together with the gate and no additional processing is required. The guard ring structure is shown schematically on Figure 2.6 and Figure 2.8. The design uses 28 rings with non-uniform spacing. The spacing increases from the main junction toward the device periphery. Numerical modeling shows that this termination structure can achieve more than 90% of the parallel plane breakdown voltage. By shifting the guard ring spacing proportionally (same amount for all spacings) the structure can serve for a range of drift epilayer doping. Figures 2.7 and Figure 2.9 show the maximum electric field at breakdown for two different epilayer doping levels.

The actual structure to be fabricated is shown on Figure 2.10. The guard rings are formed in the same manner and at the same time as the JFET gate. The spacing between the individual guard rings are defined with mesas etched together with the source mesas.

The whole guard ring structure is self aligned and requires no additional processing step, as it is formed together with the source and gate formation.

Figure 2.6. Guard ring structure (a) and Al implantation profile (b).

Figure 2.7. Maximum field in the device at 1673V.

Figure 2.8. Guard ring structure (a) and Al implantation profile (b).

Figure 2.9. Maximum field in the device at 1128V.

Figure 2.10. Floating guard ring structure, using etched mesas similar to the source mesas.

#### **2.1.4. Vertical Channel Design**

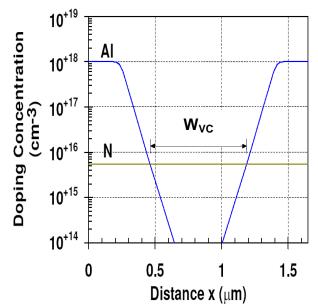

The design of the vertical channel is the most critical part of the unit cell design. The gate is formed by ion implantation. The channel width is defined by the width of the etched source mesa and the gate ion implantation depth. Three sets of Al implantation are applied on the lower half part of the gate trench to form the vertical channel and to create gate ohmic contact. The first Al implantation (p+) is applied mainly on the sidewall of the gate trench with a tilted angle so that a vertical channel with a certain height and opening can be established. The second Al implantation (p+ body) is applied on the bottom of the gate trench to form the last shallow Al implantation (p++) on the bottom of the gate trench to form the gate ohmic contact. The first Al implantation along a horizontal line across the channel is shown in Figure 2.11.

The implantation profile is simulated by ProfileCode<sup>™</sup> with Person IV distribution assumption [39]. It was previously found that the simulation software does not accurately predict the implantation tail [40] and the tail of aluminum is approximately modeled by a linear slope of  $0.1\mu$ m per decade. The implantation depth is defined by the intersection of the modeled implantation profile, including the approximated tail, and the channel doping concentration.

Figure 2.11. Gate implantation profile defining the vertical channel width.

# 2.2. Process Design

# 2.2.1. Major Fabrication Steps

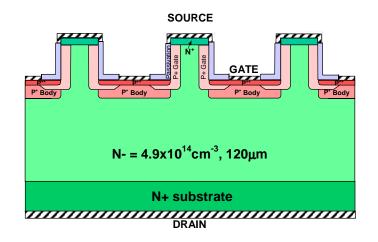

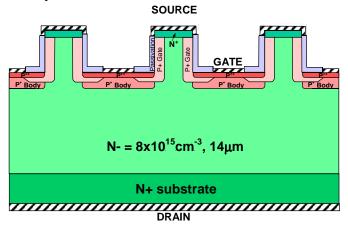

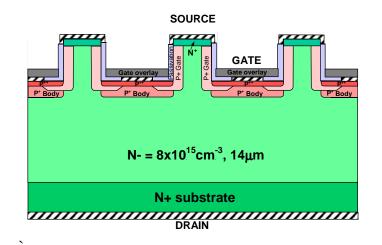

The major fabrication steps are as follows (Figure 2.12):

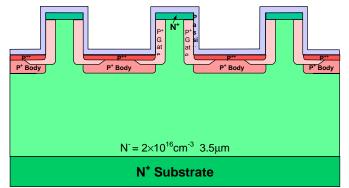

- Source mesa formation (Figure 2.12(b)).

- Gate and termination formation by p<sup>+</sup> implantation and dopant activation annealing (Figure 2.12(c)).

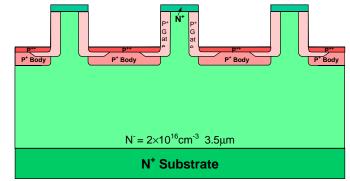

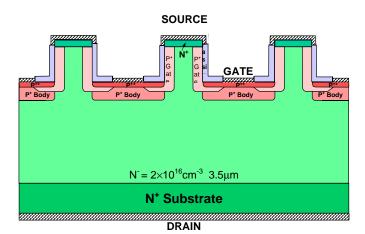

- Surface passivation by  $SiO_2$  and  $Si_3N_4$  (Figure 2.12(d)).

- Gate contact formation (Figure 2.12(e)).

- Source contact formation (Figure 2.12(e)).

- Drain contact formation (Figure 2.12(e)).

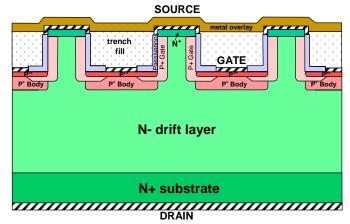

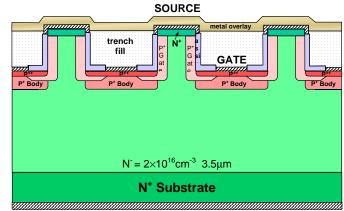

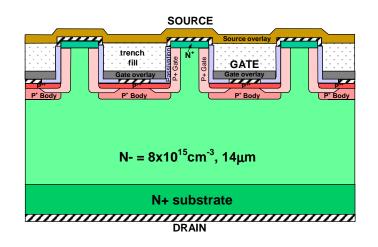

- Trench filling planarization (Figure 2.12(f).

- Source metal overlay formation (Figure 2.12(f)).

(c) Gate and junction termination formation by  $p^+$  implantation and dopant activation annealing;

(d) Surface passivation by  $SiO_2$  and  $Si_3N_4$ ;

(e) Gate, source and drain contact formation

(f) Trench filling planarization and source metal overlay formation

Figure 2.12. (a)-(f): Fabrication steps of TIVJFET structure.

Source mesa formation: The first part of the fabrication is the mesa-etching process

to create the mesas in the 4H-SiC epitaxial wafer pieces. The etching is done with an ICP

etching system; the etching masks are made of AlTi film, which is patterned by standard photolithography with wet chemical etching.

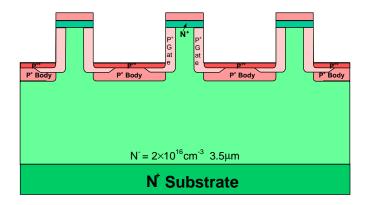

Gate and junction termination formation: Implantation for gate and junction termination includes three parts: body vertical implantation by high-energy implanter, sidewall skew implantation for gate p-type region and vertical implantation for p-type ohmic contact. Since n-type doping is done during epitaxial growth all implantations required for the device are Aluminum ion implantations. Post implantation annealing at 1550°C for 30 min in Argon is done to activate the implanted Al impurities and recover the damaged crystal structure. Two different approaches are considered for the junction termination – Junction Termination Extension (JTE) and Guard Rings (GR). The JTE is created by the Aluminum implantation done to form the vertical gate. The JTE region needs to be thinned down by dry etching in order to achieve the charge balance that will give the desired field suppression at the device periphery. The optimum etching depths of the JTE steps need to be determined experimentally on a test sample. After the optimal etch depth is found the etching of the main sample is done. Guard ring termination is created by etching ring mesas at the same time with the source mesas and later implanting the guard rings together with the gate implantation.

Surface passivation: After thorough cleaning samples are thermally oxidized at  $1100^{\circ}$ C for 30 min in wet O<sub>2</sub> ambient to form a sacrificial oxide. The sacrificial oxide is then removed and another thermal oxidation is done at  $1100^{\circ}$ C for 3 hours in wet oxygen ambient to passivate the surface. The oxide is then annealed at  $1100^{\circ}$ C for 1 hour in Ar. The thermal oxide is then covered with a PECVD Si<sub>3</sub>N<sub>4</sub> layer with thickness of 0.2µm.

Gate, source and drain contact formation: For the gate contact two options are possible - with alignment and with a self-aligned process. By the alignment method windows are opened in the passivation by photolithography and dry etching. Gate contact metal of Ti/TiN with a total thickness of 3000Å is deposited by sputtering on the sample surface. The metal is patterned by a lift-off process. The metal is finally annealed to get ohmic contact. Self-aligned process uses photoresist planarization. Metal layer of Ti/TiW with a total thickness of 3000Å is sputtered over the device active area. Photoresist planarization is then performed and the metal is etched from the source region surface by a wet etching process. The metal is annealed together with the source and drain metals. For the source ohmic contact a self-aligned lift-off process is utilized. First, the passivated surface is planarized by photoresist deposition. Second, the planarized surface is etched back until all the mesa tops are exposed. Then, Ni/TiW contacts are deposited by sputtering and lift-off. A contact to the drain is formed by sputtering AlTi/Ni (200/3000Å) on the wafer back side. High temperature annealing is done at a temperature  $\geq$  950°C to form both source and drain ohmic contacts. Alternative method for self aligned method for source and gate metal definition is possible, based on nickel silicides. After the ohmic contacts are formed the additional gate metal can be deposited to reduce the gate resistance. This is done by photoresist planarization and metal wet etching.

**Trench filling planarization and source metal overlay:** This fabrication step consists of two phases. First, thick dielectric material is deposited and then etched back to expose the source contacts. Second, thick metal overlay consisting of Al/Ti/Au is deposited and patterned. There are two choices for the planarizing dielectric. Polyimide is relatively easier to planarize, but its high temperature capabilities are limited. SiO<sub>2</sub> is

more difficult to planarize, but it ensures device performance capabilities at higher temperatures.

#### **2.2.2.** Critical Fabrication Steps – Challenges and Improvements

**Gate trench etching:** Channel width, especially for normally-off devices, is very sensitive to process non-uniformity. To establish a god control of the vertical channel width the fabrication process has to ensure line-width uniformity, good vertical mesa profile and smooth mesa sidewall. Photoresist spinning conditions should be adjusted to give maximum thickness uniformity. The metal mask wet etching conditions should be optimized to get uniform etching along the sample. Plasma-etching conditions should be refined to provide a vertical mesa sidewall as much as possible.

**Gate implantation:** Implantation for vertical gate is a critical step in the fabrication, as it defines the vertical channel width, which determines the device normally-off behavior. Aluminum is used to create the p-type regions. The gate implantation consists of three parts. First, an Aluminum vertical implantation is done to form the blocking junction. Second, the vertical gate is formed by Al implantation on the sidewalls. The third part of the implantation is shallow implantation with high concentration for the gate contacts. The most critical part of the design is the vertical sidewall implantation. This Al implantation needs to be done at a tilted angle so that the p+ regions are established with a certain thickness at the sidewalls. The tilt angle is chosen based on the consideration that shadowing from neighboring mesas should not occur. Another concern with the gate implantation. The mask should be patterned by photoresist planarization, metal deposition and lift-off. This method, however, is more time consuming and can achieve a

limited mask thickness. Another more practical approach is to do the implantation for gate without covering the source mesa tops with a mask. After the gate implantation the top of the source mesas is removed by planarization and dry etching process.

Self-aligned Gate and Source Contacts: One of the most challenging steps in the fabrication is to define gate contacts in the gate trenches. The gate trench is only about  $2\mu$ m-wide and it needs to be covered with metal, while keeping this metal safely away from the source contact that is on the top of the source mesa. The initial self-aligned process uses the following procedure for metal formation. The gate metal is defined by metal sputtering, photoresist planarization and metal wet etching. The source metal is defined by photoresist planarization, metal sputtering and metal lift-off process. For increased area devices the planarization nonuniformity becomes more significant and metal lift-off process becomes less reliable, which may lead to partial gate and source metal contact shorting.

A second method for source contact metal definition, based on a new self-aligned approach is possible without using a lift-off step. First, the gate is filled with silicon dioxide deposited by PECVD, prior to source metal deposition. Second, a photoresist planarization is performed. Third, a new self aligned method for source metal definition is applied, based on nickel silicides. The idea utilizes the fact that metals, such as nickel (Ni), react with SiC when heated to form silicides, but will not react with SiO2. Metal is deposited above the source (free of oxide) and the gate trench (covered with oxide). If the contact metal (Ni) is annealed at a high enough temperature it will react with SiC and form silicide on the source, but will not react with the oxide in the gate trench. Then the un-reacted nickel can be removed by wet etching, so only the silicide that is sitting on the source will remain.

Finally a third method is possible that uses self-aligned nickel silicide contacts for both the gate and the source.

Gate Overlay metal: The device layout is such that the gate is probed at a gate probing pad, which is located on one side of the device. Gate current flowing through the gate metal results in voltage drop along the gate, due to the gate metal resistance. Because the channel opening is controlled through a change in the depletion region width of the gate-to-source p-n junction by applying forward voltage to the gate (in forward conduction mode), it is sensitive to the applied voltage. The resistance of the gate metal, even if not very large, may cause a voltage drop enough to create different opening conditions for the channel in different regions of the device. A device consists of multiple channels connected in parallel. When the channels that are close to the gate probing pad are open and start conducting high current, other remote channels are not yet open enough. If the gate voltage is increased further more channels become fully open, but the control gate-to-source p-n junctions of the channels closer to the gate contact pad start injecting too much gate current. A p-n junction current increases exponentially with the applied voltage, so before all the channels get a chance to open completely some part of the gate starts conducting too much current and contributes most of the allowed gate current. In order to increase device current density and utilize fully the total device active area the gate metal resistance needs to be decreased. This can be done by increasing the gate metal thickness and using metals with lower resistivity.

# CHAPTER 3. NORMALLY-OFF HIGH VOLTAGE (11KV) TIVJFET 3.1. Device and Process Design

#### **3.1.1. Unit Cell Design**

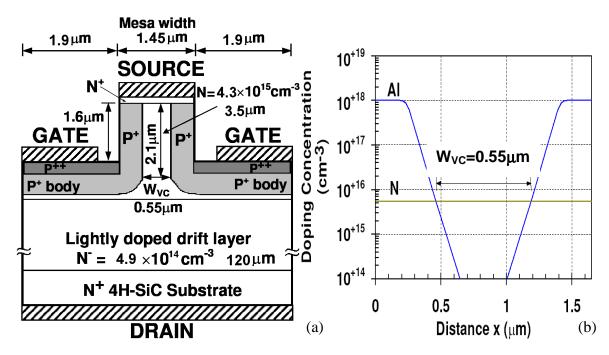

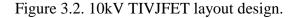

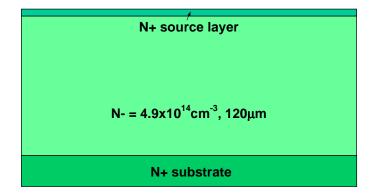

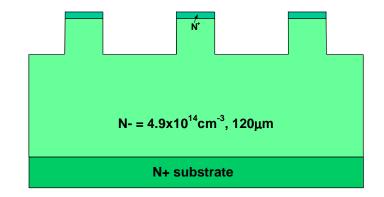

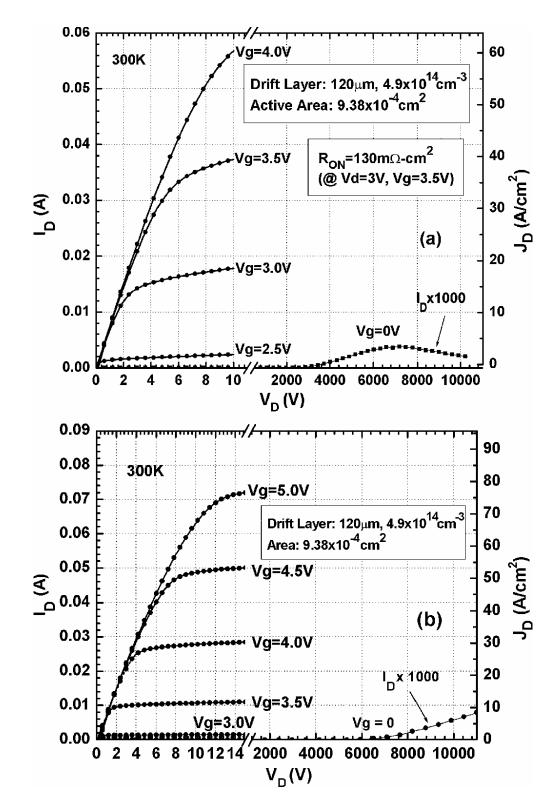

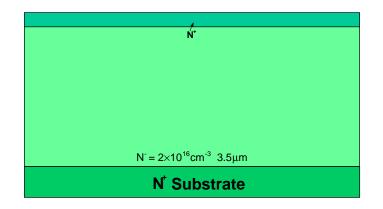

A cross sectional view of a unit cell TIVJFET structure is shown on Figure 3.1 The wafer structure consists of three n-doped epitaxial layers. The upper heavily doped (> $1 \times 10^{19}$  cm<sup>-</sup> <sup>3</sup>) n+ epilayer is used to create the source ohmic-contact. It also serves to define the vertical boundary of the gate-source p-n junction and provides a process margin for the planarization process used to fabricate the device. The second epilayer with a doping of  $4.3 \times 10^{15}$  cm<sup>-3</sup> and thickness of  $3.5 \mu$ m is used to form the vertical channel. The third epilayer is the drift layer that supports the voltage. The thickness of 120µm and doping of  $4.9 \times 10^{14}$  cm<sup>-3</sup> were designed so that the device can support a voltage of more than 10kV. A vertical channel is formed by etching source mesas and implanting the gate. The width of the channel is designed to be completely depleted at zero gate bias to ensure normallyoff behavior. The width of the gate trench is chosen to be minimum allowed by the fabrication process in order to maximize source-to-gate area ratio and device current density. The device is designed to be able to operate in a large temperature range from 70K to 600K. Since the vertical channel will become more "open" at higher temperature than at lower temperature due to the decrease of the p-n junction built-in voltage with temperature, the design should be performed at the highest temperature.

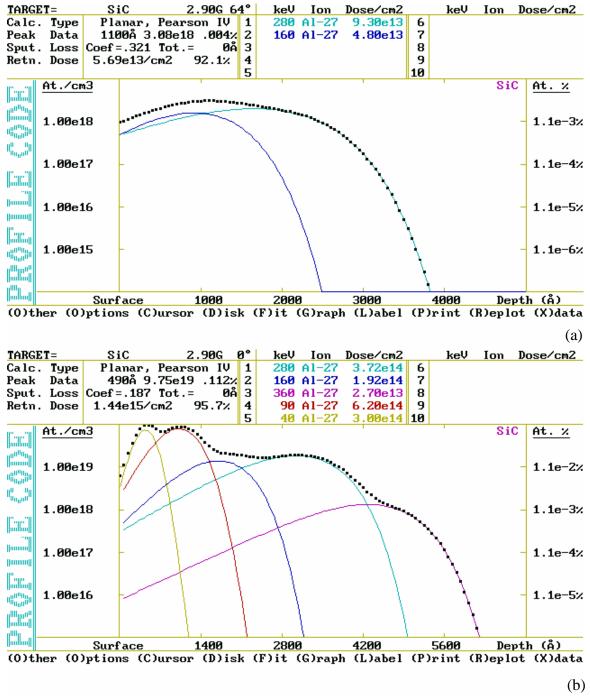

The gate is formed by ion implantation. The channel width is defined by the width of the etched source mesa and the gate ion implantation depth. Three sets of Al implantation are applied on the lower half part of the gate trench to form the vertical channel and to create gate ohmic contact. The first Al implantation (p+) is applied mainly on the sidewall of the gate trench with a tilted angle so that a vertical channel with a certain height and opening can be established. The second Al implantation (p+ body) is applied on the bottom of the gate trench to form the high-voltage blocking junction and the last shallow Al implantation (p++) on the bottom of the gate trench to form the gate ohmic contact. The designed profiles of p+ implantation along a horizontal line across the channel is shown in Figure 3.1(b).

Figure 3.1. (a) Unit Cell Structure of 10kV 4H-SiC TIVJFET; (b) Gate implantation profile.

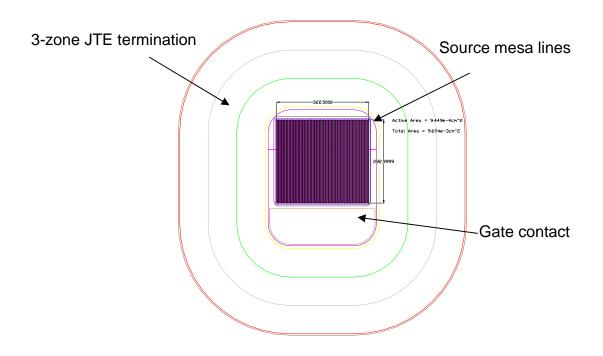

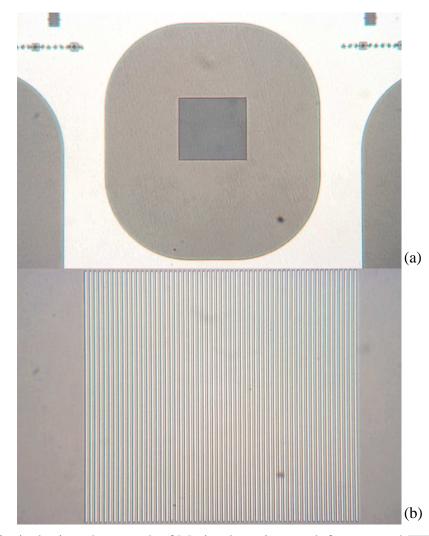

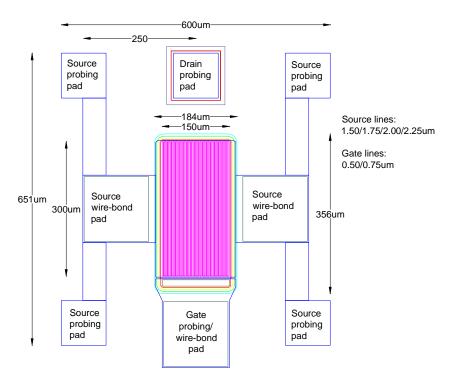

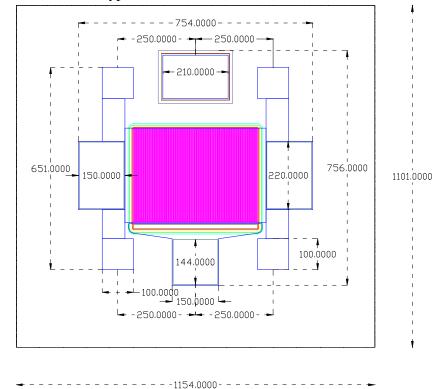

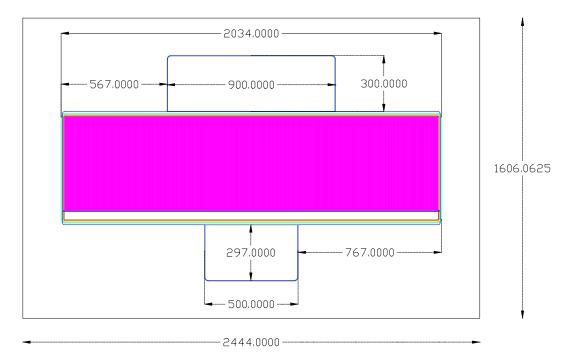

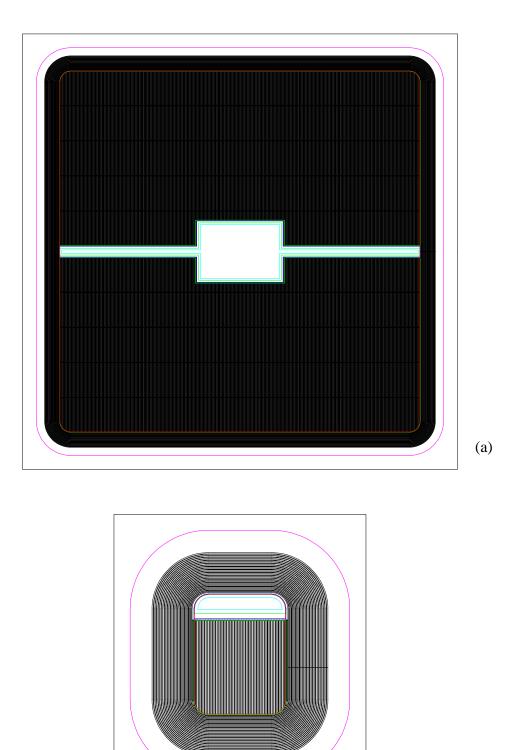

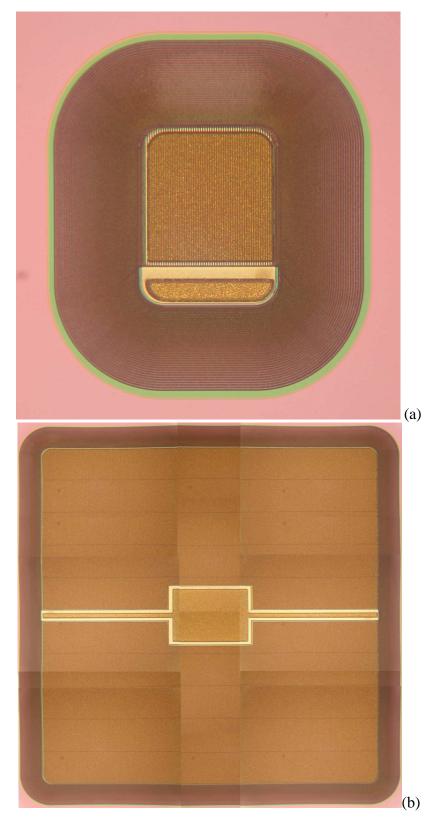

#### **3.1.2. Device Layout and Photomask Design**

The complete device layout design is shown on Figure 3.2. The active area contains a number of source lines ("fingers") surrounded by a gate region. A gate contact pad was designed with dimensions large enough to ensure probing and wire bonding capability. The device active area is surrounded by a three-step Junction Termination Extension (JTE) area that is used to suppress the high electric filed at device periphery. The width

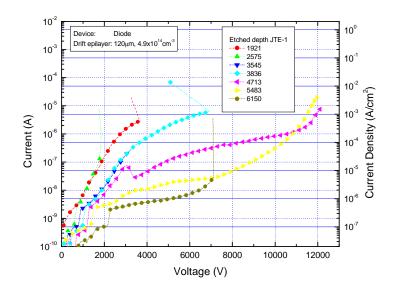

of each step is 100mm, forming a total width of 300mm, enough to ensure that the electric filed in the JTE region will be lower than the vertical filed in the bulk of the blocking epilayer. Test p-n diodes and TLM structures were also included in the design to evaluate the effectiveness of the termination and the quality of the ohmic contacts.

A set of masks suitable for self-aligned processing of SiC HF-TIVJFETs has been designed. This set of masks has been manufactured and used for the fabrication of the device. The mask set includes the following masks:

- (1) Source Mesas;

- (2) JTE-1;

- (3) JTE-2;

- (4) JTE-3;

- (5) JTE-Implant;

- (6) JTE-Mesa;

- (7) Gate Contact;

- (8) Gate Pad Window;

- (9) Metal Overlayer;

- (10) Planarization Help;

(11) Oxide Etching Active Area.

## **3.1.3. Process Design**

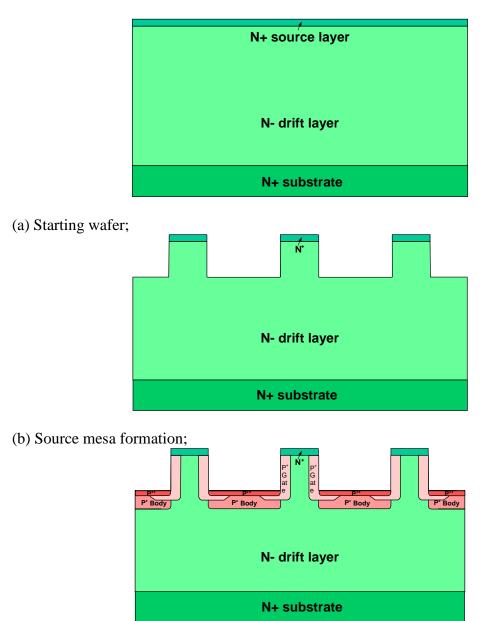

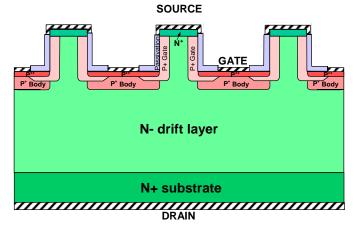

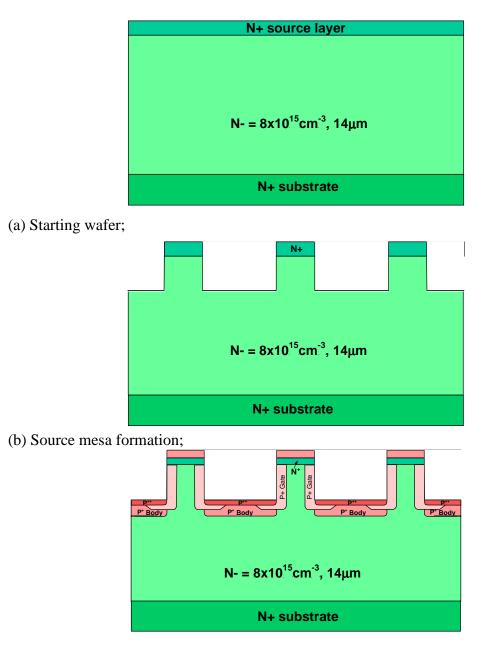

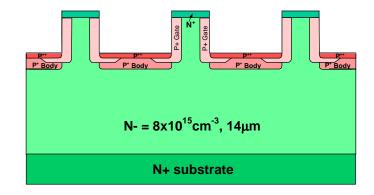

The major fabrication steps are as follows (Figure 3.3):

- Source mesa formation (Figure 3.3(b)).

- Gate and termination formation by p<sup>+</sup> implantation and dopant activation annealing (Figure 3.3(c)).

- Junction Termination Extension (JTE) formation by ICP etching (Figure 3.3(d)).

- Surface passivation by SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> (Figure 3.3(e)).

- Source contact formation (Figure 3.3(f)).

- Drain contact formation (Figure 3.3(f)).

- Gate contact formation (Figure 3.3(f)).

- Trench filling planarization and source metal overlay formation (Figure 3.3(g)).

(a) Starting wafer;

(b) Source mesa formation;

(c) Gate formation by p<sup>+</sup> implantation and dopants activation annealing;

(d) Junction Termination Extension (JTE) formation by ICP etching;

(e) Surface passivation by  $SiO_2$  and  $Si_3N_4$ ;

(f) Source, drain and gate contact formation

(g) Trench filling planarization and source metal overlay formation

Figure 3.3. (a)-(g): Fabrication steps of normally-off TIVJFET structure.

# **3.2.** Fabrication

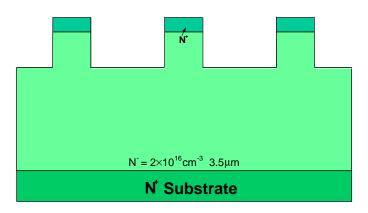

## 3.2.1. Source Mesa Formation

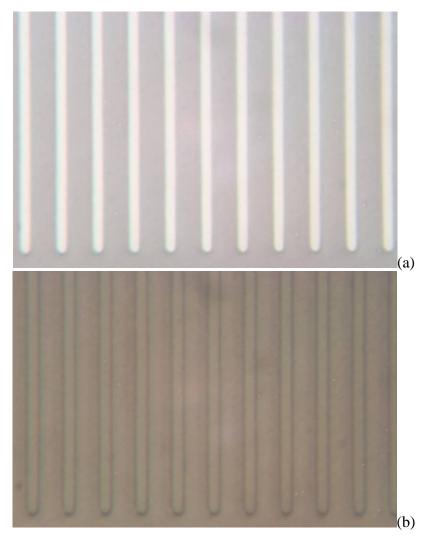

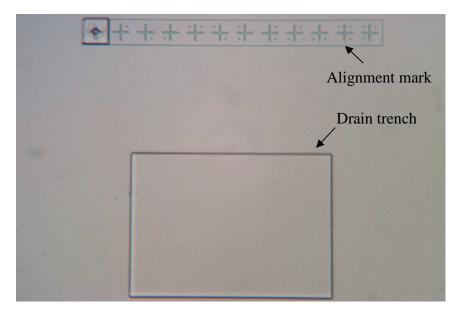

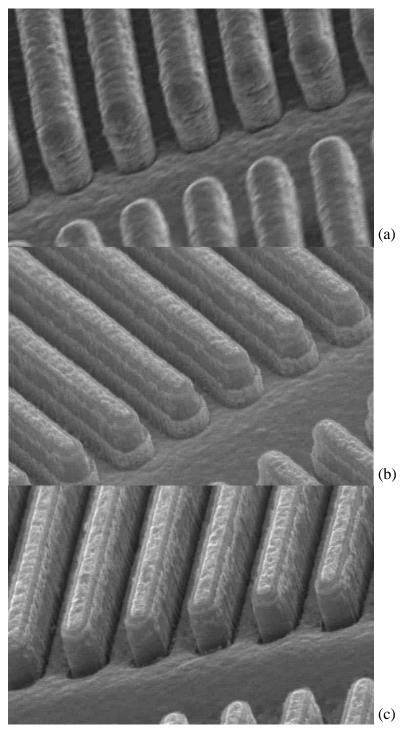

The device fabrication starts with etching of the deep trenches by inductively-coupled plasma (ICP) using CF<sub>4</sub> and O<sub>2</sub> gas mixture, forming a source mesa array. The etching masks are made of AlTi (Ti: 3.5% by weight) film, which is patterned by standard photolithography with wet chemical etching. A 2000-Å thick layer of AlTi was deposited by sputtering on the 4H-SiC wafer pieces. The deposited metal film was then patterned by the photomask "(1) Source mesa" for mesa definition with mesa width of  $2.25\mu$ m.

After that the gate trenches were etched in an ICP etcher in  $CF_4+O_2$  plasma. The etching was done in several runs and the final etched depth was  $3.2\mu m$ .

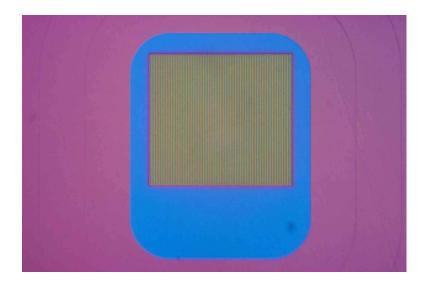

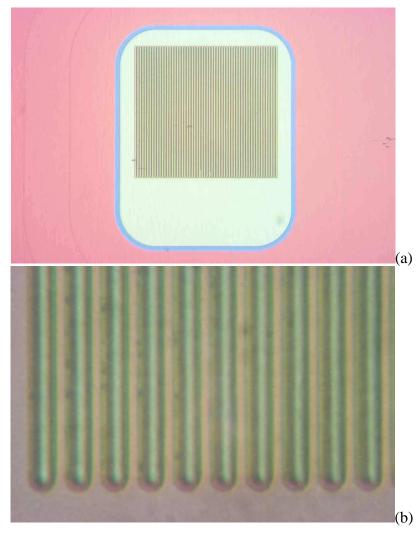

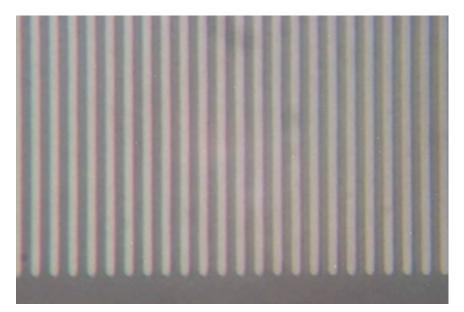

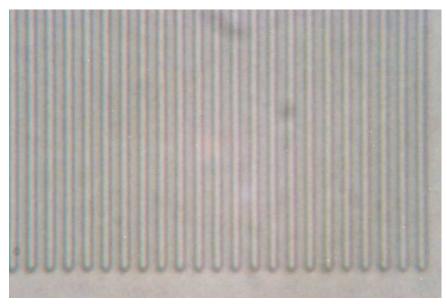

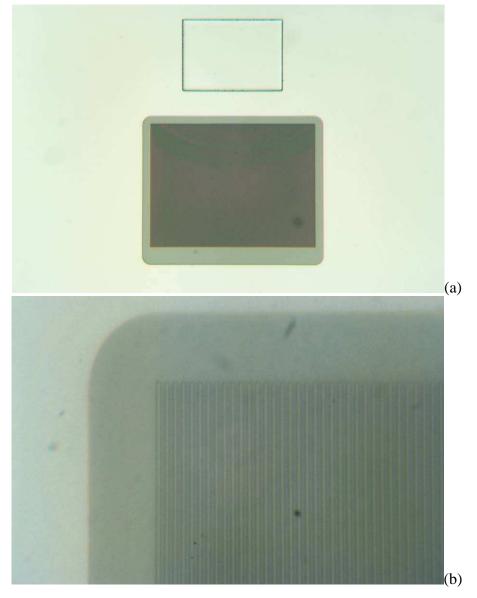

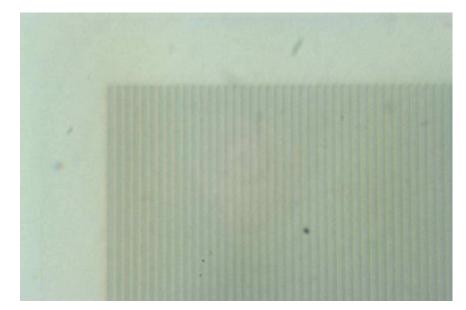

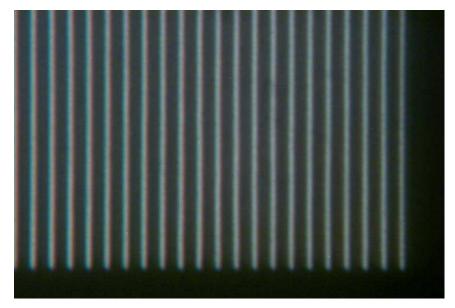

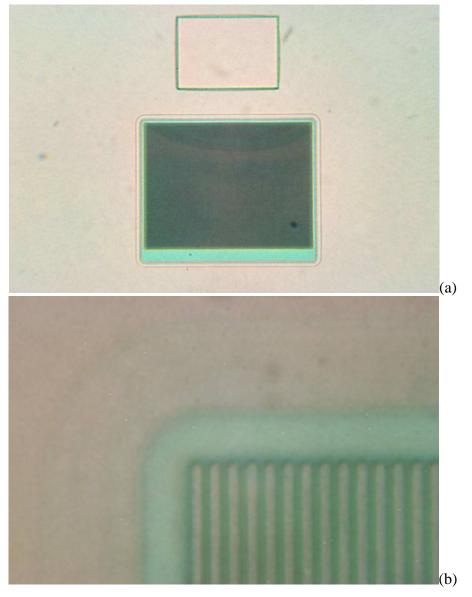

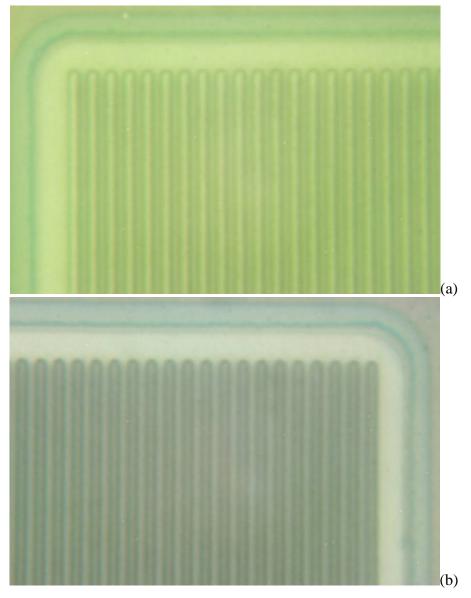

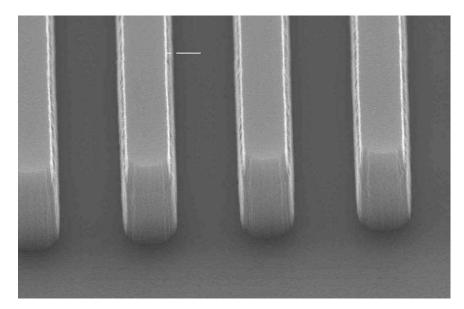

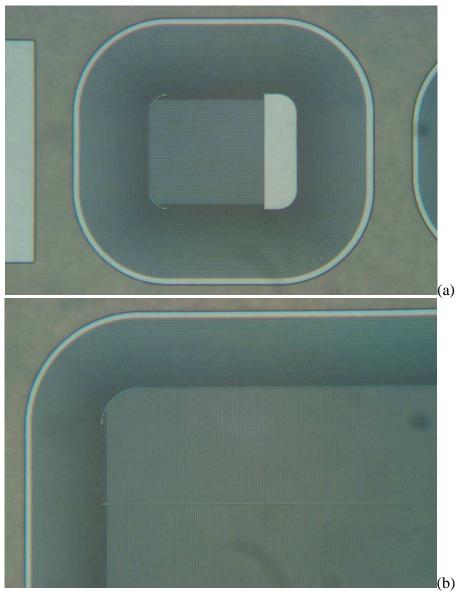

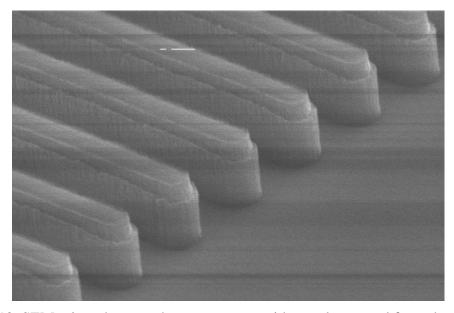

Figure 3.4. Optical microphotograph of source mesas: (a) AlTi pattern for ICP etching of source mesas; (b) etched source mesas. Structure period is 5.5µm.

## **3.2.2.** Gate and Termination Formation by P+ Implantation and Dopant

# **Activation Annealing**

Implantation for Gate and JTE include three parts: JTE vertical implantation by highenergy implanter, sidewall tilted implantation for gate p-type region and vertical implantation for p-type ohmic contact. Owing to the presence of the deep-trenched structures, self-alignment processes become possible based on planarizing the coating of photoresist and etching-back by oxygen plasma to expose the mesa tops for a blank metal sputtering and the subsequent self-aligned metal mask formation by lift-off. The implementation of the multi-step implantation structure of the gate becomes greatly simplified by the use of self-aligned implantation masks placed on the mesa top (Figure 3.5).

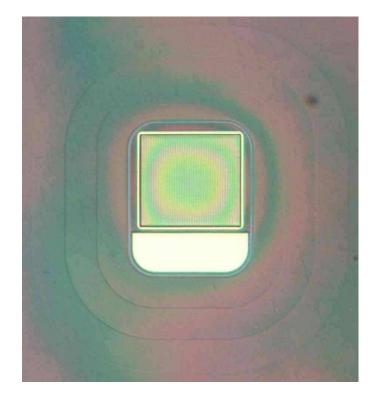

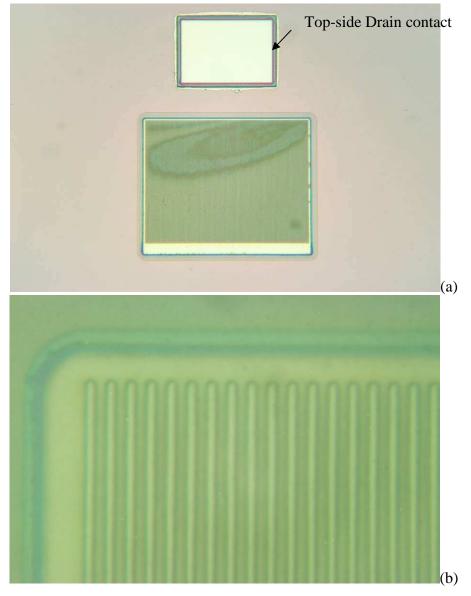

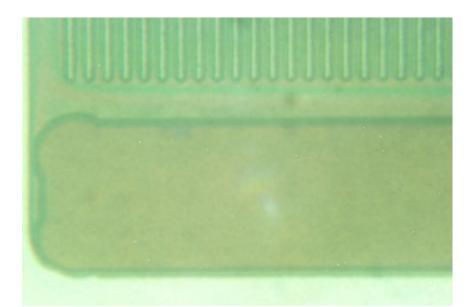

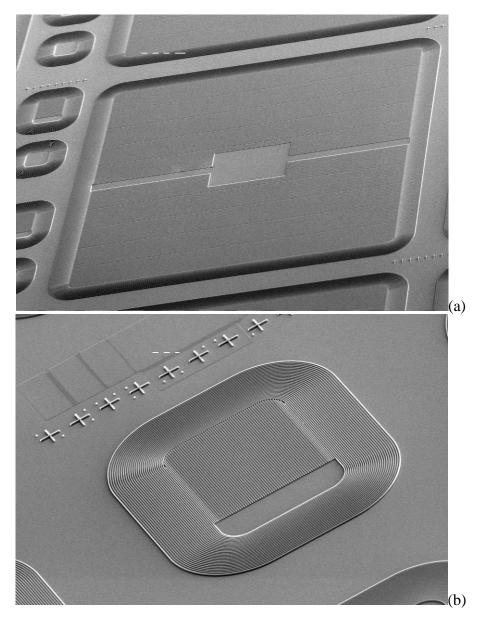

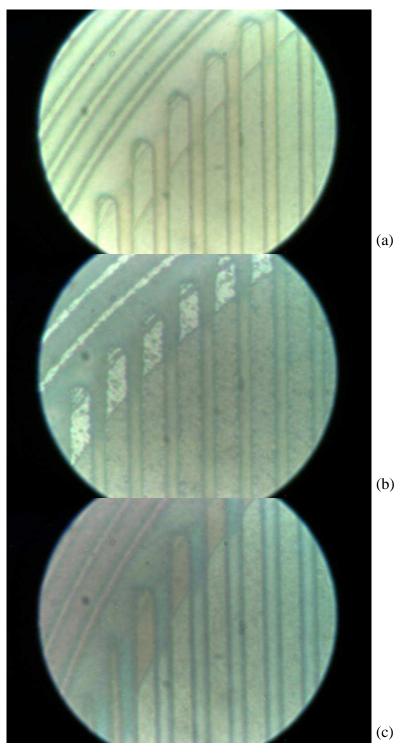

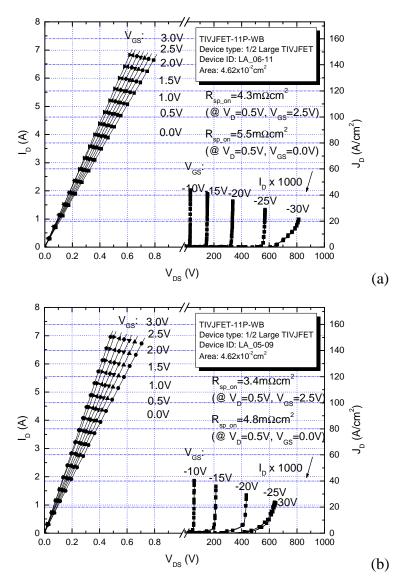

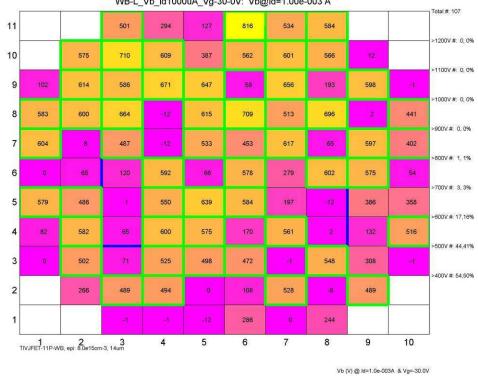

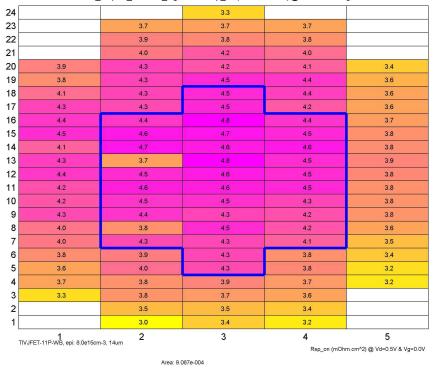

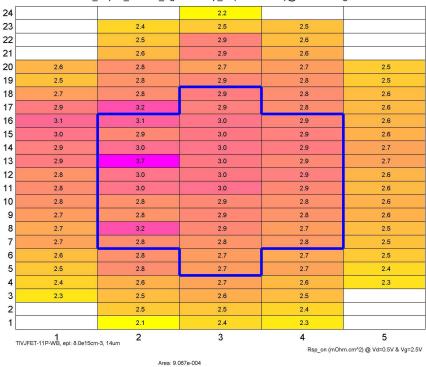

Figure 3.5. Optical microphotograph of Mo implantation mask for gate and JTE implantation (a) complete device view; (b) source mesa only view.