#### PHYSICAL LAYER DESIGN AND ANALYSIS OF WINLAB NETWORK CENTRIC

#### COGNITIVE RADIO

by

#### **TEJASWY HARI**

A Thesis submitted to the

Graduate School-New Brunswick

Rutgers, The State University of New Jersey

In partial fulfillment of the requirements

For the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Prof. Narayan Mandayam

And approved by

New Brunswick, New Jersey

October, 2009

©2009

Tejaswy Hari

ALL RIGHTS RESERVED

# ABSTRACT OF THE THESIS Physical Layer Design and Analysis of the WINLAB Network Centric Cognitive Radio

#### By Tejaswy Hari

#### Thesis Director: Prof. Narayan Mandayam

The wireless domain is ever expanding with new technologies and protocols emerging for all possible environments. Each new protocol is an improvement over the other. High performance FPGAs have entered the market with advanced signal processing capabilities which have vast resources and area to accommodate complex designs. The amalgamation of the two has given rise to programmable radios better known as cognitive radios. This thesis proposes the physical layer design and analysis of the WiNC2R- WINLAB Network Centric Cognitive Radio which is a SoC (System on Chip) based hardware platform on FPGA. This system is based on the Virtual Flow Paradigm. The key characteristic of this concept is that the protocol processing and selecting specific hardware accelerators is engaged dynamically by the software.

The WiNC2R consists of three main parts – the data layer, the interconnect layer and the control layer. All the data processing and functioning is handled by the data layer which is the focus of this thesis.

We have designed an adaptive modulator and demodulator for WiNC2R. These blocks exploit the advantages of software flexibility and hardware high speeds. It's an interprotocol operable processing engine that caters to all modulation schemes and can vary them on the fly. These engines show MIMO capabilities also due to their data flow independent design. The software interface to the register maps instantiated inside the processing engines which is used to configure the system before start of the frame.

We successfully sent OFDM frames implemented on Virtual Flow Paradigm across and performed timing and utilization analysis. The modulator and demodulator parameters can be conveniently setup in the software. The flexible hardware design enables fast switching between WiFi and WiMAX frames. The thesis starts with the design of top level architecture and further dig deeper the design of the Modulator and Demodulator processing engines. We then conclude with the timing and area resource analysis and discuss an improvement in design.

#### Acknowledgements

I would first like to thank my parents and family whose constant support and motivation has helped me throughout this journey. I would like to thank my advisors Prof. Narayan Mandayam for his constant guidance and help. I would like to thank Prof. Zoran Miljanic and Prof. Predrag Spasojevic for instilling a vision for this project and guiding me through the process. They have dedicated their valuable time and helped me complete my thesis. I am also indebted to my three most valuable mentors – Khanh Le, Renu Rajnarayan and Ivan Seskar. Their advice and never ending support has helped me gather the necessary expertise required to contribute to the team.

I would also like to thank the entire WiNC2R team – Sumit, Shalini, Vijyant, Madhura, Vaidehi, Akshay, Prasanthi, Mohit and Onkar. They taught me how dedicated team work can build monuments. I am grateful to be a part of this team. I also thank my friends for their support. And finally I would thank the staff at WINLAB for providing the facilities and support required for this thesis.

## Table of Contents

| Acknowledgements                                     | iv |

|------------------------------------------------------|----|

| Lists of tables                                      | ix |

| List of illustrations                                | xi |

| Chapter 1: Introduction                              | 1  |

| 1.1: Programmable Radios                             | 2  |

| 1.1.1: USRP                                          | 2  |

| 1.1.2: USRP 2                                        | 5  |

| 1.1.3: WARP                                          | 6  |

| 1.2: WINLAB Network Centric Cognitive Radio – WiNC2R | 9  |

| 1.3: Virtual Flow Paradigm                           | 9  |

| 1.3 Contribution                                     |    |

| Chapter 2: WiNC2R – Top level Architecture           |    |

| 2.1: Innovative Integration's X5-400M board          |    |

| 2.2: Steps for implementing on FPGA                  |    |

| Chapter 3: WiNC2R Top Level Architecture             |    |

| 3.1: Central Processors - Microblaze                 |    |

| 3.2: Processor Logic Bus v46 BUS                     |    |

| 3.3: Transmitter Architecture           |    |

|-----------------------------------------|----|

| 3.2 Receiver Architecture               |    |

| 3.3: System Flow                        |    |

| 3.3.1: Transmitter Flow for OFDM        |    |

| 3.3.2: Receiver Flow for OFDM           |    |

| Chapter 4: Functional Unit Architecture |    |

| 4.1: Bus Interface                      |    |

| 4.2: Unit Control Module Wrap           |    |

| 4.2.1: UCM                              |    |

| 4.2.2: Buffers                          |    |

| 4.2.3: Task Descriptor (TD) Table       | 39 |

| 4.2.4: GTT Table                        | 40 |

| 4.2.5: Task Scheduler Queue             | 40 |

| 4.2.6: Register Maps                    |    |

| 4.2.7: Arbiters                         |    |

| 4.2.8: DMA Engine                       |    |

| 4.2.9: Processing Engine                |    |

| Chapter 5: Processing Engine (PE)       |    |

| 5.1: PE Modulator                       | 45 |

| 5.1.1: Input Interface                     |    |

|--------------------------------------------|----|

| 5.1.2: Processing Engine                   | 46 |

| 5.1.3: Output Interface                    | 51 |

| 5.2: PE – Demodulator and Checker          |    |

| 5.2.1: PE Demodulator                      |    |

| 5.2.2: PE Checker                          | 57 |

| 5.3: PE Testbench                          | 61 |

| 5.3.1: Device under Test                   | 62 |

| 5.3.2: Reference Text Files                | 62 |

| 5.3.3: Testbench Components                | 66 |

| Chapter 6: PE Register Maps and Software   | 68 |

| 6.1: Register Map                          | 68 |

| 6.2: Address Allocation                    | 74 |

| 6.3: Software on WiNC2R                    |    |

| Chapter 7: Resource Utilization and Timing |    |

| 7.1: FPGA Resource Utilization             |    |

| 7.1.1: Transmitter Utilization             |    |

| 7.1.2: Receiver Utilization                |    |

| 7.2: Timing Analysis                       |    |

| 7.3: Parallel Implementation Design an | d Analysis |

|----------------------------------------|------------|

| Chapter 8: Conclusion                  |            |

| References                             |            |

| Abbreviations                          |            |

## Lists of tables

| Table 1.1: Details of FPGA on USRP – Altera Cyclone EP1C12      |    |

|-----------------------------------------------------------------|----|

| Table 1.2: Details of FPGA on WARP – Xilinx Virtex2 Pro XC2VP70 |    |

| Table 2.1: Details of Virtex5 FPGA                              |    |

| Table 5.1: PE Modulator Command Parameter                       |    |

| Table 5.2: Mapping Table                                        | 50 |

| Table 5.3: PE DmodChkr Command Parameters                       |    |

| Table 5.4: Chunk Sizes for WiFi                                 | 60 |

| Table 6.1: Normalization factors for various modulation schemes | 71 |

| Table 6.2: Modulator Status Register                            |    |

| Table 6.3: Demodulator Checker Status Register                  |    |

| Table 6.4: PE RAMs Address Offsets                              | 75 |

| Table 7.1: Transmitter Utilization                              |    |

| Table 7.2: Receiver Utilization                                 |    |

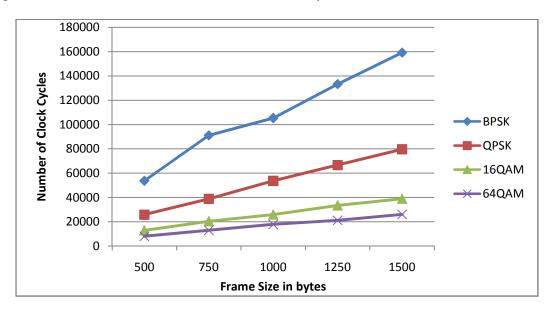

| Table 7.3: Modulation Latency                                   |    |

| Table 7.4: Latency w.r.t OFDM symbols                           |    |

| Table 7.5: PE Demodulator and Checker Latency                   |    |

| Table 7.6: Demod. Latency w.r.t OFDM Symbols                    |    |

| Table 7.7: Total PE Latency                                     | 83 |

| Table 7.8: Latency Reduction in Modulator                       | 85 |

| Table 7.9: Latency Reduction in Demodulator                     |    |

| Table 7.10: Parallel Modulator Area Utilization                 |    |

| Table 7.11: Parallel Demodulator Area Utilization | 88 |

|---------------------------------------------------|----|

|---------------------------------------------------|----|

## List of illustrations

| Figure 1.1: USRP Block Diagram[4]               | 5  |

|-------------------------------------------------|----|

| Figure 1.2: WARP Top Level Architecture[5]      | 7  |

| Figure 1.3: ADC/DAC interface blocks of WARP[5] | 8  |

| Figure 1.4: Hardware and Virtual Pipelining [9] | 11 |

| Figure 1.5: Software in WiNC2R                  | 12 |

| Figure 1.6: Hardware Platform Comparison[3]     | 13 |

| Figure 2.1: X5-400M Top Level Architecture[8]   | 17 |

| Figure 3.1: NCP top level architecture          | 24 |

| Figure 3.2: Transmiter Architecture             | 28 |

| Figure 3.3: Receiver Architecture               | 30 |

| Figure 3.4: Transmit Control Flow               | 32 |

| Figure 3.5: Receiver Command Flow               | 33 |

| Figure 4.1: Functional Unit Architecture        | 36 |

| Figure 4.2: Buffer Partition                    | 38 |

| Figure 5.1: Processing Engine Top Level Diagram | 44 |

| Figure 5.2: PE Modulator                        | 45 |

| Figure 5.3: Complex Number Representation       | 50 |

| Figure 5.4: PE Demodulator and Checker          | 52 |

| Figure 5.5: Demodulator Output RAM              | 56 |

| Figure 5.6: PE Checker                          | 58 |

| Figure 5.7: PLCP Header Contents[15]            | 58 |

| Figure 5.8: PE Test Bench Top Level Architecture | 62   |

|--------------------------------------------------|------|

| Figure 6.1: PE Mod Register Maps                 | 68   |

| Figure 6.2: 802.11a constellation diagram        | 70   |

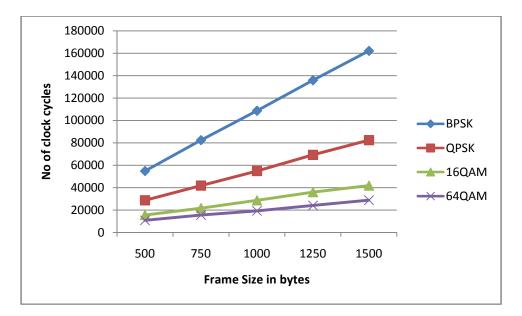

| Figure 7.1: Modulation Latency Graph             | 81   |

| Figure 7.2: Demod. Latency for various frames    | 83   |

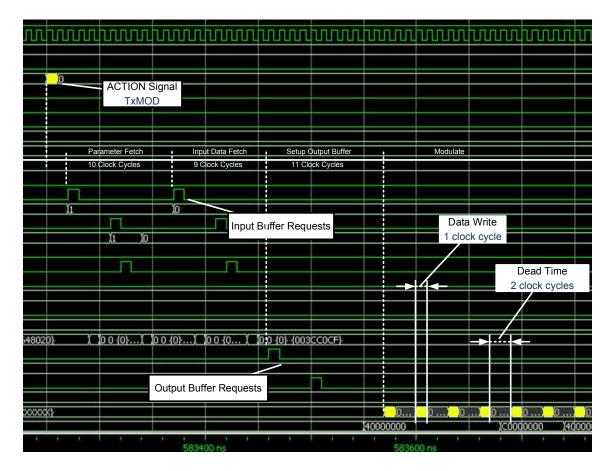

| Figure 7.3: Modulator Timing Diagram             | . 84 |

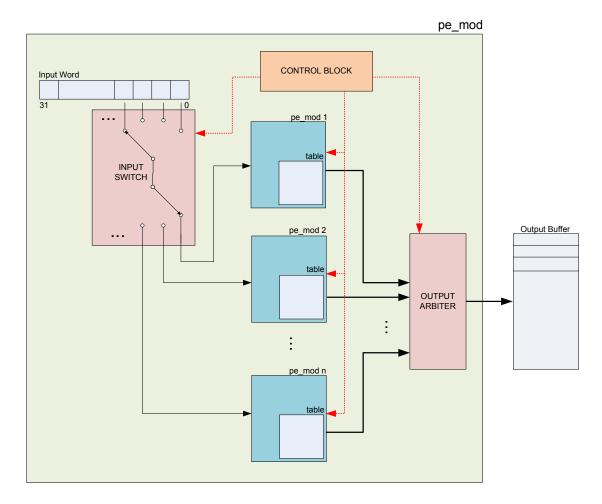

| Figure 7.4: Parallel Modulator Implementation    | 85   |

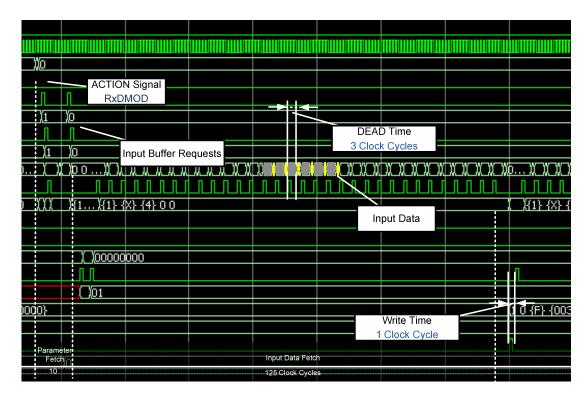

| Figure 7.5: Demodulator Timing Diagram           | 86   |

| Figure 7.6: Parallel Demodulator Implementation  | 87   |

## Chapter 1:

## Introduction

The exponential growth of the wireless industry is clear and evident in all aspects. Cell phones are now coming equipped with all protocol operability, wireless speeds are slowly surpassing the wired and remote areas are no longer remote. This has been possible with developments in physical and MAC layer research, exploding progress in semiconductor industry and blooming of various languages and scripting tools. The advent of cognitive radios- radios that can change transmission and receiving parameters based on the environment is further evidence. These platforms possess inter-operability and efficient spectrum usage and fast data rates are their main objectives. They will require flexible physical and complex network layer processing and agility.

Such platforms have not yet entered the commercial market; they are still in the research phase. The WINLAB Network Centric Cognitive Radio is such a platform that promises both speed and flexibility in the multilayer domain of mobile multimedia IP based communication. Its goal is to provide a scalable and adaptive radio platform hence the design is SoC oriented and FPGA based. The WiNC2R is an excellent platform for the research domain for analysis of the mobile applications computing, communication and control requirements, performance analysis of the applications, hardware vs. software implementation tradeoff analysis. It will also be useful for understanding the potential and limitations of traditional CPU architecture in addressing the needs of the emerging wireless communications in heterogeneous environments. Thus, this platform will not only provide a wireless testbed for academia but also a smart wireless device for various applications.

The following section will illustrate few such platforms that have pre-defined functions that can be programmed by the user.

### 1.1: Programmable Radios

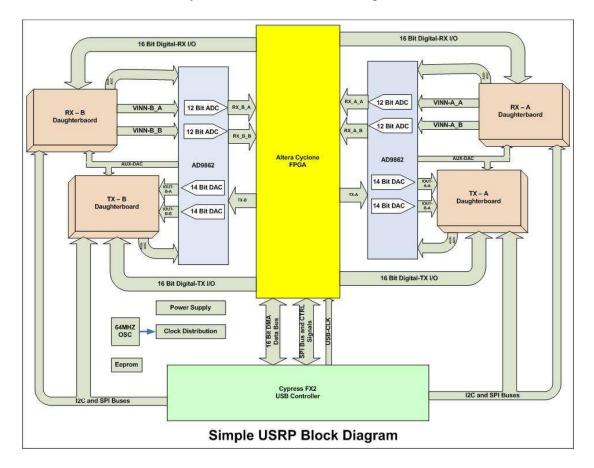

#### 1.1.1: USRP

The Universal Software Radio Peripheral is the hardware interface between RF and GNU software. It is built for general purpose computers to function as high bandwidth software radios. It works in baseband frequencies.

The advantage of using USRP is that all the signal processing is done in software, thus avoiding complex HDL language code. GNU uses python code to perform all processing engine functions. The high speed operations like digital up and down conversion, decimation and interpolation are done on the FPGA.

The users can develop a wide range of signal processing codes without worrying about the hardware capability and resources. The powerful combination of flexible hardware, open-source software and a community of experienced users make it the ideal platform for your software radio development.

Details of USRP hardware boards [4]

- 4 high-speed analog to digital converters (ADCs), each at 12 bits per sample, 64MSamples/sec.

- 4 high-speed digital to analog converters (DACs), each at 14 bits per sample, 128MSamples/sec.

- Altera Cyclone EP1C12 FPGA

- FPGA connects to a USB2 interface chip, the Cypress FX2, and the computer.

- The FPGA connects to a USB2 interface chip, the Cypress FX2. The FPGA circuitry and USB Microcontroller is programmable over the USB2 bus.

| Feature               | EP1C12          |

|-----------------------|-----------------|

| LEs                   | 12,060          |

| RAM Blocks - M4K      | 52              |

| Total RAM bits        | 92,160          |

| PLLs                  | 2               |

| Max user I/O pins     | 249             |

| Differential Channels | 103             |

| Temperature           | -40°C to +125°C |

The FPGA used is the Altera Cyclone EP1C12 FPGA whose details are given below. [6]

Table 1.1: Details of FPGA on USRP – Altera Cyclone EP1C12

As mentioned before, FPGA programming is used to interface the ADC and DAC IO ports to the data-out from the USB. The configuration typically includes digital down converters (DDC) implemented with 4 stages cascaded integrator-comb (CIC) filters.

CIC filters are very high-performance filters using only adders and delays. There are decimators and interpolators so that the data rate adjusts to USB interface or the RF. Each DDC has two inputs I and Q. These values are interleaved when multiple channels are used. The USRP block diagram is shown in Figure 1.1 [4]

#### Software

The software GNU uses is the Linux C++ where the application program interfaces with USRP. GNUradio provides USRP interface libraries which have to be linked with the user code. Most of the signal processing is done in C++. Python and SWIG are used to connect the blocks together and generate a flow. So the data that is output from the software can be fed directly to the DAC for transmitting.

#### Figure 1.1: USRP Block Diagram[4]

Many complex systems are easily realizable by software radio. Fast processors, everexpanding memory and high level programming have made it easy for designers and researchers in the wireless domain to implement communication systems.

The disadvantages of SDRs are

- Whenever a block or function call is invoked, the flow switches to and fro to the CPU processor. This drastically increases processing latency.

- USRP also restricts data flow through USB2.0 which is not scalable.

- Expertise in SDRs require proficiency in multiple languages C++ and Python for software and HDL for configuring FPGA

#### 1.1.2: USRP 2

The USRP2 is an improvement over the USRP board and it has the following additional features [4].

- Gigabit Ethernet interface

- 25 MHz of instantaneous RF bandwidth

- Xilinx Spartan 3-2000 FPGA

- Dual 100 MHz 14-bit ADCs

- Dual 400 MHz 16-bit DACs

- 1 MByte of high-speed SRAM

- Locking to an external 10 MHz reference

- 1 PPS (pulse per second) input

- Configuration stored on standard SD cards

- The ability to lock multiple systems together for MIMO

- Compatibility with all the same daughterboards as the original USRP

This board has a high performance RF end and a large FPGA. But the data processing still is implemented in software, this means that the processing speed depends on the CPU on which the GNU software is implemented. Hence, the data rate is still bottlenecked at the software.

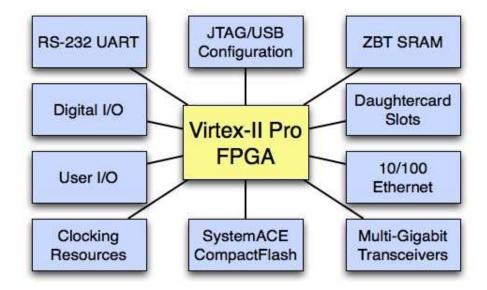

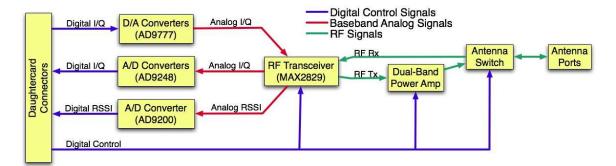

#### 1.1.3: WARP

WARP is Rice University's programmable hardware platform. It stands for Wireless Open Access Research Platform. Xilinx's Virtex 2 FPGAs provide vast recourses for hardware programmability. Like USRP, WARP also has four daughterboard slots that support wide range of input-outputs. It comes with its own programming tools.

The details of the board are given below [5]

- USB and serial port connectivity to PC

- PowerPC 405 Processor

- Rocket IO Trans-receiver

- Xilinx's SystemACE CompactFlash chip for managing the configuration process of the FPGA. The SystemACE chip acts as an interface between the FPGA and a standard CompactFlash slot.

- 160MS/s 16-bit dual DACs AD9777

- 65MS/s 14-bit dual-ADC AD9248

The top level architecture of WARP is shown below :

Figure 1.2: WARP Top Level Architecture[5]

The FPGA contains the user logic. The FPGA can be programmed by using VHDL or any other HDL. Typically Matlab and simulink is used to create the bit file that gets loaded into FPGA.

Details of Virtex2 Pro XC2VP70 are given in the table below [6]

| Feature                         | XC2VP70 |

|---------------------------------|---------|

| Rocket IO Trans-Receiver Blocks | 20      |

| Power PC Processor blocks       | 2       |

| Logic Cells                     | 74,448  |

| CLB                             |         |

| Slices                  | 33,088 |

|-------------------------|--------|

| Max distribution RAMs   | 1,034  |

| Multiplier Blocks 18x18 | 328    |

| BRAM                    |        |

| 18Kb Blocks             | 328    |

| Max Block RAMs          | 5,094  |

| DCM                     | 8      |

| Max user I/O Pins       | 996    |

Table 1.2: Details of FPGA on WARP – Xilinx Virtex2 Pro XC2VP70

The platform has 2 ADC and 1 DAC as shown in the Figure 1.3. This radio board is connected to one of the daughtercard slots.

Figure 1.3: ADC/DAC interface blocks of WARP[5]

#### Software

The Open access repository provides the model for the full SISO and MIMO OFDM transceiver implemented in Simulink.

The processor used is PowerPC linked to On-chip Peripheral Bus (OPB). OPB is a synchronous bus that provides separate 32bit addresses and data paths. The data read and write are implemented with multiplexers. The System Generator tool is responsible for converting the Matlab code & Simulink blocks to VHDL. The blocks are first created and linked in Simulink. Once the design is ready, System Generator is invoked and it performs synthesis and place and route. This design is then loaded to the FPGA.

#### Disadvantages of WARP

- Limitations to the FPGA resource space compared to the vastness of software radio resources.

- Limitations to Communication blocks in MATLAB's Xilinx blockset

#### 1.2: WINLAB Network Centric Cognitive Radio – WiNC2R

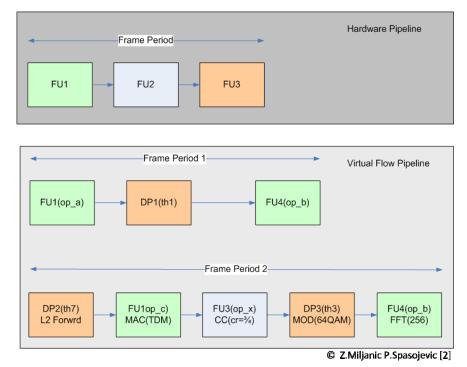

WiNC2R is a network centric cognitive radio developed at WINLAB, Rutgers University. WiNC2R is a proof of concept design that implements the Virtual Flow Paradigm (VFP) on FPGA. It is a programmable wireless protocol processing hardware platform. The VFP[1][2] is a new paradigm for programmable communication processing.

#### **1.3: Virtual Flow Paradigm**

The approach here is to strike a balance between software and hardware. An entire hardware implementation does not promise scalability and dynamic future evolution.

Since such a system does not have enough or any flexibility it fails to process various communication protocols different from the ones that the hardware is designed for.

The previous section talked about software defined radios that provide high flexibility and significant interoperability among protocols. But the software latency makes such systems impractical for high speed designs.

The idea here is to strike a balance between hardware and software implementation. The virtual flow paradigm solves the problem [1]. This paradigm introduces the Virtual Flow pipelining (VFP) combines the high speed computation capabilities of FPGA hardware and flexibility of software. The data flow and parameter inputs to processing blocks are fed by the user in the form of function calls, but the processing happens on hardware.

This type of flow gives us the freedom to add or remove any functional blocks (FU) or data processors (DP) dynamically. The blocks are not physically cascaded together which means they function independent of their preceding or succeeding processors. Hence there is a requirement of a top controller in these blocks that sets up the flow for every session. As shown in the figure below, the hardware pipeline is a pre-decided hard-coded flow that cannot be easily modified. This makes it infeasible for cognitive purposes. The virtual flow pipeline provides room for other blocks to fit in a flow. For eg, the first frame uses the modules FU1, DP1 and FU4 sequentially. The flow for the next frame shown is completely changed and independent of the first one.

Figure 1.4: Hardware and Virtual Pipelining [9]

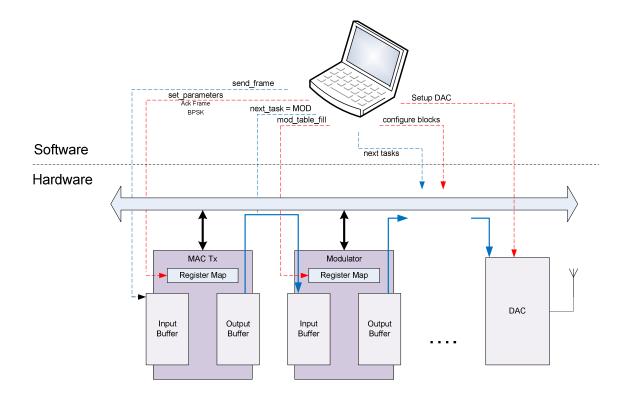

This is possible when the software is used to setup the flow –global task flows and next tasks and makes the system look like software defined radio looking from the application layer. The underlying functional blocks are all coded in hardware and take the form of a typical system on chip design as shown below.

Figure 1.5: Software in WiNC2R

The figure above shows such a scenario where the MAC Tx and Modulator are the functional blocks. Ever Functional Unit (FU) has control units in them that interpret the software calls. The next-task processors forward the processed data from the producer to the consumer based on a task table that is setup by the user via software.

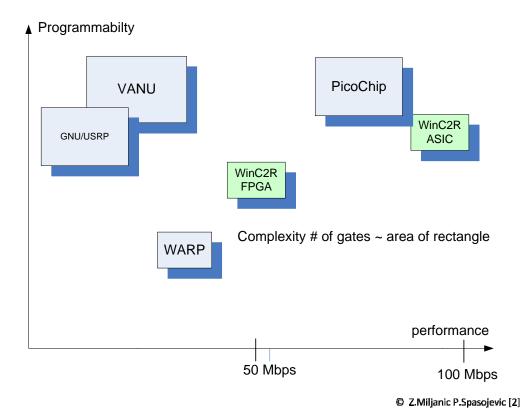

The WINLAB Cognitive Radio Platform WiNC2R is proposed and designed with the objective of achieving at speed processing of emerging WLAN and wireless broadband protocols with flexible architecture. Its underlying flexibility allows evolution within its domain space through software upgrades, and measurements and collaboration in the field with waveform and protocol adjustments for the optimum spectrum utilization. With

the help of the VFP, it places itself between high speed designs and highly programmable platforms as shown in the Figure 1.6.

WiNC2R on FPGA is well balanced in terms of programmability and speed. The figure also shows that the ASIC implementation will further improve the platform and promise greater speeds. The area of the rectangle corresponds to the complexity of design or the number of gates.

Figure 1.6: Hardware Platform Comparison[3]

Since FPGA is resource limited, we cannot achieve speeds greater than 50Mbps. We will require multiple FPGAs interfaced on PCI Express cards to achieve larger speeds. This project targets ASIC production to reach the 100Mbps destination. The WiNC2R on FPGA is merely a proof-of-concept implementation and the design procedure is followed to demonstrate the working of the Virtual Flow Paradigm. The modules are not optimized with respect to resources for commercial use.

#### **1.3 Contribution**

The thesis explores the top level design of the WiNC2R. It describes the Virtual Flow Paradigm implementation on FPGA and the modules used to achieve virtual flows. The focus of this thesis is the design and analysis of physical layer blocks on the WiNC2R. The modulator and demodulator have been designed to cater to the virtual flow paradigm. These blocks implement adaptive modulation. The user can setup the constellation points prior to the transmission. Further, during runtime, each chunk of frame, WiFi or WiMAX, can be modulated by any 4 types of modulations. It can be further noted that the processing engines work independent of each other. Hence, MIMO transmissions are possible.

The blocks have also undergone vigorous testing with the help of a simulated MATLAB model and the Bus Functional Module (BFM) environment. After successful transmissions of frames of various sizes and modulation schemes, the WiNC2R was programmed on to the FPGA.

Timing analysis and resource analysis has been performed to determine the processing latency. Even with high programmability, high speeds are achievable because the flexibility is implemented in hardware. The timing analysis establishes how much latency is contributed by the processing engines to the entire flow. The analysis also provides FPGA area utilization which will be useful for future WiNC2R releases.

The following section will explain the top level architecture.

## Chapter 2:

## WiNC2R – Top level Architecture

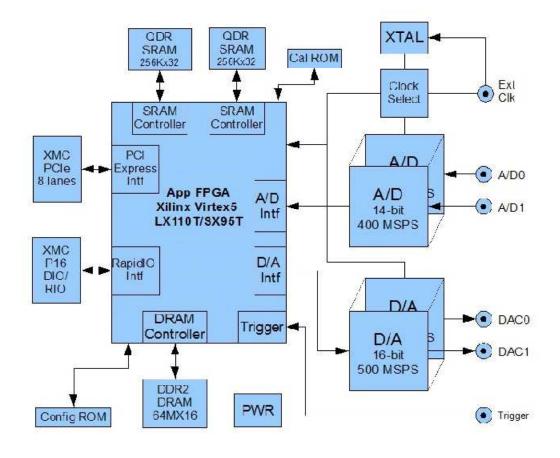

## 2.1: Innovative Integration's X5-400M board

WiNC2R is implemented on Innovation Integration's X5-400M board. This section talks about the top architecture design and the interface blocks instantiated in it. The X5-400M is PCI Express Mezzanine Card (XMC) IO module having the following features [7]

- Two 14-bit, 400 MSPS A/D and two 16-bit, 500 MSPS DAC channels

- Virtex5 FPGA SX95T

- PCI Express host interface with 8 lanes

- 1 GB DDR2 DRAM

- 4MB QDR-II

The figure below gives us the top level diagram. The board has various IO interfaces that are mentioned above and all the interfaces are designed and implemented on VHDL. WiNC2R uses some of these blocks based on the requirement. The blocks were provided by Innovative Integration board.

©Innovative Integration [8]

Figure 2.1: X5-400M Top Level Architecture[8]

#### 2.1.1) PCIe interface – PCI express 8 lanes

The PCIE interface block (ii\_pcie\_intf) provides a streaming, control and status interface to the host PCI Express interface for the user logic. It provides 8 lane motherboard-level interconnectivity and its scalable shared parallel bus architecture caters to high speed data and control transfers. It is also used to reprogram the FLASH memory on FPGA. FLASH memory is a reprogrammable memory that uses only a single power supply, making it ideally suited for in-system programming. The flash memory is used to store the application software. This block also monitors the FPGA temperature. If the temperature exceeds 85°C, this block triggers alerts and warnings. Modules use these indicators to spawn cooling and shut-down tasks.

#### 2.1.2) RapidIO Interface

The Xilinx RapidIO is a 3 layer endpoint solution which allows the users to integrate necessary portions of the design. It comes with its own protocols and frame structures. The interface block (ii\_dio) provides a simple modifiable interface with registers between the user logic and RapidIO for memory read and write.

This module is not instantiated in WiNC2R because RapidIO is not used.

#### 2.1.3) DRAM Controller

The ii\_128mq component has a high performance DDR2 DRAM interface and that requires constrained routing to the microblaze processor on the FPGA. It is connected to the Multi-Port Memory Controller (MPMC) in microblaze that supports SDRAM (single data RAM), DDR/DDR2 (Dual Data Rate) memory. Typically, it has an address and Data Paths, Arbiters for access control, a configurable physical interface IDELAY controller, Clock and Reset Logic.

This interface is used to load the application software. It as used as a replacement to Flash memory due to its huge capacity to load application software. Details of this block will be mentioned in the Software section of this document.

#### 2.1.4) QDR SRAM Controller

This component (ii\_qdr\_sram) provides an interface from the user logic to quad data rate(QDR) synchronous burst SRAM memories. The interface component supports the dual data path architecture of QDR SRAM by providing dual 18-bit address buses for read and write addressing, dual 32-bit data paths for read and write from the SRAM device. SRAMs are not used by WiNC2R, hence this module is also not used. The top level IO pins are terminated as per the user-guide.

#### 2.1.5) DAC

The DAC5687 is used in the WiNC2R. It has a 16-bit high speed DAC with interpolation filters with 2x,4x and 8x capability. It also has on board Numerically Controlled Oscillator (NCO) and onboard clock multiplier.

The X5-400M board consists of various blocks that process the data and make it compatible to the DAC. The blocks are instantiated in a block called ii\_dac\_intf. The dac interface block is instantiated between the user logic output and the DAC chip on the board. It works with 16 bit data on the system clock.

- The input to this block comes from the user logic design WiNC2R physical layer. The data is 16 bits and two modules are instantiated for I and Q values. The enable is always set high and DAC is always switched ON since frame detection happens at the receiver. This end works on system clock.

- The data is then forwarded to an offset and gain block (ii\_offgain). This block compensated for gain and offset errors. These values can be set by the user

through the software. There are specific memory locations for these values on which the user can write and read.

- After the error corrections are made, the data flows into a 1K, 16in-16out FIFO. The FIFO is written on system clock but it outputs on the sample clock (dac\_plllock) which can be set using the interpolation coefficient. This FIFO has alarms and flags if the buffer overflows or underflows.

- This interface is also equipped with test generators. By enabling the test generator, the module outputs a sample sine or ramp wave based on the amplitude and frequency offset set by the user.

#### 2.1.6) ADC

The ADC used in WiNC2R is the Texas Instrument's ADS5474. It is a 14-bit, 400-MSPS analog-to-digital converter (ADC) that operates from both a 5-V supply and 3.3-V supply while providing LVDS-compatible digital outputs That operates up to 500 MSPS.

Just like the DAC, Innovative Integration provides a set of blocks for the ADC interface. The entity ii\_adc\_intf is an important block in the receiver top and the details are given below.

• The X5-500M provides co-axial connectors for two channels – AD0 and AD1. The data from RF or cable is sampled at 200MHz clock rate. The clock is connected to adc\_data\_ready in ADC control block. The data adc0\_d and adc1\_d is triggered 1ns before the sample clock so that the peak is obtained at positive edge of clock.

- The adc0 and adc1 data flow into the adc control block and get combined into 32 bit words. The I and Q values are clubbed together and made compatible to the WiNC2R protocol followed.

- The 32 bit words are written to a 1K 32in-32out FIFO where the write enables follow the sample clock. The reading happens at the system clock. The decimation coefficient is set up by the user. The adc\_intf reads the decimation value from a designated address location to which the user has access to. It is default set to 4.

- The output from the adf\_intf is sent to the processing engine of the receiver.

- The gain and the offset can also be set by software. User can change these values dynamically by writing into the addresses assigned.

#### 2.1.7) Application FPGA

Since all the signal processing is left to the FPGA, we use a large area FPGA. Virtex5 FPGA - SX95T is best suited for this application. It has a large number of DSP blocks and RAMs to fit in the entire transmitter or receiver.

| Feature                         | SX95T |

|---------------------------------|-------|

| Rocket IO Trans-Receiver Blocks | 16    |

| СМТ                             | 6     |

| Ethernet MACs                   | 4     |

The details of FPGA are:

| Endpoints Blocks for PCIe | 1        |

|---------------------------|----------|

| CLB                       |          |

| Array (RowXCol)           | 160 x 46 |

| Slices                    | 14,720   |

| Max Distr RAM (Kb)        | 1,520    |

| DSP48E                    | 640      |

| BRAM                      |          |

| 18Kb Blocks               | 488      |

| 36Kb Blocks               | 244      |

| Max Block RAMs            | 8,874    |

| Total I/O Banks           | 19       |

| Max user I/O Pins         | 640      |

Table 2.1: Details of Virtex5 FPGA

## 2.2: Steps for implementing on FPGA

- a. Architecture Design and documentation.

- b. The RTL design is in VHDL

- c. Simulation in Mentor Graphics Modelsim and Functional Verification using Matlab and Bus Functional Model (BFM).

- d. Synthesis A process that converts high-level abstraction to low-level. The VHDL code is converted to gate level implementation for FPGA. The tool used is Mentor Graphics - Precision RTL Synthesis.

- e. Xflow Xilinx tool to achieve a design flow.

- f. Place and Route This step places the logic elements generated after synthesis on FPGA and interconnects them on FPGA. It is a long process where the Xilinx tool optimizes the space and routing to meet the timing constraints.

- g. The step generates a bitfile which is loaded into the FPGA using Xilinx Impact.

- h. Xilinx also provides a software development kit with Xilinx libraries to generate the software image that is loaded in the BRAM. We can access all memory locations through the software.

# **Chapter 3:**

# WiNC2R Top Level Architecture

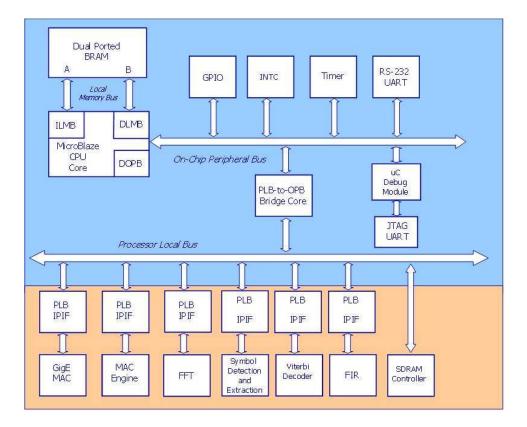

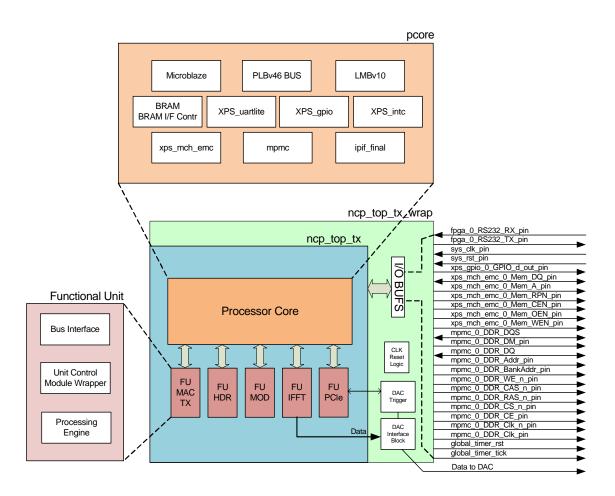

This section will explain the WiNC2R top architecture that is implemented on FPGA. The systems top level architecture is called ncp\_top and it instantiates the main architecture ncp\_cmn and the IO buffers [9].

©WiNC2R

Figure 3.1: NCP top level architecture

Syntheses provides an option of automated Input-Output buffers (IOBUFs) instantiation where the tool recognizes the IO ports and places the corresponding buffer before it. Also, when the microblaze processor is built, the tool internally places an IOBUFs for the DRAM interfaces. The place and route tool then flags an error due to the contention of multiple buffer instantiation. Hence, we manually insert the buffers where needed in the top file to isolate the central architecture and the buffers.

The WiNC2R architecture sits in the entity ncp\_top\_cmn. There are three main parts in this architecture [9]

- Microblaze Central Processor

- Functional Units Signal Processing Units

- X5-400M Interface Units ADC/DAC interfaces

# 3.1: Central Processors - Microblaze

The MicroBlaze embedded processor soft core is a reduced instruction set computer (RISC) optimized for implementation in Xilinx Field Programmable Gate Arrays (FPGAs). It is implemented with a Harvard memory architecture; instruction and data accesses are done in separate address spaces. Each address space has a 32-bit range (for example, handles up to 4-Gb of instructions and data memory respectively). The instruction and data memory ranges can be made to overlap by mapping them both to the same physical memory. This is useful for software debugging. Figure 3.1 shows the functional block diagram of the Microblaze core[6].

Microblaze has the following features:

• Thirty-two 32-bit general purpose registers,

- Up to eighteen 32-bit special purpose registers, depending on the configured options,

- 32-bit instruction word with three operands and two addressing modes,

- 32-bit address bus,

- Single issue pipeline,

- Three interfaces for memory accesses Local Memory Bus (LMB),Processor Local Bus (PLB) or On-Chip Peripheral Bus (OPB),Xilinx Cache Link (XCL)

- Supports reset, interrupt, user exception, break, and hardware exceptions,

- Supports optional direct mapped Instruction and Data cache for improved performance,

- Floating Point Units based on IEEE 754 single precision floating point format,

- Fast Simplex Link (FSL) that provides a low latency dedicated interface to the processor pipeline, extending the processors execution unit with custom hardware accelerators,

- Debug interface connected to the Xilinx Microprocessor Debug Module (MDM) core, which interfaces with the JTAG port of Xilinx FPGAs

# 3.2: Processor Logic Bus v46 BUS

The PLB is a synchronous, high performance bus used to inter connect high performance processor, ASIC and memory cores. It provides the infrastructure for connecting an optional number of PLB masters and slaves into an overall PLB system. It consists of a bus control unit, a watchdog timer, and separate address, write, and read data path units. The main features of the PLB bus are [6]:

- PLB arbitration support for up to 16 masters with number of PLB masters configurable via design parameters.

- PLB address and data steering support for up to 16 masters128-bit, 64-bit, and 32bit support for masters and slaves

- PLB address pipelining

- Four levels of dynamic master request priority

- PLB Reset generated synchronously to the PLB clock from external reset when external reset provided

- DMA support for buffered, peripheral-to-memory, memory-to-peripheral, and memory to memory transfers

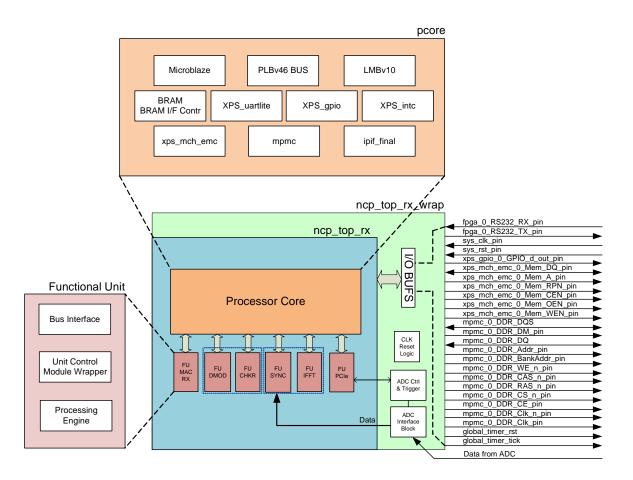

# 3.3: Transmitter Architecture

The working force of the system is the team of Functional Units (FU). The transmitter blocks are the MAC Tx, Header, Modulator and IFFT. The output of the FFT is connected to the DAC interface block. For the transmitter case, only these FUs and the DAC interfaces are instantiated.

Figure 3.2: Transmiter Architecture

The Figure 3.2 depicts an 802.11a-lite transmitter implementing the virtual flow pipelining to send an OFDM frame. Due to area restrictions, we couldn't instantiate all processing blocks of 802.11a. The processor and bus reside in the processor core bus. There are 4 functional units that are plugged to the bus. They include :

- MAC: The software feeds the MAC with the frame and this block attaches the required headers as per the standard. This is called 802.11a-lite MAC.

- Header: This block appends the PLCP header before the frame and also pads zeros at the end of the frame to make the frame size an integral multiple of number of OFDM symbols

- Modulator: The frame is then modulated according to the modulation shceme decided by the software.

- IFFT: The output of the modulator goes through IFFT and filters.

The content at the output of the FFT are OFDM format and are passed on to the DAC. The DAC interface block is also connected to the bus, hence the configuration parameters can also be setup by the user.

## **3.2 Receiver Architecture**

The receiver structure is similar to the transmitter. Only change is that the Functional units cater to receiver now. The ADC interface connects to the Synchronizer FU. The DAC interfaces don't get connected and the pins are terminated. The receiver implementation diagram is shown the figure 3.3.

Figure 3.3: Receiver Architecture

The receiver instantiates the following functional units :

- Synchronizer: This block is responsible for frame detection and frequency correction of the received frame.

- FFT: The received frame passes through FFT.

- Demodulator: This block demodulates the frame based on the modulation scheme and decision table setup by the user.

- Checker: This block contains the parity checker for the PLCP frame and CRC checker for the data frame.

- MAC: The checker passes the data to MAC which removes the header and forwards the frame to the software for verification

The data at the synchronizer is received from the ADC. Just like the DAC, the ADC parameters can also be configured by the user at runtime.

# 3.3: System Flow

The data and control flow demonstrated in the WiNC2R demo is that of 802.11a-Lite ODFM. As mentioned before, the functional units correspond to the basic physical and MAC layer blocks required for basic frame transmission. The task by task flow, which is setup by the user, is elaborated in detail below.

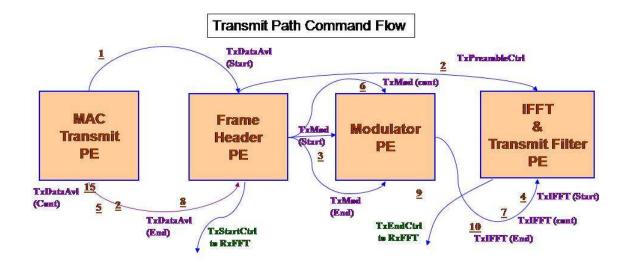

#### 3.3.1: Transmitter Flow for OFDM

The transmitted functional units and the command flow of an OFDM transmitter is shown in the figure below [10].

©Renu Rajnarayan

Figure 3.4: Transmit Control Flow

Transmitter Tasks

- TxDataAvl The frame, which is written in software, is written into the input buffer of MacTx block. MAC then spawns this task to the frame header creator and forwards the frame.

- 2. TxStartCtrl This task is sent to the receiver FFT to indicate that the control message is being transmitted. In this case, the preamble is sent.

- TxPreambleCtrl The preamble is sent directly to the IFFT for transmission during this task.

- 4. TxEndCtrl This task is sent to the receiver to indicate end of preamble transmission.

- 5. TxMod The modulator identifies this task and proceeds with modulating the input buffer. There are three different tasks for the first chunk, last chunk and the intermediate chunk. But the modulation works independent of these sub-tasks.

- TxIFFT The mod forwards the data to the input buffer of the IFFT during this task. This is the final task of one frame cycle. The FFT forwards the content directly to The DAC.

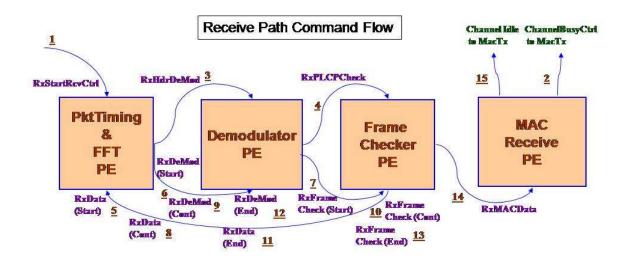

## 3.3.2: Receiver Flow for OFDM

The receiver functional units and their command flows are shown in the diagram below [10].

©Renu Rajnarayan

Figure 3.5: Receiver Command Flow

1. ChannelIdle – When the receiver is idle, it sends channel idle to Mac in the transmitter. On sensing this, the Mac sends frame across channel.

- RxStartRevCtrl On receiving this task from the transmitter, the auto-correlator in the synchronizer scans the channel for valid preambles and extracts the parameters out of it.

- ChannelBusyCtrl Once these parameters cater to a valid OFDM frame, the receiver locks the channel by sending the busy signal. This is a part of the medium access control to avoid frame collisions.

- RxHdrDmod After the preamble is parsed, the PLCP header (802.11a header) is demodulated.

- RxPLCPChk The frame checker checks the parity of the header and extracts the frame parameters from it.

- 6. RxData Once the header test passes, frame date is requested by the frame checker. There are three sub-tasks for all the data tasks: first, last and intermediate chunk.

- RxDeMod This task indicates the frame is ready in the demodulator input buffer to be demodulated.

- 8. RxFrameChk The frame checker checks the CRC of the incoming frame chunkwise and forwards data to the MAC.

- RxMacData The frame is checked for validity by the MAC and it interrupts the software accordingly.

- ChannelIdle After the frame is processed by MAC, its sends channel idle on the channel for future frames.

This concludes the conceptual part of the thesis. The coming chapters will illustrate how this design concept was implemented on FPGA. The document starts with the basic top level Functional Unit Design and digs into details of every block. The physical layer blocks – Modulator and Demodulator are discussed in detail along with the testing methodologies.

# **Chapter 4:**

# **Functional Unit Architecture**

The functional unit is the working force of the WiNC2R. They can be viewed as functions in software developed on hardware. They are connected to the slave interface of the bus only. They are completely independent of each other hence they can be connected or disconnected on the fly. All FUs share a common entity structure and architecture. They differ on the processing engine instantiated in them.

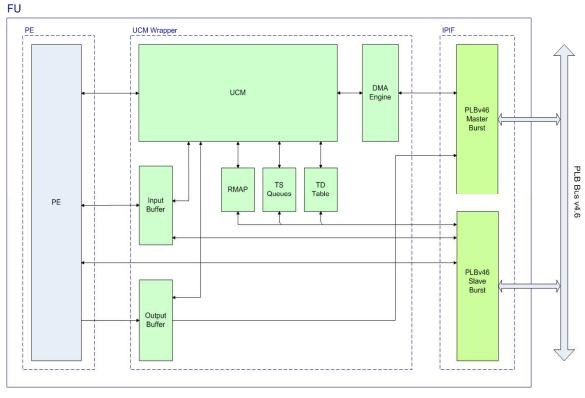

The FU has three modules [11]

- Bus Interfaces Intellectual Property Interface (IPIF)

- Unit Control Module Wrapper (UCM Wrapper)

- Processing Engine (PE)

The top level architecture diagram is shown below.

©WiNC2R

Figure 4.1: Functional Unit Architecture

# 4.1: Bus Interface

The FU ports must be consistent with the Bus signals. The Intellectual Property Interface (IPIF) features are

- It provides bidirectional interface between the user logic UCM & PE and the PLBv46 bus standard [6].

- It provides access to 32,64 and 128 width bus

- Both master and slave interfaces are merged into one block

- This block is generated using Xilinx Core Generator. The generated code was modified to isolate the user logic from the bus.

# 4.2: Unit Control Module Wrap

The UCM wrapper mainly consists of the UCM and blocks required for its access to the bus. It consists of the management layer of the WiNC2R- above MAC and PHY.

## 4.2.1: UCM

It is in charge of scheduling the tasks to the unit that it is associated with, assigning the task, monitoring the task completion, and communicating with the other units in the system for task sequencing. The task scheduling and sequencing in essence forms Virtual Flow Pipelining - the sequence of tasks performing the functions of the network protocol under the strict time frame constraints or with the best effort approach. The Virtual Channel is the sequence of tasks linked together. The linkage specifies the time frame

duration which will constrain the duration of the sequence of tasks within the frame boundary, as well as repetition period of the tasks in every frame.

#### 4.2.2: Buffers

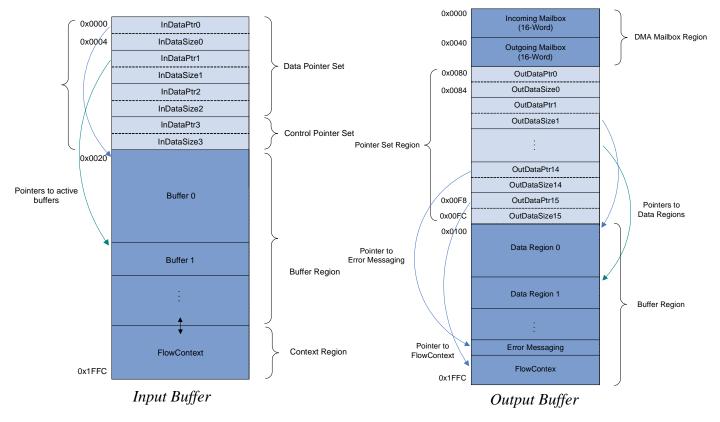

©WiNC2R

Figure 4.2: Buffer Partition

The processing engines the input and output buffers that the processing engines use for data processing. They are 1K 33bit Dual port RAMs generated by Xilinx Core Generator. The buffers are partitioned into two parts – pointer region and data region.

There are common interface blocks in the processing engine that are aware of these partitions and write/read into them accordingly. They are the ones that manage the data in all the regions[11].

- Region 0 in both the buffers contains data.

- Region 1 contains the parameter word. The parameter word contains all the details of the data that is stored in region 0.

- Region 3 in input buffer and Region 15 in the output buffer are reserved for context data. Context contains that data that are not a part of the frame that is being transmitted. If two or more processing engine need to share data that is not a part of the frame but required for the processing of the frame, they use these regions.

#### 4.2.3: Task Descriptor (TD) Table

The TD interface contains the Task Descriptor table (TD). This block specifies the task flow execution within the PE. In this table, the active task and next tasks are specified for every FU. The UCM fetches the information related to a task belonging to a particular PE from the TD table of that PE. The user has access to this RAM and can fill in the task information. The TD table contains the information about the number of input/output buffers used by the task, the next tasks triggered after the successful execution of that task and the information about whether a task is a chunking/dechunking task or not. This table can be updated for every task through the software.

#### 4.2.4: GTT Table

The Global Task Table (GTT) is a centralized table that resides in the BRAM connected to the secondary PLB bus. The processor creates and initializes the GTT at the start. The PEs decodes the data written into this table for task execution and insert the asynchronous target (consumer) tasks to the FU's queues. This table gives a global view of the data flow and it can be set for every frame. The TD table of every PE refers to this table to determine what its next task is. It also synchronizes task execution with the completion of all producer tasks.

The UCM in every FU accesses the GTT. It is array indexed by 15 bit TaskID in the Task Descriptor Table (TD) which is preset. The values in the GTT are modified by the UCM during the task execution. The GTT contains the information about the different tasks and which FU the tasks are associated to. It also helps in the task synchronization through the enable flag processing. It also contains configuration settings for the tasks.

#### 4.2.5: Task Scheduler Queue

When Producer UCM wants to schedule a task, it writes a descriptor which is present in this block to either Synchronous or Asynchronous Descriptor FIFO. This indicates to Task Scheduler Queue (TSQ) Controller that a task is ready for the en-queuing process. This block manages tasks by placing them in queues and pushing them whenever needed.

#### 4.2.6: Register Maps

Every FU also has a register map that interfaces to the user. The user can set various parameters directly which the UCM can access. They include information like task priorities, interrupt handling, error handling and task scheduling.

### 4.2.7: Arbiters

Since every block in this wrap has slave access to the bus, arbiters are placed in every block that grant access whenever the bus is idle. The arbiters work on the Bus2IP\_CS or chip select signal to select the corresponding block.

#### 4.2.8: DMA Engine

The DMA Engine provides the interface to the PLBv46 Master bus. UCM requests for PLB bus services from the DMA Engine, and provides the byte length, source and destination addresses information. Once configured, the DMA Engine performs the PLB bus DMA transactions autonomously. The various transfers handled by the DMA are -

- 1. Producer Output Buffer -> Consumer Input Buffer (Write transaction)

- 2. Producer UCM -> Consumer UCM (Write transaction)

- 3. Producer UCM <- Consumer UCM (Read transaction)

- 4. Producer UCM -> GTT (Write transaction)

- 5. Producer UCM <- GTT (Read transaction)

# 4.2.9: Processing Engine

The processing engines are the data processing blocks in the WiNC2R. The main MAC and PHY layer functioning for OFDM are performed at this level. The interfaces of these blocks are pre defined and are compatible to the UCM ports and the bus interface. Details of these blocks are presented in the further chapters.

# Chapter 5:

# **Processing Engine (PE)**

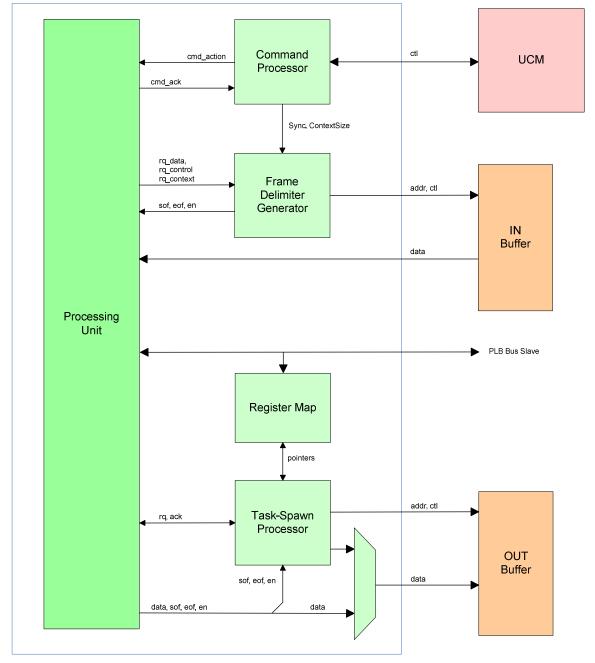

Processing Engine

©WiNC2R

#### Figure 5.1: Processing Engine Top Level Diagram

The figure shows the arrangement of the top level processing engine[10]. The Command Processor (CP), Frame Delimiter and Generator (FDG), Task Spawning Processor (TSP) and Register Maps (RMAP) are the blocks that isolate the processing unit from the upper level control blocks, they are referred to as 'PE Common Blocks'. The main objective of using the common blocks is to standardize PE input/output ports and make them independent from the UCM and I/O buffers. The function of the common blocks is given below-

- Command Processor (CP): It translates the commands coming from the Unit Control Module (UCM) to single-pulse action signals. Each PE can setup the number of action signals and context data required.

- 2. Frame Delimiter and Generator (FDG): The FDG is the interface between processing unit and the input buffer. The PE requests data for a particular data region and FDG extracts the data from the input buffer.

- Task Spawning Processor (TSP): TSP helps the PE write to the output buffer.

Whenever PE wants to write its output to the buffer, it requests TSP with data region.

After TSP acknowledges, it waits for SOF and Enables from PE.

- 4. Register Maps (RMAP): Every PE maintains a register map that adds as a slave interface to the PLBv46. The user can access PE only through the register map. User can write to the control register from software. PE can write status details like error messages, state etc. to the status register so user can read during board testing. Details of RMAP can be found in RMAP section of Chapter 6.

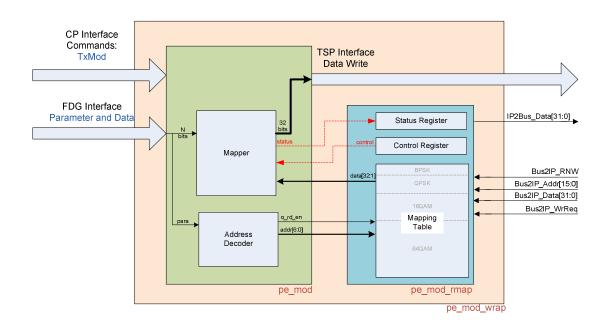

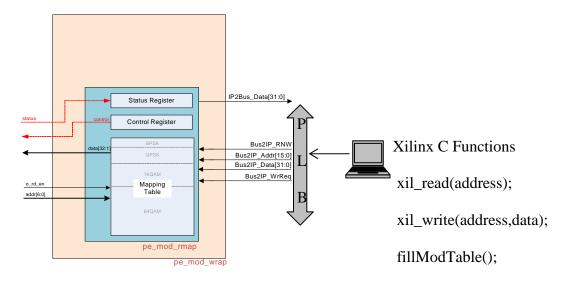

# 5.1: PE Modulator

The Modulator Processing Engine (pe\_mod) is an adaptive modulator that uses a userdefined mapping table. Since WiNC2R caters to OFDM frames, the modulator is designed for the 802.11 and 802.16 constellations provided by the standards. But this module is not restricted for the standards. A user-defined constellation space can also be defined and loaded into the modulator through the register map (pe\_mod\_rmap).

The block diagram and schematic details of the modulator is shown below.

Figure 5.2: PE Modulator

# 5.1.1: Input Interface

#### **CP Interface Commands**

The modulator has only one action signal – TxMod that initiates the mapping of the data chunk. The assertion of this signal indicates that there is a data chunk in the input buffer and the modulation procedures can begin.

### **FDG Interface**

The PE fetches the parameter word that lies in the region 1 of the input buffer. The 32-bit word contains the properties of the frame to be received. These parameters cannot be altered and any change would result in modifications of the VHDL code.

The details of the parameter word are explained in the next section.

#### 5.1.2: Processing Engine

The crux of the modulator is the RAM which contains the mapping table and an address decoder associated with it. The mapper block extracts the information from the input buffer and activates the address decoder based on the type of modulation.

Parameter Parsing :

The parameter word bit-mapping is shown below.

| Bits      | Content           |

|-----------|-------------------|

| b31       | Preamble Present  |

| b30       | Not End of Burst  |

| b29 - b28 | Midamble Interval |

| b27 - b23 | Sub-channelization  |

|-----------|---------------------|

| b22       | Short/Long Preamble |

| b21- b20  | Channel ID          |

| b19       | No Coder            |

| b18       | Uplink/Downlink     |

| b17-b16   | Standard ID         |

| b15-b11   | Header Bytes        |

| b10-b9    | Header Code Rate    |

| b8-b7     | Header Frame Modln  |

| b6        | Header Present      |

| b5-b4     | Code Rate           |

| b3-b2     | Frame Modln         |

| b1-b0     | Frame Status Bits   |

Table 5.1: PE Modulator Command Parameter

The properties that are used by the modulator are

1. Frame Tag Bits (b1 b0) : ftag

Indicates which part of the frame the chunk belongs

- 00 Start and End of frame 10 Middle of frame

- 01 -Start of frame 11 -End of frame

- 2. Frame Modulation (b3 b2) : fmod

Indicates the type of modulation for frame

| 00 - BPSK | 10 – 16QAM |

|-----------|------------|

| 01 – QPSK | 11 - 64QAM |

3. Code Rate (b5 b4) : frate

Indicates the rate of the frame (If coder present)

| $00 - \frac{1}{2}$ code | 10 - 2/3 code |

|-------------------------|---------------|

| 01 – ¾ code             | 11 – 5/6 code |

- 4. Header Present (b6) : Indicates whether PLCP is present in the chunk

- Header Modulation (b7 b8) : hmod

Indicates the modulation technique for the header

- Header Code Rate (b10 b9) : hrate

Indicates the rate of header

- 7. Header Bytes (b15 b11) : hsize

Contains the number of bytes present in the header

- 8. Standard ID (b17 b16) :

- $00 WiFi \quad 01 WiMax$

The control word contains the parameters for the data present in the data region of the input buffer. The modulator becomes aware of the frame type – WiFi or WiMAX and the type of modulation based on this word.

The 802.11 standard's PLCP header typically is BPSK modulated and <sup>1</sup>/<sub>2</sub> coded. If the coder is not present <sup>1</sup>/<sub>2</sub> repetitive code is implemented.

#### **Data Parsing:**

Once the modulator is set based on the parameters, we request for the region 0 which contains of the frame with or without header. If the header is present, the first 'hsize' number of bytes are modulated using the hmod scheme and rest of the chunk is modulated with the fmod scheme.

After the SOF is received, the mapper extracts 'n' number of bits from the 32 bit word received and the address decoder extracts a 32 bit corresponding word from the mapping table. This word is the constellation point associated with the bits. The bit-to-word mapping is given in the mapping table partition figure below.

| Addr<br>Offset | WiFi               | Addr<br>Offset      | WiMAX              |

|----------------|--------------------|---------------------|--------------------|

| 00             | 2 points<br>BPSK   | 86 2 points<br>BPSK |                    |

| 02             | 4 points<br>QPSK   | 88                  | 4 points<br>QPSK   |

| 06             | 16 points<br>16QAM | 92                  | 16 points<br>16QAM |

| 22                       | 64 points<br>64QAM |  | 64 points<br>64QAM |  |

|--------------------------|--------------------|--|--------------------|--|

| Table 5 2. Manning Table |                    |  |                    |  |

| Table 5.2 | : Mappin | g Table |

|-----------|----------|---------|

|-----------|----------|---------|

As shown in the figure, the RAM is divided into the four partitions each for the modulation scheme. The address of the RAM can be calculated using the equation below.

```

RAM address = modulation offset + bits

```

For eg. The modulation offset of 16QAM is  $16_{hex}$ . If the input data is  $D_{hex}$ , the associated constellation point can be found at the address  $D_{hex} + 16_{hex}$  which is  $23_{hex}$ .

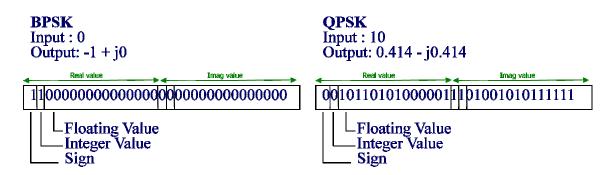

The modulation word represents a complex number. Bit 31 to 16 is associated with the real part and bit 15 to 0 contains the imaginary part and the 16 bit is the floating point number. The modulator continuously writes into the output buffer. This is done with the help of TSP. The complex number representation is shown in the diagram below

Figure 5.3: Complex Number Representation

#### 5.1.3: Output Interface

Data Write - The modulator requests region 0 for the data and provides SOF EOF and enables for corresponding 32 bit words. Since all words written are 32bit, enable signal is always 0xF. The size of the chunk written depends on the modulation scheme.

After writing the data in region 0, the modulator requests region 1 to write the parameter. The parameter word is same as the word received from the input buffer. The modulator simply forwards this information to the MAC Tx.

# 5.2: PE – Demodulator and Checker

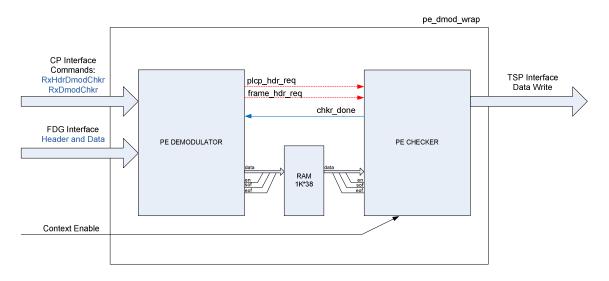

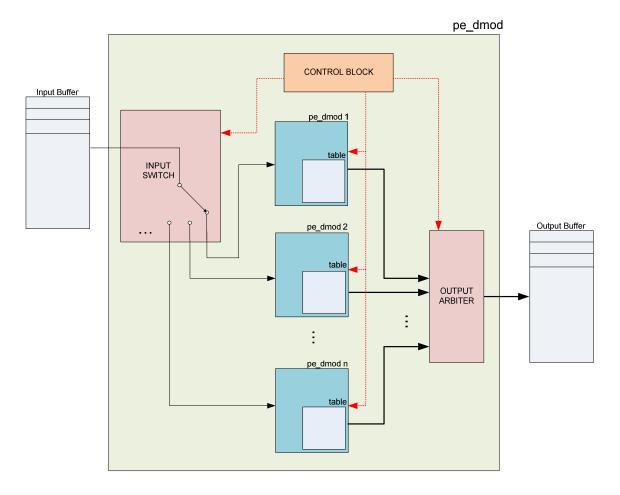

The Demodulator Processing Engine (pe\_dmod) is a processing engine that demodulates the data coming from the FFT. Due to FPGA recourse constrains, the demodulator and frame checker are combined into one processing engine. The software that establishes the modulating constellation also sets up the decision regions for the demodulation. The figure shows the top level architecture of the processing engine wrapper.

Figure 5.4: PE Demodulator and Checker

The IO ports of the top level are consistent with all the processing engine pins. The data read interface is present in the demodulator and the write interface is in the checker. There are other connections that pass control information between the two PEs.

## 5.2.1: PE Demodulator

The demodulator is a standard specific physical layer block that demodulates the input data that arrives from the FFT. Just like all PEs, the module works on 32 bit words.

# **CP Interface**

The demodulator has two tasks as mentioned in Chapter 2. The RxHdrDmod is the task that demodulates the header field. The PLCP header is demodulated in a different scheme than the frame. The FFT treats the header as a different task and triggers this task. The second task is RxDmod is the task that caters to the payload. This task is activated when there is data present in the input buffer of the demodulator.

## **FDG Interface**

The region 0 of the input buffer is reserved for data. Region 1 contains the parameter word that contains more information of the payload. Based on the requirement, the PE requests for corresponding region to the FDG.

## **Processing Engine**

The checker engine treats header and frame as two different tasks but the modulator processes these tasks in a similar way.

Once the autocorelator in the FFT triggers and validates the PLCP header and, it writes the header content to the inbuff. The demodulator first parses the parameter word which contains the following information.

| Bits    | Content             |

|---------|---------------------|

| b31-b28 | 0x0                 |

| b27-b23 | Subchannelization   |

| b22     | Short/Long Preamble |

| b21-b20 | Channel ID          |

| b19     | No Coder            |

| b18     | Uplink/Downlink     |

| b17-b16 | Standard ID       |

|---------|-------------------|

| b15-b6  | 0x0               |

| b5-b4   | Code Rate         |

| b3-b2   | Frame Modln       |

| b1-b0   | Frame Status Bits |

Table 5.3: PE DmodChkr Command Parameters

The properties that are used by the modulator are

| 1. | . Frame status Bits (b1 b0) : ftag                  |                   |  |  |  |

|----|-----------------------------------------------------|-------------------|--|--|--|

|    | Indicates which part of the frame the chunk belongs |                   |  |  |  |

|    | 00 - Start and End of frame $10 - $ Middle of fram  |                   |  |  |  |

|    | 01 – Start of frame                                 | 11 – End of frame |  |  |  |

2. Frame Modulation (b3 b2) : dmod

Indicates the type of modulation scheme used for the PLCP header

00 – BPSK 10 – 16QAM 01 – QPSK 11 – 64QAM

3. Code Rate (b5 b4) : frate

Indicates the rate of the frame (If coder present)

$00 - \frac{1}{2}$  code  $10 - \frac{2}{3}$  code

#### $01 - \frac{3}{4}$ code $11 - \frac{5}{6}$ code

- 4. Standard ID (b17 b16) :

- $00 WiFi \quad 01 WiMax$

The control word for a 14 byte QPSK modulated WiFi frame would be  $800800E5_{hex}$  and that modulated with 16QAM would be  $800800E9_{hex}$

#### **Data Parsing**

Once the frame modulation scheme is known, the processing engine demodulates the header and writes it to the RAM. The checker gets an action signal that indicates header task. In RxDmod task is similar to this, only difference is that this task triggers frame checker action at the checker to indicate payload.

#### RAM

Since there is no TSP interface, there is a 1K RAM that acts like the output buffer to the Demodulator and the input buffer to the checker. To synchronize the delimiters to the frame, the RAM width is extended to 38 bits. 32 bits are for the data, 1 for sof,1 for eof and 4 for the enable associated with the data. The diagram of the RAM is shown below.

Figure 5.5: Demodulator Output RAM

This RAM does not have data partitions like the input and output buffer. The RAM is overwritten on every task from address 0x000.

## Demodulation

Just like the modulator, the programmability of the demodulator lies in the RMAP. It is essentially a block RAM that has slave interfaces to the bus. Hence, it can be read and written by the software or the user. Just like the software calculates the constellation points and writes them to the modulator RMAP, the same function simultaneously calculates the decision regions and writes them to the dmod rmap. After knowing the type of modulation from the parameter word, the demodulator fetches the required values and stores them internally to decode. The structure of the RMAP is shown in the figure below

The 32 bit word is split into two regions – data bits and boundary. We use the lower bound method to decide boundary region. In this method, the software calculates the lower bound(value) for all the boundaries and stores it next to the decision it. So, the 16 LSB bits is the lowest value of the decision region and the MSB 16 bits correspond to the bits associated with that region.

There are separate words for both the axes. Hence, the demodulator works on the real and imaginary part separately. It concatenates the demodulated words and once 32bits are formed, it writes to the RAM with delimiters.

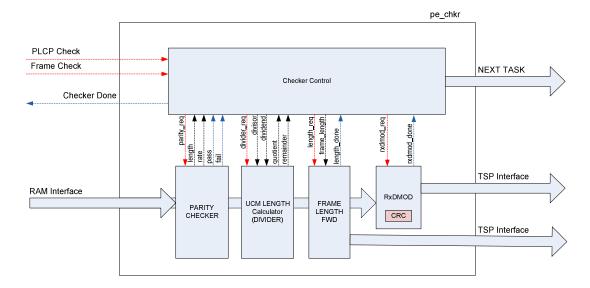

#### 5.2.2: PE Checker

The frame checker is a part of the demodulator block. It basically consists of a parity checker, header extractor, byte counter and CRC checker. The detail architecture is shown in the Figure 5.6.

Figure 5.6: PE Checker

## **Header Extractors**

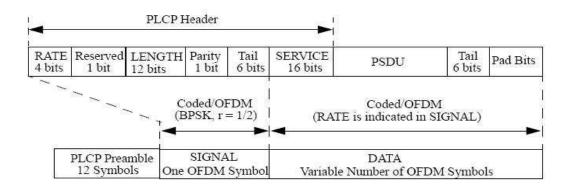

In the task RxHdrDmod, the demodulator sends a control signal to the checker that indicates whether the input data is header. The data from the header is extracted and stored in appropriate signals. The PLCP Header[15] structure specified in 802.11a standard is as follows

Figure 5.7: PLCP Header Contents[15]

## Parity checker

The only redundancy check that happens on the PLCP header is the parity check. 1 bit in the header is assigned to the parity bit. The parity check block checks the parity of the header. When there is an error, the PE checker flags an error and triggers the error handling tasks. In this case, the FFT doesn't forward the frame to the MAC and requests retransmission. If the parity check passes, this block triggers the UCM length calculator block.

The UCM length calculator calculates the number of chunks based on the total frame length received, the modulation scheme and chunk size. These details are given in the Table 5.4. Every chunk contains 4 OFDM symbols and the size of the chunk is determined by the data bits per OFDM symbol. The first chunk sizes are different because the contents of the header are not included in the frame size. Hence they get clipped off the first chunk.

| Data<br>Rate<br>(Mbps) | Modulation | Rate | OFDM | Per<br>OFDM | First<br>Chunk<br>Size<br>(Bytes) | Chunk<br>Size<br>(Bytes) |

|------------------------|------------|------|------|-------------|-----------------------------------|--------------------------|

| 6                      | BPSK       | 1⁄2  | 48   | 24          | 16                                | 24                       |

| 9                      | BPSK       | 3⁄4  | 48   | 36          | 16                                | 24                       |

| 12                     | QPSK       | 1⁄2  | 96   | 48          | 40                                | 48                       |

| 18                     | QPSK       | 3⁄4  | 96   | 72          | 40                                | 48                       |

| 24                     | 16-QAM     | 1⁄2  | 192  | 96          | 88                                | 96                       |

| 36 | 16-QAM | 3⁄4 | 192 | 144 | 88  | 96  |

|----|--------|-----|-----|-----|-----|-----|

| 48 | 64-QAM | 2/3 | 288 | 192 | 136 | 144 |

| 54 | 64-QAM | 3⁄4 | 288 | 216 | 136 | 144 |

#### Table 5.4: Chunk Sizes for WiFi

#### **Frame Length Forward Block**

The frame length block uses the length field in the header to calculate the number of OFDM symbols based on the following table. The Xilinx generated divider is used.

This block writes the number of symbols in the context field of the outbuffer. This value is read by the FFT. The UCM in the FFT is responsible for chunking, it uses this value to determine the number of chunks for the entire frame to fit the required number of OFDM symbols. The number of OFDM symbols per chunk is set by the user through the register maps

#### **CRC Check**

After the PLCP header handling, the top module sends a header check done to the FFT. After this, the FFT starts sending the frame to the demodulator which is then passed to the CRC check block in the checker.

The Frame Check Sequence (FCS) unit calculates CRC over all the data. It processes

each byte of the data per cycle and generates a 32-bit CRC. The CRC generator polynomial is specified in the standard –

$$G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$$

The CRC generated from a chunk is stored in the context field, which is region 15 of the output buffer. The initial seed of the CRC block is all 1s. Since the frame arrives in chunks, the seed for every chunk is the CRC generated by the previous one. This way, every chunk can be independent and the context field can be used to pass the intermediate CRC. The MAC Rx then checks the CRC content directly to validate the integrity of the frame.

All the processing engines have to be tested before implementing on the FPGA. The following section describes the testbench design used for automated PE verification.

### 5.3: PE Testbench

Every design has to be backed with extensive testing. In FPGA, the top level entity is called testbench. The testbench consists of two major components – The device under test is the user logic and the testbench components.

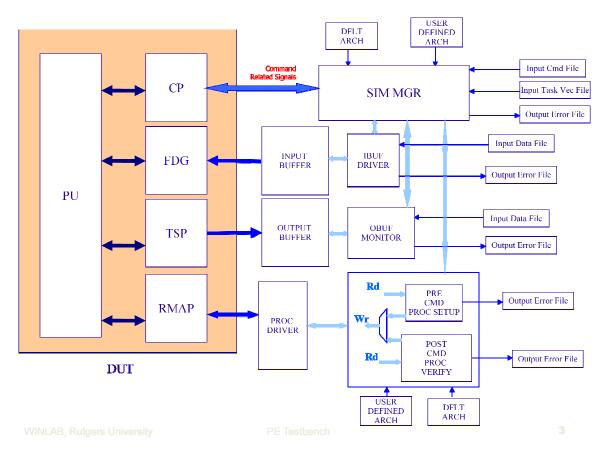

Figure 5.8: PE Test Bench Top Level Architecture

#### 5.3.1: Device under Test

The device here is pe\_top [10]. It consists of the basic processing unit (PU) with all the common blocks. The common blocks are independently tested, so the testbench is established to test the processing unit alone.

#### 5.3.2: Reference Text Files

The testbench components are RTL coded and are directly connected to the PE. They are designed to fake an UCM wrap environment. One side of these components is the testing side where the signals are compatible to the WiNC2R specific pe\_top signals and the other side is the reference model which is designed in Matlab.

The entire OFDM chain is redesigned in Matlab which acts as the reference for testing. The model generates input and output buffer data for all processing engines for various parameters. The parameters include number of frames, frame length, modulation etc. Following is the list of the text files that are generated for a 14 byte frame with modulation scheme of BPSK.

cmd – This file contains the list of commands for a single testbench session. The commands are compatible to the tasks mentioned in Chapter 2.

Ibuf – This text file is synchronous to the cmd file. It contains the content that is supposed to be in the input buffer for the corresponding command. The size of the data is also mentioned in this file

```

## Standard ID: 0 Frame Modln: 0 Header Present: 1##

# Data Region O

# Size

24

# Data

xO x3 xFO xCF

x0 x0 x0 x0

x0 x80 x0 xB8

x56 x78 x9A xBC

x92 x10 x12 x34

x0 x0 x55 x7

# Data Region O

# Size

4

# Data

x83040

```

3. Obuf – This file contains the correct output buffer contents corresponding to the ibuf f

```

## Standard ID: 0

Frame Modln: O

Header Present: 1##

# Data Region O

# Size

768

#Data

x4000 x0

x4000 x0

x4000 x0

x4000 x0

.

x4000 x0

xC000 x0

# Data Region 1

# Size

4

# Data

x83040

```

4. Tvec – This file is used to compare the next task vectors coming from the processing

engine to the reference matlab model.

5. Rmap\_drv – The register map control words can be manually entered to this text file

with corresponding addresses

```

#size

34

# Address #Control Register Values

x100 x20C4

x104 x00100180

x108 0x03FA010F

X008 OXAAAABBBB

# Mapping table Πook up

#WIFI

x800 x00010000

×804

×00000000

x808 x00010000

X80C

X00000000

×810

×00010000

x814 x00000000

```

6. Rmap\_stat – The status messages from the processing engine is written into this file

along with the address.

| Command Name<br>++++++++++++ | Command Code<br>+++++++++++++++ | Command Number<br>+++++++++++++++ | Trans. No.<br>+++++++++++ | Address<br>++++++++ | Received Value<br>++++++++++++++ | Expected Value<br>++++++++++++++++++++++++++++++++++++ |

|------------------------------|---------------------------------|-----------------------------------|---------------------------|---------------------|----------------------------------|--------------------------------------------------------|

| RxStartRcv                   | 0×81                            | 0                                 | 7                         | 0x0200              | 0x00000000                       | 0x003382F3                                             |

| RxStartRcv                   | 0×81                            | 0                                 | 8                         | 0×0204              | 0×00000000                       | 0x00276D54                                             |

| RxStartRcv                   | 0×81                            | 0                                 | 10                        | 0x020C              | 0x0000035                        | 0×00000015                                             |

| RXStartRcv                   | 0×81                            | 0                                 | 11                        | 0×0210              | 0×00000000                       | 0x0002E3BA                                             |

| RXStartRcv                   | 0×81                            | 0                                 | 12                        | 0×0214              | 0×000015AC                       | 0x00000329                                             |

| RxStartRcv                   | 0×81                            | 0                                 | 13                        | 0x0218              | 0×00000B00                       | 0×00000081                                             |

Error files – If the PE produces errors, the output buffer contents that are in error are written into this file.

| COMMAND_NUMBER                          | COMMAND_NAME                            | BUFFER_NO                               | DATA_INDEX                              | EXPECTED_DATA | DATA_IN_OUTPUT_BUFFER                   |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|---------------|-----------------------------------------|

| +++++++++++++++++++++++++++++++++++++++ | +++++++++++++++++++++++++++++++++++++++ | +++++++++++++++++++++++++++++++++++++++ | +++++++++++++++++++++++++++++++++++++++ | ************  | +++++++++++++++++++++++++++++++++++++++ |

| 1                                       | RXStartRcv                              | 15                                      | 1                                       | 0×0000003A    | 0x00000FF3                              |

| 1                                       | RxStartRcv                              | 15                                      | 2                                       | 0xc704DD7B    | 0×00000000                              |

| COMMAND NUMBER :                        | 1                                       |                                         |                                         |               |                                         |

| COMMAND NAME :                          | RXStartRcv                              |                                         |                                         |               |                                         |

| STATUS :                                | **FAIL**                                |                                         |                                         |               |                                         |

| ************                            | ***************                         | ********                                | ***                                     |               |                                         |

#### 5.3.3: Testbench Components

- Ibuf Driver When triggered, this module writes the content of the ibuf text file to the inout buffer. It follows the input buffer partitions and writes to the RAM on every command.

- Obuf Monitor This component is responsible for the comparison of the output buffer to the reference obuf text file. It also generates the error file which shows the addresses where the word was written in error.

- 3. Rmap Driver The RMAP driver has the slave interfaces that are connected to the RMAP interfaces. This acts like the bus and writes the rmap\_drv test file's content to the RMAP RAM. The pre-command processor loads the control words to the register and the post-command processor compares the content of the status register to the rmap\_stat text file.