# INFORMATION THEORETIC AND SPECTRAL METHODS OF TEST POINT, PARTIAL-SCAN AND FULL-SCAN FLIP-FLOP INSERTION TO IMPROVE INTEGRATED CIRCUIT TESTABILITY

BY RAGHUVEER AUSOORI

A thesis submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of Prof. Michael L. Bushnell and approved by

New Brunswick, New Jersey October, 2009 © 2009

Raghuveer Ausoori

ALL RIGHTS RESERVED

## ABSTRACT OF THE THESIS

# Information Theoretic and Spectral Methods of Test Point, Partial-Scan and Full-Scan Flip-Flop Insertion to Improve Integrated Circuit Testability

# by Raghuveer Ausoori Thesis Director: Prof. Michael L. Bushnell

We present a radically new design for testability (DFT) algorithm, which inserts test points (TPs) and scanned flip-flops (SFFs) into large circuits to make them testable. The algorithm measures testability using Shannon's entropy measure (from information theory), which will be shown to be a vastly superior way to measure testability, and spectral co-efficients. The spectral measures are superior in measuring fault coverage (FC) improvement. The algorithm can determine the DFT candidates using a gradient descent method or using an integer linear program (ILP). The optimal insertion of the TPs and SFFs reduces the amount of DFT hardware, since the algorithm trades off inserting a TP versus inserting a SFF. Various other derived measures are used and found to be effective in making the circuit testability better at various stages. The integer linear program finds the optimal solution to the optimization, and the testability measures are used to maximize information flow through the circuit-under-test (CUT). The result, on full-scan designs with test points, is a 40.05% reduction in test volume (TV) and a 54.24% reduction in *test application time* (TAT), compared to a full-scan design without test points. The method, used in conjunction with the Synopsys TetraMAX<sup>TM</sup> automatic test pattern generator (ATPG), achieves 1.55% higher fault coverage (FC) and 100% fault efficiency (FE) on ITC '99 benchmark circuits compared to conventional methods and reduces the ATPG time by 90.24%. The method works better than all prior methods on partial-scan circuits, as well. We achieve TV reductions of 19.56% and 33.42% and TAT reductions of 21.63% and 31.23%, over the previous best SPARTAN PS+TP1 and PS+TP2 partial scan ideas, respectively, on ISCAS '89 benchmark circuits. We also get 32.62% TV reduction and 25.39% TAT reduction over the mpscan algorithm.

## Acknowledgements

I would like to express my gratitude to Prof. Bushnell for helping me and spending his valuable time with me to bring my thesis to fruition. I am thankful for all the attention he diverted toward my work especially during the latter part of the thesis. I would also like to convey my special thanks to Dr. Tapan Chakraborty and Dr. Xinghao Chen for their feedback and ideas to make this work as good as it is now.

I would like to acknowledge my parents and family for their faith in me, which is all I needed to keep pushing myself through the hardest of times. I also want to convey my gratitude to my roommates, Hari, Shyam, Shiva and Venkat, who were my family away from home, without whom I could not have survived a day after landing in the US.

My acknowledgments would not be complete without the mention of my mentors Dr. Rajamani Sethuram and Dr. Omar Khan from whom I have learned much about DFT and I would like to thank them for all their insight and timely advice. I also thank my other seniors Dr. Hari Vijay, Varadan, Roystein, Sharanya and Aditya for making my lab visits something to look forward to. I thank all of my friends for making my graduate and personal life a lot more fun.

# Dedication

To my parents Banu and Krishna, my grandmother Janakibhai Kannan, my uncle and aunt Hanumantha Rao and Sasikala, my aunt Nalini Sathyakumar, my uncle Rajendran, my uncle Narendran, my roommates Hari, Shyam, Shiva and Venkat, and all my friends.

# Table of Contents

| Abstract                                                                                                    | ii  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Acknowledgements iv                                                                                         |     |  |  |  |

| Dedication                                                                                                  |     |  |  |  |

| List of Tables                                                                                              |     |  |  |  |

| List of Figures                                                                                             | cii |  |  |  |

| 1. Introduction                                                                                             | 1   |  |  |  |

| 1.1. Need for DFT Insertion                                                                                 | 2   |  |  |  |

| 1.2. Original Contributions                                                                                 | 4   |  |  |  |

| 1.2.1. Fully Automated Procedure                                                                            | 4   |  |  |  |

| 1.2.2. Combined Scan Flip-Flop and Test Point Insertion $\ldots$                                            | 4   |  |  |  |

| 1.2.3. Entropy Analysis                                                                                     | 5   |  |  |  |

| 1.2.3.1. Unbiasing $\ldots$                                                                                 | 5   |  |  |  |

| 1.2.3.2. Integer Linear Programming                                                                         | 6   |  |  |  |

| 1.2.3.3. Derivative Measures                                                                                | 6   |  |  |  |

| 1.2.4. Spectral Analysis                                                                                    | 7   |  |  |  |

| 1.2.4.1. High Speed Bit-Wise Computation                                                                    | 7   |  |  |  |

| 1.3. Results                                                                                                | 7   |  |  |  |

| 1.4. Outline of the Thesis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 8   |  |  |  |

| 2. Prior Work                                                                                               | 9   |  |  |  |

| 2.1. Entropy as a Testability Measure                                                                       | 9   |  |  |  |

| 2.1.1. Why Entropy is a Better Testability Measure                                                          | 10  |  |  |  |

|    | 2.2. | Partia  | l Scan                                                     | 14 |

|----|------|---------|------------------------------------------------------------|----|

|    |      | 2.2.1.  | Designing Circuits with Partial Scan                       | 14 |

|    |      | 2.2.2.  | An Exact Algorithm for Selecting Partial Scan Flip-Flops . | 15 |

|    |      | 2.2.3.  | Partial-Scan Design Based on Circuit State Information and |    |

|    |      |         | Functional Analysis                                        | 18 |

|    |      | 2.2.4.  | SPARTAN – A Spectral and Information Theoretic Ap-         |    |

|    |      |         | proach to Partial-Scan                                     | 20 |

|    |      | 2.2.5.  | Other Partial Scan Algorithms                              | 22 |

|    | 2.3. | Test P  | Point Insertion in Non-Scan Designs                        | 23 |

|    |      | 2.3.1.  | Self-Driven Test Structure for Pseudo-random Testing of    |    |

|    |      |         | Non-Scan Sequential Circuits                               | 23 |

|    |      | 2.3.2.  | Non-Scan Design-for-Testability Techniques for Sequential  |    |

|    |      |         | Circuits                                                   | 24 |

|    |      | 2.3.3.  | Non-Scan Design for Testability for Synchronous Sequential |    |

|    |      |         | Circuits Based on Conflict Resolution                      | 26 |

|    | 2.4. | Test P  | Point Insertion in Full-Scan and Partial Scan Designs      | 28 |

|    |      | 2.4.1.  | Constructive Multi-Phase TPI for Scan-Based BIST           | 28 |

|    |      | 2.4.2.  | Timing-Driven TPI for Full-Scan and Partial-Scan BIST $$ . | 31 |

|    |      | 2.4.3.  | Zero Cost TPI Technique for Structured ASICs               | 33 |

|    |      | 2.4.4.  | SPARTAN – A Spectral and Entropy-based Partial-scan        |    |

|    |      |         | and Test Point Insertion Algorithm                         | 35 |

|    |      | 2.4.5.  | Other Test Point Insertion Algorithms                      | 36 |

|    | 2.5. | Summ    | ary                                                        | 37 |

| 3. | Inte | eger Li | near Programming Approach and Formulation                  | 39 |

|    | 3.1. | Why V   | We Chose an Integer Linear Program to Select Scan-Flops    |    |

|    |      | and Te  | est Point Candidates                                       | 39 |

|    |      | 3.1.1.  | Advantages of Integer Linear Programs over Greedy Algo-    |    |

|    |      |         | rithms                                                     | 40 |

|    | 3.2. | Integer Linear Program Formulation                |

|----|------|---------------------------------------------------|

|    |      | 3.2.1. Sets 41                                    |

|    |      | 3.2.2. Parameters                                 |

|    |      | 3.2.3. Variables                                  |

|    |      | 3.2.4. Objective Function                         |

|    |      | 3.2.5. Constraints                                |

|    | 3.3. | Convergence of the ILP                            |

|    | 3.4. | Summary 46                                        |

| 4. | Alg  | orithm                                            |

|    | 4.1. | Strongly Connected Components                     |

|    | 4.2. | Logic Simulation                                  |

|    |      | 4.2.1. Advantages over Parker-McCluskey Equations |

|    | 4.3. | Entropy Calculation                               |

|    | 4.4. | Spectra Calculation                               |

|    | 4.5. | Candidate Selection                               |

|    |      | 4.5.1. ILP Mode                                   |

|    |      | 4.5.2. Gradient Descent Mode                      |

|    |      | 4.5.3. Probability Mode                           |

|    |      | 4.5.4. Entropy Mode                               |

|    |      | 4.5.5. Unbiased Entropy Mode                      |

|    |      | 4.5.6. Accumulated Entropy Mode                   |

|    |      | 4.5.7. Entropy Gain Mode                          |

|    |      | 4.5.8. Entropy Differential Mode                  |

|    |      | 4.5.9. Spectral Mode                              |

|    | 4.6. | DFT Insertion                                     |

|    | 4.7. | Flow Chart                                        |

|    | 4.8. | Complexity Analysis of the Algorithm              |

|    | 4.9. | Summary                                           |

| 5. | Res  | ults .                                      |                                                                             |  |

|----|------|---------------------------------------------|-----------------------------------------------------------------------------|--|

|    | 5.1. | Prelim                                      | inaries $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $65$ |  |

|    | 5.2. | Full Scan with Test Point Insertion Results |                                                                             |  |

|    |      | 5.2.1.                                      | Experimental Conditions and Validation                                      |  |

|    |      | 5.2.2.                                      | Fault Coverage Results    70                                                |  |

|    |      | 5.2.3.                                      | Fault Efficiency Results    77                                              |  |

|    |      | 5.2.4.                                      | Test Vector Length Results                                                  |  |

|    |      | 5.2.5.                                      | Test Volume Results                                                         |  |

|    |      | 5.2.6.                                      | Test Application Time Results                                               |  |

|    |      | 5.2.7.                                      | ATPG Time Results                                                           |  |

|    |      | 5.2.8.                                      | Entropy Run Time Results                                                    |  |

|    |      | 5.2.9.                                      | Calculation of Unbiasing factor                                             |  |

|    |      | 5.2.10.                                     | Reasons for Algorithm Performance                                           |  |

|    |      | 5.2.11.                                     | Summary of Full Scan with Test Point Results 104                            |  |

|    | 5.3. | Partia                                      | l Scan with Test Point Insertion Results                                    |  |

|    |      | 5.3.1.                                      | Experimental Conditions                                                     |  |

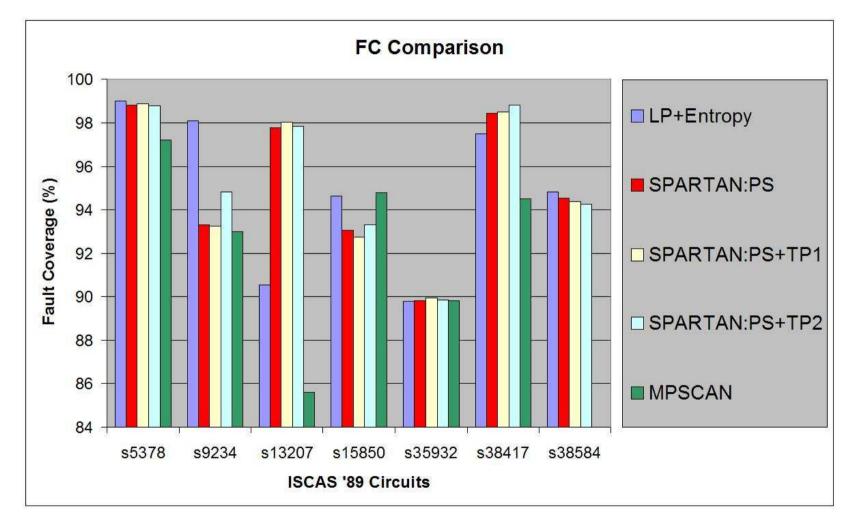

|    |      | 5.3.2.                                      | Fault Coverage and Overhead Results                                         |  |

|    |      | 5.3.3.                                      | Test length, Test Volume and Test Application Time Results111               |  |

|    |      | 5.3.4.                                      | Reasons for Algorithm Performance                                           |  |

|    |      | 5.3.5.                                      | Summary of Partial Scan with Test Point Results 116                         |  |

| 6. | Imp  | lement                                      | tation                                                                      |  |

|    | 6.1. | Writin                                      | g out the Data file                                                         |  |

|    | 6.2. | Transf                                      | erring Data and Output Files                                                |  |

|    | 6.3. | Secure                                      | Shell                                                                       |  |

|    | 6.4. | Readir                                      | ng the Output File                                                          |  |

|    | 6.5. | Summ                                        | ary                                                                         |  |

| 7. | Con  | clusio                                      | ns and Future Work                                                          |  |

|    | 7.1. | Conclu                                      | usions                                                                      |  |

| 7.2. Future Work               | 123 |

|--------------------------------|-----|

| References                     | 125 |

| Appendix A. Entropy User Guide | 131 |

# List of Tables

| 4.1.  | Truth table for example circuit.                                                | 50  |

|-------|---------------------------------------------------------------------------------|-----|

| 5.1.  | Characteristics and parameters for ITC '99 Benchmark Circuits $% \mathcal{A}$ . | 69  |

| 5.2.  | Fault Coverage results of ITC '99 Benchmark Circuits                            | 72  |

| 5.3.  | Fault Efficiency results of ITC '99 Benchmark Circuits                          | 78  |

| 5.4.  | Test Vector Length results of ITC '99 Benchmark Circuits $\ .\ .\ .$            | 84  |

| 5.5.  | Test Volume results of ITC '99 Benchmark Circuits                               | 88  |

| 5.6.  | Test Application Time results of ITC '99 Benchmark Circuits $~$                 | 92  |

| 5.7.  | ATPG Time results (in sec) for ITC '99 Benchmark Circuits $\ . \ .$             | 96  |

| 5.8.  | Run Time results (in sec) for ITC '99 Benchmark Circuits $\ .\ .\ .$            | 100 |

| 5.9.  | Unbiasing Factor for ITC '99 Circuits                                           | 103 |

| 5.10  | . Characteristics and parameters of ISCAS '89 Benchmark Circuits                | 106 |

| 5.11. | . GATEST parameters                                                             | 106 |

| 5.12  | Partial-Scan Scanned Flip-Flop Count, Test Point Count, Fault                   |     |

|       | Coverage, and Hardware Overhead for ISCAS '89 Circuits $\ . \ . \ .$            | 108 |

| 5.13. | Partial-Scan Test Vector Count, Test Volume and Test Application                |     |

|       | Time for ISCAS '89 Circuits                                                     | 112 |

# List of Figures

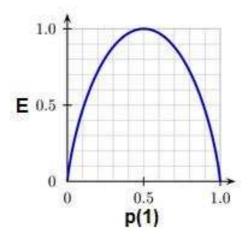

| 2.1. Entropy, $E$ , vs. $p(1)$ for a signal $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 10 |

|-------------------------------------------------------------------------------------------------------|----|

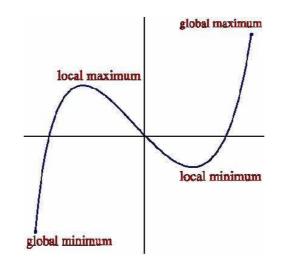

| 3.1. Range of values for a sub-problem                                                                | 40 |

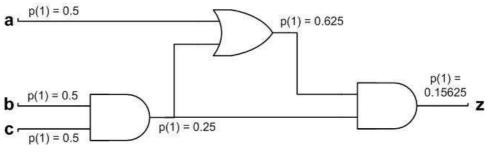

| 4.1. Example circuit                                                                                  | 50 |

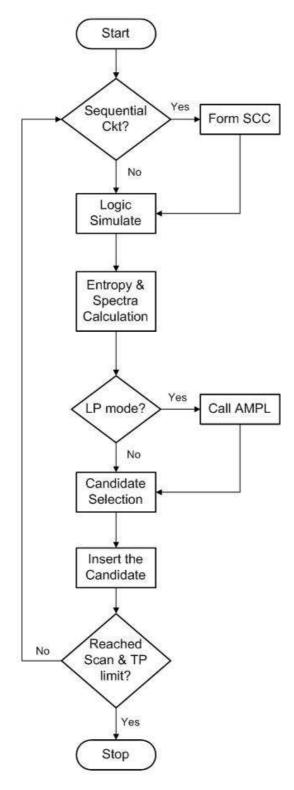

| 4.2. Flow chart of the algorithm                                                                      | 61 |

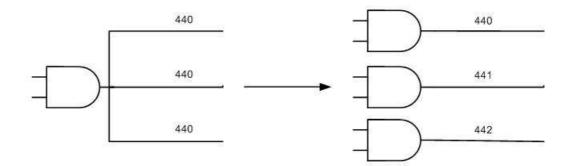

| 5.1. Example gate showing modification of b05                                                         | 68 |

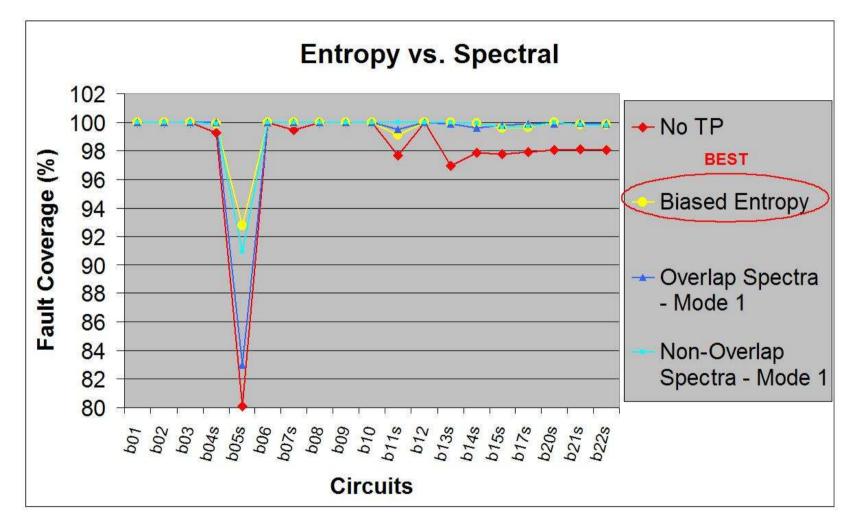

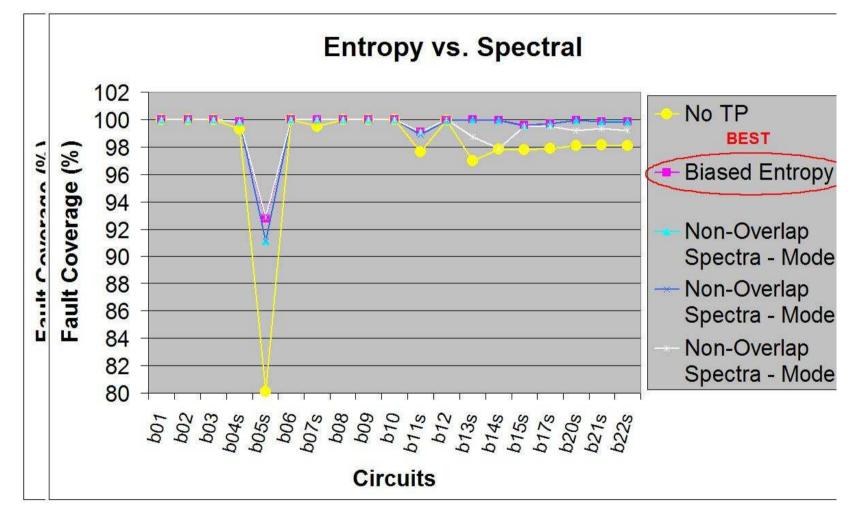

| 5.2. Fault Coverage comparison: Entropy vs. Spectral                                                  | 73 |

| 5.3. Fault Coverage comparison: Entropy vs. Spectral                                                  | 74 |

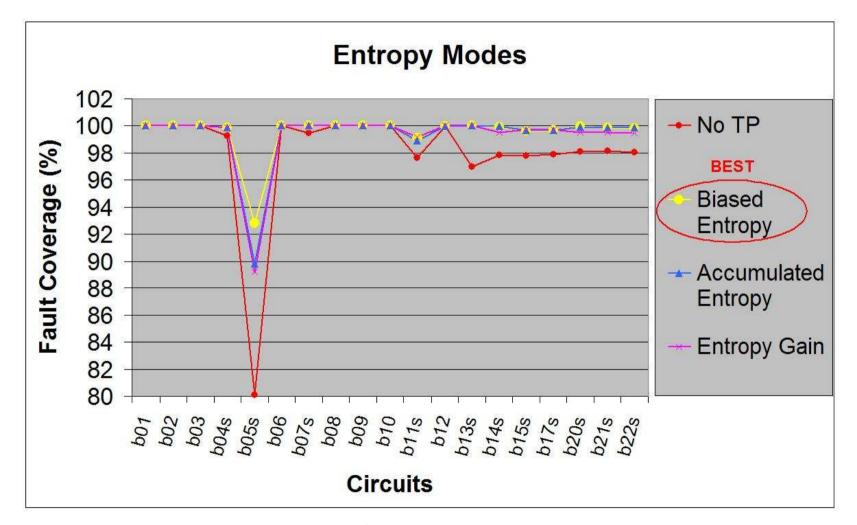

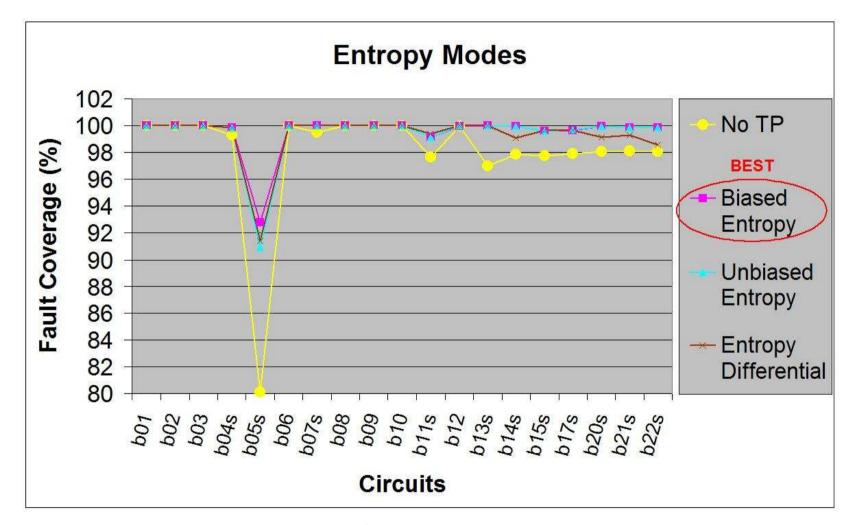

| 5.4. Fault Coverage comparison: Entropy Modes                                                         | 75 |

| 5.5. Fault Coverage comparison: Entropy Modes                                                         | 76 |

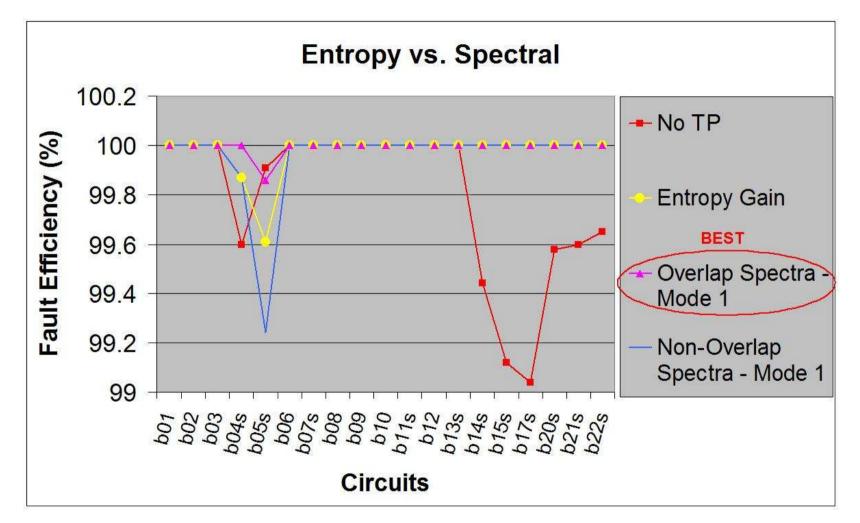

| 5.6. Fault Efficiency comparison: Entropy vs. Spectral                                                | 79 |

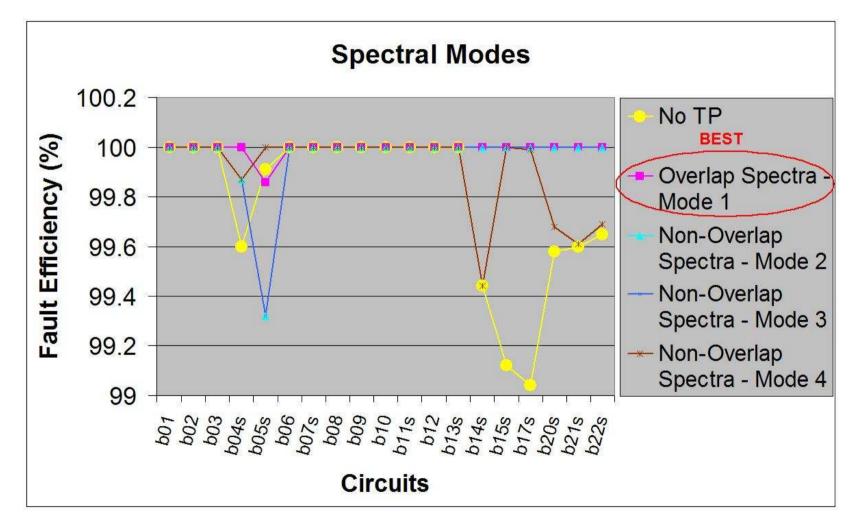

| 5.7. Fault Efficiency comparison: Spectral Modes                                                      | 80 |

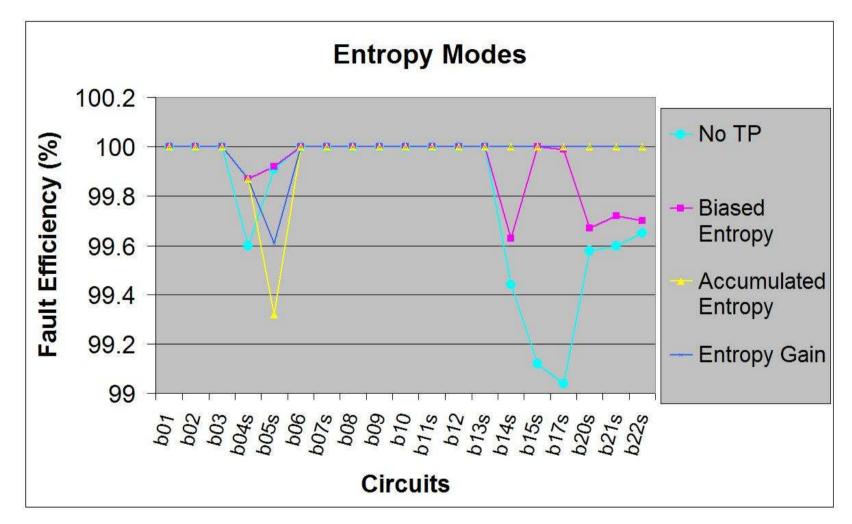

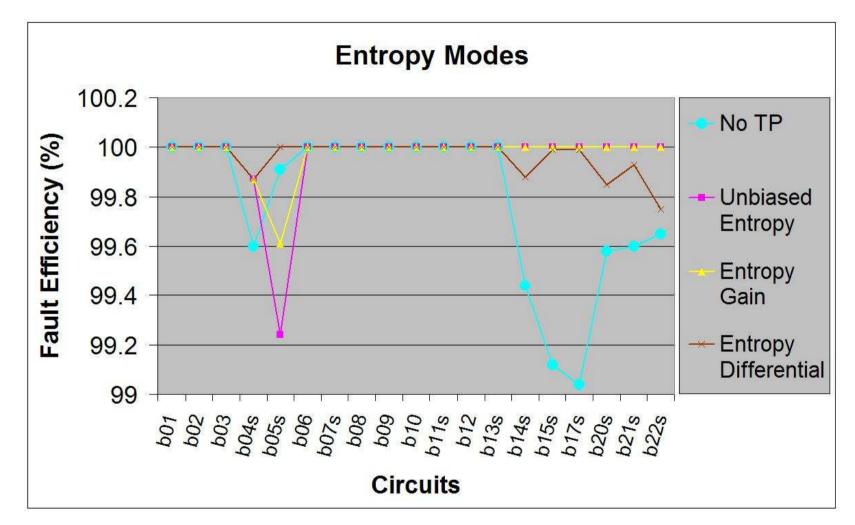

| 5.8. Fault Efficiency comparison: Entropy Modes                                                       | 81 |

| 5.9. Fault Efficiency comparison: Entropy Modes                                                       | 82 |

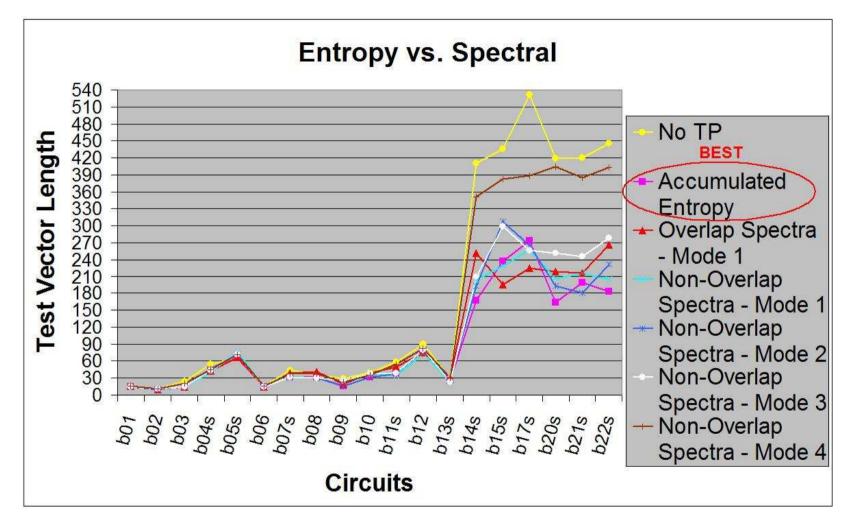

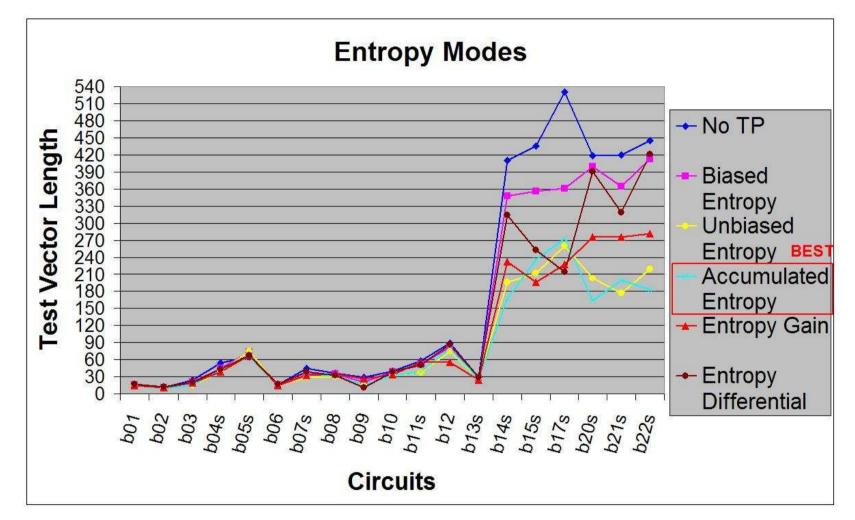

| 5.10. Test Vector Length comparison: Entropy vs. Spectral                                             | 85 |

| 5.11. Test Vector Length comparison: Entropy Modes                                                    | 86 |

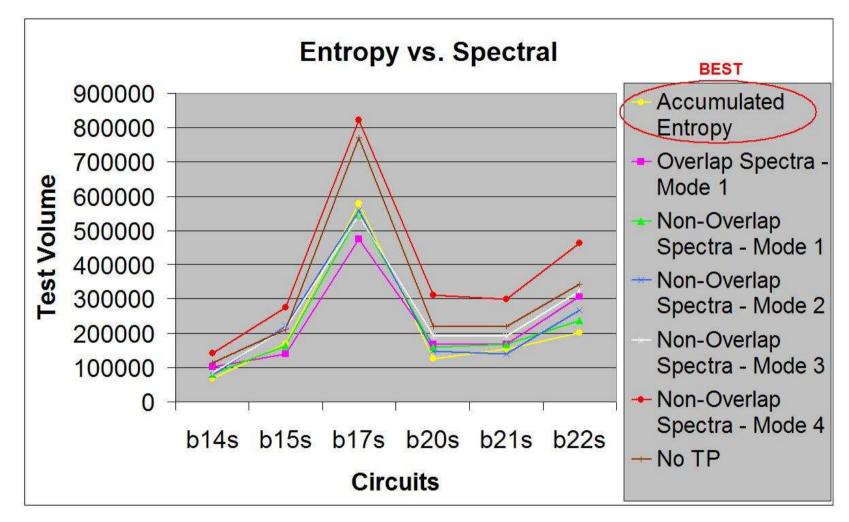

| 5.12. Test Volume comparison: Entropy vs. Spectral                                                    | 89 |

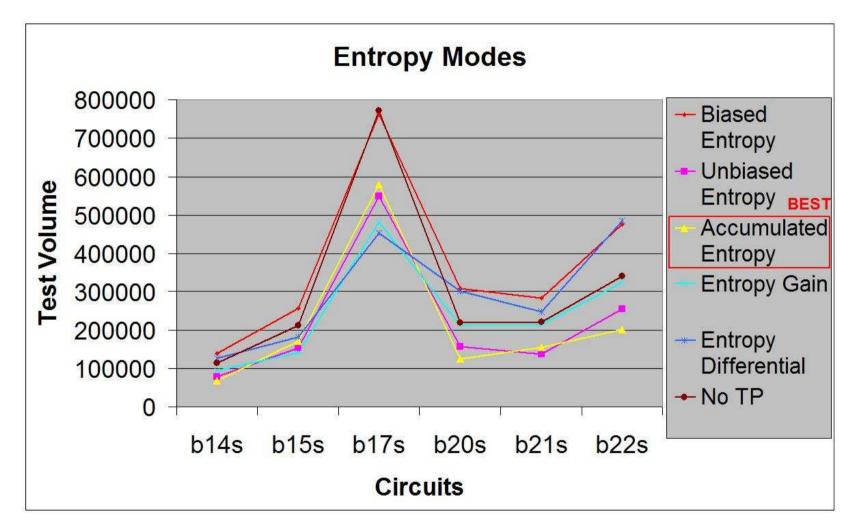

| 5.13. Test Volume comparison: Entropy Modes                                                           | 90 |

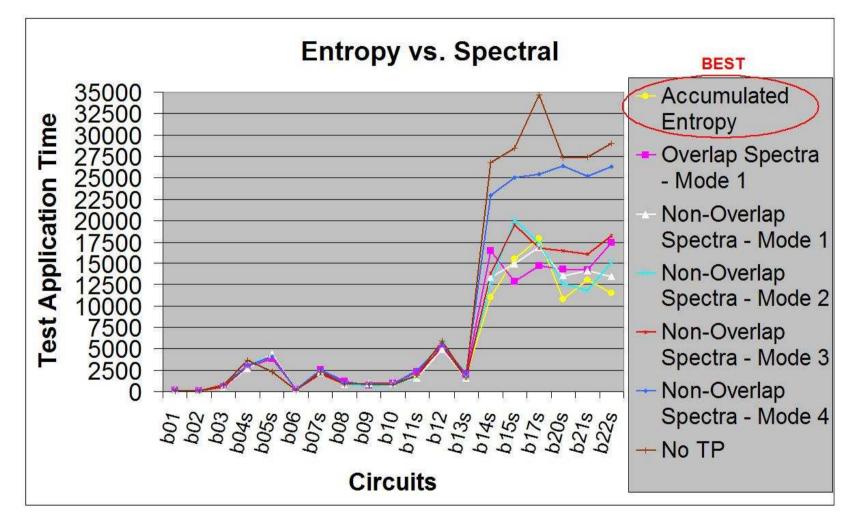

| 5.14. Test Application Time comparison: Entropy vs. Spectral                                          | 93 |

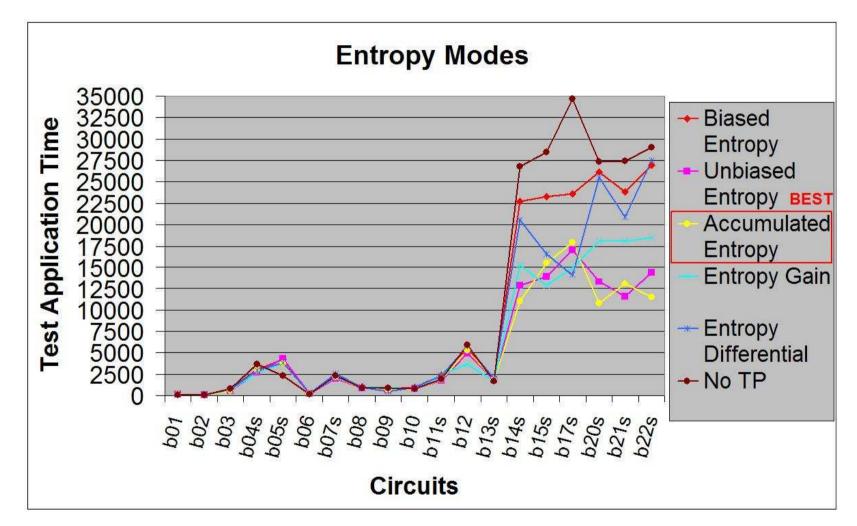

| 5.15. Test Application Time comparison: Entropy Modes                                                 | 94 |

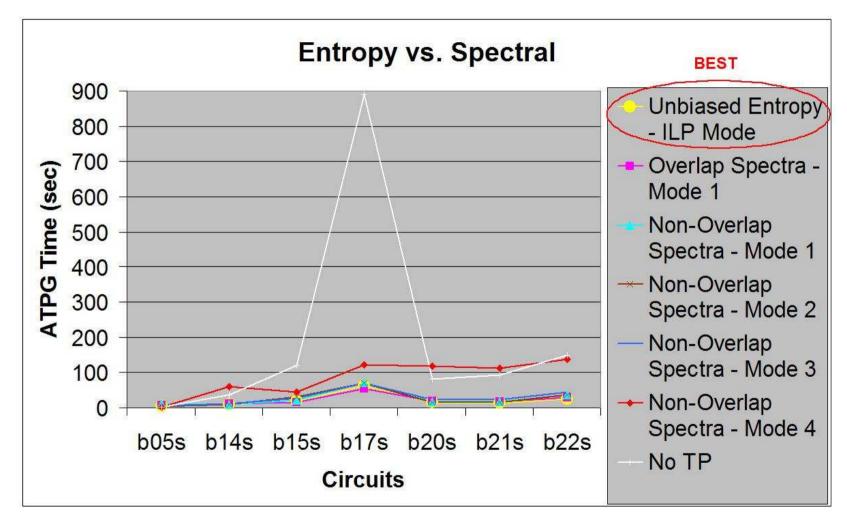

| 5.16. ATPG Time comparison: Entropy vs. Spectral                                                      | 97 |

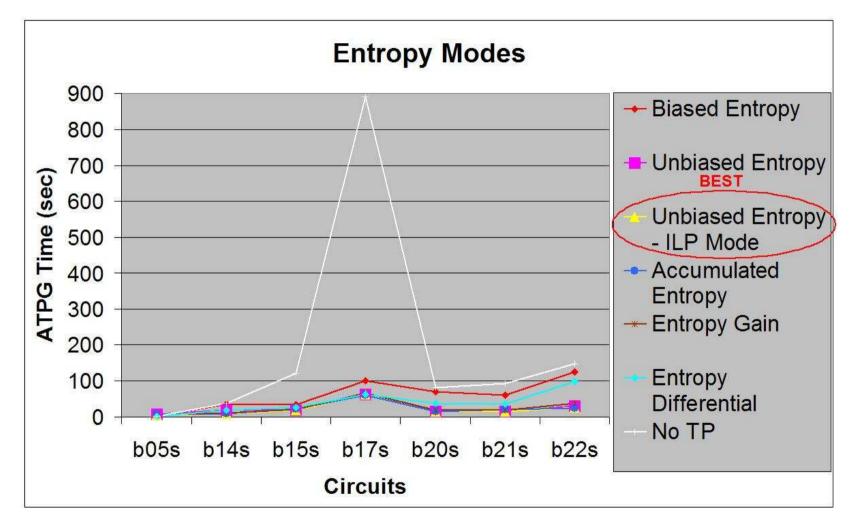

| 5.17. ATPG Time comparison: Entropy Modes                                                             | 98 |

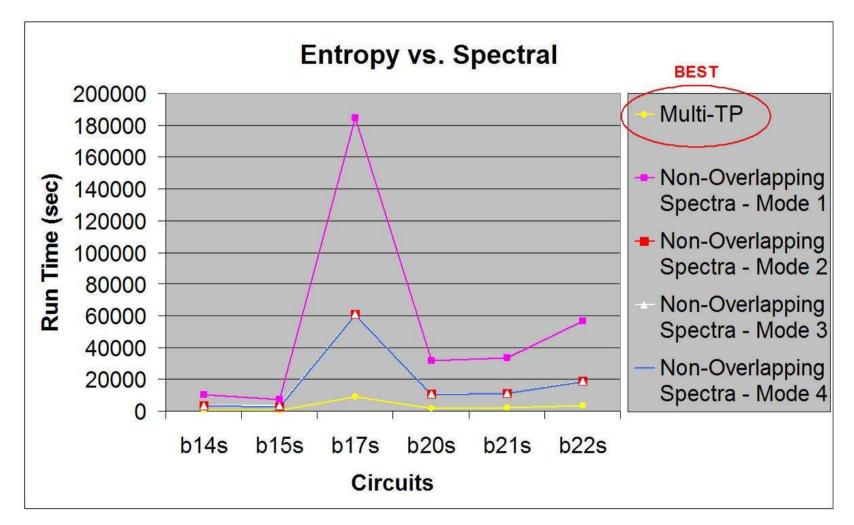

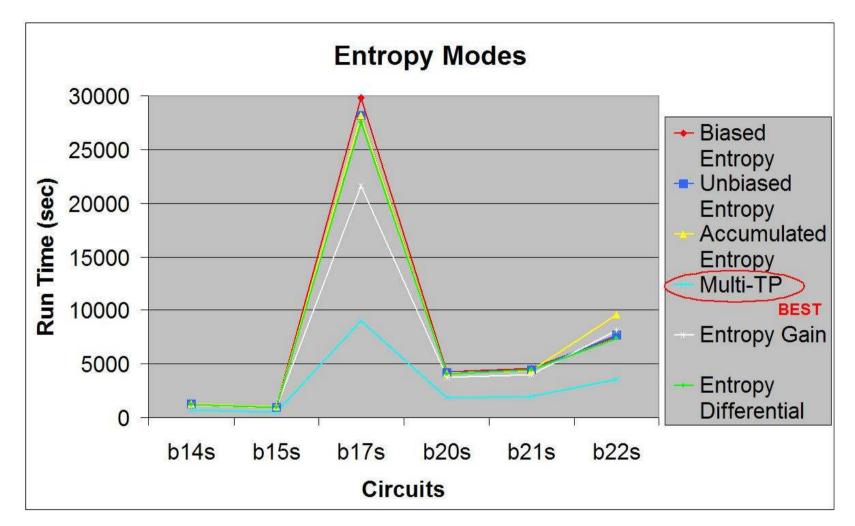

| 5.18. Run Time comparison: Entropy vs. Spectral                                                       | 01 |

| 5.19. Run Time comparison: Entropy Modes                                                              | 02 |

| 5.20. Fault Coverage comparison        | 109 |

|----------------------------------------|-----|

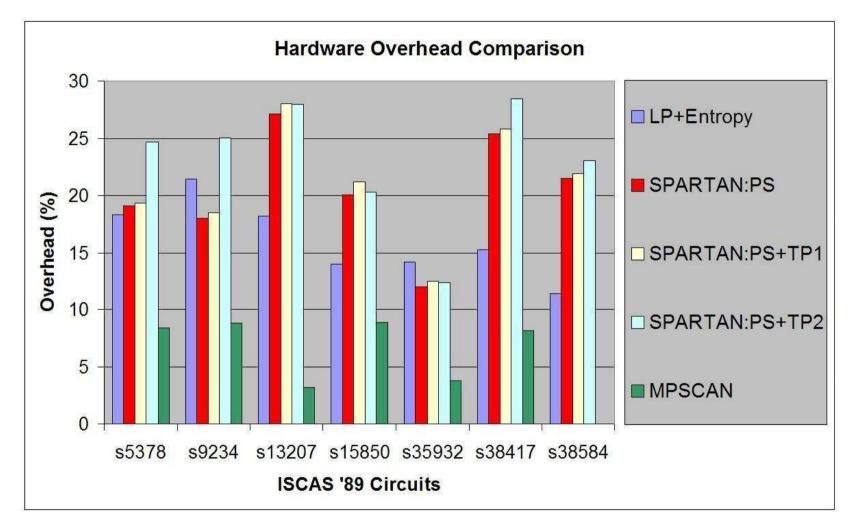

| 5.21. Hardware Overhead comparison     | 110 |

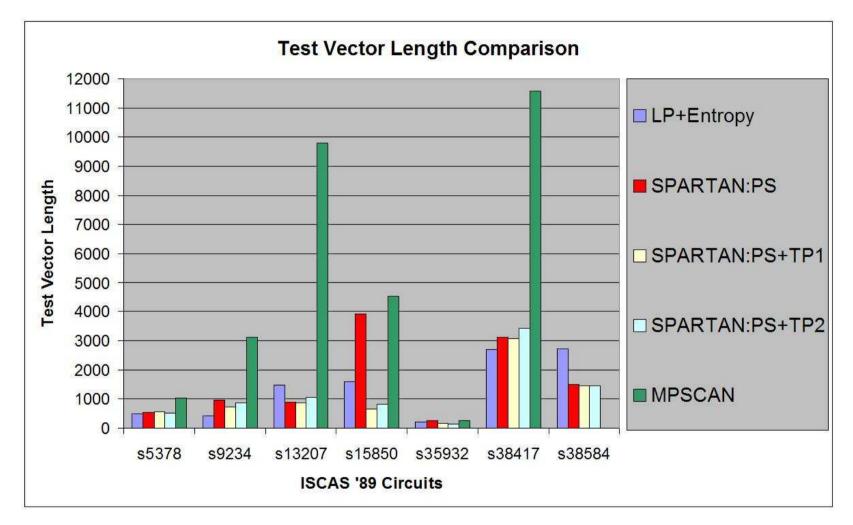

| 5.22. Test Vector Length comparison    | 113 |

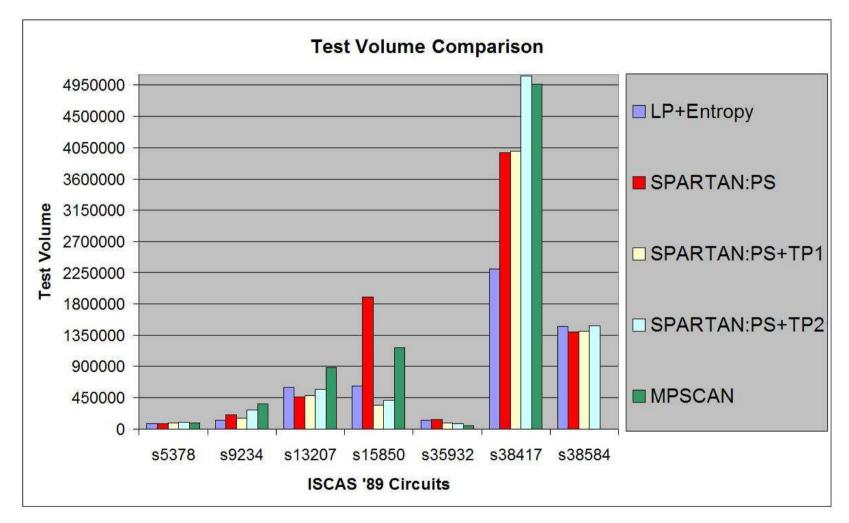

| 5.23. Test Volume comparison           | 114 |

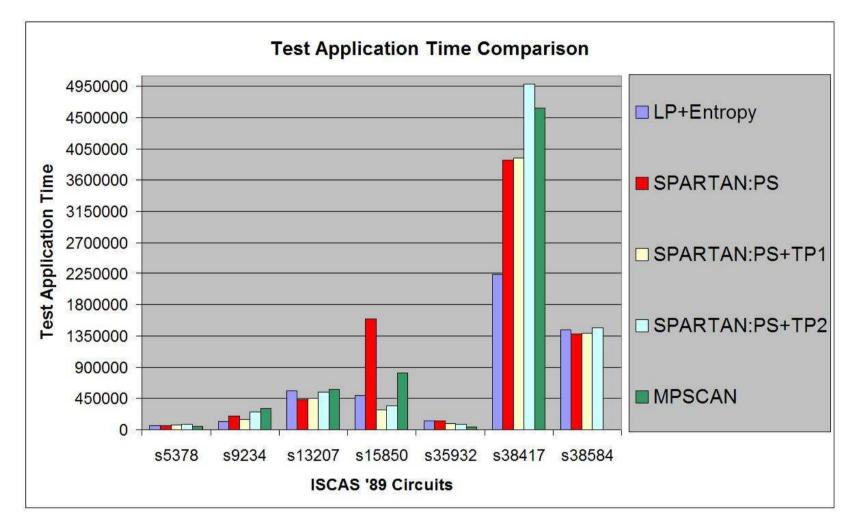

| 5.24. Test Application Time comparison | 115 |

# Chapter 1 Introduction

The Equation below represents Moore's Law [45], which stated that the number of transistors on a chip will double roughly every year and a half. This is mathematically shown by Bell [5] as follows:

Transistors per chip =

$$2^{t-1959}$$

for  $1959 \le t \le 1975$

$2^{16} \times 2^{(t-1975)/1.5}$  for  $t \ge 1975$

The first half of the Equation shows that every year after 1959, the number of transistors per chip doubles from the previous year. The growth in the *integrated circuit* (IC) industry was so rapid that Moore's Law had to be modified as shown in the second half of the Equation, which shows that the number of transistors in a chip doubles every one and a half years. The transistor count on each chip has already broken the one billion barrier and continues to increase rapidly. It is now commonplace to have netlists with more than 50 million logic gates. By 2010, scalable CMOS microprocessors could combine into powerful, multiple processor clusters of up to one million independent computing streams [5]. Designing and fabricating these devices pose a tough challenge to the industry and this challenge has to be met with less cost than for the previous generation to survive in the market. Companies strive to be the first to release new chip sets and capture a greater share of the market. In order to achieve this, a good fabrication line and a good testing scheme are required.

### 1.1 Need for DFT Insertion

Hardware testing is the process of testing the chip to determine whether the chip has been fabricated properly. The cause of failure can be that the fabrication process was faulty or there could be a design or specification mistake or the test itself was wrong to begin with. The role of testing is to detect whether something went wrong and if anything did, then the defect can be diagnosed and rectified, and the process is repeated. A good test helps remove the bad chips in a short amount of time. While testing, the metric that is observed is *fault coverage* (FC), which is the percentage of faults detected by the tests. The higher the FC, the better the quality of the chip. Getting high FC on chips with one billion transistors is hard and to make the process easy, the chips are designed so that they are easily testable. This concept is called as *design-for-testability* (DFT). In DFT, the chip logic is altered so that the chip is easier to test with higher FC, while maintaining the original functionality. The following are some ideas used in DFT:

- Full Scan: Scanning is the process of converting the hard-to-test flip-flops present in the circuit into shift registers, and thus, making them easier to control from the pins. When all of the flip-flops present in the circuit are scanned, then the circuit acts as a combinational circuit and it is said to be *full-scanned*. Combinational circuits are easier to test with high FC, but have high hardware and delay overheads.

- Partial Scan: When only a subset of flip-flops present in the circuit are scanned, then the circuit is said to be *partially-scanned* [2]. The circuit still remains sequential but a good partial-scan algorithm should be able to achieve high FC [35, 36]. The hardware overhead is less than for a full-scanned circuit.

- **Test Point Insertion:** Test points are special designs that help introduce a certain logic value into a particular combinational part of the circuit or

help observe the output of a gate. They help improve the testability of combinational parts of the circuits [62]. Another advantage of test points is that when placed properly, they can help reduce the amount of time taken to test the circuit [57].

Testing a chip costs money and it is estimated that testing alone comprises about 33% to 40% of the chip cost [10]. Automatic test equipment (ATE) is very costly and its operating cost increases with every second. ATE tests the chips by applying certain inputs to the pins of the chip and observing the outputs to detect faults. The inputs that are applied to the chips are called test vectors, which are determined before the fabrication of the chip. The test vector sets are processed to achieve high FC with fewer vectors. The total number of vector bits stored in the ATE is called the *test volume* (TV) and the time taken by the ATE to apply the test vectors to one chip and read its outputs is called the *test application time* (TAT). Higher TV and TAT add to the test cost of the chip. Testing cost with the latest equipement is estimated to be 7 cents per second. The more time each chip spends on the ATE, the higher the testing cost incurred. For example, let us assume that the test time for a digital *application specific IC* (ASIC) is around 10 seconds and that 100,000 chips are fabricated every day.

Testing  $Cost = 7 \times 10 \times 100,000 = 7,000,000$  cents = \$70,000 per day

By using the DFT ideas discussed above intelligently, the TV and TAT can be reduced, which in turn, helps reduce the test cost. The ideas proposed in this thesis help reduce the TV by 40.05% and TAT by 54.24%, while acheiving a near 100% stuck-at FC. Now the testing cost calculation becomes:

Testing Cost =

$$7 \times 10 \times 100,000 \times (1 - 0.5424) = $32,032$$

per day

Using the ideas proposed here, the testing cost is cut in half. Hence, DFT insertion not only contributes to higher FC, but it can also help reduce the cost of the product.

#### **1.2** Original Contributions

The previous section explained why DFT insertion is important from the quality and economic viewpoint of the IC industry and how the ideas proposed in this thesis help with better DFT. This section explains what makes the ideas unique and better than existing ideas.

### **1.2.1** Fully Automated Procedure

Existing automated methods insert partial-scan or full-scan DFT hardware. However, for high-performance designs, the DFT insertion process is largely manual, because various performance and low power design constraints make it difficult to fully automate this. This leads to a very labor intensive process of an expert test engineer inserting the DFT hardware by hand into a high-performance design, such as a microprocessor or cell phone chip. This thesis provides better design automation, because the algorithm for DFT hardware insertion allows performance critical nets in the circuit to be weighted, so that the algorithm will never put DFT hardware on those nets, but instead the hardware is driven off of the nets onto other sites. The algorithm, thus, reduces the manual process involved in DFT insertion and reduces the design time and time-to-market of the product.

### **1.2.2** Combined Scan Flip-Flop and Test Point Insertion

Existing partial scan with test point insertion algorithms first scan the flip-flops and then insert test points [35, 36, 37]. Following this two-step procedure could increase the hardware overhead and TV of the circuit. One original idea here is to simultaneously insert test points while scanning the flip-flops, so that the advantages of either can be weighed and a wiser choice can be made. In the former method, if the testability of a combinational block is found to be low, a nearby flip-flop will be scanned to improve the testability but if this does not help the cause, then the second stage of the algorithm will insert a test point, thus increasing overhead. The latter method would automatically insert a test point at the appropriate point in the combinational block. This concept can be observed through the results obtained where the idea performs better than the previous best idea with less overhead.

## 1.2.3 Entropy Analysis

Entropy is the amount of information flowing through a particular point of interest in the circuit, first proposed by Shannon [59]. If there is more information flowing through a gate, then there is more activity in the gate and, hence, it can be more easily controlled. Increasing the information flow throughout the circuit translates into better circuit testability. Entropy is a very simple testability measure that can be easily calculated by logic simulating the circuit with a certain number of random input vectors. The entropy analysis is explained in detail in the Chapter 4. Using entropy as a testability measure has been proposed before by Dussault [23]. He proposed a way to calculate the entropy and conditional entropy of the gates in the circuit and defined observability, controllability and testability measures from the entropy values. Agrawal [3] proposed a method to use entropy for digital fault testing. He calculates the detection probability of a fault and explains how to suitably design a pattern generator to improve the detection probability. Thearling and Abraham [64] proposed information theory based testability measures at the functional level. Probabilities were estimated either via logic simulation, called *sampling*, or by using functional level information of the circuit components, known as *composition*. They also proposed partitioning of the circuit, to improve testability, using entropy-related measures. We use the following ideas to obtain better performance.

#### 1.2.3.1 Unbiasing

Entropy is calculated using logic simulation. This simulation does not exhaust the input space for the circuit as that can be very time consuming for larger circuits and, hence, a sample of the input space is used for logic simulation. This input vector sampling can introduce a statistical sample bias into the entropy values [28, 31]. We propose a novel way of calculating this bias and a method to remove the bias. Our bias removal improves the algorithm performance greatly when compared to using biased entropy as the testability measure.

#### 1.2.3.2 Integer Linear Programming

Integer linear programming is an optimization algorithm that chooses the optimal solution for the problem. The proposed algorithm uses an integer linear program to choose candidates for scanning and test point insertion based on the testability measures. Another advantage with using an integer linear program is that in the case of many candidates having the same testability measure, the selection is made randomly, which works better than selecting based on a candidate characteristic such as the gate name.

#### 1.2.3.3 Derivative Measures

Entropy as such can be an effective testability measure for candidate selection but the entropy measure only accounts for difficult-to-control gates. To account for difficult-to-observe gates, derivative measures were invented:

- *Entropy gain* selects candidates by the increase in entropy at the fan-out gates if the candidate is scanned or receives a combinational logic test point.

- *Entropy differential* selects candidates by the drop in entropy from the candidate to its fan-out gates.

After inserting a test point or scanning a flip-flop, the variables used for the entropy calculation are cleared for recalculation of the entropy in the next simulation. When these variables are not cleared, the information from previous simulations accumulates and the entropy calculated using this information is called *accumulated entropy*. The calculations of all of the measures are explained in detail in the Chapter 4.

### 1.2.4 Spectral Analysis

Spectral analysis of a circuit gives information about the types of frequencies that best excite the circuit. The output from each gate for 32 clock periods is multiplied with a  $32 \times 32$  Hadamard matrix, to calculate the spectral co-efficients of the gate. The spectral co-efficients calculated from the result help identify the natural response frequencies for the gate. Using spectral co-efficients as testability measures has been done before [35, 36, 37] and in this thesis, we use the existing ideas of spectral analysis in combination with our entropy ideas.

#### 1.2.4.1 High Speed Bit-Wise Computation

The original contribution to spectral analysis from the approach here is a high speed bit-wise computation to multiply the  $32 \times 32$  Hadamard matrix with the output of each gate to calculate its spectral co-efficients. The matrix multiplication is replaced with a bit-wise XNORing operation. Each row of the Hadamard matrix is transformed into a 32-bit word and the 32-bit logic response from the gate is bit-wise XNORed with each row to obtain the spectral co-efficients. This method speeds up the spectral analysis many fold.

### 1.3 Results

The complexity of the proposed gradient descent algorithm is  $O(N^2)$  with logic simulation taking the most computation time. The complexity of the algorithm while using integer linear program is  $O(2^N)$ , but the AMPL solver used manages to find a solution in a very short time and hence, this method can be used practically. The algorithm can be made to insert test points in a full-scan circuit or to insert test points and scan flip-flops in a partial-scan circuit. By inserting test points into a full-scan circuit, the algorithm was able to achieve a 40.47% TV and a 54.24% TAT reduction over a full-scan circuit with no test points. The fault coverage went up by 1.64% while keeping the hadware overhead below 10%, on average. By inserting both test points and scan flip-flops into a circuit with partial scan, the algorithm acheives 19.56% TV reduction and 21.63% TAT reduction over the previous best algorithm.

## 1.4 Outline of the Thesis

This thesis is organized as follows. Chapter 2 discusses the prior work in the DFT field. Section 2.1 introduces various interesting ideas used for partial scan, Section 2.2 explains the algorithms that insert test points into sequential circuits with no scan flip-flops, Section 2.3 discusses test point insertion algorithm in full-scan and partial scan designs and Section 2.4 introduces entropy as a testability measure and discusses its advantages. Chapter 3 discusses the integer linear programming approach and the formulation used by the algorithm to select the test point candidates. Chapter 4 explains the algorithm in detail including the various testability measures used and provides a flow chart of the entire procedure. Chapter 5 discusses in detail the various results obtained for various runs of the algorithm. Chapter 6 explains the implementation of the algorithm. Chapter 7 presents the conclusion and future work.

# Chapter 2 Prior Work

The design-for-testability (DFT) techniques are required to improve the testability and reduce the test cost of the circuit. DFT techniques include ad-hoc and structured techniques. Test point insertion (TPI) is a common ad-hoc DFT technique to improve the circuit testability and scan design is the most widely used structured DFT methodology. Full-scan, partial-scan and random-access scan (RAS) design are the three most common scan architectures. Full-scan techniques scan all the flip-flops in the circuit and make the circuit combinational so that it is easier to test. Partial scan techniques scan a subset of the flip-flops in the circuit and, hence, incur smaller hardware overhead and test volume than full-scan techniques. RAS techniques group the flip-flops present in the circuit into random access memory (RAM) and write the test vectors into them by using a special address scan register and address decoding hardware. TPI techniques concentrate on increasing the testability of the circuit by inserting controllability and observability points.

## 2.1 Entropy as a Testability Measure

Entropy as proposed in Shannon's Information Theory [59] is an effective measure of randomness in data. It is widely used as a measure of information in signals to combat noise-related errors of communication.

#### 2.1.1 Why Entropy is a Better Testability Measure

In this work, we use entropy as a testability measure to estimate the testability of circuits. The Entropy E of a signal that has n distinct values [44, 73, 74] is:

$$E = -\sum_{i=1}^{n} p_i \log_2(p_i),$$

where  $p_i =$  probability of outcome *i* (2.1)

Equation 2.1 is plotted in Figure 2.1 with Entropy E on the ordinate and the probability of an outcome being 1, p(1), on the abscissa. The maximum entropy in Figure 2.1 occurs when 0 and 1 are equally likely. Consider an 8-input AND

Figure 2.1: Entropy, E, vs. p(1) for a signal

gate, with p(0) = p(1) = 0.5 on each input. From SCOAP measures [26], the difficulty of setting the output to a 1 is CC(1) = 9, and the difficulty of setting it to a 0 is CC(0) = 2. From COP measures [49], the probability of the output being 1 is p(1) = 1/256 and p(0) = 255/256. However, the entropy measure of the output, which incorporates both 0 and 1 values, is 0.03687.

Dussault proposed the first information theoretic testability measure [23]. He proposed a way to calculate the entropy and conditional entropy of the gates in the circuit. Conditional entropy is the average information required to specify an event  $x \in X$  after  $y \in Y$  is known as shown in Equation 2.2. X and Y are events of logic 0 or logic 1 occurring at a gate or a primary input or a primary output.

$$E(X|Y) = -\sum_{x,y} P(x,y) \log_2 P(x|y)$$

(2.2)

He also defines the following measures for a circuit with inputs being X and outputs being Y:

Observability measure =

$$\frac{1}{E(X|Y)}$$

(2.3)

Controllability measure =

$$\frac{1}{E(Y|X)}$$

(2.4)

Testability measure =

$$I(X;Y) = E(X) - E(X|Y)$$

(2.5)

$$= E(Y) - E(Y|X)$$

Based on these measures he proposes to select test points for the circuit. Lines with low observability measures are observability test point candidates, lines with low controllability measures are controllability test point candidates, lines with low testability measures are complete test point candidates. He also proposes to calculate these measures using logic simulation or using Parker-McCluskey Equations [52]. He does not report any experimental results for his ideas, but the concepts he proposed were investigated further by Agrawal [3] and Thearling and Abraham [64].

Agrawal proposed an information theoretic approach to testing digital circuits [3] and derived the probability P(T) of detecting a stuck-at fault by a vector sequence T as:

$$P(T) = 1 - 2^{-E_o T/k} (2.6)$$

where k is the number of lines through a circuit partition where the detectable fault exists and  $E_o$  is the entropy at the output of the circuit. Consider a 2-input AND gate with inputs i1, i2 and output Z. If the probability of logic 0 (logic 1) occurring at the inputs is 0.5 (0.5), the entropies at the inputs, i1 and i2, are:

$$E_{i1} = E_{i2} = -0.5 \, \log_2(0.5) - 0.5 \, \log_2(0.5) = 1.0 \tag{2.7}$$

Therefore, the total information present at the inputs is 1+1 = 2. The probability of logic 0 (logic 1) at output Z is 0.75 (0.25) and the entropy of Z is:

$$E_Z = -0.25 \, \log_2(0.25) - 0.75 \, \log_2(0.75) = 0.811 \tag{2.8}$$

So, the AND gate has information loss of 2.0 - 0.811 = 1.189. Agrawal proposed an ATPG method that reduces the loss (by increasing entropy) of information and maximizes P(T) in the circuit by adjusting the probabilities of 0 and 1 at the inputs. He discusses a way to generate test patterns that increases the information flow in the circuit based on the functionality of the circuit. Since he uses the functionality of the circuit to generate patterns, different implementations of the same functionality can produce different results. By increasing the information flow in the circuit, he is able to detect permanent faults and intermittent faults, faults that become active intermittently.

For sequential circuits, he calculates the information flow on a per pattern basis. Consider a circuit that is designed to perform n operations. Let us assume that the  $j^{th}$  operation requires an input sequence of  $v_j$  patterns and can produce  $m_j$  distinct output sequences. The information output of this operation will be maximum when each of the  $m_j$  output sequences are made equiprobable. Then the average information output of  $j^{th}$  operation is given as:

$$h_j = \frac{\log_2 m_j}{v_j} \text{ bits/pattern}$$

(2.9)

If the probability of executing  $j^{th}$  operation is  $p_j$ , the average information output of the circuit is:

$$H_o = \sum_{j=1}^{n} p_j \times h_j \text{ bits/pattern}$$

(2.10)

In order to generate patterns, first,  $p_j$ 's are assigned to the various operations such that the output information as given by Equations 2.10 and 2.9 is maximized. The pattern generator would then proceed by selecting operations with the assigned probabilities and generating an input pattern sequence for the selected operation. An input pattern sequence is generated from the functional description of the circuit and data patterns are selected to make all possible outputs equiprobable. These patterns are then stored as the test patterns for the circuit.

Thearling and Abraham proposed information theory based testability measures at the functional level [64]. They use relative information and mutual information measures instead of absolute values. They use the *information transmission co-efficient* (InTC) as their testability measure. InTC is defined as a measure of the fraction of information that can be transmitted through a line. It is computed by taking the ratio of the entropy on the inputs of a line and the entropy of the outputs of the line. They use InTC as their controllability measure. For an observability measure, they use the ratio of mutual information of an output with an internal circuit node and the entropy of the output. Probabilities of logic 0 (logic 1), p(0) (p(1)), were estimated either via logic simulation, called *sampling*, or by using functional level information of the circuit components, known as *composition*.

They also proposed partitioning of the circuit, to improve testability, using entropyrelated measures. By partitioning a circuit, increased controllability and observability can be achieved through DFT insertion. When data flows through a circuit, it may be difficult to produce desired values on the inputs of some gates. Similarly, data from gates may not always flow to the outputs. To alleviate this problem, the circuit is partitioned and additional controllability and observability are added. Their basic idea is to use their testability measures to determine the amount of information compression occurring in a circuit and then to use that knowledge to perform partitioning of the circuit. They provide an algorithm to effectively partition the circuit. The basic premise of the partitioning algorithm is to first push the limits of the partition until signal paths have a controllability less than the desired threshold. The partition limits are then pulled back until each path in the partition has an observability greater than than the desired threshold. This is repeated until the entire circuit has been partitioned. Their results show that partitions with higher values of controllability and observability threshold achieve higher fault coverages.

From the above mentioned work, it is clear that the advantage of using entropy, rather than conventional testability measures, is that it can be reliably calculated using a limited number of simulation vectors and it is a single metric that accurately reflects the information flow in the circuit.

## 2.2 Partial Scan

## 2.2.1 Designing Circuits with Partial Scan

Agrawal *et al.* [2] discuss two methods of selecting flip-flops for scanning. In this scan design methodology, only selected faults are targeted for detection. The targeted faults are those not detected by the functional vectors and the test generator decides exactly which flip-flop to scan using one of the two ways. By using partial scan, they achieve 40% savings over the full scan overhead while using comparatively fewer test vectors to obtain similar fault coverages.

In the first method known as the Frequency Approach, all of the possible tests are generated for each targeted fault and then the test vectors that require the fewest flip-flops to be scanned are selected. This approach uses a modified *path oriented decision making* (PODEM) test generation program [25] to generate all possible tests for the targeted fault by only setting inputs that are needed to be set while leaving all other inputs as "don't care's." The fault and corresponding vectors are analyzed to obtain a minimal set of vectors that covers the maximum faults but requires fewer flip-flops to be scanned. This is done by selecting vectors that detect hard-to-detect faults and removing all the faults that get detected by these vectors from the fault list. The flip-flops required by these vectors are scanned. Then the flip-flops with higher frequency, are selected for scanning.

The second approach is the Distance Approach, which generates only one test per fault. The test vectors are generated by setting the *primary inputs* (PI) nearest to the fault site and propagating the fault to the nearest *primary outputs*  (PO). In the distance approach, all the PIs and POs are assigned 0 distance, while combinational logic whose inputs and outputs are derived from flip-flops is set to a distance value of 100. Once a flip-flop is scanned, these inputs and outputs get a distance value of 0.

They also provide an option table to the designer for each approach suggesting the fault coverage that can be obtained by selecting a certain percentage of flipflops. So, the designer will have a choice of selecting the number of flip-flops that he needs to scan to obtain the desired fault coverage.

They achieve fault coverages comparable to full scan, but by only scanning a smaller percentage of flip-flops for the same circuit. The total vectors required for partial scan are less than half compared to full scan for some circuits. The frequency approach fares better than the distance approach as they obtain an optimized set of test vectors for the targeted faults. But, the test generation time for the frequency approach can be very high for big circuits as multiple vectors are generated for each fault. They also do not provide the test generation time for either of the approaches. They use PODEM [25] for test generation, which is an outdated algorithm and better test generation algorithms have been developed since.

# 2.2.2 An Exact Algorithm for Selecting Partial Scan Flip-Flops

Chakradhar *et al.* [12] develop an exact algorithm for selecting flip-flops in partial scan design to break all feedback cycles. They make use of graph transformations, partitioning schemes and *integer linear programming* (ILP) to develop their algorithm, which performs well on the ISCAS '89 benchmark circuits and several production VLSI circuits within reasonable computation time.

Their main idea in this algorithm is to cut all of the feedback paths except selfloops present in a circuit as proposed previously by Cheng and Agrawal [14] and Gupta and Breuer [27]. For this they model the circuit as a directed graph called the *S-graph* with the flip-flops in the circuit as vertices and the arcs (or edges) connecting the vertices modeling the combinational logic present in the circuit. The problem of selecting flip-flops to break all feedback cycles is equivalent to the problem of finding a set of vertices whose removal makes the S-graph acyclic. The vertex set is referred as the *minimum feedback vertex set* (MFVS) and this problem is an NP-hard problem. But, by using an MFVS-preserving graph transformation that defines a new class of graphs, they solve the problem in polynomial time complexity.

They propose three graph transformations that are MFVS-preserving. If there exists an arc from  $(v_i \rightarrow v_j)$ , then  $v_i$  is the predecessor of  $v_j$  and  $v_j$  is the successor of  $v_i$ . Let  $remove(v_i)$  denote the process of removing all incoming and outgoing arcs of vertex  $v_i$ . The three transformations are as follows:

- T1: If v<sub>i</sub> has a self-loop then remove(v<sub>i</sub>) from the s-graph and return v<sub>i</sub>.

A MFVS for the S-graph is obtained by adding v<sub>i</sub> to any MFVS of the modified graph.

- **T2:** If  $v_i$  has either indegree or outdegree equal to 0 then  $remove(v_i)$  from the s-graph. The MFVS's of the S-graph and the modified graph are identical.

- **T3:** If  $v_i$  has either indegree or outdegree equal to 1 but no self-loop then  $ignore(v_i)$ , which connects each predecessor of  $v_i$  to all its successors,  $re-move(v_i)$  and collapses multiple arcs (if any) into a single arc. Any MFVS of the modified graph is an MFVS for the S-graph.

Each of these transformations will remove one vertex and they are applied to the S-graph until no more transformations are applicable. If these transformations reduce the S-graph to an empty graph, then this S-graph is called a *two-way reducible* graph and the MFVS can be determined in polynomial time complexity. If an S-graph is not two-way reducible then its MFVS can be computed in polynomial time, and it is classified as *scc-compressible*. If the S-graph is not scc-compressible then these transformations will reduce it to a final graph containing one or more *strongly connected components* (SCC). An SCC that cannot be further reduced is called a *compressed scc*.

The branch-and-bound partitioning scheme is used when the above transformations cannot reduce the graph completely. A Boolean variable  $x_i$  is assigned to each vertex  $v_i$  in the graph. For any assignment of 0-1 values to the Boolean variables, they construct a vertex set that includes only those vertices for which the corresponding Boolean variables assume the value 1. The 0-1 assignments that correspond to feedback vertex sets are called feasible solutions and the rest are infeasible solutions. The branch-and-bound procedure systematically searches the space of all 0-1 vectors for an optimum solution corresponding to the MFVS. This way the graphs that cannot be reduced by graph transformation are converted into vertex clusters using branch-and-bound partitioning.

The MFVS for the compressed SCCs is found by formulating the problem as an *integer linear program* (ILP). Weights  $w_i$  are associated with each  $v_i$  and start with the requirement that for every arc  $(v_i \rightarrow v_j)$ ,  $w_i - w_j \ge 1$ . But for feedback loops, this will not be true. Hence they add n to the weight of  $v_i$  where n is the number of arcs in the longest cycle. Now the requirement can be expressed as: for every arc  $(v_i \rightarrow v_j)$ ,  $w_i - w_j + nx_i \ge 1$ . Here  $x_i$  is a Boolean variable associated with  $v_i$  and is set to 1 whenever  $v_i$  is on a cycle. Now to find an MFVS, it suffices to minimize  $\sum x_i$ .

They compare their results with Lee and Reddy [41], PASCANT [6] and OPUS [17]. They compute optimal solutions for large circuits in ISCAS '89 benchmarks in less than a minute while the other methods only produce sub-optimal solutions. They also provide results for three production VLSI circuits. But, they do not show the results for the fault coverage obtained, which is the basic metric to compare the quality of the algorithms. Moreover, breaking the feedback loops present in a circuit alone is not enough to ensure that the overall testability of the circuit is increased.

# 2.2.3 Partial-Scan Design Based on Circuit State Information and Functional Analysis

Xiang and Patel [70] present a multi-phase flip-flop selection approach that breaks critical cycles and selects flip-flops based on conflict resolution. Critical cycles are broken using a combination of valid circuit state information and conflict analysis. Circuit state information is obtained using logic simulation and is updated after selection of a few flip-flops for scanning. Valid-state-based testability measures and conflict-based testability measures are presented in this work.

The definitions and notations provided by them to understand their work better are as follows:

#### **Definition 1:**

A state for a fault-free circuit is an assignment of Boolean values  $\{0, 1\}$  to the output values of the flip-flops. The reset state is a state that can be reached from any state of the circuit.

#### **Definition 2:**

A state is called a *valid state* if it is reachable from the reset state; a state is called an *invalid state* if it is not reachable from the reset state. Let  $v_1, v_2, ..., v_n \in \{0, 1\}$ ,  $i_1, i_2, ..., i_k \in \{1, 2, ..., n\}$  and  $k \leq n$ . Assume that a state is an *n*-tuple, where n is the number of flip-flops in the circuit, and a partial state  $(v_{i_1}, v_{i_2}, ..., v_{i_k})$  is called a partial invalid state if the corresponding state is invalid. State mapping maps a state to all of the cycles in the circuit, where each cycle contains a subset of circuit flip-flops.

#### **Definition 3:**

The vertices of the directed s-graph of a sequential circuit are the flip-flops of the circuit. There is an edge  $(v_m, v_n)$  in the s-graph if there is a combinational path from flip-flop  $v_m$  to flip-flop  $v_n$ .

#### **Definition 4:**

The density of encoding of a circuit is defined as  $\frac{V}{2^n}$ , where n is the number of flip-flops in the circuit, and V is the number of valid states in the circuit. The number of valid states V for a circuit with n flip-flops is usually much less than  $2^n$ . When  $\frac{V}{2^n}$  is much less than 1, the test generator may frequently justify invalid states. An invalid state indicates that backtracks are needed.

#### **Definition 5:**

A conflict is defined as follows: A line l is assigned value v. In the previous process of test generation, l needs to be assigned the value v'. If the intersection of v and v' produces a value in the logic system, line l is assigned value  $v \cap v'$ ; otherwise, a conflict occurs on l.

The conflict measures are calculated for the circuit using:

- i Controllability, C(i), of a node l, which is the potential number of conflicts and the number of clock cycles required in order to justify a signal requirement (l, i), where  $i \in \{X, 0, 1\}$ .

- $v Observability, O_A(v)$  ( $v \in \{D, \overline{D}\}$ ), reflects the number of conflicts or the number of clock cycles required to propagate fault effect v along the *easiest fault effect propagation* (EFEP) path.

These were adapted from their previous work [72], which gives a clear explanation on how the conflict analysis is done.

The valid state analysis is performed by logic simulating the circuit from either a reset state (if known) or by having all of the flip-flops in the unspecified state. Then, the number of  $0 \rightarrow 1$  and  $1 \rightarrow 0$  transitions for two continuous valid states is observed for each flip-flop. With the results from this analysis, they conclude that if a circuit has many flip-flops that do not transition much and if a circuit with cycles has few valid states, then the testability of the circuit is poor. Based on the valid state and conflict analysis, they define a new testability measure T(f, c) and testability improvement potential (TIP), which gives the improvement obtained by scanning a flip-flop. The summation of TIP with the controllability and observability values for each flip-flop is adopted for scan flip-flop selection.

They achieve high fault coverages on the ISCAS '89 benchmarks. They compare their results with OPUS [17] and COP [49], which use partial scan designs, ZSCAN [54], OPSCAN [69] and SDSCAN [20], which are implemented using valid state information, and SAMSON [34], which uses the implicit state enumeration method. They achieve better results than all of these algorithms on most of the ISCAS '89 benchmarks.

# 2.2.4 SPARTAN – A Spectral and Information Theoretic Approach to Partial-Scan

Khan *et al.* [35, 36] propose a greedy algorithm that analyzes the *circuit-undertest* (CUT) and selects *scan flip-flops* (SFFs) using three measures: spectral analysis of the flip-flop oscillations, entropy from information theory, and logic gate circuit level information to measure observability and controllability. They use the spectral analysis and entropy combination because spectral analysis incorporates only functional information and does not use any structural information of the CUT. The experimental results show that they achieve very high fault coverages comparable to full-scan designs.

To select flip-flops for scanning, they construct an s-graph from the circuit with each node as a flip-flop. They condense this s-graph to contain nodes that are only SCCs. They propose a two-step approach to select flip-flops for scanning:

- Step 1: Calculate correlation coefficients using spectral analysis and select flip-flops based on this information.

- Step 2: Calculate entropy information passing through each flip-flop and select flip-flops based on this entropy analysis

The final set of scan flip-flops is selected by combining the sets of candidates obtained by spectral analysis and entropy analysis.

The spectral analysis first logic simulates the circuit with random vectors. Spectral coefficients (SCs) are calculated based on the logic simulation values for each flip-flop and PO using the 16 × 16 Rademacher-Walsh transform (RWT). These coefficients describe the controllability of the flip-flop. The  $SC_{i\_avg}$  is calculated for each flip-flop and PO using the following equations:

$$SC_{i\_avg} = \frac{\sum_{i=1}^{k} w_i \times |SC_i|}{k}$$

(2.11)

$$w_i = \frac{\varphi_i + 1}{\sum_{j=1}^k (\varphi_i + 1)}$$

(2.12)

where  $\varphi_i$  is the sequency of a transform matrix row, which represents the number of  $1 \rightarrow -1$  and  $-1 \rightarrow 1$  transitions in a matrix row;  $|SC_i|$  represents the SC of each row; and k represents the number of rows in the matrix. If  $SC_{i\_avg}$  of a flip-flop and any of the POs in its fanout cone are equal, then the flip-flop is considered to have good observability. The flip-flops that have poor observability and have lower  $SC_{i\_avg}$  than an SC Threshold are marked for scanning. Then, the largest SCCs in the condensed graph are selected and flip-flops in these SCCs that are marked for scanning are scanned. This ensures that the cycles in the circuit are also broken. The number of flip-flops that are scanned is limited to 25% of the total number of flip-flops present in the circuit.

The entropy analysis logic simulates the circuit with random vectors to compute p(0) and p(1), which are the probabilities of a flip-flop being 0/1, respectively. The entropy H(Q) and average conditional entropies H(D|PI) and H(Q|PO) are:

$$H(Q) = -(p(0)\log_2 p(0) + p(1)\log_2 p(1))$$

(2.13)

$$H_{avg}(D|PI) = \frac{\sum_{x=1}^{p} H(D|PI_x)}{p}$$

(2.14)

$$H_{avg}(D|PO) = \frac{\sum_{x=1}^{q} H(D|PO_x)}{q}$$

(2.15)

where p is the number of PIs in the fanin cone of the flip-flop and q is the number of POs in the fanout cone of the flip-flop. Now for each SCC, a flip-flop is scanned and the entropies are updated. Flip-flops that give the maximum improvement to the entropy of the SCC are scanned. Experimental results show that SPARTAN performs better than the previous best result of MPSCAN [70] on all ISCAS '89 benchmark circuits. They achieve higher fault coverage with lower test volume than MPSCAN. But, they achieve this at the cost of scanning more flip-flops than MPSCAN.

### 2.2.5 Other Partial Scan Algorithms

A variety of partial-scan design methods have been developed to improve the fault coverage obtained by *automatic test pattern generators* (ATPGs). They can be classified into the following three categories: structure-based [4, 12, 13, 14, 16, 27, 40, 41, 51, 61], testability-measure based [1, 7, 16, 33, 34, 38, 49, 51, 54, 66, 71], and test-generation-based methods [29, 42, 43, 50, 60].

Cheng and Agrawal [14] proposed a structure-based method in order to break cycles and reduce sequential depth for the first time. They pointed out that test generation complexity may increase exponentially with the number of cycles present in the circuit and linearly with the sequential depth. Algorithms were presented to break cycles and reduce the sequential depth. Gupta and Breuer [27] presented a structure-based method that requires only combinational test generation and attains complete coverage of all detectable faults. Scan flip-flops are selected in such a way that the resulting kernel belongs to a so-called *bal*anced sequential structure (B-structure), test generation of which can be treated as that of combinational logic. Jiang et al. [32] proposed a novel method to reduce the length of the synchronizing sequences by scanning several flip-flops of the sequential machines. Trischler [66] introduced a simple testability measure to select scan flip-flops, which is the first testability-analysis based partial-scan design method. Parikh and Abramovici [49] presented a partial-scan design based on a simple testability measure. The testability measure represents the number of clock cycles required to activate, propagate or detect a fault. Abramovici *et al.* [1] selected partial-scan flip-flops by untestability analysis. Many methods have been introduced to reduce test application time. Narayanan et al. [47] proposed an optimal k-scan chain configuration using dynamic programming, which can

get an optimal solution in  $O(k \cdot N^2)$  (N is the number of scan flip-flops).

### 2.3 Test Point Insertion in Non-Scan Designs

# 2.3.1 Self-Driven Test Structure for Pseudo-random Testing of Non-Scan Sequential Circuits

Muradali and Rajski [46] introduce a self-driven test point structure that permits at-speed, on-chip, non-scan, sequential testing using parallel pseudo-random test patterns applied only to the primary inputs of the circuit-under-test. The test network is unique in that aside from a test mode flag, all I/O signals needed for test system operation are tapped from within the circuit itself. They achieve high single stuck-at fault coverage for a number of ISCAS '89 benchmarks. This is the only paper to come out on non-scan *built-in self-test* (BIST) with test point insertion.

The testability measure they use is based on probability analysis of gate I/Os obtained after logic simulation. They analyze the fault-free information local to a circuit line, which can be used to quickly recognize regions that might hinder fault detection. The observability is estimated using the sampled  $OL_i$ , which is the probability that the bit value, i, at that gate input is observable at the gate output, obtained from a circuit tracing method similar to STAFAN [31]. Observability point candidates are selected by calculating observabilities of each gate as a weighted sum of the products of local observabilities evaluated along each combinational path backtraced from the output of a gate toward its inputs. That is, such a path concludes when a flip-flop is reached. Observabilities are calculated for every time frame by backtracing paths that start from each flip-flop encountered in the previous time frame. Therefore, the upper bound on the number of time frames is equal to the sequential depth of the longest path. Since sequential loops can exist, the number of time frames per calculation is limited.

Controllability point candidates are accumulated using threshold-driven backtracing techniques in which flip-flops are transparent, given an initial reference switching profile determined using logic simulation. This begins by identifying all lines with a  $OL_i$  value below a user defined block threshold (that is, blocking lines). Next, since the  $OL_i$  at a gate input is influenced by the bias at the other inputs to that gate, for each blocking line, the circuit is backtraced along the most controlling path commencing at the neighbor of the blocking line and terminating when an  $OL_i$  value above a user-defined stop threshold is reached. The backtrace may also begin at lines that switch below a threshold rate. For each backtrace, the appropriate controllability point can be determined by the start gate and the number of inversions encountered.

The most interesting part of their work is their self-driving test-point structure, which does not need any external input to drive it. This is done by extracting candidate test-point source lines from circuit regions suspected to be uncorrelated to the activity of the respective test points and connecting these source lines to the corresponding control points. They achieve high stuck-at fault coverage for all the ISCAS '89 benchmarks and the results show that this BIST scheme outperforms their *automatic test pattern generator* (ATPG) method. But, they assume that all flip-flops are initialized and do not include the area overhead due to the initializing hardware into their calculations.

# 2.3.2 Non-Scan Design-for-Testability Techniques for Sequential Circuits

Chickermane *et al.* [18] introduce a new technique of parallel loading of flip-flops in test mode for enhanced controllability combined with probe point insertion for enhanced observability. Selection of candidate flip-flops and probe points is done by their tool, OPUS-NS, which is their previous work. They achieve fault coverages higher than 96% and ATPG effectiveness improvement greater than 99.7%. ATPG effectiveness is the percentage of faults either detected or proven to be untestable within the gate-level logic simulation constraints. Their work is not fully focused on test point insertion but has good results.

Flip-flop selection is based on cycle cutting and SCOAP [26] measures. After fault simulation, observation points are inserted based on information from hardto-detect faults. Another alternative to their method is to do fault simulation first and then target flip-flops based on hard-to-detect faults. But they have dealt only with their former idea in this paper.

Parallel loading of flip-flops means that the inputs of those flip-flops that are scanned will be directly connected to the PIs in test mode and hence they have an upper bound of scanning only as many flip-flops in a circuit as the number of PIs. For enhancing the controllability of the circuit, some flip-flops are selected to be scanned depending upon the criteria that they help in cutting cycles in the circuit and based on SCOAP measures. They calculate a variable called *profit* depending upon the improvement of SCOAP values of a circuit by scanning a flip-flop and select those with high profit. They do not provide a clear idea on an *observability point* (OP) selection procedure but propose two schemes to reduce pin overhead due to the OP insertion. One is to use XOR gates to compress their outputs into one pin and the other is to connect the outputs of these points to POs making only one of the POs or OPs observable at any given time.

They use HITEC [48] for test generation and obtain high fault coverages for selected ISCAS '89 benchmarks and achieve high improvements in HITEC performance. But, their parallel load scheme requires as much hardware as normally scanning the flip-flop and does not provide any better results. Their results are beaten in the paper discussed next.

# 2.3.3 Non-Scan Design for Testability for Synchronous Sequential Circuits Based on Conflict Resolution

Xiang et al. [72] propose a non-scan design-for-testability method for synchronous sequential circuits. A testability measure called *conflict* based on conflict analysis in the process of synchronous sequential circuit test generation is introduced. Reconvergent fanouts with non-uniform inversion parity are still one of the main causes of redundancy and backtracking in the process of sequential circuit test generation. A new concept called *sequential depth for testability* is introduced to calculate the conflict-analysis-based testability measure. Potential conflicts between fault effect activation and fault effect propagation are also checked because they are closely related. The testability measure estimates the number of potential conflicts to occur or the number of clock cycles required to detect a fault. The non-scan design for testability method based on the conflict measure can reduce many potential backtracks, make many hard-to-detect faults easy-to-detect and make many redundant faults testable; therefore, it can greatly enhance the fault coverage of the circuit. It is believed that non-scan design for testability using the conflict measure can improve the actual testability of a circuit. They present extensive experimental results to demonstrate the effectiveness of the method.

Some definitions are provided in their paper that will help one to understand the calculation of *conflict* measures,

#### **Definition 1:**

A conflict is defined as follows: A line l is assigned value v. In the previous process of test generation, l needs to be assigned value v'. If the intersection of v and v' produces a value in the logic system, line l is assigned value  $v \cap v'$ ; otherwise, a conflict occurs on l.

#### **Definition 2:**

Inversion parity of a path is defined as the number of inversions in the path modulo 2. Inversion parity  $inv_v(B, A)$  ( $v \in \{0, 1\}$ ) from node A to B is defined as a two-bit binary number with these meanings:

- 00 if there is no path from A to B or no signal requirement on node A in order to meet signal requirement (B,v).

- 01 if the easiest way to justify (B,v) passes only a path of odd inversion parity from A to B.

- 10 if the easiest way to justify (B,v) passes only a path of even inversion parity from A to B.

- 11 if the easiest way to justify (B,v) passes at least one path of even inversion parity and one path of odd inversion parity from A to B, respectively.

#### **Definition 3:**

Sequential depth for testability  $seq_v(l, s)$   $(v \in \{0, 1\})$  from a fanout stem s to a line l is defined as the number of clock cycles required to justify a signal requirement (l, v) at the line l to the fanout stems in the easiest way.

The paper provides formulas for calculating  $inv_v(B, A)$  and  $seq_v(l, s)$  for each type of node present in a circuit. The controllability and observability of each line is calculated similar to SCOAP [26] measures but they incorporate the  $inv_v(B, A)$  and  $seq_v(l, s)$  values calculated for each gate into these measures. Then, they choose the lines with hard faults and their immediate successors and predecessors as *test point candidates* (TPCs) on the basis of conflict. The *testability* gain (TG) function is calculated for each candidate from the conflict measures. Then, depending upon the requirement, they insert a 1-controllability point, a 0-controllability point, or an observability point and update the conflict measures. The inputs to controllability points are derived from existing PIs and easy-to-control nodes while taking into consideration the conflicts and reconverging fanouts introduced into the circuit due to this. Exclusive-OR chains are used to drive the observability point outputs to the POs.

They also provide a new test point structure that uses internal lines to drive the test points but, unlike Muradali and Rajski [46], they use extra pins to drive test points in some cases. They implement a system called *nscan* to test the nonscan circuit. They achieve higher fault coverages than OPUS-NS by Chickermane *et al.* [18] and HITEC [48]. Their test volume is higher than HITEC but they claim that this is because they manage to detect hard-to-detect faults, which HITEC does not. They have the best results for test point insertion in a nonscan design.

# 2.4 Test Point Insertion in Full-Scan and Partial Scan Designs

### 2.4.1 Constructive Multi-Phase TPI for Scan-Based BIST

Tamarapalli and Rajski [62] present a novel test point insertion algorithm based on a constructive methodology. They partition the circuit and conduct tests in multiple phases while inserting test points in each phase targeting a specific set of faults. Control points within a particular phase are enabled by fixed values, resulting in a simple and natural sharing of the logic driving them. By inserting a few test points and with a minimal number of phases, they achieve high fault coverages. In each phase, control point candidates are selected using a probabilistic fault simulation technique, which accurately computes the impact of a new control point in the presence of the control points selected so far. Observation points maximally enhancing the fault coverage are selected by a covering technique that utilizes the probabilistic fault simulation information.

Their BIST scheme contains a phase decoder block. The inputs of the phase decoder are driven by a pattern counter, which is part of the BIST controller. The

outputs of the phase decoder, which indicate the current phase in progress, drive control points inserted in the combinational logic. Given the number of phases N, the phase decoder block can be synthesized with the number of outputs ranging from  $\lceil \log_2 N \rceil$  to (N-1) based on the constraints on routing and area overhead. In each phase, a set of control points is enabled by the phase decoder outputs and a specific number of patterns is applied. Each phase thus facilitates detection of a specific set of faults and contributes to the fault coverage obtained so far.

For every phase from 0 to (N-1), probabilistic fault simulation is performed to determine, for each node in the circuit, the list of faults that propagate to it, along with the associated detection probabilities. The conditional probability of a D or  $\overline{D}$  occurring at an output when the inputs are  $\{0, 1, D, \overline{D}\}$  is calculated for each node in the circuit. The node that offers a higher improvement to the testability of the circuit is selected as the control point candidate. The formulas for the probability calculation are given in the paper.

The observability point candidates are selected such that detection probability of a maximum number of faults meets a user specified threshold DTh. A three step process explained below is followed to achieve this objective.

- 1. Probabilistic fault simulation is performed to determine the propagation profile. This information is represented internally as a sparse two-dimensional matrix  $T_{M\times N}$ , with the collected nodes as rows, undetected faults as columns, and the probability of detecting a fault j, at a node i, as entry T[i.j]. The problem of selecting a pre-specified number of observation points now becomes equivalent to that of selecting the set of rows that maximizes the number of columns satisfying the detection threshold DTh.

- 2. The partial covering  $(PC_j)$  of a column j represents the approximate cumulative detection probability of the corresponding fault at nodes corresponding to the selected rows. A row i is said to cover a column j if  $PC_j < DTh$  and  $PC_j + T[i, j] \ge DTh$ . Let  $W_i = \sum_{j=1}^{N} max(0, min((DTh PC_j), T[i, j]))$  denote the weight of a row i, where i = 1 to M. The selection

of rows is performed iteratively and in each step, the row that covers the maximum number of columns is selected. When two or more rows cover the same number of faults, their weight function is used to select them. This selection process continues until a pre-specified number of observation points are selected or no observation point meets the minimum-benefit-per-cost criterion.

3. Following the completion of the selection process, an improvement of the set of selected rows is performed. Since the selection of a row at iteration *i* does not consider the effect of rows selected in subsequent iterations, the final number of columns covered by such a row could be less than the number of columns covered by it at the point of selection. Hence, the selected row that covers the least number of columns at the end of the selection process is returned and the partial cover of affected columns is changed accordingly. The best unselected row is then determined. The returned selected row is replaced by the best unselected row, if it covers fewer columns than the latter.

The advantages of their method are its ability to converge, due to partitioning, and increased accuracy in predicting the impact of multiple control points, due to the usage of fixed values. In addition, the number of ineffective control points is reduced, since conflicting control points are enabled in different phases. They achieve optimal or near optimal fault coverage for large benchmark circuits with only few phases. But, the disadvantage with their method is that they need to fault simulate for every phase and this would increase the design time for large circuits if the fault simulation takes longer.

# 2.4.2 Timing-Driven TPI for Full-Scan and Partial-Scan BIST

Cheng and Lin [15] introduce a gradient-based approach to estimate the random pattern testability improvement factors for the test point candidates of either fullscan based or partial-scan based BIST. They also propose a symbolic computation technique to compute testability for circuits under the partial-scan based BIST scheme. They use a greedy approach to select one test point at each iteration. The selection is based on a cost function that comprises the profit of global random pattern testability and the penalty of timing. Timing analysis is done to determine the slack available in each node as the candidate test points can only be at the cell boundaries but not inside the cells as they could disrupt the timing of the chip.