# Architecture Validation of VFP Control for the WiNC2R Platform

BY AKSHAY JOG

A Thesis submitted to the

Graduate School -- New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Prof. Predrag Spasojevic

and approved by

New Brunswick, New Jersey

October, 2010

# © 2010

# AKSHAY JOG

# ALL RIGHTS RESERVED

## **ABSTRACT OF THE THESIS**

# Architecture Validation and Characterization of VFP for WiNC2R Platform

## Akshay Jog

## Thesis Director: Prof. Predrag Spasojevic

A Cognitive Radio processing requires intelligent transceiver which can be easily programmed and reconfigured dynamically to support multiple protocols. The Winlab Network Centric Cognitive Radio (WiNC2R) platform is based on the concept of Virtual Flow Pipelining Paradigm. WiNC2R can support per packet protocol adaption through the reconfiguration of function sequencing. Since WiNC2R platform can be programmed by adding additional functions in software, and flow sequencing reprogramming architecturally supported in hardware, it can easily support future protocols. The latest version of WiNC2R has advanced shared VFP control unit, cluster based SoC architecture with all the processing engines in an 802.11a like OFDM transmitter flow.

It is very important to characterize the VFP overhead with the realistic protocol processing examples to understand the performance and cost penalties of added flexibility, and establish the base for the comparison with Software Defined Radio approach. The performance analysis of the VFP will give detailed insight about the various latencies involved in the VFP processing. VFP Architecture is validated to see that the current implementation does meet the requirements of the WiNC2R platform. This performance analysis will help in characterizing VFP overhead under varying throughput requirements. Architectural validation of VFP will characterize certain parameters of the system programming, like reschedule period, guard time, etc.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisors, Prof. Predrag Spasojevic and Prof. Zoran Milijanic for their constant support, guidance and concern. Despite all their commitments and responsibilities they always gave me time and guided me at every step of my thesis.

I would also like to thank my Parents for their constant support. I would like to thank my team comprising of Onkar Sarode, Madhura Joshi, Mohit Wani and Khanh Le for their support at every point of my thesis. Last but not the least, thanks to Mohnish Kulkarni, Akshay Shetty, Ronak Daya.

| ABSTRACT OF THE THESIS ii                                                   |

|-----------------------------------------------------------------------------|

| ACKNOWLEDGEMENTS iv                                                         |

| 1. Introduction of WiNC2R Platform                                          |

| 2. Overview of Testbench                                                    |

| 2.1 Flat Testbench6                                                         |

| 2.2 Layered Testbench                                                       |

| 2.3 Verification Techniques11                                               |

| 2.4 Verification Methodology Selection12                                    |

| 3. Overview of OVM16                                                        |

| 4. OVM Configuration for WiNC2R Platform25                                  |

| s4.1 OVM Sequence Item for WiNC2R Platform29                                |

| 4.2 OVM Sequence for WiNC2R Platform                                        |

| 4.3 OVM Sequencer for WiNC2R Platform                                       |

| 4.4 OVM Driver for WiNC2R Platform                                          |

| 4.5 OVM Monitor for WiNC2R                                                  |

| 4.6 OVM Scoreboard for WiNC2R40                                             |

| 4.7 OVM Test for WiNC2R                                                     |

| 5. Constrained Random Stimulus Generation for validating WiNC2R Scheduler44 |

| 6. Performance Analysis of VFP overhead55                                   |

| 7. Conclusion                                                               |

| 8. Future Work                                                              |

| References                                                                  |

## **Table of Contents**

## **Table of Figures**

| Figure 1: WiNC2R Platform (4)                       | 2  |

|-----------------------------------------------------|----|

| Figure 2: Generic Testbench (6)                     | 5  |

| Figure 3: Layered Tesetbnech (6)                    | 8  |

| Figure 4: OVM Class Hierarchy (5)                   | 18 |

| Figure 5: OVM Based Verification Environment (11)   | 20 |

| Figure 6: AXI Write Channel Signals                 | 27 |

| Figure 7: AXI Write Burst Transaction (3)           |    |

| Figure 8: SYNC and ASYNC Task Queue Descriptor (18) | 44 |

| Figure 9: TD Table Format (18)                          | 47 |

|---------------------------------------------------------|----|

| Figure 10: GTT Table Format (18)                        | 47 |

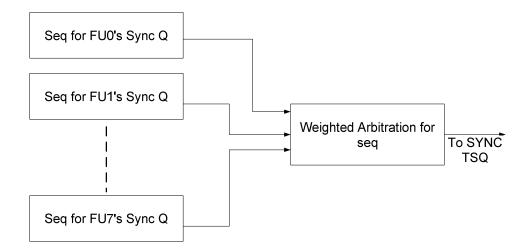

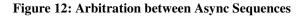

| Figure 11: Arbitration between Sync Sequences           | 52 |

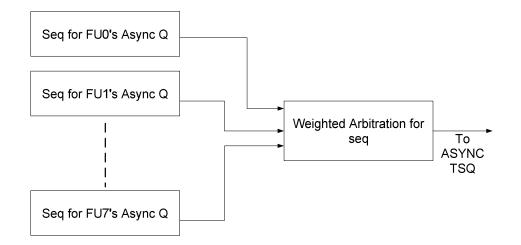

| Figure 12: Arbitration between Async Sequences          | 53 |

| Figure 13: Arbitration between Async and Sync Sequences | 53 |

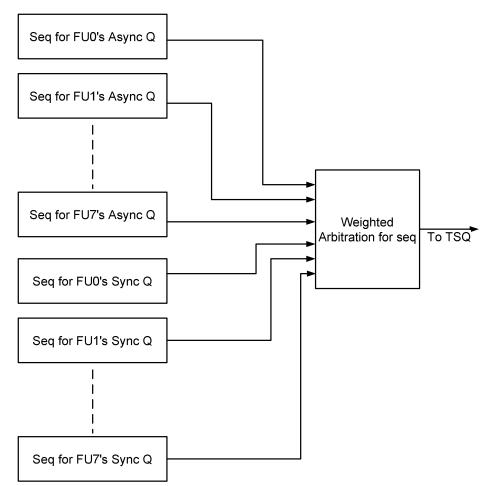

| Figure 14: Producer Consumer Interaction in WiNC2R      | 55 |

#### 1. Introduction of WiNC2R Platform

The Winlab Network Centric Cognitive Radio (WiNC2R) is Cognitive radio platform (1). WiNC2R is also a software programmable platform which can provide necessary flexibility in hardware for various protocols. The WiNC2R platform is based on the concept of Virtual Flow Pipelining Paradigm (2). WiNC2R can support per packet protocol adaption through the reconfiguration of function sequencing. Since WiNC2R platform can be programmed by adding additional functions in software, and flow sequencing reprogramming architecturally supported in hardware, it can easily support future protocols. The latest version of WiNC2R has advanced shared VFP control unit, cluster based SoC architecture with all the processing engines in an 802.11a like OFDM transmitter flow.

The traditional hardware pipelined system has a fixed set of operation, fixed operations at each stage of the chosen operating mode and fixed timing of operation which is end to end processing latency. Multiplexing of functional units is also not possible in traditional pipeline based system. VFP processing allows flexibility with respect to each design dimension described above. VFP processing also allows software defined functions to be incorporated into the VFP based program control framework (2). Since the system is not hardwired system, where block1 gives output to block2 and block2 gives output to block3 and so on, WiNC2R provides flexibility in hardware so that processing engine1 can give its output to processing engine4 as per the requirement. This provides flexibility for transferring data from any processing engine to any other processing engine unlike hardwired system. This flexibility allows flow of traffic to be configured at run time.

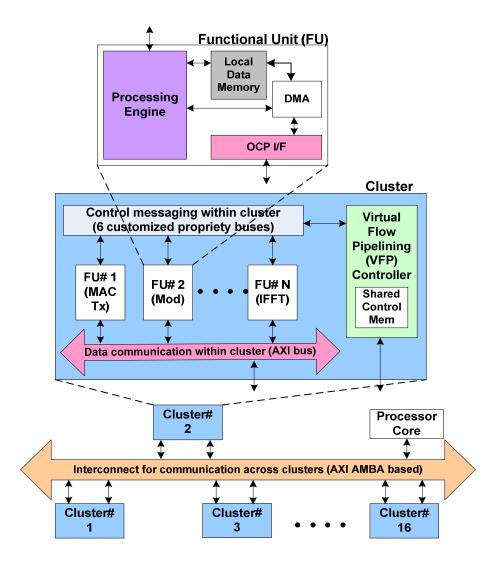

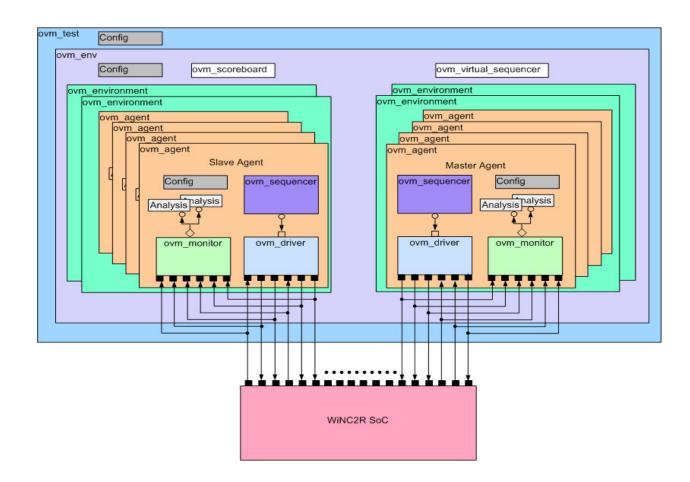

Figure 1 shows the current WiNC2R platform implementation. As shown in the Figure 1, the WiNC2R platform is a cluster based SoC having AMBA AXI bus as main system interconnect (3). Every cluster is connected to main system interconnect via AXI bus. Each cluster consists of

many functional units and a VFP controller. Every functional unit has a single processing engine. Current implementation of WiNC2R has processing engines (PEs) like Header, Modulator, IFFT, scrambler etc to support 802.11a like OFDM transmitter flow. All functional units communicate with each other, over the local AXI bus. All the data

Figure 1: WiNC2R Platform (4)

transfers between functional units occur on AXI bus. VFP controller is also connected to local AXI bus. All the communication between VPF and functional units (FUs) for control messaging occurs on local bus as shown in Figure 1. As shown in Figure 1, functional unit consists of PE, local data memory, Direct Memory Access (DMA) engine and interface to access the local and

AXI bus. The local data memory present is FU is used by PE for processing the data and for storing the processed data. The data to be processed by PE is placed in Input Buffer, and processed data is stored in Output Buffer. DMA engine is responsible for transferring the data from Producer Output Buffer to consumer Input Buffer.

VFP controller is responsible for following tasks

- 1. Dynamic Scheduling of Tasks

- 2. Task Activation

- 3. Next Task Processing

- I. Consumer Identification

- II. Data transfer initiation between producer and consumer

Consider one producer PE has finished its processing and it has stored the processed data in its Output Buffer. This producer PE then sends a message to VFP controller indicating he has finished working on the data and based on the flow, the VFP should initiate a data transfer between producer and consumer. In order to determine which consumer to activate the VFP accesses Next Task (NT) table. When producer PE sends a message to VFP to initiate a data transfer, producer PE sends an NT table pointer. This NT table pointer decides the particular consumer which can change as per the flow. By accessing NT table VFP sends a control message to consumer DMA engine to initiate data transfer between producer and consumer. After DMA transfer is done, VFP does flow graph dependency checks by accessing Global Task Table (GTT). GTT has all the necessary information related to a particular task for a particular consumer has a Task Descriptor (TD) table. TD table has all the necessary information related to the activated task. Essentially TD table has information related to the data size to be processed by PE, the starting address of the Data stored in Input Buffer for processing and the Output buffer pointers, to store the processed data. GTT and TD table has descriptors related to all tasks in the system. NT table has descriptors related to the next task processing. GTT, TD and NT table are backbone of the WiNC2R platform since they have necessary information about the flow graph dependency, next task processing and about the current task to be processed by PE.

Considering the complexity of the system, it is very important to characterize the VFP overhead with the realistic protocol processing examples to understand the performance and cost penalties of added flexibility, and establish the base for the comparison with Software Defined Radio approach. The performance analysis of the VFP will give detailed insight about the various latencies involved in the VFP processing. VFP Architecture is validated to see that the current implementation does meet the requirements of the WiNC2R platform. In order to validate and extract performance from the WiNC2R platform, very powerful verification/ validation environment is needed. In the later chapters, it will be shown that how Open Verification Methodology (OVM) based verification environment can be used to validate the architecture and to extract performance from WiNC2R (5).

## 2. Overview of Testbench

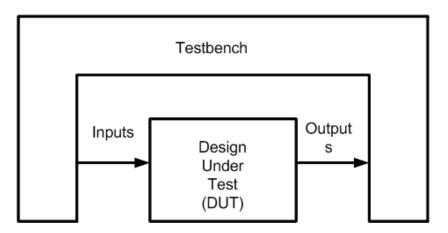

Figure 2: Generic Testbench (6)

Generic testbench wraps around the Design Under Test (DUT) as shown in the Figure 1. The testbench has to work over wide range of the levels of abstraction, sequences and transaction to verify the DUT under various scenarios. The basic testbench functionality is as follows

- 1. Generate Stimulus

- 2. Apply stimulus to the DUT

- 3. Capture the response

- 4. Check for correctness

- 5. Measure progress against the overall verification goals

Testbench consists of various Bus Functional Models (BFM). For DUT, BFMs are real component, but these BFMs are part of the testbench. Consider the Advance Microcontroller Bus Architecture (AMBA) bus as DUT (3). To verify the functionality of the AMBA bus, real components connected to bus are not required. BFMs will be used in place of the real components which will comply with AMBA protocol. BFMs will be designed to meet the functionality of the

real component. BFMs are not required to be synthesizable unless prototyping is done on FPGA or emulations (6).

#### 2.1 Flat Testbench

Consider DUT is a generic bus. A basic testbench to verify the generic bus will look like following

module test\_AMBA (addr, write, read, data, rst, clk, grant, req);

//port declarations and wiring ......

initial begin

rst = 0; // initializing the reset to zero

clk=0; // initializing the clock to zero

#40 rst=1; // assigning reset to 1, this will pull out the DUT from reset

#20; // wait period of 20 time units

//To write on Bus, address , data, control bits needs to be enabled or driven

addr=32'h40;

write=1;

data=32'h100;

req=1; // driving request to one

wait(grant==1) // waiting on grant from bus

• • • • • • • • • •

end // end of the initial begin

#### always

#10 clk= ~ clk; // clock generation

#### endmodule

The Advantages of Flat Testbenches are

- 1. Easy to write

- 2. Rapid Development of basic testbench

#### Disadvantages of Flat Testbench

- 1. Without grouping of similar transaction into task and functions, the Testbench is not reusable

- 2. All the testcases are written manually implying more probability of error

- 3. Only limited testcases can be executed which will not cover wide range of the input combinations

- 4. Constrained-random stimuli are not generated in the flat Testbenches. Constrainedrandom stimuli help in finding the bugs at a faster rate

- Process of verification using flat Testbenches, converges slowly in terms of meeting verification goals. This can affect the product launch, implying loses to the company, considering the competition in the market

- 6. No automation is provided to check the correctness of the results and to generate stimuli

The disadvantages of the flat testbench, dictates the need of the layered testbenches.

#### 2.2 Layered Testbench

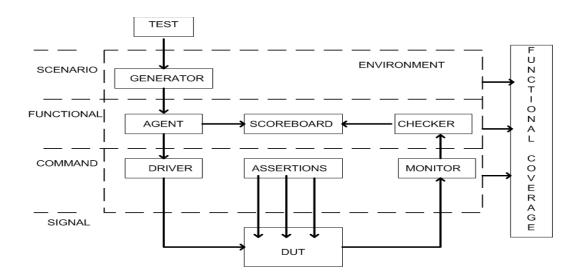

Layered testbench reduces the complexity of the verification process to the manageable pieces. Transactors provide a useful pattern for building these pieces. With appropriate planning, testbench infrastructure can be built which will be shared by all tests and does not have to be continually modified as per the tests. Building the layered testbench will take longer time than flat testbenches, but the paybacks are very high in long run. Due to layered approach, the designing of testbench can be broken down to different layers which can be designed by different teams simultaneously. Different layers are also broken down to different blocks (Transactors) to make reusable, self contained blocks. Figure 3 shows the layered testbench.

Figure 3: Layered Tesetbnech (6)

Signal layer contains the DUT and the signals connecting it to the testbench. The command layer is next layer. The DUT's inputs are driven by driver which is a command and the responses or the output is captured by monitor. Assertions also cross the command/signal layer as they look at individual signals but look for changes across an entire command. The command layer is specific to the protocol. For example if the DUT is AMBA bus or System connected to AMBA bus, then the driver need to comply AMBA protocol and monitor halso has to follow AMBA protocol in order to monitor the correct transactions. Considering the AMBA based system, the command in

this case is bus read or bus write. The functional layer feeds the command layer. The agent block receives the higher level transaction such as DMA read or DMA write and breaks them into individual commands like bus read or bus write. Agent also gives these commands to scoreboard that predicts the results of the transaction. The checker then compares the commands from monitor with those in scoreboard. The Scenario layer feeds the functional layer. As the name suggests, the function of the scenario layer is to create the scenario for DUT so as to stress the DUT to the boundaries. Consider MP3 player as a DUT which can concurrently play music stored into memory, download new songs, respond to user input like play next song, increase/ decrease volume etc. Consider downloading a music file from internet, involves reading control registers, writing to memory for setting up the download, multiple DMA write transfers for song etc. This is the scenario while downloading a song. Like this various scenarios needs to be executed to verify the DUT. The scenario layer uses constrained-random values for scenario generation. The blocks in each layer are written once during the development for verification infrastructure. During verification process, the functionality is added to these blocks as per the requirement, but the blocks do not change as per the test. The hooks are written in the code so as to change the behavior of the block as per the test without rewriting the block again. The test layer contains the constraints to create the stimulus. The test orchestrates the various scenarios. Functional coverage measures the progress of all the tests in accordance with the verification plan. As per the project requirements, functional coverage criteria changes. Because of varying nature of functional coverage criteria, the functional coverage is not part of layered testbench. Even to run direct tests, the layered testbench or the verification environment does not have to change. Direct tests are written to explore the bugs which were not activated when constrained random stimulus were used. Due to constrained random stimulus functional coverage may saturate to a fixed value. After this point direct testing is required to achieve 100% functional coverage. Functional coverage is a measure of which design features have been exercised by the tests. 100% functional coverage implies all the features of the DUT are verified correctly (6).

If constrained-random stimuli are used, fewer tests need to be written. But with direct testing, verification engineer has to write thousands and thousands of tests. Due to layered testbench, the lower layers that is command, signal, functional remains generic implying reuse of the infrastructure. All the testcases are generated automatically unlike flat testbench. Testcases can be executed automatically for all days of the week and all months of the year. Also due to automatic checking capability of the layered testbench, testcases can be executed for a longer time without human intervention. The complexity of the modern devices dictates the need for an automated, systematic, efficient testbench environment to fix the bugs as fast as possible. To make efficient use of the layered testbench, methodology is required. Selection of appropriate methodology is crucial for the success of the product.

To verify earlier implementation of WiNC2R, Xilinx Bus Functional Model was used to simulate the system. Earlier WiNC2R platform was based on Processor Local Bus (PLB) bus which required using BFMs supporting PLB protocol (7). The Xilinx BFM is like a flat testbench and posses all the disadvantages of the flat testbench. There is need of an automated testbench to verify WiNC2R which can gather data from hardware component and use this feedback to modify the tests being executed (8). BFMs are part of the layered testbench, but they cannot serve the purpose of the entire layered testbench. As shown in figure 2, the driver and monitor are BFMs. But just the driver and monitor does not suffice the purpose of the complex requirements of the verification process. BFMs are in command layer as shown in figure 2. These BFMs are protocol specific as mentioned earlier. So Xilinx BFMs were just following the PLB protocol. Current implementation of WiNC2R is based on AMBA AXI bus requiring new BFMs supporting AMBA AXI protocol (3). AMBA AXI bus was chosen for the current WiNC2R architecture, because of the burst constraint of PLB bus. PLB bus allowed only 64 bytes of data transfer in one burst transaction. In case of bytes more than 64, several burst transactions were required which was creating a bottleneck for system performance. In AXI burst length can go up to 1024 byte (9). Hence to generate constrained-random stimulus, to gather functional coverage information, to have one common testbench for all tests and to keep test code specific separate from testbench, Layered testbench with appropriate methodology is required.

#### **2.3 Verification Techniques**

Verification is a process used to demonstrate the functional correctness of a design (10). Following are three categories in functional verification (11).

- 1. Formal Verification

- 2. Simulation-based Verification

- 3. Acceleration/ Emulation-based Verification

#### 2.3.1 Formal Verification

Formal Verification uses logical and mathematical formulas and approaches to prove or disprove a given property of a hardware implementation. Formal verification operates on equations describing the system and not on test vectors. Any property proved by a formal verification tool holds for all possible test vectors applied to that behavior. Formal verification does not require test vectors to be applied. Also formal verification techniques are able to make universal statements about a property of a design implementation holding for all possible inputs. This technique is useful when the testbench and test vectors are not yet available.

#### 2.3.2 Simulation-Based Verification

As the name suggests, simulations are done for functional verification. The verification environment consists of a testbench and a design. The DUT is put into known current state and based on the output of the current state, DUT is put into next state. The output of current state is checked with the expected outputs. This technique involves the process of consecutively taking the design through different states where the sequence of observed design states corresponds to a verification scenario listed in verification plan.

#### 2.3.3 Acceleration/Emulation-based Verification

Formal and simulation-based verification techniques provide many benefits in the early to middle stages of the design flow. The speed of those techniques falls short, when the entire system along with its application software needs to be verified. In this scenario, the simulation needs to run for millions and billions of instructions so that the macro behavior of the application software can be verified. In this technique design is mapped to configurable platform like FPGA. Since the design is mapped to FPGA, the instructions can run at the desired clock rate of the design, making the execution time shorter. In hardware acceleration, the testbench program is running on host computer. In hardware emulation, stimuli are applied via real world interfaces and verification in general is restricted to monitoring the input and outputs of the DUT. In the hardware acceleration the acceleration is limited by runtime of the testbench on the host computer and the speed of the communication channel between host computer and acceleration platform.

To verify current implementation of the WiNC2R, simulation-based verification technique has been chosen. Most of the processing engines in the current WiNC2R are written in C/ C++ code. These processing engines are not synthesizable. The reason for choosing most of the processing engines in C/ C++ is to evaluate the current architecture for performance, assuming the standard delays involved with the processing engines, so as to check the compliance with 802.11a standard.

#### 2.4 Verification Methodology Selection

Recent statistics show that 60-70 % of the entire product cycle for a complex logic chips is dedicated to the verification tasks. Verification of complex functions that can be built using new tools poses a challenge to reduce the total product time. Designing at a higher abstraction level

allows the designers to build highly complex functions with ease. This increase in the design complexity doubles the verification effort. The increasing size and complexity of designs and shortened time to market window means verification engineers need to verify the more complex and larger designs in a shorter time frame than previous projects (12) (11). Due to such stringent requirement, challenges in verification process increases. Hence selection of verification methodology is very crucial in the success of the product. Efficiency, reusability, and productivity are of at most importance in the verification process. There are many verification methodologies available in the market. Verification Methodology is categorized in to Assertion- Based Verification, Coverage Driven Verification and Metric-Driven Verification. Out these three options, coverage driven verification is chosen. Coverage Driven verification methodology brings the following concepts and approaches.

- 1. Transaction Driven Verification

- 2. Constrained random Stimulus generation

- 3. Automatic Result Checking

- 4. Coverage Collection

- 5. Directed-test- based verification

Layered testbench will provide the necessary infrastructure for the coverage driven methodology. Also for the verification of WiNC2R coverage driven verification methodology

Following are different criteria to choose verification methodology (12) (13).

- 1. Identifying verification goals which will be catered by the Verification methodology

- Evaluate the effect of adapting new verification methodology in terms of tools and learning curve of the team

- 3. Direct and indirect effect of new verification methodology on cost and time to market

- 4. Available support for new verification methodology

- 5. Interoperability with existing in-house tools and methodology and Interoperability with existing Verification IPs (VIP) and new methodology

- 6. Effectiveness of the new methodology in case of various products

- 7. Reusability of infrastructure across different projects

- 8. Ability to quickly provide necessary infrastructure for the verification, considering the verification goals and time to market

- 9. Modularity of the Verification Methodology

- 10. Scalability of the Verification Methodology

- 11. Flexibility of the Verification Methodology

- 12. Predictability of the Verification Methodology

Advance Verification Methodology (AVM) by Mentor Graphics, Universal Reuse Methodology (URM) by Cadence, Verification Methodology Manual (VMM) (14) by Synopsys and Open Verification Methodology (OVM) (15)by Cadence and Mentor Graphics were available methodologies in the market. OVM was available for download from January 2008. Since OVM was joint development between Cadence and Mentor Graphics, options to choose methodology, narrowed down to VMM and OVM. Among OVM and VMM, OVM was chosen as verification methodology to verify WiNC2R. OVM is coverage driven verification methodology which will help in building the layered testbench. Following are the key aspects of OVM (16).

- 1. Open

- 1.1 Written in IEEE 1800 SystemVerilog

- 1.2 Runs on any simulator supporting the IEEE 1800 standard

- 1.3 Verified on Cadence's Incisive and Mentor Graphics' Questa Verification Platform

- 1.4 True open-source license agreement (Apache 2.0)

#### 2. Interoperable

- 2.1 Ensures VIP interoperability across ecosystem & simulators

- 2.2 Enables VIP 'plug and play' functionality for designers

- 2.3 Ensures interoperability with other high level languages

- 3. Proven

- 3.1 Based on Cadence's Incisive Plan-to-Closure Methodology URM Component and Mentor's Advanced Verification Methodology (AVM)

- 3.2 Incorporates Best Practices from >10 years of experiences

VMM Initially was not open. VMM has many flaws compared to OVM (13). VMM is based on old technology. OVM takes full advantage of SystemVerilog and Object Oriented Programming (OOP). VMM 1.1 included many features borrowed from OVM. Many important features of OVM like Transaction Level Modeling (TLM), Factory, set/get\_config methods, automated phasing are not there in VMM. In terms of building and configuring the verification environment, VMM is not as Flexible as OVM. OVM environments are scalable whereas in VMM only one environment can be built. More detailed difference between OVM and VMM are given by Tom Fitzpatrick (13). Hence OVM is the best choice for the validation/verification methodology.

#### 3. Overview of OVM

OVM is an open source, SystemVerilog based class library developed to quickly build objectoriented verification environment. Due to availability of the predefined classes for building verification environment and writing tests allows verification engineers to meet their verification goals sooner with high confidence. The OVM class library objects and classes are defined to implement multi-layered verification environment based on coverage driven methodology. OVM class library features can be categorized as follows

- 1. Creating and managing class objects in the verification environment

- 2. Building and configuring the verification environment hierarchy and managing the simulation runtime phases

- Use of Transaction Level Modeling (TLM) for connecting verification environment blocks

- 4. Generating transaction sequence for verification scenarios

- 5. Provide built in checking support

- 6. Provide facility for reporting and messaging (11) (17)

Following are various verification components used in building verification environment using OVM (11) (17)

Driver: Driver is a verification component which connects to Design Under Test (DUT) via interface. It has transaction level interface to communicate with other transaction level component in verification environment. Driver is just responsible for driving the transactions to DUT. Sequence generation is not done in driver. Driver has to follow a particular protocol to drive the transactions to DUT. Driver receives the transaction on transaction level interface from sequence generator and then by following the protocol driver drives the transaction to DUT. This makes the driver reusable for later projects provided it has to follow same protocol.

Monitor: Monitor is a verification component responsible for extracting signal information at the interface level and translating it into events, data and status information. Coverage and basic protocol checking is also done in Monitor. Monitor can broadcast the information received from DUT to other verification components using TLM which can also act as a feedback in sequence generation.

Sequence: Sequences generate the data items and other sequences (subsequences) which are sent via Driver to DUT. Constrained random stimulus generation is done in sequences. Various complex scenarios can be generated using the sequences.

Sequence Library: A collection of sequences used by sequencer

Virtual Sequence: Any sequence that co-ordinates the activities of other sequences in one or more sequencers is called Virtual Sequence. Virtual Sequences enable centralized data flow control on multiple interfaces.

Sequencer: Sequencer is a verification component that mediates the generation and flow of data between sequences and driver.

Virtual Sequencer: Virtual Sequencer allows a single sequence to interact with multiple sequencers and hence interact with multiple drivers.

Sequence Item: Sequence Item is the transaction generated by sequence, based on the constraints given to sequence item.

OVC: OVM Verification Component is an encapsulated, reusable and configurable verification component for an interface protocol, a design sub-module or a full system.

Bus monitor: Bus monitor is verification component responsible for extracting signal information at bus level and translating it into events, data and status information

Agent: Agent encapsulates driver, monitor, and sequencer. An agent is capable of independent operation. In a verification environment there can be many agents with different behavior. Behavior of each agent is configurable. Consider a case of multiport router verification. In this

case there can be single agent per port of the router. Since the behavior of each agent is configurable, this gives the opportunity to generate real world scenario.

Environment: Environment is top level component of the OVC. Environment can contain one or more agents and top level component such as bus monitor. The environment is also configurable. In a verification environment many environments can exist at the same time each with configurable behavior. Environment is useful in reuse of the verification environment. Environment can configure underlying agent for particular test scenario.

Scoreboard: Scoreboard is a verification component responsible for checking the correctness of the transactions received from DUT. Scoreboard has transaction level interface to communicate with the monitor.

Testbench: Testbench can contain various environments, scoreboards. Testbench can configure the each environment.

Test: Test encapsulates the test specific instructions from the test writer. Test can configure testbench as per the test scenario.

TLM: Transaction Level Modeling interfaces provide a standard method for components to exchange transactions instead of signals. TLM focuses on the transaction and not on the implementation of the components using it.

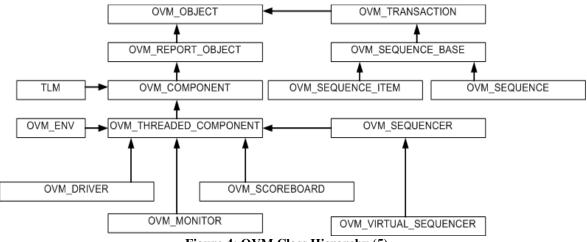

Figure 4: OVM Class Hierarchy (5)

Figure 3 shows the Unified Modeling Language (UML) diagram of OVM class library. Using these predefined classes, OVM based verification environment is built. OVM classes help to build hierarchical class based verification environment which makes it layered testbench. OVM gives the facility to generate constrained random stimulus, to apply the stimulus via driver, to capture the responses via monitor, to check the correctness via scoreboard and to measure the overall progress against the overall verification goals via coverage. The OVM class library and methodology provides all the technology need to implement the reusable constrained random, coverage driven layered testbench. Use of TLM communication as the underlying foundation for connecting verification components facilitates reusability and modularity. OVM based verification environment can be modified on the fly and multiple tests are written from the same base environment with minimal code changes. OVM provides common configuration interface so that all components can be customized on per\_type or per\_instance basis without changing the underlying code. OVM also provides common message reporting and formatting interface (5). In SystemVerilog simulation, time is advanced without any consideration of abstract phases that may exist in verification flow. Progression of time in verification environment is however, managed in phases where different sets of activities take place in each phase. OVM defines such simulation phases. OVM class library provides following built in simulation phase methods (17).

- 1. build ()

- 2. connect ()

- 3. end\_of\_elaboration()

- 4. start\_of\_simulation()

- 5. run ()

- 6. extract ()

- 7. check ()

- 8. report ()

Figure 5: OVM Based Verification Environment (11)

1. build ()

build () is the first phase called automatically for all components in a top-down fashion. Build is a function call and executes in zero time. Build method creates its components child components and optionally configure them. The top-down execution order allows each parent's build () method to configure or otherwise control child parameters before the child component's build () method is executed.Since the build is called in top down fashion, to make sure that build is called only once, every build call has a super.build (). Following is sample SystemVerilog (SV) code

Class child1 extends ovm\_component;

virtual void function build(); super.build (); //get the configuration information //create child compoenent //configure child component endfunction

. . . . . .

....

#### endclass

As shown in the Figure 4, test level class will call the build function of the env level class and then finally build of the driver, monitor, sequencer will be called.

2. connect ()

The connect phase is executed after build (). connect () is a function call which executes in zero time. connect (). connect () phase makes the TLM connections between verification components in verification environment. Following is a sample SV code for connect () phase.

Class child2 extends ovm\_component;

. . . . . . . .

virtual void connect();

if (is\_active = = OVM\_ACTIVE )

#### driver.seq\_item\_port.connect (sequencer.seq\_item\_export);

for(int i=0; l < = num\_subscribers; i++)</pre>

monitor.analysis\_port.connect (subscr[ I ].analysis\_export);

. . . . . . . .

endfunction

.....

#### endclass

Above code makes first connection between sequencer and driver so that transactions can reach from sequence to driver via sequencer. Second connection is made between monitor and subscriber component (it can be scoreboard) in a loop.

3. end\_of\_elaboration()

This phase allows final adjustments to the environment after build () and connect () phases are over. User can assume that the entire environment is built and connected. This phase is a function call and executed in zero time.

4. start\_of\_simulation()

start\_of\_simulation () phase provides a convenient place to perform any pre-run activity like displaying banners, printing final topology and configuration information. This phase is function call and executes in zero time.

5. run ()

run () phase is only predefined time consuming phase unlike other phases. During this phase components primary run time functionality is executed. Since this phase is implemented as a task it can spawn various processes. This phase can also have function calls during the execution of task. When a component return from run task it does not assure that run phase is complete. Since run is task which can spawn many processes, there can be many processes forked during run. There needs to be a mechanism to stop or kill these processes.

stop- when component's enable\_stop\_interrupt bit is set and global\_stop\_request is called, components stop task is called. This essentially allows completion of current transaction, flush queues, etc. after stop call is returned, kill is executed to kill any remaining processes.

(stop is a method user can implement for safe and desired shut down of processes. global\_stop\_request is a function call made to kill all the current processes of all the components)

- kill- when kill is called all component's run processes are killed immediately. It is recommended that kill should not be called explicitly, instead use stop method of the component for safe shutdown.

- timeout- If a timeout is set, the phase can end at the timeout, provided the timeout came before kill or stop.

Example of run phase will be driver driving the current transaction to the DUT.

6. extract ()

This phase is useful for extracting the simulation results before checks are done in next phase. This phase is function call which executes in zero time. Due to this phase, results from all the components can be gathered and then decision or feedback can be provided later. Following things can be done in extract phase ()

- Collect the assertion-error count

- Collect the coverage information

- Extract internal signals and registers of DUT

- Extract statistics or other information from all component

7. check()

After extraction of the vital information, checks can be applied to decide the progress of the simulation. This phase is a function call which will executes in zero time.

8. report ()

As name suggests this phase is used for reporting the results into the files or on screen. This phase is also a function call which will execute in zero time. Apart from these phases OVM allows users to define additional phases. For detailed information on how to insert new phases to OVM and how to create a verification environment using OVM, refer to OVM User Guide (17).

#### 4. OVM Configuration for WiNC2R Platform

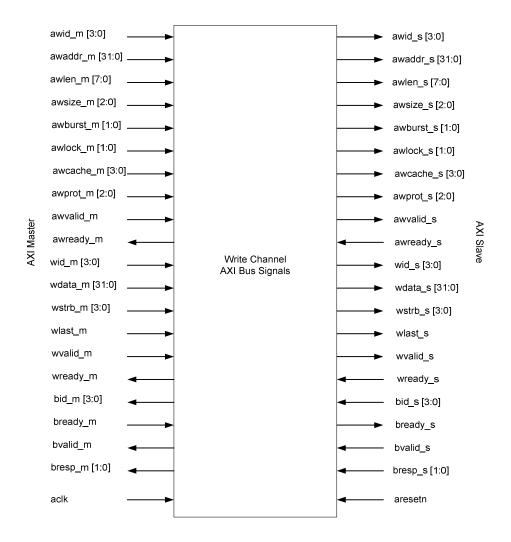

Deciding the parameters for sequence item is the primary step in constrained random stimulus generation. These parameters depend upon the Input variables of the DUT. WiNC2R is an AMBA AXI based bus system. To apply input to the WiNC2R system, bus transaction needs to be done in order to write a descriptor in the queues (as explained in chapter 1). So parameters in sequence item will be the parameters required to initiate bus transaction on AXI bus. The width of these parameters will be depending upon the AXI bus configuration. Following table shows the various parameters required to initiate a write bus transaction on AXI bus. The width of these parameters is decided during AXI bus configuration (3).

| Parameter | Width  | Input/ | Description                                                                |

|-----------|--------|--------|----------------------------------------------------------------------------|

| Name      | (bits) | Output |                                                                            |

| awid_m    | 4      | Input  | Write address ID. This signal is used as identification tag for write      |

|           |        |        | address group of signals. This signal belongs to Write Address<br>Channel. |

| awaddr_m  | 32     | Input  | Write Address. The write address bs gives the address of the first         |

|           |        |        | transfer in a write burst transaction. The associated control              |

|           |        |        | signals are used to determine the address of the remaining                 |

|           |        |        | transfers in busrt. This signal belongs to Write Address Channel.          |

| awlen_m   | 8      | Input  | Burst Length. The burst length gives the exact number of the               |

|           |        |        | transfers in a burst. If burst length is equal to 8, this implies 256      |

|           |        |        | data words can be transferred in a single burst transaction. This          |

|           |        |        | signal belongs to Write Address Channel.                                   |

| awsize_m  | 3      | Input  | Burst Size. This signal indicates the size of each transfer in the         |

|           |        |        | burst transaction. This signal belongs to Write Address Channel.           |

| awburst_m | 2      | Input  | Burst Type. The burst type coupled with size information details           |

|           |        |        | how the address for each transfer will be computed within the              |

|           |        |        | burst. This signal belongs to Write Address Channel.                       |

| awlock_m  |        |        | Lock Type. This signal provides additional information about the           |

|           |        |        | atomic characteristics of the transfer. This signal belongs to Write       |

|           |        |        | Address Channel.                                                           |

| awcache_m | 4      | Input  | Cache Type. This signal indicates the bufferable, cacheable, write-        |

|           |        |        | through, write-back and allocates attributes of the transaction.           |

|           |        |        | This signal belongs to Write Address Channel.                              |

| awprot_m  | 3      | Input  | Protection Type. This signal indicates the normal, privileged or           |

|           |        |        | secure protection level of the transaction and whether the                 |

|           |        |        | transaction is data access of an instruction access. This signal           |

|           |        |        | belongs to Write Address Channel.                                          |

| awvalid_m | 1      |        | Write Address Valid. This signal indicates that the valid write            |

**Table 1: AXI Write Channel Signals**

|           |    |                | address and control information is available. This signal belongs    |

|-----------|----|----------------|----------------------------------------------------------------------|

|           |    |                | to Write Address Channel.                                            |

| awready_m | 1  | output         | Write Address ready. This signal indicates that the slave is ready   |

| /_        |    |                | to accept an address and associated control signals.                 |

|           |    |                | 1 = Address and Control information available                        |

|           |    |                | 0 = Address and Control information not available                    |

|           |    |                | This signal belongs to Write Address Channel.                        |

| wid_m     | 4  | Input          | Write ID tag. This signal is the ID tag of the write data transfer.  |

| -         |    | <b>1</b> • • • | The wid, awid must match for same transaction. This signal           |

|           |    |                | belongs to Write Data Channel.                                       |

| wdata_m   | 32 | Input          | Write data. The write data bus can be 8, 16, 32, 64, 128, 256, 512,  |

|           | -  | <b>1</b> • • • | 1024 bits wide. This signal belongs to Write Data Channel.           |

| wstrb_m   | 4  | Input          | Write Strobe. This signal indicates which byte lanes to update in    |

|           |    |                | memory. This signal belongs to Write Data Channel.                   |

| wlast_m   | 1  | Input          | Write Last. This signal indicates the last transfer in a write burst |

|           | _  |                | transfer. This signal belongs to Write Data Channel.                 |

| wvalid_m  | 1  | Input          | Write Valid. This signal indicates that the write data and strobes   |

|           | -  |                | are valid.                                                           |

|           |    |                | 1 = Write data and strobes are available.                            |

|           |    |                | 0 = Write data and strobes are not available.                        |

|           |    |                | This signal belongs to Write Data Channel.                           |

| wready_m  | 1  | Output         | Write ready. This signal indicates that the slave can accept the     |

|           |    |                | write data.                                                          |

|           |    |                | 1 = Slave ready.                                                     |

|           |    |                | 0 = Slave not ready.                                                 |

|           |    |                | This signal belongs to Write Data Channel.                           |

| bid_m     | 4  | Output         | Response ID. The identification tag of the write response. Bid,      |

|           |    | e acp at       | wid, awid must match for same write transaction. This signal         |

|           |    |                | belongs to Write Response Channel.                                   |

| bready_m  | 1  | Input          | Response Ready. This signal indicates that the master is ready to    |

|           |    |                | accept the response information.                                     |

|           |    |                | 1 = Master is ready.                                                 |

|           |    |                | 0 = Master is not ready.                                             |

|           |    |                | This signal belongs to Write Response Channel.                       |

| bresp_m   | 2  | Output         | Write Response. This signal indicates the status of the write        |

|           | -  | Carpar         | transaction. This signal belongs to Write Response Channel.          |

| bvalid_m  | 1  | Output         | Write Response Valid. This signal indicates that the valid write     |

|           | -  |                | response is available. This signal belongs to Write Response         |

|           |    |                | Channel.                                                             |

| aclk      | 1  | Input          | Global Clock for AXI bus.                                            |

| aresetn   | 1  | Input          | Global reset. This signal is active low.                             |

| uresetti  | ±  |                | follows                                                              |

AXI bus has five different channels as follows

- 1. Read Address Channel

- 2. Write Address Channel

- 3. Write Data Channel

- 4. Read Data Channel

- 5. Write Response Channel

Out of these five channels three channels namely Write Address Channel, Write Data Channel, Write Response Channel are used for write transaction on the AXI bus. Above table and Figure 5 shows details of only Write Channel signals. For detailed information on all channels and the encoding scheme for these parameters, refer to AMBA AXI Specification Document (3).

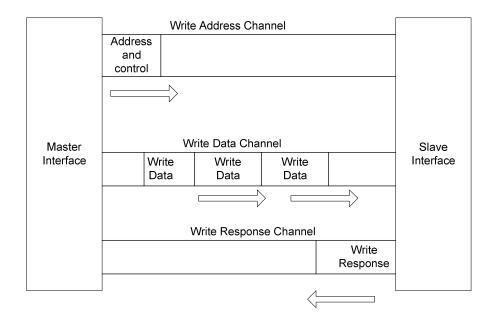

Figure 6: AXI Write Channel Signals

Figure 7: AXI Write Burst Transaction (3)

Figure 6 shows a write burst transaction on AXI bus. In order to initiate a write transaction on AXI bus, the master has to assert awvalid\_m signal only when it drives the valid write address and control information ( like awprot\_m, awcache, awlen etc) about the write transaction( \_m is appended to every signal to denote the master side signals and \_s is used to denote the slave side signals ). awvalid\_m signal must remain high till slave asserts the awready\_s signal. During write burst transaction then master drives wvalid\_m and waits for wready\_s from slave. Master is supposed to keep wvalid\_m high till the entire burst transaction is complete. High wvalid\_m validates the data on write\_data. The master then asserts wlast\_m signal, in order to indicate the last transaction from master. Once all the words have been transferred, master makes the wvalid\_m low. Master needs to drive bready\_m signal high to accept the responses from slave. After complete data transaction, slave asserts bvalid\_s and drives correct responses on bresp\_s. Slave drives responses per transaction by driving appropriate bid. For same transaction, bid, wid and awid must match. For detailed information on AXI protocol refer to AMBA AXI Specification Document (3).

#### s4.1 OVM Sequence Item for WiNC2R Platform

In order to do constrained random stimulus generation, various constraints need to be applied to the parameters involved in AXI bus transaction. So constraints will be applied on the write address channel, write data channel and write response channel parameters. Following snippet of code shows, how to write constraints and how to define sequence item needed for constrained random stimulus generation.

class write\_addr\_ch extends ovm\_sequence\_item;

.....

rand bit [3:0]i\_awid\_m; constraint awid {i awid  $m \ge 0$ ; i awid m < 16;} rand bit [AXI AW-1:0]i awaddr m; rand bit [AXI\_BLW-1:0]i\_awlen\_m; constraint length {i\_awlen\_m >=0; i\_awlen\_m<256; } rand bit [2:0]i\_awsize\_m; constraint awsize {i\_awsize\_m==3'b010;} rand bit [1:0]i awburst m; rand bit [1:0]i awlock m; constraint lock {i\_awlock\_m==2'b00;} rand bit [3:0]i\_awcache\_m; constraint cache {i awcache m==4'b0000;} rand bit [2:0]i\_awprot\_m; constraint protection { i\_awprot\_m==3'b010;} rand bit i\_awvalid\_m; rand bit [AXI\_MIDW-1:0]i\_wid\_m; rand bit [AXI DW-1:0]i wdata m[]; constraint data size { i wdata m.size() == i awlen m+1;} rand bit [(AXI DW/8)-1 :0]i wstrb m; rand bit i\_wlast\_m;

rand bit i\_wvalid\_m; rand bit o\_wready\_m; rand bit i\_bready\_m;

# .....

#### endclass

Consider awid\_m parameter, for writing constraints. AXI bus supports only 16 slaves. While configuring the AXI bus, awid field was set to 4 bits to uniquely identify 16 different slaves. For example to access slave0, awid can be set to 0, for accessing slave1, awid can be set to 1 and so on. Hence the constraint was put on awid so that randomly different values can be generated from 0 to 16. It is not necessary to set awid to 0,1,2 and so on to identify the slaves. awid field is just transaction ID. By keeping the awid 0 for slave0, 1 for slave1 helps in debugging the transactions going on bus. Note that the key word rand was used while defining awid field. Key word rand denotes that the particular field will be randomized in the given range. For example a parameter is defined as follows

#### rand bit [7:0]val

Here if the constraints are not specified explicitly, then randomization engine of SystemVerilog (SV) will generate values from 0 to 255. But if the constraint was written as follows like

constraint limit\_val {val >= 2; val <= 50;}

Then above constraint define the range in which the field val must be randomized. Any attempt to randomize the val outside the given range will result in randomization error. By writing constraints, SV allows users to generate constrained random stimulus. AXI bus was configured to support burst transaction of length 255, hence the constraint was put awlen parameter so that randomly values can be selected only from 0 to 255. Encoding of the bits for awsize, awprot, awlock, awcache, awburst etc is decided by AMBA AXI specification. awsize is set to 2, since that implies 4 bytes are begin transferred in one burst transaction. awlock is set to zero, implying

normal access. AXI bus supports normal, exclusive locked access. awburst is set to one, implying incrementing address burst mode. AXI bus supports 2 more burst types, one is fixed address burst and second is wrap burst transaction where incrementing address burst wraps to a lower address at the wrap boundry, wdata is declared as dynamic array whose length is constrained by the awlen. SV has constraint solver which will assign value to awlen first then constraints will be put on wdata size dynamically. Constraints are not written for awburst since the type of the burst transaction will be set during the runtime. For more information on constraints, constraint solver etc in SV refer to book SystemVerilog for verification (6). Sequence item is a class where the parameters, their ranges, and their constraints are defined. The advantage of extending the class write\_addr\_ch with ovm\_sequence\_item is the built in methods, macros defined in ovm\_sequence\_item. User can completely focus on the parameters, their constraints and their ranges in order to generate constrained random stimulus instead of interaction between sequence item and sequences. Before the data is applied through the driver to DUT, the data or the transaction is generated in sequence item. From sequence item the transaction is passed to sequence. After this transaction is sent to the driver via sequencer. Sequence item, sequence, sequencer, driver are all classes. The communication between different classes is managed by OVM for User. Through various OVM macros various parameters can be set from the test level as per the test writer. OVM methods and macros allow test writer to modify various verification environment configurations without changing underlying code. This sequence item forms the basis for write burst transactions which will be used in generating constrained random stimulus for the WiNC2R Platform. All the SV code related to building verification environment is stored under cog\_svn/Design/trunk/ovm\_tb folder.

#### 4.2 OVM Sequence for WiNC2R Platform

The next verification component in OVM hierarchy is Sequence. Sequence decides the nature of the transaction. Sequences are the back bone in generating constrained random stimulus which in turn are backbone for generating various complex scenarios for validating/ verifying DUTs.

Following snippet of a code shows a sequence written to initiate a single AXI Write burst transaction.

class single\_write\_burst\_tran extends ovm\_sequence;

write\_addr\_ch w;

. . . . . . . .

task body()

for (int i=0; i<1; i++)

`ovm\_do\_with(w,{ w.i\_awvalid\_m==1; w.i\_aresetn ==1; w.i\_awaddr\_m==addr[i]; w.i\_awlen\_m==255;

```

w.i_awburst_m ==1; w.i_wdata_m[0]==data[i];});

```

for(int z= 1; z<256; z++ )begin

`ovm\_do\_with(w,{w.i\_wdata\_m[0]==data[z];

```

w.i_aresetn ==1;});

```

endtask

. . . . .

#### endclass

OVM provides default task called body. User must write the procedural code in the task body so as to generate and drive the transactions. The calling of the task body is managed by OVM for users. Consider the snippet of code as shown above. Inside the task body there is for loop has been coded so as to provide facility to generate different scenarios particular number of times. The loop control parameter can be easily set by test writer before executing this sequence. Consider ovm\_do\_with macro. The first argument of the ovm\_do\_with argument is the object of the sequence item class write\_addr\_ch. ovm\_do\_with macro is used when inline constraints are applied on the parameter defined in sequence item. First in-line constraint in ovm\_do\_with macro is applied to awvalid signal. Note to assign a value 1 to awvalid signal assignment operator is not used, instead equality operator is used. Since the awvalid is forced to 1, whenever the randomization engine will be called, assigned value, in this case, decimal one value will be checked against the constraints written in sequence item class for the awvalid parameter. In the write\_addr\_ch class the awvalid field is defined as rand bit awvalid\_m, implying the awvalid can be assigned any value between 0 and 1 (since this is one bit signal). Therefore by controlling the awvalid signal, the transaction going on AXI bus can be validated or invalidate as per the requirement. Similar explanations can be given for aresetn, awburst, awlen. So there are two places where constraints can be defined. One is sequence item and another place is in sequence by writing in-line constraints. Refer to book, SystemVerilog for verification (6) for detailed information on in-line constraints. Consider a simple example as follows

//constraint defined in sequence item

rand bit [31:0] addr

constraint addr\_range {addr >= 100; addr <= 32'h4000\_0000;}

// in-line constraint defined in sequence

`ovm\_do\_with (w, {w.addr == 200;})

Note that user can specify the in-line constraints only in the range defined in the sequence item class. Using the in-line constraints a specific scenario can be generated very easily. A logic can be written to increment the addr in linear fashion or decrement the addr in linear fashion or do increment or decrement in any fashion provided all operations generate the values in the specified range. Also note that awsize, awcache, awprot have not been assigned a value from ovm\_do\_with

macro. Constraints written in sequence item class will be applicable to these variables when randomization call will be made. Once the ovm\_do\_with macro is called the in-line constraint will be considered while applying constraints to the parameters defined in sequence item class. Based on the in-line constraints, constraint solver of SV will generate random values for other parameters in their ranges. ovm\_do\_with macro will make sure that the newly generated values reach from sequence item to sequence class, from which it can be applied to the driver via sequencer. If the ovm\_do\_with macro calling sequence has a priority than other sequences or it's the only sequence running on sequencer then the generated parameters will reach driver via sequencer. This sequence will be basic for applying constrained random input to the WiNC2R platform as well for initial configuration of WiNC2R, implying for loading GTT, NT, TD memories.

#### **4.3 OVM Sequencer for WiNC2R Platform**

As explained earlier Sequencer just mediates between various sequences and established link between sequences and driver. The main use of the sequencer comes into the picture when there are many sequences running in parallel and they have weighted or fixed priority. In this scenario, sequencer needs to make sure that at the correct time correct sequence and driver link is established. Connection between driver and sequencer is made during the connect phase which is called at agent level.

## 4.4 OVM Driver for WiNC2R Platform

OVM Driver has three main duties to follow.

- 1. Get new transaction from Sequencer

- 2. Drive new transaction on virtual interface connecting verification environment to DUT

- 3. Comply to the Protocol for driving the transaction

OVM gives seq\_item\_port which is built into ovm\_driver class. seq\_item\_port is a bidirectional port and includes TLM methods called get () and peek (). Using the seq\_item\_port driver and

sequencer interact with each other via TLM channel. Series of actions take place when either get or peek task is called. There are two modes in which driver and sequencer can work namely

- 1. Push mode

- 2. Pull mode

In push mode, a sequencer drives a produced item into a driver when that item is generated and waits till the driver consumes this item. In pull mode driver demands the new transaction and gives feedback when the driver is done consuming the data. The pull mode is superior that push mode for following reasons

- In pull mode, a sequence item is immediately consumed after it leaves the sequencer. This means that sequencer can customize the sequence item to the timing consumption of the sequence item unlike push mode where sequencer will wait till the driver finishes consuming the data.

- 2. Single stream of sequence items leaving a sequencer may represent multiple concurrently running scenarios and pull mode gives sequencer chance to arbitrate among the items generated by these concurrently running sequences.

Hence pull mode is preferred than push mode. So while implementing driver pull mode was use than push mode. get (), get\_next\_item (), item\_done (), peek () etc are various built in tasks provided by OVM for interaction between driver and sequencer. get() task is used in driver implementation since item\_done () need not be called explicitly after the items are consumed by the driver. If get\_next\_item () task is used then item\_done task needs to be called explicitly and if peek () task is called then also item\_done () task call is required to make. Once get () task is called feedback is already sent to the sequencer and there is no need to explicitly send feedback to sequencer. In pull mode, once driver requests for the transaction then following series of actions occur as follows

- 1. Driver sends request to the sequencer

- Depending upon the current arbitration scheme, sequencer will choose one sequence at a time

- 3. Selected sequence will be executed and Send the item to sequencer's fifo

- 4. Send the item to the driver from sequencer

- 5. Driver can send feedback by calling item\_done ()

Again driver can send the request to the sequencer. For more information on driver, sequencer interactions refer to OVM User Guide (17). Once the driver gets the transaction, driver assigns the transaction to the virtual interface. Driver is the place where transactions are converted into pin level signals.

Since the WiNC2R is AXI bus based system, the driver has to follow the AMBA AXI protocol as explained earlier with Figure 6. Following snippet of code shows the run phase of the driver

Class write\_driver extends ovm\_driver;

. . . . . . . . .

virtual task run();

forever begin

get\_new\_transaction();

drive\_addr\_ch(t);

check\_awready();

drive\_data\_ch();

read\_response();

end

endtask

. . . . . .

#### endclass

run task of driver is kept in forever loop, so that transactions can be sent continuously to the DUT. This run phase involves following tasks

- 1. Get the transaction from sequencer

- 2. Drive address and corresponding control information on the interface

- 3. Wait for awready from slave

- 4. Drive the data and corresponding control information on the interface and wait for acknowledgement from slave

- 5. Once all the transactions are over then wait for the responses for the current transaction.

Once valid responses are received, driver can ask for the next new transaction from sequencer.

Currently implemented driver supports AMBA AXI protocol.

#### 4.5 OVM Monitor for WiNC2R

The basic purpose of the monitor is as follows

- 1. Monitor the transactions,

- 2. Send the appropriate information to scoreboard,

- 3. Perform protocol related checks and other basic checks

- 4. Gather coverage information.

OVM monitor provides ovm\_analysis\_port, using which monitor can send the necessary information to the scoreboard and to any verification component in the verification environment.

There can be many monitors in the environment for various different interfaces serving different purpose. Verification/ Validation environment implemented for WiNC2R has many different monitors. There are two monitors which are monitoring the read and write transaction going on AXI bus from OVM driver. There is one monitor per single Functional Unit (FU) of WiNC2R. Currently WiNC2R has seven FUs, implying seven monitors. These monitors are connected on different interface than two monitors connected to the AXI bus of OVM driver. Following snippet of code shows one OVM monitor connected to the AXI bus monitoring OVM driver.

class monitor extends ovm\_monitor;

. . .

write\_addr\_ch write\_tran; // creating a object of write\_addr\_ch ovm\_analysis\_port #(write\_addr\_ch) write\_tran\_port;

• • •

virtual task run(); forever begin begin\_recording\_tran(); check\_awready(); write\_tran\_port.write(write\_tran); end // end of the forever begin endtask : run

. . . .

#### endclass

Run phase of the monitor is also kept in the forever loop, so that signals can be monitored continuously. Run phase of the monitor waits till the awvalid signal. After that monitor waits for the awready signal. Checks are provided so as to check that valid acknowledgements are received from slave and correct valid signals are driven as per the protocol. Once the valid data is put on the bus, coverage group is triggered every time new data is driven on the bus. For detailed information on coverage, refer to SystemVerilog for Verification (6). Consider

`ovm\_analysis\_port macro. By using this port, monitor can send the current transaction to the scoreboard. Write\_addr\_ch in `ovm\_analysis\_monitor specifies data structure of the transaction to be sent to the scoreboard. Write\_tran\_port is the name of the analysis port. Due to use of `ovm\_analysis\_port macro, users get write method by which they can send the current transaction to the necessary verification component.

Following snippet of code shows a simple covergroup

- covergroup cov\_write\_tran @ record\_coverage;

- 2. option.per\_instance =1;

- addr : coverpoint write\_tran.i\_awaddr\_m {

- 4. bins valid[] = { [0:9] };

- 5. illegal\_bins invalid\_addr = { [10:\$]}; }

- data : coverpoint write\_data { option.auto\_bin\_max=8; }

- 7. len: coverpoint write\_tran.i\_awlen\_m { option.auto\_bin\_max=8; }

- 8. endgroup : cov\_write\_tran

cov\_write\_tran is the name of the covergroup which will be triggered by record\_coverage event. Once new data is validated on the bus, record\_coverage event will be triggered. There are various options in the covergroup. Option.per\_instance set to one implies that per monitor object this covergroup will be instantiated once per object of the class. Various coverpoints are defined in the covergroup to sample the values of the parameters. The goal of the coverage is to measure how many valid input combinations have been applied to the DUT. For more information on the coverage refer to SystemVerilog for Verification (6). Coverage information helps in understanding the progress of the verification process. addr is name given to the coverpoint write\_tran.i\_awaddr\_m. write\_tran is an object of class write\_addr\_ch. This will sample the AXI address available on its interface. User should specify the valid range for sampling of the parameters. Specifying the valid range for the parameters is necessary in order to have correct measure of the coverage. Bins is a SV construct by which user can specify the valid range. So line 4, implies that only 10 bits of the awaddr will be sampled. In this case, that means addresses from 0 to 1024 will be considered in a valid address range. Next SV construct is illegal\_bins, which allows user to specify invalid range of the parameter. Here in this case address from 1025 to ( $2^{32} - 1$ ) will be considered as illegal address. SV can create automatic bins for user considering the width of the parameter. For example for 3 bit variable, SV will create 8 automatic bins, one per unique combination. User can also specify the number of automatic bins SV should create for the parameter. Line 6 shows option for automatic bin creation. As shown in line 6, data will be sampled into 8 bins. So first bin will sample values from [0:3] that is from 0<sup>th</sup> bit to 3<sup>rd</sup> bit, then second bin will sample values from [4:7] and so on. For more information on coverage refer to SystemVerilog for Verification (6).

#### 4.6 OVM Scoreboard for WiNC2R

Through driver, transaction or particular input combination is applied to the DUT. Based on the input combination, DUT produces output. The correctness of the output is determined in the scoreboard. Monitor sniffs on the interfaces and send the information to the scoreboard. In basic implementation of the scoreboard for WiNC2R, during write transaction, correct data is sent to the scoreboard which is getting loaded into the memories. During the read transaction another monitor sends the read data to scoreboard for checking the data integrity. Scoreboard has `ovm\_analysis\_imp\_port due to which scoreboard can receive the transactions from different monitors. Every ovm\_analysis\_imp\_port provides write method which is called automatically when the monitor sends the data. Scoreboard can have only function, since all function calls are of returned time. Consider following snippet code for scoreboard in zero `ovm analysis imp decl( write)

`ovm\_analysis\_imp\_decl(\_read)

class scoreboard extends ovm\_scoreboard;

ovm\_analysis\_imp\_write #(write\_addr\_ch,scoreboard)write\_port; ovm\_analysis\_imp\_read #(read\_addr\_ch\_seq\_item,scoreboard)read\_port; ..... virtual function void write\_write(input write\_addr\_ch write\_tran); memory\_write(write\_tran);

endfunction : write\_write

. . . . . .

virtual function void write\_read(input read\_addr\_ch\_seq\_item read\_tran);

memory\_read(read\_tran);

endfunction : write\_read

.....

#### endclass

`ovm\_analysis\_imp\_decl(\_write) implies that name of the write method associated with this ovm analysis import will be write\_write and `ovm\_analysis\_omp\_decl(\_read) implies that the write method associated with this ovm analysis import will be write\_read. There is one write method associated with each ovm\_analysis\_imp port. If there are more ovm\_analysis\_import ports then every port needs to have different write method. Consider following line of the code

ovm\_analysis\_imp\_write #(write\_addr\_ch,scoreboard)write\_port;

Here write\_addr\_ch specifies that scoreboard class will receive a transaction of type write\_addr\_ch and name of the port is write\_port. Similar explanation can be given for read\_port. write\_write method will be called when the monitor class will send the transaction to the scoreboard. write\_read method will be called when monitor\_read class will send the transaction to the scoreboard (monitor\_read, monitor is used for sniffing read transaction on AXI bus initiated by OVM driver). memory\_write function is used to store the data sent by monitor class. memory\_read function is called to check the data integrity when monitor\_read send the data to the scoreboard. The connection between scoreboard's ovm\_analysis\_imp and monitor's ovm\_analysis\_port is made during the connect phase. Connect phase is called at an environment level where scoreboard is instantiated as shown in Figure 4.

OVM agent, OVM env are implemented just to complete the hierarchy for verification environment. For WiNC2R, there is no need for multiple environments. Current verification environment has 2 agents one encapsulating the driver, monitor and sequencer responsible for write burst transaction called agent\_write and other encapsulating driver, monitor and sequencer responsible for read burst transaction called agent\_read. Next chapter will focus on generating constrained random stimulus to validate the architecture and on checking the correctness of the output from WiNC2R.

#### 4.7 OVM Test for WiNC2R

OVM test is the level from which test writer can do the necessary configuration for the particular scenario. Test writer can implement his algorithm at this level to generate a particular scenario, by selecting sequences. Three different environment setups are created for the current implementation of WiNC2R. One setup is created to support single flow. Second setup is created to support multiple flows. Third setup is created where instead of processing engines in 802.11a like OFDM transmitter flow, Golden PE is used. Golden PE is like a dummy PE which will mimic the behavior of the normal PE. This setup is useful for experimentation in terms of

determining certain system related parameters. Single flow means currently system is configured to support one virtual flow. As described in chapter 1, it is essential to load the correct GTT, TD and NT tables for correct functioning of the system. So while doing any setup for the WiNC2R, it is essential to load the Memories i.e. GTT, TD, NT tables correctly as part of the configuration. Later part of the setup is related to the requirements. Consider following steps for the single flow setup

- 1. Load the GTT, TD, NT table

- 2. Load the Task Descriptor for MAC

- 3. Wait for an interrupt from MAC

- 4. Insert the data into Input Buffer of MAC

- 5. Repeat step 2-4 till specified number of frames

OVM sequences are chosen for particular activity from OVM test level. By selecting proper sequences, any setup can be done using the same environment. For example, to create a setup for multiple flows, just one parameter of the sequence needs to change and rest of the setup can still remain same as single flow. Due to this feature of OVM Methodology, verification components become highly reusable.

Due to ease of adaptability to different requirements, OVM based verification environment becomes versatile. Currently configured OVM based verification environment for WiNC2R is used for single flow setup, multiple flow setup and setup with Golden PE. Also same verification environment is used for extracting performance from the system. Setup with the Golden PE will be used for validating the architecture and to determine certain system related parameters like guard time.

# 5. Constrained Random Stimulus Generation for validating WiNC2R Scheduler

Constrained random stimulus generation is done by applying constraints on the input parameters. In order to generate constrained random stimulus for WiNC2R, it is important to understand how input is applied to WiNC2R platform, the nature of the asynchronous (async) descriptor, synchronous (sync) descriptor, GTT and TD table descriptors. Parameters defined in the GTT, TD tables and parameters defined in async and sync task descriptors determine the input variables which can be constrained. Whenever any block in the system needs to insert one task in the system, has to form a sync or async descriptor and write that descriptor to the Task Scheduler Queue (TSQ). Once the task is written to TSQ then, it is the scheduler's job to schedule the particular task as per priority. Consider async task descriptor as shown in Figure 8.

| Synchronous Task Scheduler |

|----------------------------|

| Queue Descriptor           |

|                          | FirstChunk Chunk<br>Flag Flag |                  |  |  |  |  |  |  |  |  |

|--------------------------|-------------------------------|------------------|--|--|--|--|--|--|--|--|

| 31 2                     | 4 18/1716                     | 15 0             |  |  |  |  |  |  |  |  |

| FUID                     | <b>A</b>                      | TaskID           |  |  |  |  |  |  |  |  |

| Fran                     | neSize                        | RepetitionNumber |  |  |  |  |  |  |  |  |

| ChunkSize FirstChunkSize |                               |                  |  |  |  |  |  |  |  |  |

|                          | TdPointer                     |                  |  |  |  |  |  |  |  |  |

|                          | Resched                       | ulePeriod        |  |  |  |  |  |  |  |  |

|                          | Start                         | Time             |  |  |  |  |  |  |  |  |