# SYSTEM INTEGRATION AND PERFORMANCE

# EVALUATION OF WINC2R PLATFORM FOR 802.11a

# LIKE PROTOCOL

### BY MADHURA JOSHI

A Thesis submitted to the

Graduate School -- New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Dr. Predrag Spasojevic

and approved by

New Brunswick, New Jersey

October 2010

© 2010

Madhura Joshi

ALL RIGHTS RESERVED

### **ABSTRACT OF THE THESIS**

# System Integration and Performance Evaluation of WINLAB Network Centric Cognitive Radio Platform for 802.11a Like Protocol

By Madhura Joshi

#### Thesis Director: Prof. Predrag Spasojevic

A Cognitive Radio (CR) is an intelligent transceiver that is able to support multiple technologies. It can also be dynamically reconfigured and be easily programmed to achieve high flexibility and speed.

The WiNC2R platform is based on the concept of Virtual Flow Paradigm. The key characteristic of this concept is that the software provisions the flow by determining the roles of hardware and software modules whereas the runtime processing flow is controlled by the hardware. The revision1 of WiNC2R platform was a proof of concept implemented on an FPGA with the basic processing engines to achieve an 802.11a-light OFDM flow, and a simple Virtual Flow Pipeline (VFP) control unit. In the new revision, we have an advanced shared VFP control unit, cluster based SoC architecture, and all the processing engines in an 802.11a like OFDM transmitter flow.

The focus of this thesis was to integrate the WiNC2R platform as an 802.11a like transmitter with the advanced VFP control unit and perform a performance analysis for the realistic application scenario. The performance evaluation revolves around system throughput and latency as a function of frame size, bandwidth, pipelining granularity, number of traffic flows, and flow bandwidth. The analysis is performed for various traffic mix scenarios. We analyze also how effectively the VFP control scheme performs run time task control for a single and multiple OFDM flows.

The thesis starts with the comparative study between the two revisions of WiNC2R and continues to describe in detail the new revision features. The programming techniques are described next, followed by a performance evaluation section and suggestions for future work.

### ACKNOWLEDGEMENTS

I would first like to thank my parents for their constant support without which my journey of completing the MS degree would not have been possible. I would like to thank my advisors Prof. Predrag Spasojevic and Prof. Zoran Miljanic for their time and guidance during the course of completing my thesis. Their advice and suggestions have proven to be very helpful in successfully accomplishing my task. I would also like to thank Ivan Seskar for his support despite being on a very busy schedule.

Being a part of the WiNC2R team has been a fun experience, which would not have been possible without Onkar, Akshay and Mohit. I would like to thank them from the bottom my heart, and I will truly miss working with them. I would also like to thank Khanh, Sumit, Tejaswy, Renu and Prasanthi who have always helped me to resolve my doubts.

# **Table of Contents**

| ABSTRACT OF THE THESISii                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiv                                                                                                                                                                                                                                     |

| Table of Contentsv                                                                                                                                                                                                                                     |

| List of Abbreviationsviii                                                                                                                                                                                                                              |

| List of Tablesix                                                                                                                                                                                                                                       |

| List of Figuresx                                                                                                                                                                                                                                       |

| CHAPTER 11                                                                                                                                                                                                                                             |

| INTRODUCTION1                                                                                                                                                                                                                                          |

| 1.1 Classification of CR Platforms 2                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                        |

| 1.2 WINLAB Network Centric Cognitive Radio Platform                                                                                                                                                                                                    |

| 1.2 WINLAB Network Centric Cognitive Radio Platform    3      CHAPTER 2    6                                                                                                                                                                           |

|                                                                                                                                                                                                                                                        |

| CHAPTER 2                                                                                                                                                                                                                                              |

| CHAPTER 2                                                                                                                                                                                                                                              |

| CHAPTER 2                                                                                                                                                                                                                                              |

| CHAPTER 2                                                                                                                                                                                                                                              |

| CHAPTER 2    6      Cluster Based WiNC2R Architecture    6      2.1: WiNC2R Revision 1 Architecture    6      2.1.1: Functional Unit Architecture    8      2.1.2: WiNC2R Revision 1 Shortcomings    11                                                |

| CHAPTER 2    6      Cluster Based WiNC2R Architecture    6      2.1: WiNC2R Revision 1 Architecture    6      2.1.1: Functional Unit Architecture    8      2.1.2: WiNC2R Revision 1 Shortcomings    11      2.2: WiNC2R Revision 2 Architecture    12 |

| CHAPTER 26Cluster Based WiNC2R Architecture62.1: WiNC2R Revision 1 Architecture62.1.1: Functional Unit Architecture82.1.2: WiNC2R Revision 1 Shortcomings112.2: WiNC2R Revision 2 Architecture122.2.1 WiNC2R Revision1 Memory Map16                    |

| 2.2.4: Tensilica FU Memory Map                |    |

|-----------------------------------------------|----|

| 2.3: AMBA Advanced eXtensible Interface (AXI) |    |

| 2.3.1: Read Burst Transaction                 |    |

| 2.3.2: Write Burst Transaction                |    |

| 2.3.3 AXI Bus Configuration Parameters        |    |

| CHAPTER 3                                     | 33 |

| WiNC2R Revision2 Programming Flow             |    |

| 3.1 GTT, TD and NTT Interface                 |    |

| 3.2 Input Buffer and Output Buffer Indexing   |    |

| 3.2.1 Input Buffer                            |    |

| 3.2.2 Output Buffer                           |    |

| 3.3 System Flow                               |    |

| 3.4 Task Scheduling                           | 39 |

| 3.4.1 Concept of Chunking                     |    |

| Chapter 4                                     | 43 |

| WiNC2R Revision 2 Processing Engines          | 43 |

| 4.1: 802.11a Protocol Description             |    |

| 4.1.1:PLCP Frame Format                       |    |

| 4.2: 802.11a TRANSMITTER                      |    |

| 4.3 WiNC2R 802.11a Transmitter Flow:          | 50 |

| 4.3.1: GNU Radio                              | 51 |

| 4.3.2: Integrating GNU functions in WiNC2R    | 51 |

| 4.3.3: Direct Programming Interface           | 51 |

| 4.3.4: Implementation                         |    |

| 4.3.5: Compiling                                 | 53 |

|--------------------------------------------------|----|

| 4.4: WiNC2R Processing Engine Specifications     | 54 |

| CHAPTER 5                                        | 61 |

| Performance Evaluation of WiNC2R                 | 61 |

| 5.1 WiNC2R Test – Bench Using OVM                | 61 |

| 5.1.1 Basic Experiment                           | 63 |

| 5.1.2 System Latency Experiment                  | 68 |

| 5.1.3 Variation of chunk size on system latency  | 70 |

| 5.1.4 Evaluation of Multiple Flow Support by VFP | 71 |

| CHAPTER 6                                        | 78 |

| CONCLUSION AND FUTURE WORK                       | 78 |

| Bibliography                                     | 80 |

# **List of Abbreviations**

- CR: Cognitive Radio

- WiNC2R: WINLAB Network Centric Cognitive Radio

- VFP: Virtual Flow Pipeline

- FU: Functional Unit

- PE: Processing Engine

- PLB: Processor Local Bus

- AXI: Advanced eXtensible Interface

- OVM: Open Verification Environment

- DPI: Direct Programming Interface

- SV: System Verilog

# List of Tables

| Table 2-1: AXI Core Configuration Parameters   | 32 |

|------------------------------------------------|----|

| Table 4-1: Rate Field Encoding                 | 46 |

| Table 4-2: ChunkSize Calculation               | 56 |

| Table 5-1: System Throughput                   | 68 |

| Table 5-2: Variation of latency with chunksize | 71 |

| Table 5-3: Throughput for two flows            | 77 |

# List of Figures

| Figure 2-1: WiNC2R Revision1 Architecture   | 6  |

|---------------------------------------------|----|

| Figure 2-2: Functional Unit Architecture    | 8  |

| Figure 2-3: WiNC2R Revision2 Architecture   | 13 |

| Figure 2-4: VFP Processing Flow             | 15 |

| Figure 2-5: WiNC2R revision1 memory map     | 16 |

| Figure 2-6: WiNC2R revision1 FU memory map  | 17 |

| Figure 2-7: WiNC2R Base Address Calculation | 19 |

| Figure 2-8: WiNC2R System Memory Map        | 20 |

| Figure 2-9: AXI Read Channel Architecture   | 23 |

| Figure 2-10: AXI Write Channel Architecture | 24 |

| Figure 2-11: AXI Read Burst Transaction     | 25 |

| Figure 2-12: AXI Write Burst Transaction    | 26 |

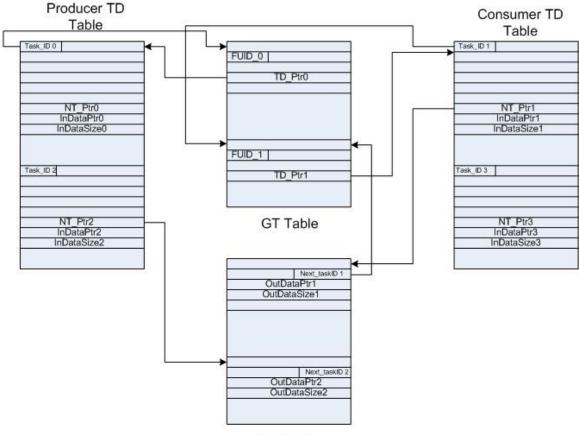

| Figure 3-1: GTT, TD and NT table interface  | 34 |

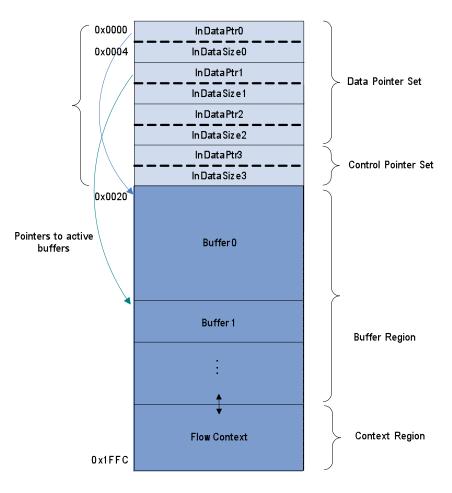

| Figure 3-2: Input Buffer Partitions         | 35 |

| Figure 3-3: Output Buffer Partitions        | 36 |

| Figure 3-4: System Flow                     | 39 |

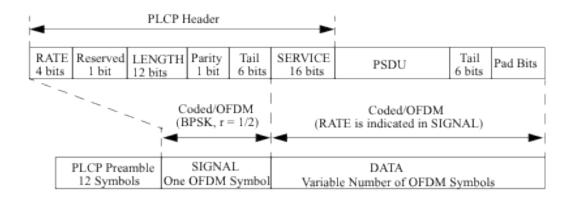

| Figure 4-1: PPDU Frame Format               | 45 |

| Figure 4-2: OFDM Training Sequence          | 45 |

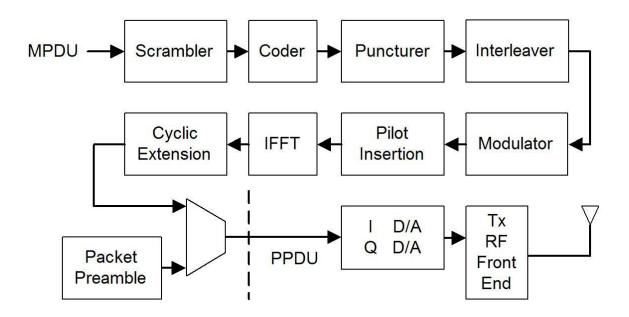

| Figure 4-3: 802.11a Transmitter             | 49 |

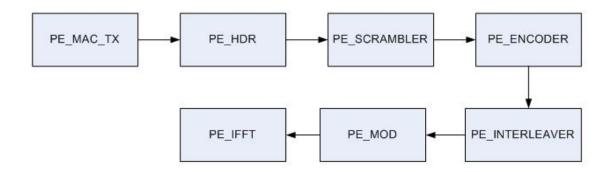

| Figure 4-4: WiNC2R 802.11a Transmitter      | 50 |

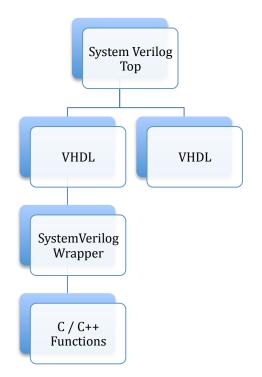

| Figure 4-5: WiNC2R System Hierarchy         | 53 |

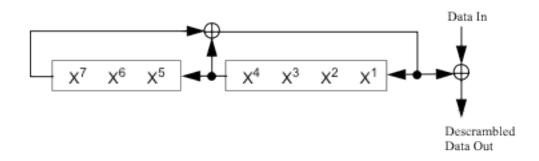

| Figure 4-6: Data Scrambler                  | 57 |

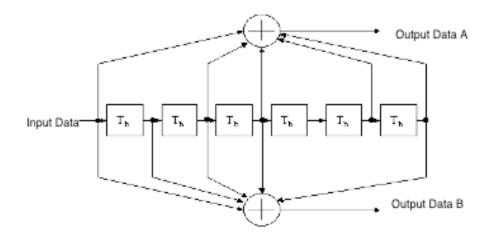

| Figure 4-7: Convolutional Encoder (Constraint Length 7)                      | 59 |

|------------------------------------------------------------------------------|----|

| Figure 5-1: WiNC2R Verification Environment                                  | 62 |

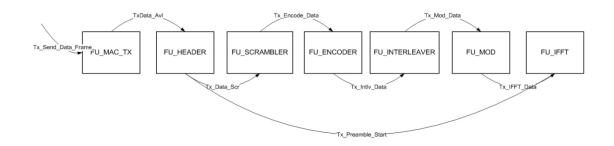

| Figure 5-2: Single Flow Data Transfer                                        | 63 |

| Figure 5-3: WiNC2R Transmitter Frame Flow                                    | 64 |

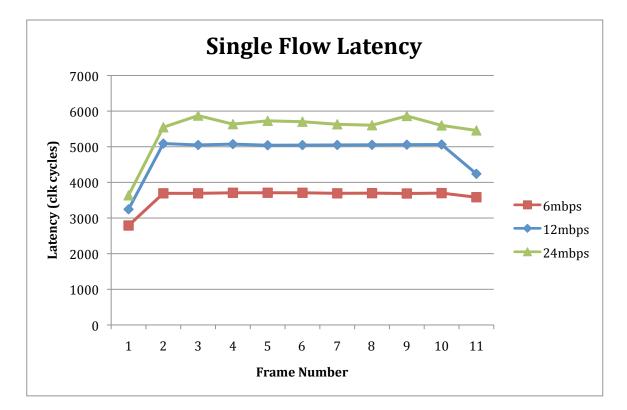

| Figure 5-4: Single Flow Latency                                              | 69 |

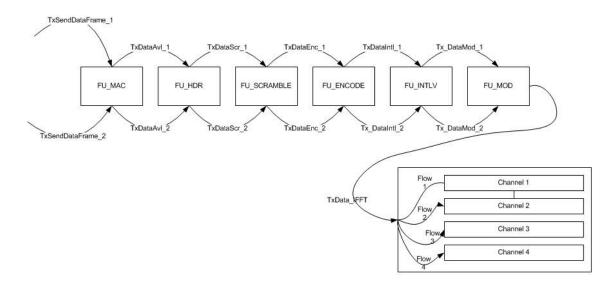

| Figure 5-5: Multiple Flow Data Transfer                                      | 73 |

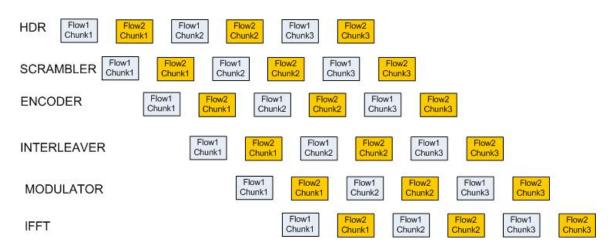

| Figure 5-6: Multiplexing of chunks in 2 flows                                | 73 |

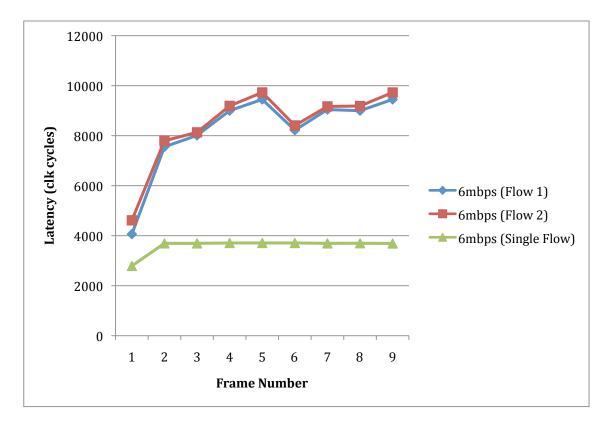

| Figure 5-7: Variation in latency between single and two flows at rate 6Mbps  | 75 |

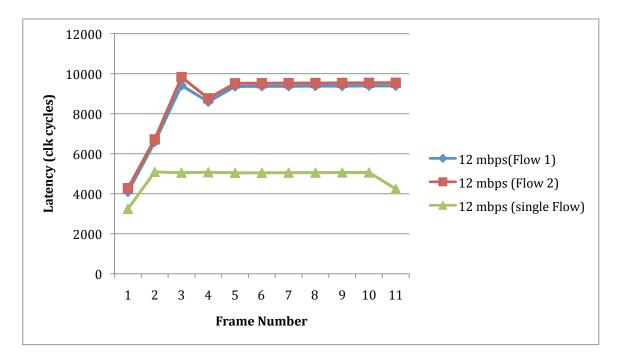

| Figure 5-8: Variation in latency between single and two flows at rate 12Mbps | 76 |

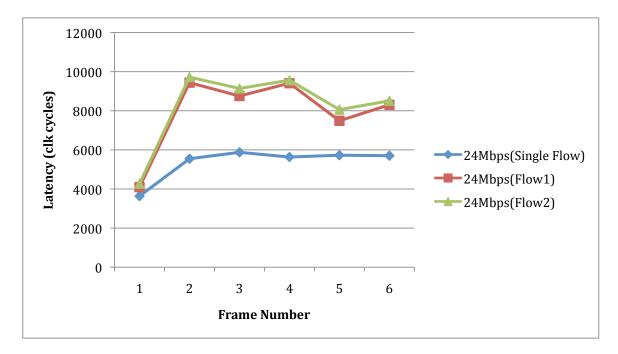

| Figure 5-9: Variation in latency between single and two flows at rate 24Mbps | 76 |

### **CHAPTER 1**

### INTRODUCTION

The next generation wireless technologies clearly impose heterogeneity in their infrastructures, with devices using different radio access technologies and operating at different spectrum bandwidths. (1)Emerging wireless technologies call for solutions with frequent spectrum sensing in addition to per packet adaption of interference, adaption of frequency bands, and yet remain power friendly.

Simultaneous support of such diverse traffic streams and dynamic adaption drives the need of virtualization that can guarantee proper sharing of resources, yet maintaining the end to end latency requirements for each flow.

Cognitive Radio (CR) platforms strive to achieve adaptability, inter-operability and efficient spectrum usage at fast data rates. The following section describes some of the cognitive radio platforms in brief.

#### **1.1 Classification of CR Platforms**

The current CR platforms are classified into four types(2)(3).

- Multimodal Hardware-based Platforms: These platforms implement different technologies by implementing separate modules that support a particular technology. Once programmed, the modules cannot be reprogrammed to implement a different MAC protocol or modify the system parameters. Thus, this type of platform lacks the re-configurability of an ideal cognitive radio. Also, this kind of platform is not scalable, as new modules need to be implemented to support more number of technologies.

- 2. Portable Software Platforms: These platforms implement the radio functionalities in a high level programming language such as C, C++ or JAVA. As the modules are implemented in software, they are easily reconfigurable and also scalable to support multiple technologies. These platforms run as application software on a general purpose or real time operating system on а general-purpose processor. Since RF functionalities such as filtering, up/down conversion, analog to digital conversion and digital to analog conversion are cumbersome to implement in software, RF boards are used to provide a wireless interface. The GNU Radio is one such portable software platform. The performance of these platforms depends on the general purpose processor and the underlying operating system.

- 3. Reconfigurable Hardware Platforms: These platforms implement the physical and the MAC layer functions in FPGA blocks or a combination of FPGA and DSP processor. The platform can support either one or a limited number of protocols, but can be re-configured to support a different protocol by uploading a different bit image onto the FPGA. The modules performing the radio functions are implemented either in low-level hardware or embedded languages and hence difficult to program. The performance of these platforms is limited by the logic capacity of FPGA and the clock rates supported by FPGA and DSP processors. The RICE university WARP platform is one such platform.

- 4. SoC Programmable Radio Processors: These platforms are based on an array of special purpose processors and hardware accelerators for implementing physical layer radio functions. The MAC and the physical layer functions are software programmable. There is no underlying operating system like in the case reconfigurable platforms. The performance of these platforms mainly depends on the number of the processors used and the choice of hardware accelerators.

#### 1.2 WINLAB Network Centric Cognitive Radio Platform

The WINLAB Network Centric Cognitive Radio (WiNC2R) is a platform that targets speed, simple programming and flexibility in the multilayer domain of mobile IP based communication. Its goal is to provide a scalable and adaptive radio platform for the range of cost-capacity configurations, so the architecture is

suitable for both standard cell SoC and FPGA based implementations. The WiNC2R is an excellent platform for the research and development communication labs in academia, industry and government institutions. It can be used for the analysis of the mobile applications computing, communication and control requirements, performance analysis of communication algorithms in a realistic radio propagation environments and hardware versus software implementation tradeoff analysis. This paradigm introduces the concept of Virtual Flow pipelining (VFP) which combines the high-speed computation capabilities of FPGA hardware and flexibility of software. The data flow and parameter inputs to processing blocks are fed by the user in the form of function calls, but the processing happens on hardware. The WiNC2R board is differentiated from the other cognitive radio projects in the sense that the design uses hardware accelerators to achieve programmability and high performance at each layer of the protocol stack.

The WiNC2R revision1 framework was a successful proof of concept implementation on an FPGA. The framework consisted of basic 802.11a processing elements and a low level VFP controller. The transmitter and receiver were implemented on separate FPGA's and successful transmission and reception of packets was achieved. The next revision of WiNC2R is targeted towards an ASIC implementation and hence is a re-configurable SoC based architecture. This revision aims to achieve successful transmission and reception of 802.11a frames with the advanced VFP controller for scalable SoC solutions. The following chapters describe a comparative analysis between the two

frameworks, in detail description of different processing engines and an evaluation of the new framework.

### **CHAPTER 2**

## **Cluster Based WiNC2R Architecture**

### 2.1: WiNC2R Revision 1 Architecture

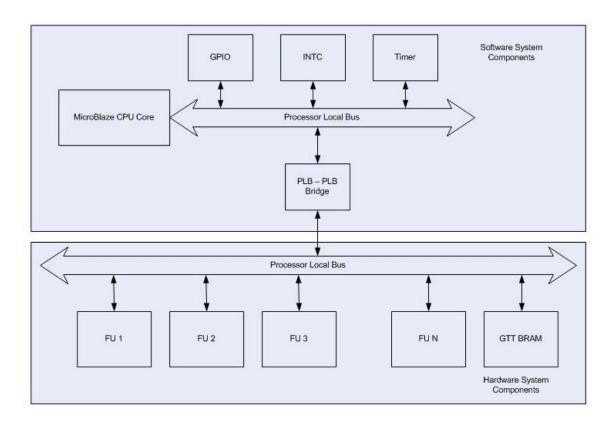

Figure 2-1: WiNC2R Revision1 Architecture

The above figure shows the top-level architecture of WiNC2R (revision 1). The architecture can be split into two main sections – software and hardware. The upper block represents the software components that perform the task of initial configuration of the system. Since WiNC2R revision1 was FPGA based architecture, the CPU core used on the software side was a standard Xilinx soft-core CPU called Microblaze which connected to its own GPIO ports (General Purpose IO), Timer and Interrupt peripheral modules using an IBM standard bus structure called Processor Local Bus (PLB). The hardware components are initialized and the data flow between them was configured through software. The lower block represents the hardware components that perform the actual radio processing tasks. The data processing occurs in the Functional Units (FU) and the data transfer from one FU to another occurs over the PLB. All FU's were implemented in VLSI Hardware Description Language (VHDL). The FU interfaces to the PLB through Xilinx standard Intellectual Property Interface (IPIF).

#### 2.1.1: Functional Unit Architecture

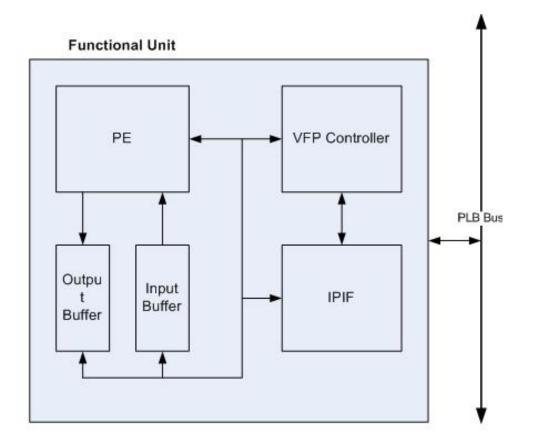

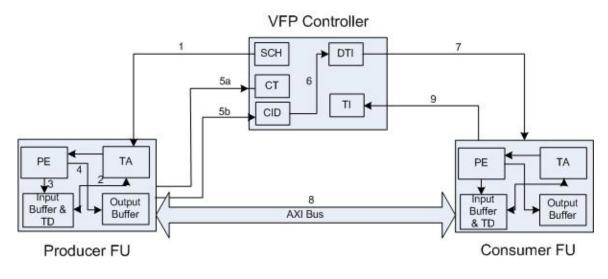

Figure 2-2: Functional Unit Architecture

The FU consists of Processing Engine (PE), VFP controller, input and output memories as shown in the above figure. The operations performed by an FU are split into two categories – data and control. The data operation refers to the data processing handled by the PE, while the control operation refers to the tasks performed by the VFP controller to initiate and terminate the PE tasks. The inputs required by the PE for data processing is stored in the input memory buffer, while the data generated after processing is stored in the output memory buffer. The memory buffers are implemented as Dual Port Random Access Memory (DPRAM) generated using Xilinx CoreGen. The Register MAP (RMAP) within the PE stores software configurable control information required for PE processing.

The VFP controller manages the operation of FU-s achieving reconfigurability. WiNC2R uses a direct architectural support for task-based processing flow. The task flow programming is performed by two control data structures: Global Task-descriptor Table (GTT) and Task-Descriptor Table (TD Table). Both control tables are memory based. GTT was implemented as a block RAM connected to the PLB and common to all FUs while each FU had its own TD Table. Based on its core functionality, each PE was assigned a set of input tasks and the PE was idle until it received one of those tasks. The PE handles two types of tasks: data and control. Data task indicated that data to be processed was present in the input buffer of the PU. For example, data task "TxMod" told the Modulator block that there was data in the input buffer that needed to be modulated. This data was first transferred to the input buffer of FU before the task was sent to the PE. Control tasks do not operate on the payload but behave as pre-requisites for data tasks in some PE's. For example, "TxPreambleStart" control command initiated the preamble generation task in the PE TX IFFT engine before handling a data task. This was necessary, as the preamble is attached to the beginning of the data frame before transmitting.

The TD Table stores all the required information for each task for the FU. When the FU received a data task, the VFP controller Task Activation (TA) block fetches the information from the TD table and processes it. It then forwards the task to PE along with the location and size of input data. The PE processed the data and stored it in the Output Buffer. Once the processing was over, PE

relayed the location and size of processed data in Output Buffer to the VFP controller through Next Task Request and Next Task Status signals. The Next Task Status bits indicate the location of the processed data in the output buffer. Depending on the PU, the output data may be stored at more than one location. The Next Task Request signal informs the VFP controller Task Termination (TT) block how the output data at locations indicated by status bits should be processed. The TT processing includes transferring the data to next FU/FUs in the data flow. The NT Request tells the TT to which FU the data is to be sent. The FU in the data flow in determined by the information stored in TD table. By updating the information in TD table, software can change the next FU in the data flow path. Thus, the PE has no information regarding the next processing engine in the flow. As a result, all the PE's are independent of each other and only perform the tasks allocated to them. The next processing engine in the flow can thus be changed on-the-go and hence a complete reconfigurable architecture is achieved.

#### 2.1.2: WiNC2R Revision 1 Shortcomings

As shown in Figure 2-2, currently each functional unit has a dedicated VFP controller. Initial analysis has revealed that this scheme keeps each VFP controller unutilized for more that 70% of the time(2). This incurs a high hardware as well as power cost. Moreover, the need for synchronization among the various distributed VFP controllers requires the maintenance and access of a common global control memory structure. These accesses over the common bus increase bus traffic and latency, eventually delaying task termination. This impacts the system performance as well as end-to-end protocol latency, thus limiting the application of the platform. The above-mentioned issues with VFP controller per functional unit scheme have prompted us to explore new architectures implementing a centralized approach.

The data generated by a PE can exceed several 100 bytes and the transfer of data occurs over the system bus. Hence it is mandatory that the bus does not create a bottleneck in the system. The PLB is the system bus used in WiNC2R revision1 over which data is transferred from one FU to another depending on the programmed application. The PLB has a limitation where it can transfer a maximum of 64bytes (16 words) in a single burst transfer. After transferring the 16 words, the master has to place a request to access the bus and can resume transferring the data once PLB has granted access to the requesting master. A case of data transfer from FU\_MODULATOR to FU\_IFFT was analyzed, where the FU\_MODULATOR generates data of size 768 bytes. Due to the PLB bus limitation the entire transfer of 768 bytes occurs as of 12 chunks each of 64 bytes.

The above-mentioned shortcomings of WiNC2R revision1 architecture led us to explore different options to overcome the shortcomings. Centralizing the VFP controller for several FU's and using a system bus of better throughput such as AMBA AXI, are the highlights of the WiNC2R revision2 architecture.

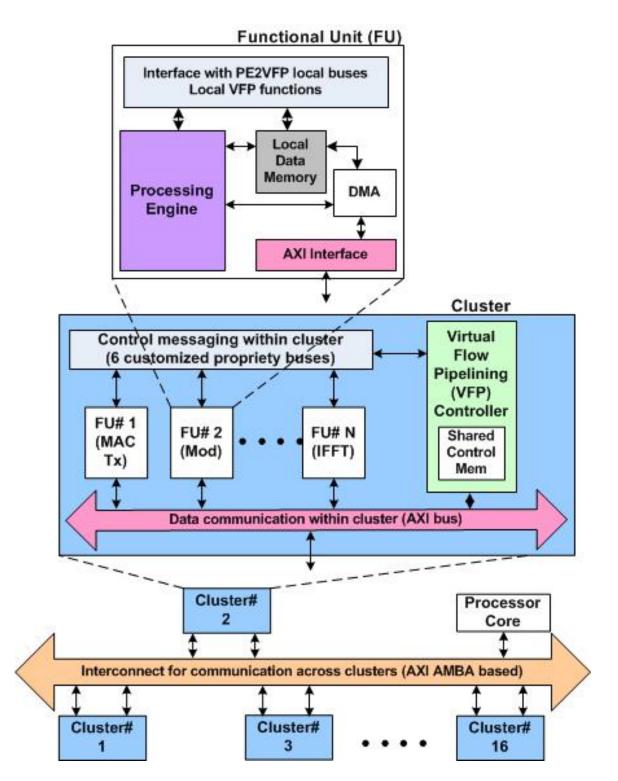

#### 2.2: WiNC2R Revision2 Architecture

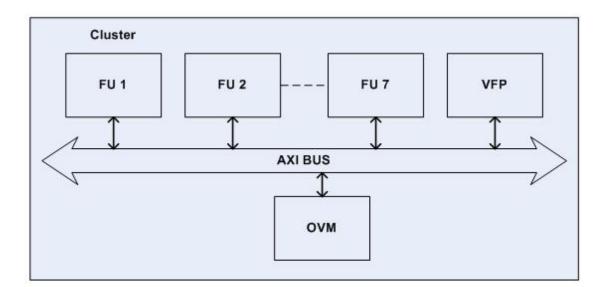

WiNC2R revision2 is a Cluster Based System on Chip architecture (SoC) as shown in the Figure 2-3. The system interconnect used in revision2 architecture is AMBA AXI. Hierarchical bus architecture is implemented as shown in Figure 2-3. The communication between the clusters occurs over the main system bus while the communication between the FU's within a cluster occur over another AXI bus within a cluster. The dedicated VFP controller in the previous architecture is replaced with a VFP Controller that is common to several FU's within a cluster. The architecture of the FU is similar to the one in revision1 architecture consisting of a dedicated processing engine, input, output buffer memories and a Dynamic Memory Access (DMA) Engine to transfer data between FU's over the AXI bus present with a cluster. The communication between the VFP controller and FU's occur over a dedicated bus to each FU. As in the previous architecture, the PE handles both the data and the control tasks while the VFP controller schedules the tasks to each FU.

Figure 2-3: WiNC2R Revision2 Architecture

Source: Onkar Sarode, Khanh Le, Predrag Spasojevic, Zoran Miljanic: Scalable Virtual Flow Pipelining SoC Architecture, IAB Fall 2009 Poster

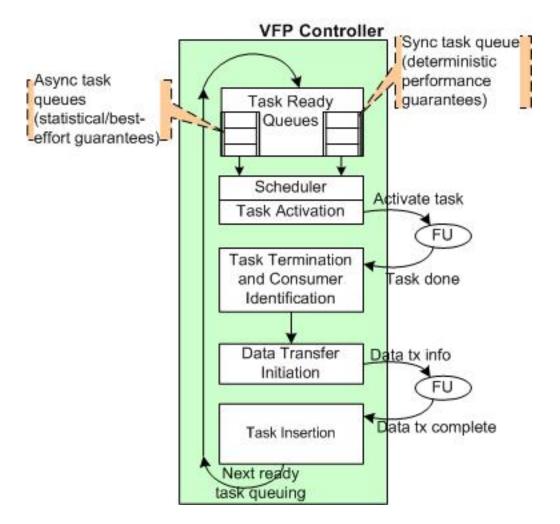

The VFP controller's functions are divided into - task scheduling and activation, communication between the tasks and scheduling of processing resources to the tasks. The task activation function includes dynamically scheduling a task, identifying the FU corresponding to the task and initiating it. The Task Activation (TA) block that is local to every FU performs the actual initiation of a task. Once the VFP activates a particular FU, it is free to perform task activation of other FU's. Once the PE within an FU completes processing the data, it activates the task termination blocks within the VFP. The Next Task Table (NTT) within the VFP contains information regarding the task to be performed next. Hence, the VFP initiates the data transfer between the producer and consumer FU. The consumer FU can be placed either in the same (local) cluster or a different (remote) cluster. If the consumer FU is present in the local cluster, the data transfer occurs over the AXI bus within the cluster. But if the consumer FU is present in a remote cluster, the data transfer occurs over the system-interconnect.

Figure 2-4: VFP Processing Flow

Source: Onkar Sarode, Khanh Le, Predrag Spasojevic, Zoran Miljanic: Scalable Virtual Flow Pipelining SoC Architecture, IAB Fall 2009 Poster

Due to centralization of the VFP and a cluster-based architecture, the decoding scheme to identify a particular FU is different from the revision1 architecture. The following section describes the WiNC2R revision1 and revision2 memory maps in detail.

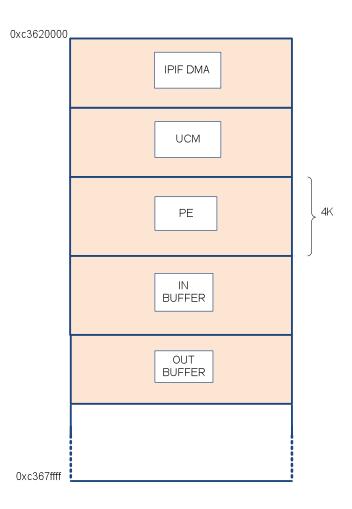

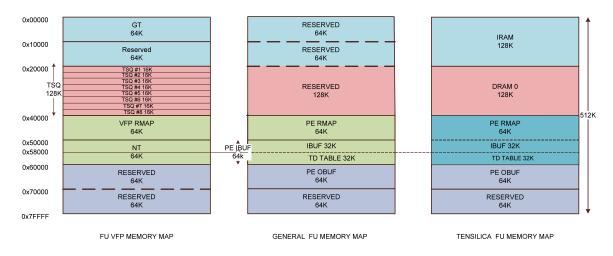

#### 2.2.1 WiNC2R Revision1 Memory Map

All the blocks in the revision1 platform are of size 64k and can be visualized as seen in the figure 2-5

Source: Khanh Le, Shalini Jain: ncp\_global\_memory\_map.doc

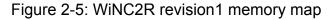

As shown, each FU consists of the following sub-blocks: IPIF DMA, UCM (dedicated VFP controller), PE, input buffer and output buffer. Each FU has a 64k address range divided into five main regions as shown in figure 2-6.

Figure 2-6: WiNC2R revision1 FU memory map

Source: Khanh Le, Shalini Jain: ncp\_global\_memory\_map.doc

Since, each FU has a dedicated VFP controller, address decoding of the different FU's is based only their base memory address. Secondly, each FU has its own TD table and Task Scheduler Queue.

Due a centralized VFP controller in the new revision, the address decoding of the different FU's is based on an FU\_ID and CLUSTER\_ID. These id's allow the VFP

controller to identify a particular FU. This feature was unnecessary in the previous revision because of a dedicated VFP controller.

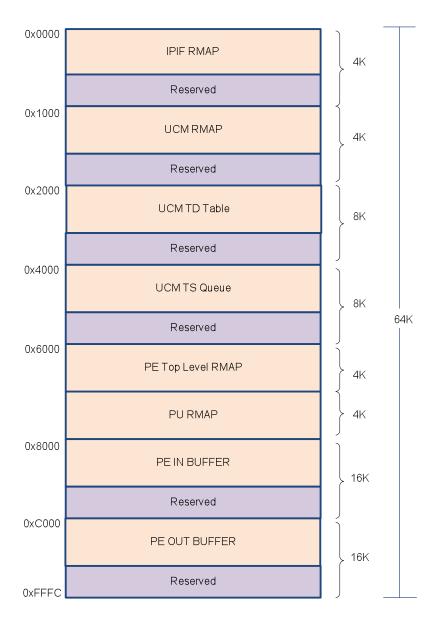

#### 2.2.2: WiNC2R Revision2 System Memory Map

The WiNC2R revision2 architecture has a maximum of 16 clusters and each cluster can have a maximum of 16 FU's.

Size of 1 FU = 512KB

Size of 1 Cluster = 16 \* 512KB = 8MB

Size of 16 Clusters = 16 \* 8MB = 128MB.

Hence, the total system memory is of size 128MB. The base address of each cluster and the decoding of the FU address are shown in figure 2-7.

To access a memory space of 128MB, we require 27bits. Its "Cluster ID" identifies the cluster while the FU is identified by its "FU ID". The cluster and FU ID are 4 bits wide. As shown, the bits 26 to 23 represent the cluster ID and bits 22 to 19 represent the FU ID. For example, the base address of FU 1 in cluster 0 is 0x0008000.

Figure 2-7: WiNC2R Base Address Calculation

Source: Akshay Jog, Khanh Le: WiNC2R Global Memory Map – Release 2

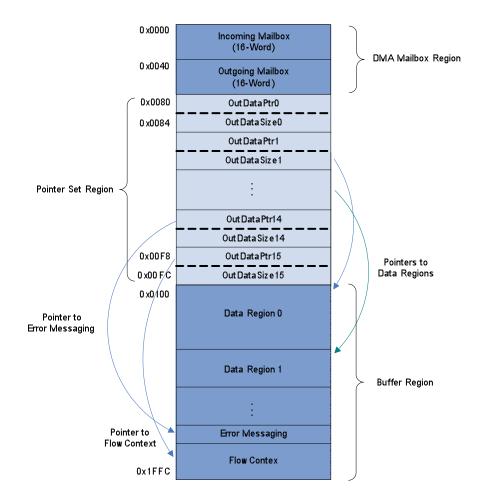

The revision2 framework consists of certain new FU's in addition to the FU's from the revision1 architecture. The processing engine within the FU is either a native C/C++ function from GNU Radio or a SystemC wrapped Tensilica Application Specific Instruction Set Processor Entity or a VHDL entity from revision1 architecture. Figure 2-8 represents the VFP, General FU and Tensilica based FU memory map. The base address of each memory entity is also shown.

Figure 2-8: WiNC2R System Memory Map

Source: Akshay Jog, Khanh Le: WiNC2R Global Memory Map – Release 2

#### 2.2.2: VFP Memory Map

Since the VFP is a centralized entity controlling several FU's, certain memories that were local to an FU in the previous architecture are now a common memory entity in the VFP.

*Global Task Table (GTT):* The GTT is a 64KB memory that resides within the VFP. Since the GTT is local to VFP, there is one GTT per cluster. The GTT describes the flow of tasks depending on the application. The GTT was a global memory table in the revision 1 framework and hence was common to all FU's .

*Task Scheduler Queue (TSQ):* Each FU in the revision 1 framework had a local TSQ. Depending on the nature of the task, the task descriptors were either stored in the synchronous or the asynchronous queues. Since the common VFP controller handles the scheduling of tasks of different FU's, the TSQ is now made

local to the VFP rather than having a separate TSQ in each FU.

To begin with, it is assumed that a cluster consists of 8 FU's. Hence the 128KB memory space of TSQ is divided into 8 resulting in a 16KB TSQ per FU. The tasks corresponding to every FU is placed in the appropriate TSQ by the VFP controller.

*VFP RMAP:* The VFP controller can be initialized by the software by writing into the VFP RMAP. Currently the VFP RMAP is not used.

*Next Task Table (NTT):* The NTT contains information regarding the next task to be activated the VFP after the completion of a particular task by the FU. This information previously resided in the TD table that was local to each FU. It is now stored in a different memory entity and is local to the VFP.

#### 2.2.3: General FU Memory Map

The general FU memory map is similar to the one in the previous revision, except for some minor changes that are described below.

*PE RMAP:* The processing engine can be configured and initialized by writing into its RMAP. The software writes into the RMAP during system configuration.

*PE IBUF:* The PE IBUF is divided into two sections – the IBUF and the TD table. The PE reads the required data for it's processing from the PE IBUF, while the TD table consists of information that describe the task being performed. Hence each FU has a local TD table describing the tasks that the particular FU can perform.

*PE OBUF:* After processing the data read from IBUF, the PE writes the data into the OBUF. When the VFP controller initiates a DMA transfer, the data from the OBUF is transferred into the IBUF of the FU that is next in processing flow.

#### 2.2.4: Tensilica FU Memory Map

*Instruction RAM (IRAM):* The Instruction RAM stores the instruction set required for the processor to execute the data processing algorithm.

*Data RAM (DRAM):* The Data RAM stores the variables required by the processor to execute the data processing algorithm.

The data stored in PE RMAP, IBUF and OBUF is similar to the one described in the general FU memory map section.

The second bottleneck in the revision 1 framework was created by the PLB. We decided to replace the PLB with the AMBA AXI bus. The following section describes the AXI bus in detail.

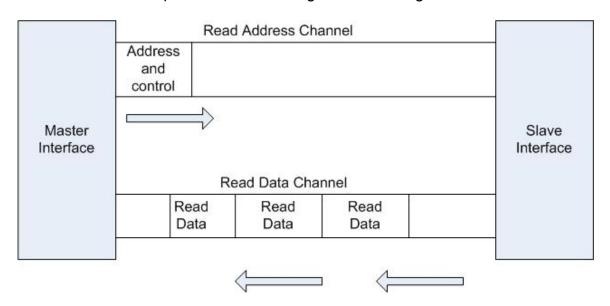

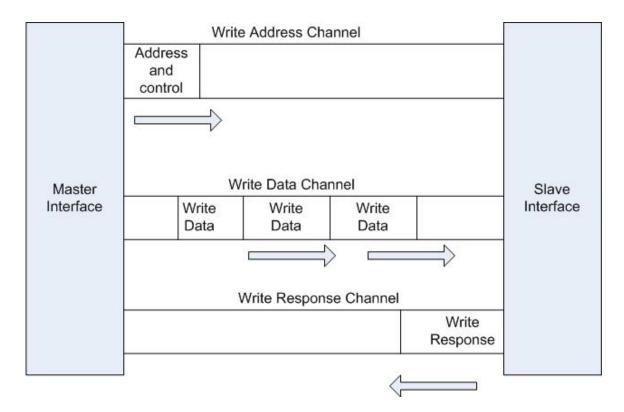

### 2.3: AMBA Advanced eXtensible Interface (AXI)

The AMBA AXI bus extends the AMBA Advanced High performance Bus (AHB) with advanced features to support next generation high performance SoC architectures. The AXI bus has channel architecture and can be configured to have separate write and read address and data channels. The AXI architecture for read and write requests is shown in Figure 2-7 and Figure 2-8.

Figure 2-9: AXI Read Channel Architecture

Figure 2-10: AXI Write Channel Architecture

The channel architecture for read transactions depicts a separate channel for address and data. The master sends the address and control information over the address channel to the slave. The slave in response sends the data over the data channel.

Similar to the read transaction, the write transaction channel architecture is also depicted. The master sends the address and the control information over the address channel to the slave, while the data to be written is sent over the data channel as shown. The slave sends out the response to the master over the write response channel. As the read and write address and data channels are separate, the AXI bus can handle simultaneous read and write transactions. In addition to performing simultaneous read and write operations, the AXI bus can also handle multiple outstanding instructions and out of order completion of transactions. The read and write transaction protocols are described below.

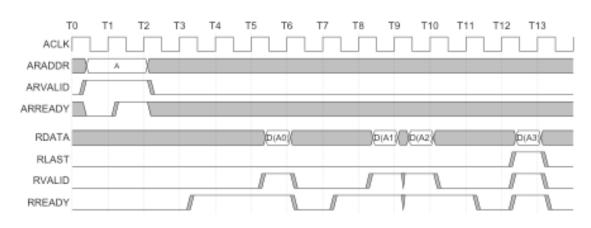

### 2.3.1: Read Burst Transaction

Figure 2-11: AXI Read Burst Transaction

Source: AMBA AXI v1.0 Specifications

The above figure represents a read burst transaction.(4)

- The master asserts the "arvalid" signal along with a valid address on the "araddr" signal.

- The slave asserts the "arready" signal, indicating that the slave is ready to accept the address and the corresponding control signals.

- The master asserts the "rready" signal, indicating to the slave that it is ready to accept the data and the responses.

- The slave asserts the "rvalid" signal along with the valid data on the "rdata" signal. The slave indicates the master that the data on the "rdata" signal is the last in the burst transaction by asserting the "rlast" signal.

### 2.3.2: Write Burst Transaction

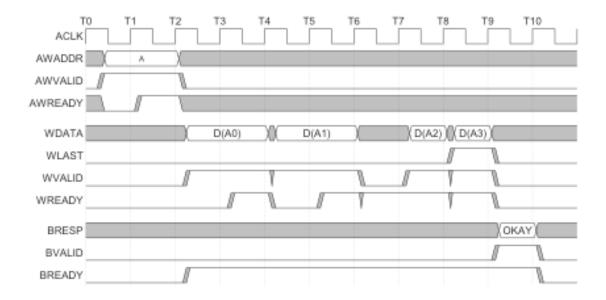

Figure 2-12: AXI Write Burst Transaction

Source: AMBA AXI v1.0 Specifications

The above figure represents a write burst transaction.(4)

- The master the "awvalid" signal along with a valid address on the "awaddr" signal.

- The slave asserts the "awready" signal, which indicates that the slave is ready to accept the address and other control signals.

- The slave asserts the "wready" signal, which indicates that the slave is ready to accept the data.

- The master then asserts the "wvalid" signal and also puts valid data on the "wdata" signal. Along with this, the master also asserts the "bready" signal indicating that it is ready to accept the response from the slave.

- The master asserts the "wlast" signal along with the "wvalid" and "wdata" signal, indicating that the word is the last word in the burst transaction.

- The slave sends back the response on the "bresp" signal along with asserting the "bvalid" signal, indicating that the response on "bresp" channel is valid.

The maximum number of data transfer in a burst is defined by the "awlen" or "arlen" signal. The signal can be configured to have a maximum of 256-byte transfer in a single burst. This provides an improved performance over the PLB, which handles only 64-byte transfer in a single burst transaction. The size of data in each burst is configured by the "awsize" and "arsize" signals and is set as 32 bit word. The AXI bus can perform burst transfers of 3 kinds.

- *Fixed Burst:* In a fixed burst, the address remains the same for every transfer in the burst. This burst type is for repeated accesses to the same location such as when loading or emptying a peripheral FIFO.

- Incremental Burst: In an incrementing burst, the address for each transfer in the burst is an increment of the previous transfer address.

The increment value depends on the size of the transfer. For example, the address for each transfer in a burst with a size of four bytes is the previous address plus four.

Wrap Burst: A wrapping burst is similar to an incrementing burst, in that the address for each transfer in the burst is an increment of the previous transfer address. However, in a wrapping burst the address wraps around to a lower address when a wrap boundary is reached. The wrap boundary is the size of each transfer in the burst multiplied by the total number of transfers in the burst.

### 2.3.3 AXI Bus Configuration Parameters

The AXI bus core is configured using Synopsys DesignWare CoreConsultant. There are various design parameters that determine the behavior of the AXI core. Some of the parameters that are relevant to the system are mentioned in the table below.

| AXI Core         | Parameter Definition                 | Configuration | Reason            |  |

|------------------|--------------------------------------|---------------|-------------------|--|

| Parameter        |                                      | Chosen        |                   |  |

| AXI Data Bus     | This is the width of the data bus    | 32 bits       | Standard data     |  |

| Width            | that applies to all interfaces.      |               | size width        |  |

|                  | Legal values: 8, 16, 32, 64, 128,    |               |                   |  |

|                  | 256 or 512 bits                      |               |                   |  |

| AXI Address Bus  | This is the width of the address     | 32 bits       | Standard address  |  |

| Width            | bus that applies to all interfaces.  |               | size width        |  |

|                  | Legal values: 8, 16, 32, 64, 128,    |               |                   |  |

|                  | 256 or 512 bits                      |               |                   |  |

| Number of AXI    | Number of masters connecting         | 9             | System consists   |  |

| Masters          | the to AXI master port.              |               | of 7 functional   |  |

|                  | Maximum value = 16                   |               | units, 1 VFP      |  |

|                  |                                      |               | controller and    |  |

|                  |                                      |               | OVM               |  |

|                  |                                      |               | environment. All  |  |

|                  |                                      |               | act as masters    |  |

| Number of AXI    | Number of slaves connecting to       | 8             | The 7 functional  |  |

| slaves           | the AXI slave port                   |               | units and VFP act |  |

|                  |                                      |               | as slaves         |  |

| AXI ID: Width of | This is the ID bus width of all five | 4             | 4 bits are        |  |

| Masters          | AXI channels connected to an         |               | sufficient to     |  |

| (AXI_MIDW)       | external master. All masters have    |               | access 9 masters  |  |

|                  | the same ID width for all five AXI   |               |                   |  |

|                  | channels.                            |               |                   |  |

| AXI ID: Width of | This is the ID bus width of all five | 8             | Generated         |  |

| Slaves           | AXI channels connected to an         |               | automatically     |  |

| (AXI_SIDW)        | external slave. It is a function of |                            | using the          |  |

|-------------------|-------------------------------------|----------------------------|--------------------|--|

|                   | the AXI ID Width of Masters         | he AXI ID Width of Masters |                    |  |

|                   | (AXI_MIDW) and the number of        |                            | formula            |  |

|                   | masters (AXI_NUM_MASTERS).          |                            |                    |  |

|                   | AXI_SIDW=AXI_MIDW                   |                            |                    |  |

|                   | +ceil(log2(NUM_AXI_MASTERS))        |                            |                    |  |

|                   | This parameter is calculated        |                            |                    |  |

|                   | automatically, and the same width   |                            |                    |  |

|                   | is applied to all slaves.           |                            |                    |  |

| AXI Burst Length  | This is the width of the burst      | 8 bits                     | Maximum value of   |  |

| Width             | length signal for both read and     |                            | burst length width |  |

|                   | write address channels on both      |                            | is selected to     |  |

|                   | the master and slave ports. The     |                            | enable the         |  |

|                   | AXI protocol specifies this is a 4  |                            | transfer of 256    |  |

|                   | bit value, but this width is        |                            | words in a single  |  |

|                   | configurable to 8 bits wide to      |                            | burst.             |  |

|                   | support longer bursts up to 256     |                            |                    |  |

|                   | data beats.                         |                            |                    |  |

| Slave Port        | Selects the type of arbiter to be   | First Come First           | All the slaves are |  |

| Arbiters (read    | used at the slave port read         | Serve                      | of equal priority  |  |

| address, write    | address, write address and write    |                            | and hence first    |  |

| address and write | data channels.                      |                            | come first is      |  |

| data channels)    | Priority Arbitration: Highest       |                            | chosen             |  |

|                   | priority master wins                |                            |                    |  |

|                   | First Come First Serve: Masters     |                            |                    |  |

|                   | are granted access in the order of  |                            |                    |  |

|                   | the incoming requests.              |                            |                    |  |

|                   | Fair Among Equals – 2 tier          |                            |                    |  |

| arbitration: First tier is dynamic  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| priority; second tier shares grants |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| equally between masters of the      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| same highest requesting priority    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| on a cycle-by-cycle basis.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| User Defined: instantiates a plain- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| text arbitration module which the   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| user can edit to their own          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| requirements                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Selects the type of arbiter to be   | First Come First                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | All the masters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| used at the master port read data   | Serve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | are of equal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and burst response channels.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | priority and hence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Priority Arbitration: Highest       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | first come first is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| priority master wins                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | chosen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| First Come First Serve: Masters     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| are granted access in the order of  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| the incoming requests.              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |