## ARCHITECTURE OF A PROGRAMMABLE SYSTEM-ON-CHIP PLATFORM FOR FLEXIBLE RADIO PROCESSING

BY ONKAR SARODE

A thesis submitted to the

Graduate School—New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of Prof. Predrag Spasojević

and approved by

New Brunswick, New Jersey October, 2010 © 2010

Onkar Sarode ALL RIGHTS RESERVED

## ABSTRACT OF THE THESIS

## Architecture of a Programmable System-on-Chip Platform for Flexible Radio Processing

## by Onkar Sarode Thesis Director: Prof. Predrag Spasojević

The emergence of multiple radio access technologies (RATs) and their continuous evolution, is driving the need for programmable radio processing. Programmable radio devices with run-time flexibility and resource virtualization features will not only enable faster time-to-market, longer lifetime of devices, and universal connectivity, but also act as building blocks for advanced wireless technologies of adaptive and cognitive radios. These requirements have forced a shift from the traditional ASIC approach. However, most existing flexible solutions are based on either fully software-defined or softwarecontrolled approaches that lack the power efficiency, performance and determinism (for real-time constraints) needed for wireless processing.

In this thesis, we propose a programmable multi-processor system-on-chip (SoC) platform architecture based on a novel Virtual Flow Pipelining (VFP) framework that aims at striking a balance between flexibility (as provided by SDR) and performance (as provided by ASICs). The key highlights of this concept are a simple task-level programming model for provisioning protocol flows, and the use of dedicated hardware-based OS-like support for controlling their run-time execution. We present the evolution of

a clustering-based organization for the SoC with distributed-shared controllers. Clustering along with an inherent architectural support for message passing provides a balance between scalability and hardware overhead. Shared controllers with a pipelined microarchitecture and a separate interconnect for control messaging are designed for low hardware complexity and high performance.

The proposed architecture is evaluated by creating a bit- and cycle-accurate model in synthesizable *register-transfer-level* (RTL). It has been built into a virtual platform for 802.11a transmitter, which has successfully executed single and multiple flows for rates of 6, 12 and 24 Mbps. This thesis also presents a characterization and analysis of the architecture to provide key implications such as control overhead for different task sizes, its impact on cluster size etc.

## Acknowledgements

Foremost, I would like to express my sincere gratitude to my advisors, Prof. Zoran Miljanić and Prof. Predrag Spasojević, for their continuous support and guidance throughout my thesis. I am indebted to Prof. Miljanić for his confidence in my abilities and all the opportunities he has provided. I cannot thank him enough for the great learning experience that this has been. I am grateful to Prof. Spasojević for giving me complete freedom in my work and teaching me to think with respect to the *big picture*.

I would also like to thank Khanh Le for all the *anytime* discussions and brainstorming sessions that have taught me many detailed aspects of digital design. Khanh's modesty and helpful nature are an inspiration. Many thanks to Ivan Seskar for his timely help and support.

Working at WINLAB would not have been half as enjoyable without my friends; Akshay, Mohit, Madhura, and Prashant. A special thanks to my roommates; Arjun Adimari, Pandeyji, Pompy, and Srini, for adding the fun quotient to my life at Rutgers.

Most importantly, I would like to thank my family. I cannot even imagine pursuing my dreams and ambitions without the unconditional love, support, and encouragement of my parents; Mrs. Manjiri Sarode and Mr. Anant Sarode. I owe my every success to them. Many thanks to my brother, Swatantra, for taking up my share of responsibility back at home. Last but not least, I would like to thank my fiancée, Poonam Deshmukh, for her patience and sacrifices, and always being there for me.

## Table of Contents

| Abstract                                                                  |  |  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|--|--|

| Acknowledgements                                                          |  |  |  |  |  |

| List of Tables                                                            |  |  |  |  |  |

| List of Figures                                                           |  |  |  |  |  |

| <b>1.</b> Introduction                                                    |  |  |  |  |  |

| 1.1. Software Defined Radio                                               |  |  |  |  |  |

| 1.2. Factors Driving the SDR                                              |  |  |  |  |  |

| 1.2.1. Short Term Driving Factors                                         |  |  |  |  |  |

| 1.2.2. Long Term Driving Factors                                          |  |  |  |  |  |

| 1.3. True SDR versus ASIC: the flexibility-performance gap                |  |  |  |  |  |

| 1.4. Bridging the gap: a hardware-oriented, programmable SoC solution $6$ |  |  |  |  |  |

| 1.4.1. Introducing Our Solution – Background and Overview of the Thesis 7 |  |  |  |  |  |

| 2. Requirements of Flexible Baseband Processing for Cognitive Radio       |  |  |  |  |  |

| Applications and their Implications                                       |  |  |  |  |  |

| 2.1. The Requirements                                                     |  |  |  |  |  |

| 2.1.1. Platform-based Paradigm                                            |  |  |  |  |  |

| 2.1.2. Programmability/Configurability                                    |  |  |  |  |  |

| 2.1.3. Dynamic Reconfigurability                                          |  |  |  |  |  |

| 2.1.4. Multiple Simultaneous Traffic Flows                                |  |  |  |  |  |

| 2.1.5. Resource Virtualization and QoS guarantees                         |  |  |  |  |  |

| 2.1.6. Throughput, Real Time Constraints and Power Efficiency $\ldots$ 15 |  |  |  |  |  |

| 2.2. Implications of the Requirements                                     |  |  |  |  |  |

|    | 2.3. | Related Work                                                        | 17 |  |  |  |

|----|------|---------------------------------------------------------------------|----|--|--|--|

| 3. | The  | Framework: Virtual Flow Pipelining                                  | 20 |  |  |  |

|    | 3.1. | Divide and Conquer Approach: Task Level Programmability with Coarse |    |  |  |  |

|    |      | Grain PEs                                                           | 20 |  |  |  |

|    | 3.2. | What is a Virtual Flow?                                             | 22 |  |  |  |

|    |      | 3.2.1. Pipelining: Exploitation of Task-level Parallelism           | 23 |  |  |  |

|    |      | 3.2.2. Virtual Flow Pipelining Overview                             | 24 |  |  |  |

|    | 3.3. | How are Virtual Flows Created? – The VFP Programming Model          | 25 |  |  |  |

|    |      | 3.3.1. Representing the Virtual Flow Program                        | 26 |  |  |  |

|    |      | 3.3.2. Features of the Programming Model                            | 26 |  |  |  |

|    | 3.4. | VFP Mechanisms                                                      | 27 |  |  |  |

|    |      | 3.4.1. Control-flow Sequencing and Data Communication               | 27 |  |  |  |

|    |      | 3.4.2. Synchronization                                              | 28 |  |  |  |

|    |      | 3.4.3. Scheduling                                                   | 29 |  |  |  |

|    |      | 3.4.4. Context Switching                                            | 31 |  |  |  |

|    | 3.5. | . Putting it All Together – The Layered Radio Perspective           |    |  |  |  |

|    | 3.6. | Correlating the VFP Framework and the Requirements                  | 34 |  |  |  |

| 4. | Virt | Virtual Flow Pipelining based SoC Architecture                      |    |  |  |  |

|    | 4.1. | Preliminaries                                                       | 36 |  |  |  |

|    |      | 4.1.1. Control-code Memory Structures                               | 36 |  |  |  |

|    |      | 4.1.2. VFP Control Mechanisms                                       | 40 |  |  |  |

|    | 4.2. | Distributed-Control Approach                                        | 43 |  |  |  |

|    |      | 4.2.1. Distributed-control SoC Organization                         | 43 |  |  |  |

|    |      | 4.2.2. Issues with the Distributed Approach                         | 44 |  |  |  |

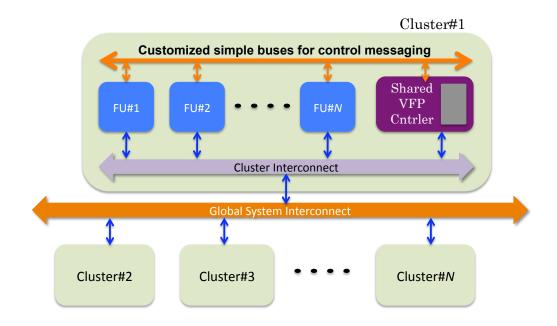

|    | 4.3. | Clustering-based SoC Organization                                   | 47 |  |  |  |

|    | 4.4. | Shared VFP Controller                                               | 48 |  |  |  |

|    |      | 4.4.1. Control-code Memory Organization                             | 48 |  |  |  |

|    |      | 4.4.2. Parallelism among the VFP functions                          | 49 |  |  |  |

|    |                                        | 4.4.3.                                            | VFP Controller Architecture                 | 50 |  |  |

|----|----------------------------------------|---------------------------------------------------|---------------------------------------------|----|--|--|

|    | 4.5.                                   | . Control Communication Interconnect              |                                             |    |  |  |

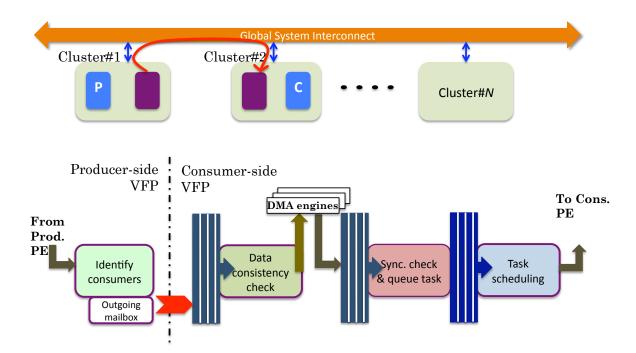

|    | 4.6.                                   | . Clustering-based Producer-Consumer Interactions |                                             |    |  |  |

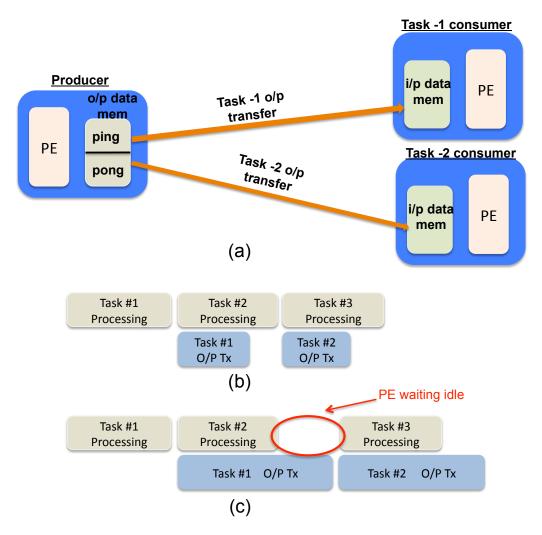

|    |                                        | 4.6.1.                                            | Intra-Cluster Producer-Consumer Interaction | 54 |  |  |

|    |                                        | 4.6.2.                                            | Inter-Cluster Producer-Consumer Interaction | 55 |  |  |

| 5. | Imp                                    | lemen                                             | tation and Performance Results              | 58 |  |  |

|    | 5.1.                                   | Imple                                             | mentation                                   | 58 |  |  |

|    |                                        | 5.1.1.                                            | Hardware Complexity                         | 58 |  |  |

|    | 5.2. Evaluation Metrics and Parameters |                                                   |                                             |    |  |  |

|    |                                        | 5.2.1.                                            | PE Utilization                              | 59 |  |  |

|    |                                        | 5.2.2.                                            | VFP Controller Idle Time                    | 60 |  |  |

|    |                                        | 5.2.3.                                            | PE Throughput                               | 60 |  |  |

|    | 5.3.                                   | Performance Results                               |                                             |    |  |  |

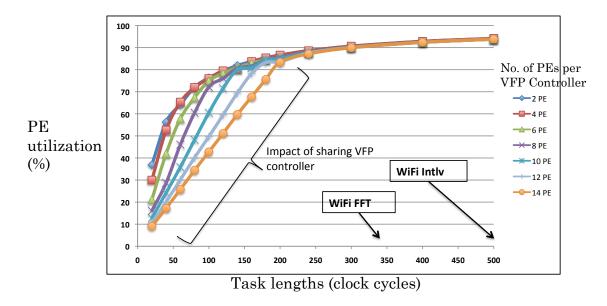

|    |                                        | 5.3.1.                                            | PE Utilization – No Data Transfer           | 61 |  |  |

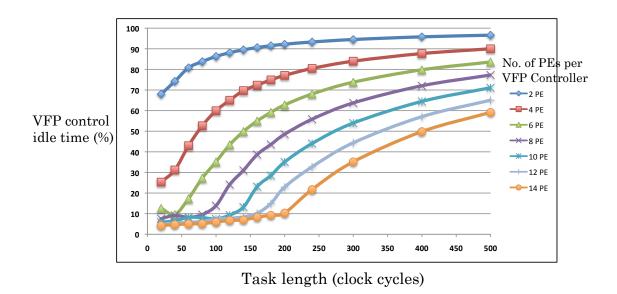

|    |                                        | 5.3.2.                                            | VFP Controller Idle Time                    | 63 |  |  |

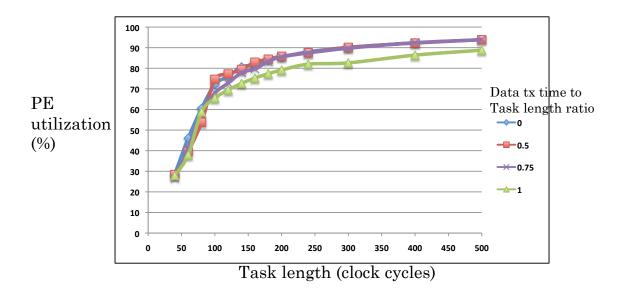

|    | 5.4.                                   | Impac                                             | t of Data Transfer                          | 64 |  |  |

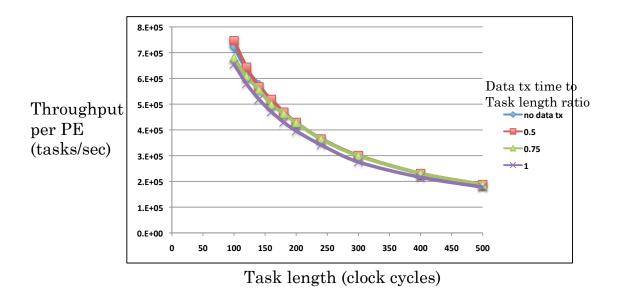

|    | 5.5.                                   | PE Tł                                             | aroughput                                   | 67 |  |  |

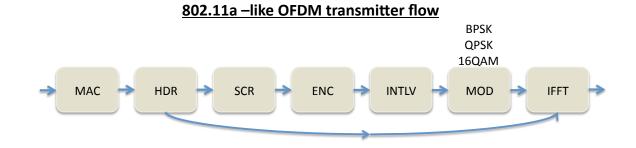

|    | 5.6.                                   | Real I                                            | Life Application – 802.11a                  | 68 |  |  |

| 6. | Con                                    | clusio                                            | n and Future Work                           | 71 |  |  |

| Re | <b>References</b>                      |                                                   |                                             |    |  |  |

## List of Tables

| 5.1. | Throughput Results for | : 802.11a-like | OFDM Flows |  | 70 |

|------|------------------------|----------------|------------|--|----|

|------|------------------------|----------------|------------|--|----|

# List of Figures

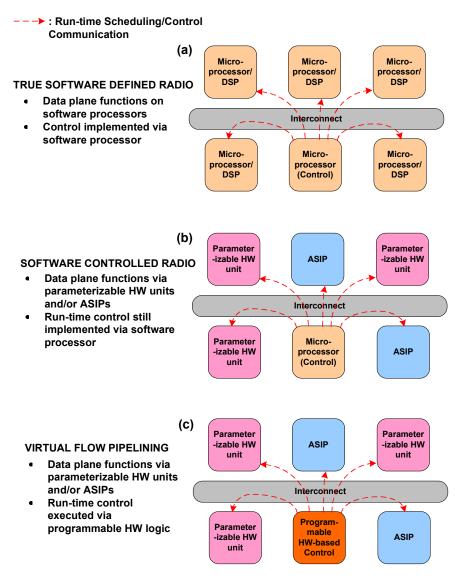

| 1.1.  | SDR v/s SCR v/s VFP                                                             | 7  |

|-------|---------------------------------------------------------------------------------|----|

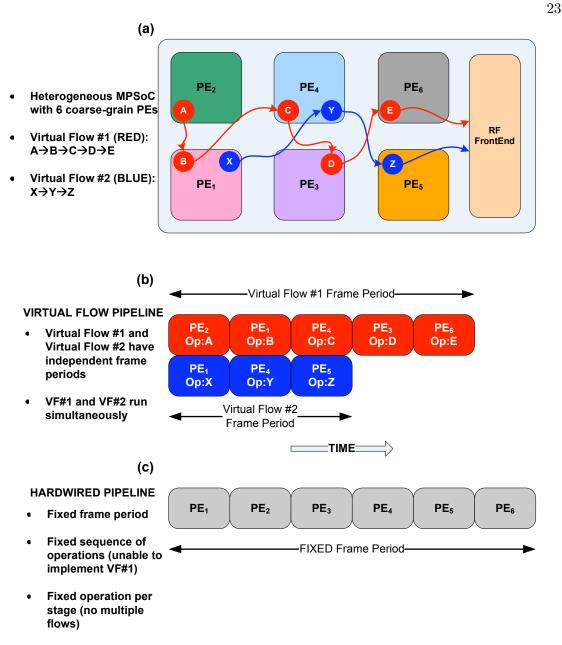

| 3.1.  | Virtual Flow Pipelining – Abstract View                                         | 23 |

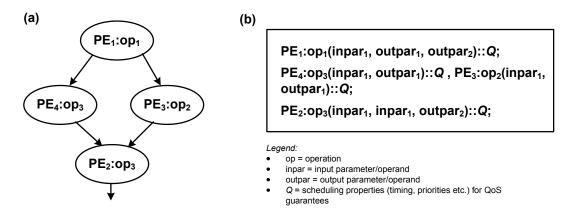

| 3.2.  | VFP Programming Model                                                           | 26 |

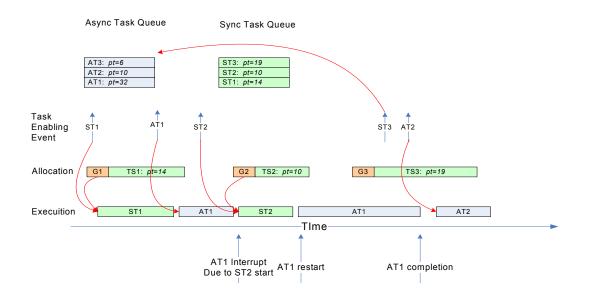

| 3.3.  | VFP Scheduling Policy                                                           | 30 |

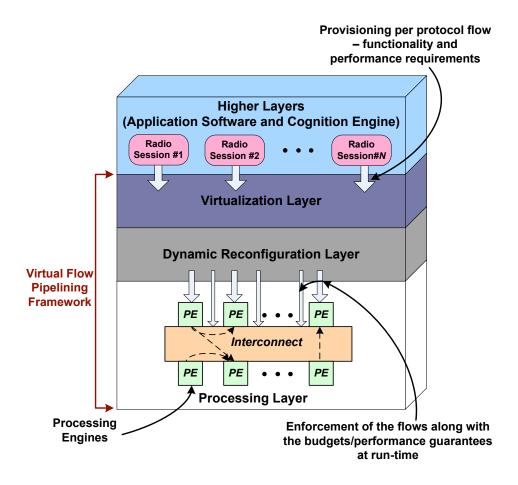

| 3.4.  | Layered Radio Architecture                                                      | 32 |

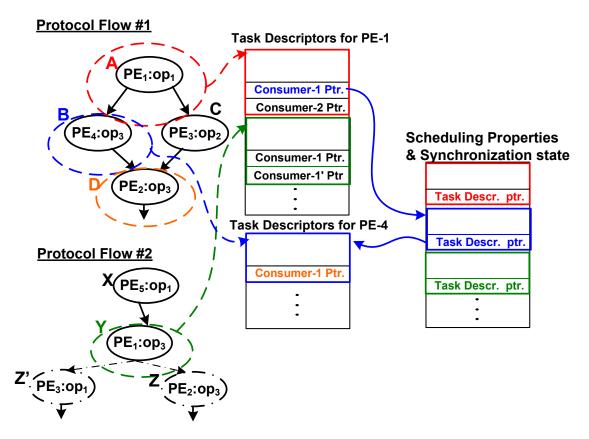

| 4.1.  | Control Code Data Structures                                                    | 37 |

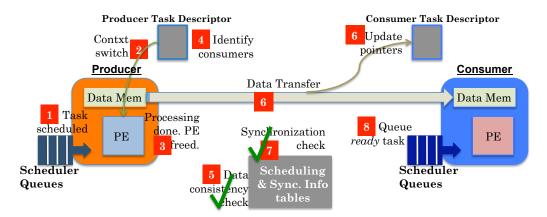

| 4.2.  | VFP Control Mechanisms                                                          | 41 |

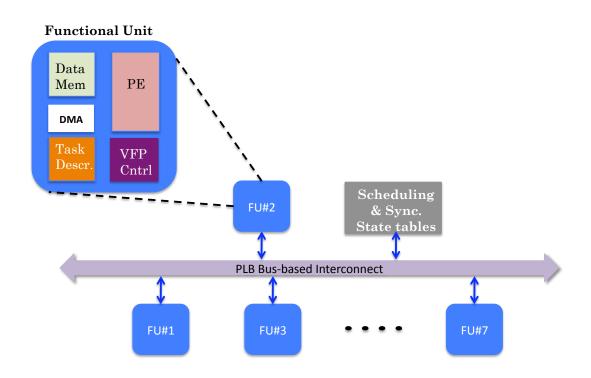

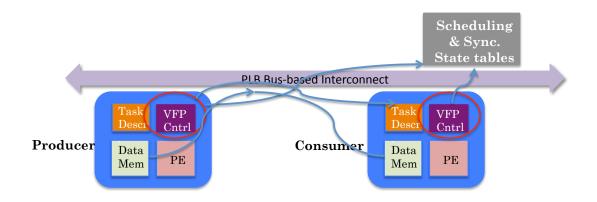

| 4.3.  | Distributed-Control SoC Organization                                            | 43 |

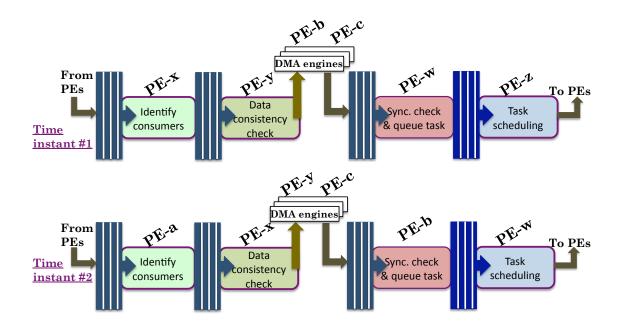

| 4.4.  | Issues with the Distributed-Control Organization                                | 46 |

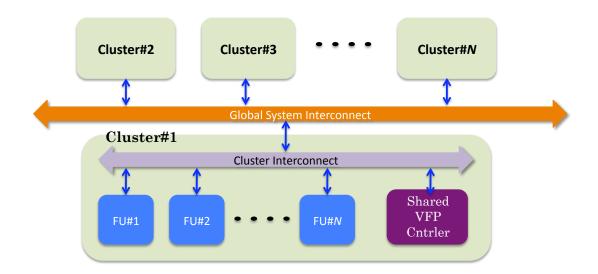

| 4.5.  | Clustering-based SoC Organization                                               | 47 |

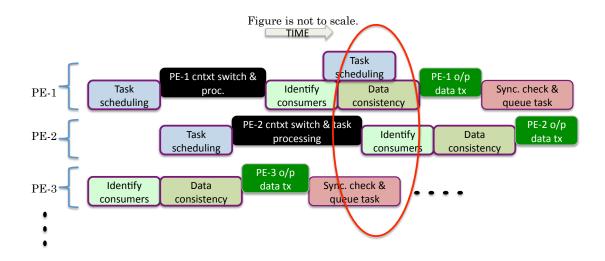

| 4.6.  | Parallelism Among VFP Mechanisms                                                | 50 |

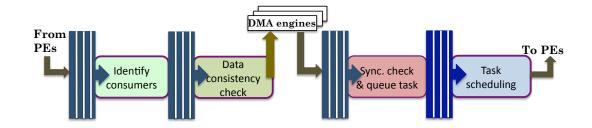

| 4.7.  | Shared VFP Controller Pipelined Architecture                                    | 51 |

| 4.8.  | Parallelism Exploited by the VFP Controller Pipeline                            | 51 |

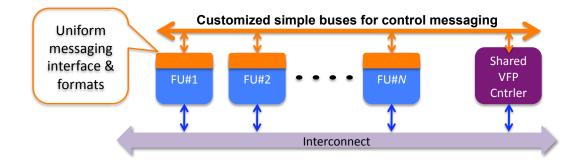

| 4.9.  | VFP-FU Control Communication Interconnect                                       | 53 |

| 4.10. | Inter-cluster Producer-Consumer Interaction                                     | 56 |

| 4.11. | Complete Clustering-based SoC                                                   | 57 |

| 5.1.  | PE Utilization v/s Task Processing Time (No Data Transfer) $\ . \ . \ .$ .      | 62 |

| 5.2.  | VFP Controller Idle Time v/s Task Processing Time $\ldots \ldots \ldots \ldots$ | 63 |

| 5.3.  | PE Utilization v/s Task Processing Time (Impact of Data Transfer) $\ .$ .       | 65 |

| 5.4.  | Impact of Data Transfer                                                         | 66 |

| 5.5.  | PE Throughput v/s Task Processing Time                                          | 67 |

| 5.6.  | Real Life Application – 802.11a - like OFDM Transmitter                         | 68 |

# Chapter 1

## Introduction

Evolution of wireless devices is at a very exciting stage. We are now amidst of an accelerating trend towards intelligent devices, such as smart phones, that converge services and functionality earlier provided by cell phones, tablet computers, MP3 players etc. Maximizing the efficacy of these devices calls for providing wireless connectivity across space and time. In fact, applications in the near future will demand availability of ubiquitous connectivity in a seamless manner. However, providing such connectivity is difficult because there exists no single universal wireless technology that covers the entire world. This recent and projected growth in the demand for wireless connectivity together with the emergence of diverse *radio access technologies* (RATs) and standards, has opened significant opportunities and challenges in the wireless communication devices industry.

Future wireless devices must incorporate multiple communication functions provided via different standards, e.g. personal navigation (GPS), personal area networking (Bluetooth, Zigbee etc.), local area networking (802.11a/g/n), TV reception (MediaFLO, DVB-H/T etc.), and mobile cellular networking (LTE, WiMax) on a single device. With this increase in the ways and means by which people need to communicate – i.e. data communications, voice communications, video communications, broadcast messaging, command and control communications, emergency response communications, etc. – modifying radio devices easily and cost-effectively has become *business critical*. The emerging 4G wireless standards itself impose heterogeneous wireless communication environments where the infrastructure will be built with devices using different radio access technologies, and operating at different spectrum bandwidth. Furthermore, the cognitive radio technology, seen as the solution to deal with the problem of spectrum scarcity, demands broader flexibility and agility features from the wireless devices.

### 1.1 Software Defined Radio

Software defined radio (SDR) [1] technology is seen as the solution for providing the flexibility, cost efficiency and power to drive communications forward, with wide-reaching benefits realized by service providers and product developers through to end users. Here we shall define a Software Defined Radio and discuss the factors/benefits that drive this technology. Understanding these driving factors is vital to be able to appreciate the implications they have on the requirements/specifications for these devices (discussed in Chapter 2).

Simply put, a SDR is defined[2] as a *Radio in which some or all of the physical layer functions are Software Defined*; where Software Defined refers to *the use of software processing within the radio system or device to implement operating (but not control) functions.* This definition implies that the complete physical layer processing for the SDR is performed by software routines running on processor(s). A later discussion will explain how our programmable solution contrasts with the SDR notion. But, for now we put forth the driving factors for the SDR because these are the very same factors that drive a programmable system-on-chip (SoC) solution that we propose.

## **1.2** Factors Driving the SDR

The factors driving the SDR can be divided into two broad categories: *Short Term drivers* and *Long Term drivers*. Short Term drivers refer to the factors that influence the adoption of this technology in the near future, i.e., 5 years or so. On the other hand, Long Term refers to the factors and visions, related to the advanced wireless market in the distant future, for which the SDR can act as a key enabling technology.

## 1.2.1 Short Term Driving Factors

Benefits of SDR will be seen throughout the wireless industry chain – from productbased and service-based providers through end users of the devices and services.

#### Factors affecting network operators

Network operators have to deal with the constant evolution of standards and technologies. For example[3], LTE Advanced is currently in the works and it features a full OFDMA uplink physical layer as opposed to SC-FDMA for LTE. Such evolutions take place over a short period of time – sometimes as low as two years – which is short in comparison to the time it takes to develop, test and validate equipment.

For network operators, SDR enables new features and capabilities to be added to existing infrastructure – increasing the *time-in-market* for their purchased equipment. This allows network operators to quasi-future proof their networks – saving major new capital expenditures. The ease of upgrades means faster deployment of new standards and services. The use of a common radio platform for multiple markets, significantly reducing logistical support and operating expenditures.

## Factors affecting product-based providers

SDR approach implies the use of a common platform for implementation of diverse wireless technologies and standards. The impact of such a platform-based approach is that it will dramatically reduce the *time-to-market* for new products. By facilitating extensive reuse, this approach will also reduce the effort involved in development and testing of new products, thus lowering the costs. Thus, infrastructure equipment vendors, system integrators and terminal device makers can all roll out "family" of radio products e.g. macrocells, femtocells etc. in a fast and cost effective manner. New algorithms and software will be targeted for a proven framework, thus making the process of estimating their performance, latency etc. not only easier but also more deterministic. It also makes debugging and upgrading devices easy.

Furthermore for terminal device manufacturers, SDR also acts as a enabling technology towards the need for a cost-effective multi-modal solution – one that can provide connectivity across heterogeneous RATs. The benefit of providing the ability to evolve/upgrade with improvements in standards applies here as well.

#### Factors affecting end-users

For end-users, the SDR offers ubiquitous wireless connectivity - i.e. the means to connect using whatever means (RATs, bands etc.) available. The easy-to-upgrade feature of SDRs imply a longer lifetime for the mobile devices - thus reducing costs.

#### **1.2.2** Long Term Driving Factors

Software Defined Radios are seen as the potential building blocks for advanced wireless technologies – Adaptive Radio, Cognitive Radio[1, 4] – which act as a major driving factor for SDR technology from a long term perspective.

The next couple of paragraphs very briefly introduce the advanced adaptive and cognitive wireless technologies, which themselves are vast topics of very active research.

## Advanced Wireless Technologies – Adaptive and Cognitive Radios

Adaptive radio is a technology in which communications systems have a means of monitoring their own performance and modifying their operating parameters to improve this performance. The use of SDR technologies in an adaptive radio system enables greater degrees of freedom in adaptation, and thus higher levels of performance and better quality of service in a communications link.

Furthermore, building on adaptive radios, the cognitive radio technology[5, 1] offers to solve the problem of efficient utilization of the radio spectrum, which has become critical in order to accommodate the exponential growth of wireless devices in the future. These future cognitive radios will perform continuous or frequent sensing of their network environment (spectrum, interference conditions etc.) and dynamically change (their RAT, operating frequency, power control etc.) to make optimum use of the available spectrum while providing seamless connectivity.

## SDR – Key Enabler for Advanced Wireless Technologies

In order to accomplish these advanced features, we need wireless devices that can adapt to a variety of radio interference conditions and protocol standards. Such a radio should be capable of dynamic physical layer adaptation via scanning of available spectrum, selection from a wide range of operating frequencies, rapid adjustment of modulation waveforms and adaptive power control.

SDR technology has the capability of providing the physical layer flexibility required for realizing these technologies. Thus adoption of the SDR technology is critical in allowing end-users to make optimal use of available frequency spectrum and wireless networks, with a common set of radio hardware.

Having discussed the positive benefits driving the SDR concept, we now introduce the challenges and difficulties involved in realizing this technology. From hardware design point of view, the challenges are enormous, both on the *radio-frequency* (RF) and analog front-end and on the digital baseband side. This thesis focusses on and discusses only the digital baseband challenges and solutions. The following section is aimed at discussing, from a high-level perspective, the difficulties of adopting the SDR approach as well as at presenting an overview that can act as a platform for introducing our work. More details of related work, their aspects and contrast with our solution will be covered in Chapter2 after we explain the specifications/metrics for comparison.

## 1.3 True SDR versus ASIC: the flexibility-performance gap

The discussion up to this point focussed only on the features, flexibility and driving factors related to future wireless devices. With this myopic view, fully programmable SDRs seem to be the dream solution. In fact SDR has been a dream for the last decade – without any solutions available in the volume market. The major gap between this dream (SDR) and reality (traditional ASICs) is performance and power.

As we have already seen, the need for adaptability, reduced *time-to-market*, longer *time-in-market* etc. all point against the full custom ASIC solution. But the ASIC approach is capable of delivering on the low-cost, performance and power requirements of future wireless protocols. Resorting to a technique of building multi-modal radios

comprising of multiple ASIC modules (one for each standard), is not a feasible solution. The current requirement itself will demand at least 16 baseband modules[6], which will result in heavy silicon and prohibitive costs, let alone the incapacity to evolve with the volatile standards.

Fully software programmable solutions built using CPUs - true SDR - depicted in Fig.1.1a, although providing maximum flexibility, are compute centric. They are not suitable for delivering the requirements of the network-centric world - i.e.[7] a short sequence of data manipulation operations, sequential nature with high data dependency. Moreover, these solutions are extremely power hungry.

## 1.4 Bridging the gap: a hardware-oriented, programmable SoC solution

To keep the cost low to enable a deployment model that can provide the capacity for future data traffic requirements while allowing evolution with wireless standards creates a dichotomy that can be resolved through a new generation of *platform-based Systemon-Chip* (SoC) devices that combine aspects of programmable devices and ASICs in a balanced manner.

A key aspect to consider is that providing wireless devices with flexibility within certain reasonable bounds is enough. A fully programmable solution is an overkill. Metaphorically, if the problem is undoing a screw, and the type of screw head is unknown, then carrying a single screwdriver with modifiable screw-ends is enough. Carrying a complete toolset is not required. A solution that provides limited versatility – to support diverse RATs and adapt to their evolutions – is enough.

Depicted in Fig.1.1b, the Software Controlled Radio [2] concept, i.e., using a mix of parameterizable hardware functional units (FUs) and application specific instruction set processors (ASIPs) under the control of a central software programmable CPU, is a step in right direction for achieving the required balance. Nevertheless, for reasons discussed in Section 2.2, the software controlled approach cannot deliver the performance and power requirements. This approach proves even weaker, when we consider support

for virtualized multiple traffic flows etc., which are required by the advanced wireless technologies.

Figure 1.1: SDR v/s SCR v/s VFP

## 1.4.1 Introducing Our Solution – Background and Overview of the Thesis

To summarize the implementation challenges, they can be broadly categorized under RF and Analog Front-end design; and Digital Baseband Design. As mentioned previously, our work focusses on the Digital Baseband part. In fact, the Digital Baseband Design challenges can be further classified as;

- related to processing/functional units: These deal with the design of the data plane processors/functional units. The issues here involve analysis and exploration of algorithms, their hardware/software partitioning and implementation, making them parameterizable and flexible etc.

- 2. related to system integration, programmability and run-time control: This deals with the challenges in creating a framework, which provides all the required mechanisms for programmability, scheduling of the numerous different tasks running on very different operating units and executing the program within a real-time constraint, while accurately resolving the dependencies and exploiting parallelization possibilities. This challenge is precisely the the scope of our work.

This thesis proposes a programmable SoC architecture, based on a novel Virtual  $Flow \ Pipelining \ (VFP)[7]$  framework (elaborated in Chapter3), wherein the system control, while being programmable, is implemented as dedicated hardware – not using a central software programmable CPU with a real time operating system. Fig.1.1c depicts the concept. We refrain from calling our solution a SDR or SCR, which implies a software programmable CPU based control. Instead we have OS-like hardware based support that executes *soft* control flow programs. We aim at striking a favorable balance between flexibility and performance. An important point is that the VFP based approach targets better performance and power than the Software Controlled approaches, while providing the required flexibility.

The architecture proposed in this work is a clustering-based architecture which aims at striking a balance between fully distributed and fully centralized approaches. The architecture uses distributed-shared controllers with a scheme for message passing to handle scalability. This enables us to achieve scalability with a reasonable hardware overhead. Another major aspect, of this work has been the architecture and design of the shared controller. The challenge was to enable the controller to support maximum number of processing elements with minimum impact on performance. This has been achieved by designing an asynchronous pipelined microarchitecture for the controller that can simultaneously serve multiple processing elements. Identifying the parallelism in the VFP control mechanisms and exploiting it using the pipelined architecture is a major contribution of this work. Furthermore, a new interconnect for control communication was designed to improve performance. The concept of IDs is introduced and uniform messaging schemes/formats and interfaces for the processing elements are designed for communication with the VFP controller. This work has implemented the complete system in synthesizable *hardware description language* (HDL), enabling bit and cycle accurate simulations and performance analysis. During the coarse of this work, 802.11a-like OFDM based baseband processing has been successfully implemented on the system[8]. More details will be covered in later chapters.

The organization of the rest of the thesis is as follows; based on the driving factors discussed in this chapter, Chapter 2 will discuss the specific requirements/specifications of the programmable radio devices. Using these specifications as criteria, Chapter 2 will also discuss some of the existing and related work/solutions as well as compare and contrast them with our solution. Chapter 3 will describe the Virtual Flow Pipelining architectural framework and programming model. Chapter 4 will delve into the architecture of the SoC and controller. Experimentation and performance analysis is covered in Chapter 5. Finally, Chapter 6 concludes with the insights and scope for future work.

## Chapter 2

# Requirements of Flexible Baseband Processing for Cognitive Radio Applications and their Implications

In Chapter 1 we discussed the factors driving the need for flexible solutions for the wireless radio processing. We also introduced the challenges involved in realizing such a solution, namely the performance-flexibility gap between the established ASIC approach and the desired SDR approach. This chapter will identify and present the specific requirements of a flexible solution. The requirements presented in this chapter can be thought of as higher level specifications for the architecture and will also act as guidelines for drawing comparisons with other related work.

As mentioned in the previous chapter, this work focuses only on the digital baseband challenge of the radio system. More specifically, we concentrate on the system integration, programmability and run-time control/scheduling of the digital baseband. Hence, the next section will focus more on the framework requirements rather than those of constituent data-plane processors and/or hardware functional units. Later in 2.2 we discuss the impact of these requirements on the architectural decisions.

## 2.1 The Requirements

Before, we begin elaborating the requirements it is important to mention that, from an application point of view, we are targeting a system that together with the short term SDR factors, can also support the cognitive and adaptive radio applicative scenarios (long term factors of Chapter 1). Broadly speaking the goal is to create a *Dynamically Reconfigurable Platform*[9]. The following sections put forth the requirements and their justification for such a system.

### 2.1.1 Platform-based Paradigm

The realization of the flexible wireless digital basebands calls for an evolution from the *Intellectual Property* (IP) reuse paradigm to a platform reuse paradigm[9]. Simply putting, a platform is a SoC communication structure on which different IP can be seamlessly connected. [10] defines a platform as a *layer of abstraction with two views*. The upper view allows an application to be developed without referring to the lower levels of abstraction. The lower view is a set of rules that classify a set of components belonging to the platform.

The main requirements that a platform targeting digital baseband must provide are:

- 1. A network-centric framework that provides separation between communication and computation aspects of the executed protocols. The communication scheme architected must be independent of the type of interconnect used (bus, crossbar, etc.), thus providing support for the *Globally Asynchronous Locally Synchronous* (GALS) approach, which is now imperative for seamless IP integration in large SoCs.

- 2. A programming model or *Application Programming Interface* (API) which is a high level interface to the hardware. This provides the required upper view or level of abstraction for easily programming the system. This decouples the programming aspect of the platform from the microarchitecture aspects as well as makes the programs independent of the actual functional units or processors used for executing the data operations.

- 3. Integration of heterogeneous processing engines within unified programming paradigm. This is even more important because there is a consensus appearing[9][11][12][13][14], which states that the way of solving the tradeoffs between power, performance and flexibility is the use of *heterogeneous multi-processor SoC* (MPSoC) based solutions (discussed in section 2.2). Therefore, a platform should provide the uniform rules/interface to seamlessly integrate these heterogeneous computing cores. This will help create a library of components that are compliant with the platform, thereby increasing their reusability and making system integration faster

and easier. Development and/or enhancements of the IP components can be done completely independently and in parallel – provided the platform/interface rules are obeyed.

- 4. System integration and verification phases becomes straightforward. IPs can be developed independently without caring about communication with other IPs. This boosts the reusability of cores and enable developing families of products. Thus, reducing the time to market and *non-recurring engineering* (NRE) costs.

- 5. Programmability is facilitated by the common platform programming model or API. This makes mapping of protocols onto the hardware easy and reconfigurable. Thus, a platform-based approach lends itself to the realization of a flexible solution. It also enhances the software reusability and makes upgrades easy.

## 2.1.2 Programmability/Configurability

We have already mentioned that there is a growing demand by consumers for connectivity everywhere. This demand, together with the goals of small size, low cost, and power efficiency are driving the need for multi-modal solutions that are implemented as a common configurable hardware platform (as opposed to having independent hardware per RAT). In fact this is the very basic idea behind the concept of SDR.

Furthermore, there is practically no doubt that the MPSoC ([9][11][15][13][16][14]) is a promising approach to solve the challenge of improving the contradicting objectives of performance, power efficiency and flexibility.

We must be able to program the MPSoC in order to execute a complete wireless communication protocol. Moreover, changing the configuration/program must enable the implementation of different protocols on the same platform. The following points explicitly define the properties of the required programmability/configurability and degrees of freedom, which are required to be provided by the platform architecture in order to support diverse RATs.

**Configurability of the Computing Cores:** This degree of freedom primarily deals with the computational aspect of the platform. The MPSoC approach involves a

new step in programming of the chip, where constituent computations/functions of the protocol must be identified, extracted and mapped onto the constituent processing elements (PE). Thus the different PEs that make up the MPSoC must be configurable computing cores – i.e. parameterizable hardware functions for computational intensive tasks that need less flexibility (e.g. FFT) or general purpose RISC processors or application specific instruction set processors (ASIP). The platform programming model must provide uniform way – irrespective of the type of PE – for selecting the required configuration/function of the PE, as per the protocol under execution. The nature of this programmability/configuration depends on the granularity of PEs – coarse-grain or fine-grain. For example, while executing a WiMAX transmitter on a MPSoC with coarse-grain PEs, the interleaver ASIP must be configured to perform the WiMAX interleaving algorithm. This configuration must be changed to run the 802.11a interleaver algorithm when the device has to transmit 802.11a packets.

- **Configurability/Programmability of the Control-Flow:** The platform must have a programmable control-flow as per the protocol being implemented. This degree of freedom deals with the programmable nature of the sequence of the constituent computations/functions of the protocol that being implemented on the PEs. The programming model must provide flexibility in defining the producer-consumer relations, which must be supported by the hardware platform in the form of configurable communication structure.

- Freedom to Upgrade/add FU Configurations: This degree of freedom enhances the ability of the platform to evolve with emerging protocols, specifically when it needs a completely new computational task not considered at design time. This aspect applies only to the programmable processor-based components of the MPSoC, where new programs on the CPUs will manifest as new configurations. A thorough analysis of the value and affordability of the degree of programmability required for different functions needs to be performed. For example, a configurable hardware engine capable of multi-length (over a wide range) multi-stream FFT

core is enough – dedicating a CPU for the FFT function is neither affordable nor does it add any value.

All these above mentioned of degrees of freedom, together with the ability to exploit task-level parallelism, must be built into the programming model.

### 2.1.3 Dynamic Reconfigurability

The technologies of Adaptive Radio and Cognitive Radio take the programmability/configurability requirement to the next level. The solutions for efficient spectrum usage need the wireless devices to dynamically reconfigure based on the changes in the radio environment. In fact, this agility in adaptation is required on a per-packet basis.

This requirement of *dynamic reconfigurability at run-time on a per-packet basis* is also driven by the user demand for seamless connectivity when moving across heterogeneous RATs. In fact this requirement for seamless connectivity has even more implication on the requirements, discussed in the next section.

### 2.1.4 Multiple Simultaneous Traffic Flows

Consider the following applicative scenario: A person starts a video conference with a friend while leaving office in a business center, then takes the train to go home in the suburbs. During the person's journey the video conference must be continued without any disconnections. This demand of seamless and ubiquitous connectivity for users – during the course of an active application – needs to be supported by *soft vertical handovers* across the diverse RATs that are available. The implications of this on the digital baseband platform is that it needs to support at least 2 diverse RATs simultaneously [9][17].

In fact users will be running multiple radio applications simultaneously on the same wireless device - e.g. GPS and Bluetooth file transfer to a friends phone together with data download from the internet. Such scenarios drive the need for more than 2 simultaneous diverse traffic flows on the platform. This support for independent radio links is also needed by the future cognitive radios in order to communicate (control and

data) and co-operate with multiple radio neighbors for opportunistic spectrum usage as well as formation of ad hoc networks.

#### 2.1.5 Resource Virtualization and QoS guarantees

Satisfying the previous two requirements - simultaneous support for multiple traffic streams and dynamic (per-packet) reconfigurability - with lowest cost requires sharing the hardware resources of the platform. At the same time every radio session is also required to adhere its relevant real-time constraints. This poses a difficult system problem - as satisfaction of temporal constraints depends on the resource availability, resource sharing can make the temporal behavior of each radio session (or traffic flow) depend on the behavior of all other simultaneous radio sessions in the system, which is difficult to predict since the combinations of radio sessions change dynamically.

This drives the need for virtualization support that will isolate each radio session such that it only sees a fraction of the platform resources. It will also protect the higher protocol layers from the changes in radio access features and loading on the hardware[7][18].

Thus the platform API layer or programming model will have to incorporate virtualization features. Primarily, this involves handling the hardware processing resource allocation for enforcing the QoS guarantees across the multiple traffic sessions while maintaining isolation between them. Thus from the point of view of higher layers, each session treats its share of bandwidth as a separate (virtual) channel that is unaware of other sessions in the system.

## 2.1.6 Throughput, Real Time Constraints and Power Efficiency

The throughput requirements of digital baseband processing for 4G devices are in the range of 100Mbps data rates which translates to approximately 500 giga operations per second (GOPS)[11]. Moreover, this high throughput must be delivered within a minimal power budget of around 200mW[11][19].

In addition to the throughput requirements, most of the processing is bound by tight real-time constraints; e.g. WLAN packet retransmission has strict deadline (SIFS time) that is 16 micro seconds, which involves the entire receive and transmit paths. A failure in meeting these real time constraints will cause the processing to be worthless. These type of strict latency and timescale requirements, makes the scheduling and execution of the tasks on the platform challenging.

### 2.2 Implications of the Requirements

#### Heterogeneous MPSoC

In order to provide required performance within the power budget, the solution has to be MPSoC based, as multiple simpler cores running at lower frequency are more power efficient. Moreover, the functional analysis[14] of the tasks performed in the the digital baseband processing has revealed a clear diversity of computational load and flexibility requirements. Hence, a *heterogeneous MPSoC* is the best suited solution for our requirements of sections 2.1.2 and 2.1.6 – providing flexibility only where it adds value and can be afforded.

#### **Run-time Task Scheduling**

The requirements of data dependent control-flow, dynamic (per-packet) reconfigurability (section 2.1.3), and maintenance of real-time constraints and performance guarantees across multiple radio sessions (sections 2.1.5, 2.1.6); on a heterogeneous MPSoC cannot be satisfied by compile-time scheduling. This dictates the need for run-time scheduling.

## Hardware Support for Programmability/Scheduling

Providing this run-time scheduling support is difficult as well as inefficient with a software controlled approach. The software control implies that the scheduler is implemented as software on a CPU and will require a *real time operating system* (RTOS) for sharing the CPU processing power. Running the RTOS will itself consume considerable energy. Moreover, the synchronization between the control code (running as software) and the processing elements (performing data-plane processing) will be interrupt based. To avoid high interrupt overheads, the execution time of the PEs must at least be a degree higher (thousands of cycles) than the interrupt latencies (hundreds of cycles) of the operating system environment. As an interesting example[20], consider the interrupt latency is around 300 cycles and 50,000 interrupts are generated per second, this overhead itself swallows 10% of the 150MHz processor resources. Also the delayed responses to the PEs will decrease the PE utilization as well as increase system latency.

Broadly speaking, the time scales of real-time operating system slices and CPU context switching in the software controlled environment are an order of magnitude larger than the ones required by the wireless protocol processing (tens of  $\mu$ s vs.  $\mu$ s)[7]. Hence, Software Controlled Radio platforms are not adequate for the multi-flow communication support since time slicing of processing resources will be inefficient and non-precise.

These implications drive the need for a architectural framework with hardware-oriented support for dynamic task scheduling/programmability on the heterogeneous MPSoC. This architecture must have mechanisms for efficient resource sharing, low overhead context switching, high utilization of PEs and exploiting the task-level parallelism inherent in wireless protocol processing. The *Virtual Flow Pipelining* (VFP) concept is a novel architecture framework that caters to these requirements and their implications.

## 2.3 Related Work

A number of architectures and implementations for flexible baseband processing are available in literature. But none of them cover all the requirements and their implications mentioned in the prior sections. We discuss some of these below.

The work by G. Fettweis *et al* [13][21] incorporates the use of a dedicated hardware unit for programmability/scheduling with real-time support. This work is the most closely related to ours. But, unlike our scheme, they resolve their control dependencies in software. This causes stalling due to long interrupt latencies. Also they have a fully centralized approach for which the performance degrades for tasks that are smaller than 4000 clock cycle. As shown in Chapter 5, our performance is better with efficient support for short tasks. Also, their solution cannot support simultaneous multiple flows. In fact, as described in [22] they too resort to a software approach in order to support multiple flows. The good point about their work is that it is C-programmable.

Another interesting approach is by [40], where they have their control implemented using a SW programmable processor – but the processor is an application specific processor (ASIP), designed with special hardware supported instructions for scheduling etc. This gives the approach the programmability of a SW approach with better performance. However, as will be shown in Chapter 5 the performance is limited when compared to ours. Also, our argument is that we really do not need that much programmability.

The IDROMEL platform[17] from OpenAirInterface use a software based approach, but claims to performance by delocalizing part of the scheduling to local MIPS microprocessors – present in every processing block. They aim at support for only 2 simultaneous RATs – thus lacking support for virtualization.

[23] too has a distributed software based control with a MIPS processor embedded in every processing element. Real-time scheduling is achieved by avoiding the use of an operating system and interrupt based mechanisms. Instead a polling based event detection (per control processor) is used. Also, this is a homogeneous MPSoC solution, hence probably the MIPS based software control makes sense – complex scheduling techniques can be implemented. Support for multiple flows and virtualization is missing.

IMECs COBRA [24] is perhaps one solution that meets most of the requirements described in this chapter. But not many details about it are available in literature. It targets 4G giga-bit rates and claims support for multiple simultaneous radio sessions with real-time guarantees.

The architectures of PicoChip[25], Infineon's MuSIC[26] and Sandbridge's SB3011 platform[27] argue high computational performance and high flexibility. But they are all DSP-centered and accelerator-assisted with a centralized control – reconfiguration and scheduling is performed by one central software processor. This approach is not scalable and complex control strategies (pipelining, etc.) are difficult and inefficient to implement. Also reconfiguration is often slow.

SODA[28] too has CPU based control and scheduling. It also lacks support for

dynamic reconfiguration, multiple flows and virtualization. Moreover, its performance is limited – supports maximum of 24Mbps rate for the 802.11a protocol at 400 MHz. Our platform can achieve the same performance at just 100 MHz.

## Chapter 3

## The Framework: Virtual Flow Pipelining

The previous chapter elaborated on the requirements of digital baseband platforms for supporting future wireless technologies. We also discussed the implications of the requirements on the approach to be taken towards realization of the required features. Finally, with these guidelines for reference we evaluated some of the existing solutions in literature.

This chapter will elaborate on the specifications and features of the Virtual Flow Pipelining (VFP) framework, which is the basis for the programmable SoC architecture. As introduced in the Section 1.4.1, the VFP architecture framework addresses the workload characteristics of wireless communication protocols with hardware-based programmable control mechanisms that engage both hardware and software modules in a uniform manner in order to satisfy both functional and performance requirements. The following sections detail the features, the programming model, and the mechanisms of the VFP framework.

## 3.1 Divide and Conquer Approach: Task Level Programmability with Coarse Grain PEs

As per the arguments of Section 2.2 and [15, 9, 11, 12, 13, 14], we have concluded that the MPSoC is the most suitable approach for achieving the flexibility and performance requirements of emerging wireless protocols within the strict power budgets. The MPSoC approach brings with it the challenge of distributing the workload across its constituent *processing elements* (PEs) and programming the system.

#### Power related considerations

Before we can actually tackle programmability/scheduling related challenges we need to decide the nature of the PEs. This is an important design issue because it impacts the power efficiency of the system. Analysis ([29, 14, 30]) of the workload of wireless baseband processing has led to the realization that many of their constituent functional entities are similar – e.g. channel encoder/decoder, block interleaver/deinterleaver, modulator/demodulator, pulse shaping lter, and channel estimator. The specific algorithms that each of these entities performs – e.g. type of interleaving etc. – will depend on the standard/protocol being executed. Moreover, these different functional entities offer plenty algorithm/task level parallelism – implying each of these can be executed in parallel without intensive interactions. In fact, the analysis in [29] shows that in most computation intensive algorithms, the amount of memory access for internal computation is about 10 to 200 times greater than that for the communication with other algorithm blocks. It means that if a PE is strong enough to cover one entire signal processing algorithm, the amount of interprocess communication can be minimized.

Minimizing the amount of interprocess communication is important in a low power system because the energy cost of inter process communication (involving access to system interconnect etc.) is at least two times higher than that of internal memory access. This is the primary reason we choose to use coarse grained PEs.

## Throughput related considerations

From the view point of system throughput, the coarse grain PE is also a better choice because the communication delay between ne grain PEs degrades system throughput. Usually, the operation speed of the interprocess communication network is slower than the internal memory access. Furthermore, the interprocess communication time is not deterministic. So, the ne grain PEs must be scheduled under the assumption of worst case delay. These factors degrade achievable maximum system throughput, if fine grained PEs are used.

#### Flexibility related considerations

The use of coarse grained PEs, each executing specific tasks/algorithms, paves the way for the use of heterogeneous PEs. As discussed in Section 2.2, the diversity of computational complexity and flexibility among the functional tasks/algorithms further advocate this *divide-and-conquer* approach. It facilitates achieving flexibility while using specialized cores – which help achieve power efficiency by adding flexibility and/or computational power only when required and afforded.

Thus, with all these considerations, the VFP framework uses a heterogeneous MP-SoC approach with coarse-grain PEs, which can be configured to execute constituent tasks/kernels of the wireless protocol. These tasks are stitched together by another higher level of programmability, which in effect implements the intended wireless protocol.

## 3.2 What is a Virtual Flow?

The allocations of the share of platform hardware resources to a protocol flow, specifying the tasks involved, their sequence and performance requirements, in effect creates a *Virtual Flow*. Multiple such virtual flows can be supported by the VFP framework.

Consider a heterogeneous MPSoC that includes the PEs shown in Fig. 3.1a. This figure is meant to be an abstract view of the MPSoC platform, meant for building the notion of virtual flows and comparing it to the traditional hardwired pipeline. Details regarding the SoC organization, microarchitecture, interconnect etc. will be discussed in the next chapter.

Building on this abstract view, Fig. 3.1a shows two virtual flows being executed on the MPSoC. The blue path depicts virtual flow 1 (VF1) and the red path depicts virtual flow 2 (VF2). As can be seen each flow has its own sequence as well as different operations to be performed within each stage of the sequence. Also, both these flows coexist on the MPSoC platform concurrently, with their performance guarantees (QoS requirements) specified as part of the flow timings and priorities.

Figure 3.1: Virtual Flow Pipelining – Abstract View

## 3.2.1 Pipelining: Exploitation of Task-level Parallelism

This section considers the execution of the programmed virtual flows in a pipelined manner. Specifically, the VFP framework executes asynchronous pipelines (of *soft nature*) in order to exploit the coarse grained parallelism. Fine-graned instruction and data parallelism is utilized within the individual PEs. As elaborated in section 3.1, the VFP framework uses the divide-and-conquer principle to implement the wireless protocols on a programmable task-level. This is particularly important for 2 reasons;

• it makes the mapping of tasks to PEs and programming the flow simpler (discussed

in section 3.3)

• it presents the opportunity to exploit *task-level parallelism* by executing different operations of potentially independent virtual flows on the PEs in parallel.

In order to exploit this task-level parallelism, the tasks within the virtual flows are executed in a pipelined fashion. For example, the Fig. 3.1b illustrates the pipelined operation of the virtual flows extracted from Fig. 3.1a. The most important advantages to be noted from the Fig. 3.1b are that;

- 1. The platform is executing two virtual flows concurrently, in a pipelined fashion, by multiplexing the PEs among the flows. Thus, the utilization of PEs is high and high system throughput is sustained, while supporting virtualization.

- 2. The flexibility of defining the virtual flows enables the latency of the pipelines executing the virtual flows to be variable. This is important from the point of view of achieving the real-time constraints associated with the protocol flows, while maintaining virtualization properties.

### 3.2.2 Virtual Flow Pipelining Overview

The pipelined execution of the programmable virtual flows in essence gives the name *Virtual Flow Pipelining* (VFP). Managing this flexible pipelined operation is achieved using the event-based control-flow sequencing and synchronization mechanisms that constitute the VFP framework. These are discussed in section 4.1.2. The VFP framework also handles the fast context switching and data communication between different PEs (stages of the pipeline) in a manner so as to achieve high PE utilization and system throughput.

In contrast to VFP, a traditional hardware pipeline is incapable of providing the performance, flexibility and virtualization properties. Fig. 3.1c illustrates the inefficiencies if a hardware pipeline was used to implement the two protocol flows depicted in 3.1a. But the benefit of a hardware pipeline is that it has a deterministic performance – since allocation of all the resources is completely inflexible and static throughout the frame period. The determinism is a desirable feature in order to guarantee QoS features. Our Virtual Flow Pipeline framework adds the required flexibility to the hardware pipelining approach, while retaining performance guaranties. This is achieved in the VFP by use of scheduling mechanisms (discussed in 4.1.2), which respect and enforce the priorities and timings requested by the upper layers.

## 3.3 How are Virtual Flows Created? – The VFP Programming Model

Before we go on and present the VFP control mechanisms, let us consider the VFP programming model. It is the programming model that enables creation and description of the virtual flows – in terms of functionality and performance requirements.

Based on the divide and control principle, our model involves breaking up the protocol flow into constituent tasks/functions. A task is an atomic computational kernel/algorithm that can be completely executed on a PE, e.g. interleaving, MMSE estimation etc. Thus at flow provisioning time, the following information is to be identified and represented in order to create a virtual flow;

- Description of the tasks involved (i.e. the operation to be executed, number of operands etc.) and their mapping to respective PEs. This is the lower level of programming.

- 2. Description of control-flow/sequence of the protocol, which effectively stitches the different tasks performed by the PEs into forming a flow. This is the higher level of programming that brings out the data dependencies among tasks.

- 3. Performance requirements of the flow in terms of timings and priorities of the constituent tasks from the perspective of higher layers.

The representation of the above information in form of control data structures is called a *Virtual Flow Program*. Multiple such flow programs can be created and defined at the flow provisioning time. But as discussed in the previous chapter (2.2), the need for virtualization, run-time reconfiguration and execution of multiple flows, together with maintenance of real-time constraints adds dynamics to the problem of actual scheduling and execution of tasks. Hence, the potential sequence space and timings of operations in a virtual flow are described at provisioning time, but the actual sequence and timings are decided at run-time – based on the run-time results.

### 3.3.1 Representing the Virtual Flow Program

The tasks and their sequence is then represented using a *directed acyclic graph* (DAG). A DAG representation enables representation and execution of spawning of one-to-many child tasks as well as facilitates joining many-to-one tasks.

Figure 3.2: VFP Programming Model

For example, lets assume that Fig. 3.2a represents a simple protocol. The structure of the DAG represents the protocol flow (higher level of programmability), whereas the nodes depict the PEs involved and their required configuration (lower level of programmability). Fig. 3.2b, illustrated the example flow program for the protocol depicted in Fig. 3.2a.

On the MPSoC, the virtual flow programs actually translate to control code that resides in the form of tables/data structures in the memories. These tables will be described in the next chapter.

## 3.3.2 Features of the Programming Model

Salient features of the programming model are:

- 1. The heterogeneous PEs are treated uniformly. Thus, the fact that a PE could a configurable HW module or a programmable processor, does not impact the way the platform is programmed.

- 2. The programmer is relieved from the burden of synchronization and data dependency checks. This is completely handles by the hardware.

- 3. Although the mapping of task-to-PE is done by the programmer, the actual scheduling and activation of tasks is managed by the hardware mechanisms at run-time. Thus, the programmer is not required to handle this at compile-time making the programming easier and more conducive to dynamics associated with virtualization. This feature provides the required level of abstraction towards the higher layers.

- 4. The task-level break up and two level programmability facilitates pipelining of operations, thus exploiting task level parallelism.

## 3.4 VFP Mechanisms

This section will describe the underlying control mechanisms of the VFP framework. These mechanisms support the programming model and are actually responsible for the execution of the protocol flows on the platform. A unique aspect of the VFP is that these mechanisms are all hardware-oriented. In a way, these mechanisms can be looked at as a hardware implementation of some operating system functions, thus obviating the need for one.

### 3.4.1 Control-flow Sequencing and Data Communication

The control-flow, which executes the higher level programming, is implemented as a sequence of producer-consumer interactions. Basically, the virtual flow program represented by the DAG is nothing but a bunch of producer-consumer sequences. A PE task acts as *producer* for the tasks following it in the DAG. Essentially, for a given virtual flow, every PE in the DAG acts as a producer (except the leaf node tasks) and every

PE acts as a consumer (except the root).

Thus, whenever a PE task (producer) completes, its consumers are identified and further mechanisms are triggered. This process of identifying and engaging of all the consumers of a particular producer task - as per the Control-flow data structure in the memory - in essence executes the control flow.

The data communication, between PEs is also handled by the VFP framework – again using the producer-consumer notion. The framework has provisions for checking race conditions and data overwrites using semaphores. Moreover, data transfers are performed by *Direct Memory Access* (DMA) engines that relieves the PEs of this burden. This effective separation of computation and communication, improves the PE utilization as well as the determinism in allocation of PE bandwidth.

#### 3.4.2 Synchronization

The programming model of VFP allows for forking (for parallel execution) and joining of tasks. This calls for the need for task synchronization. For example, in the case of joining, the start of a task has to be synchronized with the completion of multiple producer tasks. In general, the synchronization mechanisms are needed to trigger/activate particular tasks in the flow only after all their associated dependencies have been resolved.

As mentioned in section 3.3.2, the VFP framework handles the task synchronization independently - i.e. without the need for specific programming. This is done by maintaining *counting semaphores* associated with every task in every flow. These semaphores are initialized at the provisioning time (and periodically reinitialized for repeating tasks), and decremented once on every associated producer task completion. Finally, a semaphore reaching zero is the triggering event for that particular task. All these mechanisms are implemented in dedicated hardware logic, together with memory table entries for maintaining the synchronization states.

## 3.4.3 Scheduling

The stringent performance requirement of wireless protocols needs to be supported at the architecture level with mechanisms that will guarantee processing latency, timely response, and provisioned quality of service parameters. Hence effective scheduling mechanisms are incorporated in the VFP framework to satisfy requirements of individual flows as well as to efficiently share the processing resources between the flows.

As mentioned earlier, the virtual flows (tasks, their sequence and performance requirements) are defined at provisioning time, but need the run-time scheduler in order to ensure the performance under dynamic system loading. The run-time scheduler is in charge of ensuring both the deterministic and the statistical (average type) performance guaranties, depending on the flow setup. The scheduling function of the VFP controller multiplexes each PE (configurable hardware unit or programmable processor) either based on a time reservation (for deterministic guarantees) or a best effort scheme (for deterministic guarantees). In order to support synchronous framing type of protocols (e.g., time division multiplexing), the flow scheduling information for the time reservation based scheme also specifies the repetition time.

For providing these degrees of priorities, the tasks whose synchronization criteria is met are queued up as either synchronous tasks or as asynchronous tasks (with multiple priorities) for scheduling. The type of tasks depends on the type of performance demanded as per the virtual flow program.

### Synchronous Tasks

The synchronous tasks are associated with the deterministic guarantees. These tasks have allocation per repetitive flow frame intervals, reserving the corresponding PE for the required processing time at the specific interval within the periodic frame. In short, synchronous tasks have a dedicated share of the PE bandwidth. Fig. 3.3 illustrates the allocation of bandwidth to the synchronous tasks. These allocations can belong to different virtual flows.

Figure 3.3: VFP Scheduling Policy

### Asynchronous Tasks

These tasks are associated with the statistical guarantees. The asynchronous tasks which are allocated in the shared processing bandwidth left over after the allocation of the reserved capacity by the synchronous tasks. Thus they are scheduled as per a best effort policy. The asynchronous tasks are scheduled by fixed or Weighted Round Robin scheduling discipline. The asynchronous tasks are interrupted at the start time of the synchronous task time slot, and resumed at the point of interruption after the completion of the synchronous task. The interruption is also necessary in order to guaranty the processing bandwidth for the deterministic processing of synchronous tasks. (Presently our implementation does not support interruption of async tasks. Instead we stall scheduling an async task if its processing time is long enough so as to clash with a synchronous task allocation.)

The fig. 3.3 illustrates all the scheduling policies. Important observations are that the async task AT1 is interrupted and resumed later in order to cater to the dedicated bandwidth of synchronous task ST2. The G1, G2 and G3 are guard times for the

synchronous tasks - it is the time window for sampling the enabling event. Enabling events delayed more than the time G cause the synchronous task to be rescheduled (red arrow) and the dedicated bandwidth is released (used up by AT2).

#### 3.4.4 Context Switching

Given the short processing time for the packet, or parts of it, the fast context switching needs to be supported by both software execution (CPUs), as well as hardware PEs, otherwise the utilization of the units will be low. For the systems targeting hundreds of megabits per second data throughput the unit processing time is sub-microsecond, dictating the use of hardware assisted and controlled context switching.

Also, the processing time of the task execution has to be deterministic. In order to cater to these requirements, the VFP system controller completely handles all the activities up to beginning of task processing (pre-processing) and takes over immediately after the completion of task execution. Thus the PEs are engaged only in useful processing activities and can be kept occupied in a pipelined fashion.

The pre-processing functions performed by the VFP for the PE, include scheduling the task, bringing in the input data, setting up the input buffer pointers and flow context information. Following this the PE is triggered with the task command, which it promptly begins executing. Similarly, the post-processing functions performed by the VFP after the task execution completes include, identifying consumers and transferring the output data.

Thus, the constituent PEs of the system have a very myopic view. They are unaware of notions of flows nor do they know to which flow the task they are processing belongs. The PEs just respond to the commands from the VFP controller and hand over the control back to the VFP controller as soon as execution completes.

## 3.5 Putting it All Together – The Layered Radio Perspective

This sections attempts to provide a high level overview of the VFP framework while summarizing the features and mechanisms discussed in the previous sections. We try to provide this complete picture by proposing a *Layered Radio Architecture* view of the system. This view is depicted in the fig. 3.4.

Figure 3.4: Layered Radio Architecture

The following points describe the different layers while relating them to the VFP:

- **Higher Layers** These layers dictate the number of flows executed by the lower layers as well as their functionality and performance requirements. This is done by creating the virtual flow programs (according to the protocol requirements) through interactions with the *virtualization layer*.

- **Virtualization Layer** This layer presents the uniform API for the higher layers to program the virtual flows. It effectively provides a hardware abstraction between

the multi-radio environment at the higher layers and the common hardware platform at the lower levels – thus shielding the radio applications from the sharing and loading of the processing layer and hiding the existence of other concurrent seesions.

- **Dynamic Reconfiguration Layer** This layer constitutes the efficient control-flow, synchronization, fast context switching and run-time scheduling mechanisms as discussed in section 4.1.2. It is this layer that is responsive to the dynamics of the system and is responsible for enforcing the budgets and guarantees provisioned at compile time. On one side the dynamic reconfiguration layer interacts with the virtualization layer to receive the provisioned functionality and timings, while on the other side it schedules and drives the PE execution and data transfers as per the run-time results and events. It is also responsible for exploiting task-level parallelism by managing the asynchronous pipeline.

- **Processing Layer** This is the layer where the actual data plane processing is done. It constitutes the heterogeneous PEs (which presents a uniform interface to the dynamic reconfiguration layer) and the underlying interconnect. This layer offers the dynamic reconfig layer with three degrees of freedom in order to achieve the required flexibility. They are;

- 1. selection of PE configuration, which decides what operation/algorithm the PE executes;

- 2. sequencing of the PEs to form the coarse grain protocol flow; and

- denition of new PE functions by adding new software programs to the CPUbased data plane PEs.

The constituents of the processing layer have a myopic view. They are completely transparent of the notion of flows. They are like slaves of the dynamic reconfiguration layer – responding to commands on as a case by case basis.

## 3.6 Correlating the VFP Framework and the Requirements

In this final section of the chapter describing the VFP framework, we will correlate the framework with the requirements covered in Chapter2. This will bring out the significance of different aspects of the framework and help evaluate it qualitatively. Let us discuss each of the requirements, one by one.

- **Platform-based Paradigm** This requirement is satisfied by the two level programming model provided by VFP. It provides separation between programming the PE tasks and the actual top level sequence of the tasks – effectively achieving separation of computation and communication. Uniform support for heterogeneous components further qualifies the framework.

- **Programmability/Configurability and Dynamic Reconfiguration** The Programmability requirement is satisfied in a straightforward manner by the programming provisions. Various protocols/standards can be programmed onto the SoC at compile time. The particular protocol to be used/executed in order to transmit a particular packet can be decided at run-time – when inserting the packet for baseband processing. This feature in effect achieves the required per-packet dynamic reconfigurability.

- Multiple Simultaneous Traffic Flows The support for having multiple diverse protocols pre-programmed together with the ability of the framework to multiplex and interleave the tasks onto PEs achieves this requirement.

- Virtualization and QoS guarantees This is achieved by the scheduler policy and its run-time implementation. The protocols are pre-programmed and then dynamically initiated by the higher layers at run-time – without system loading considerations. Then the run-time scheduling of the tasks to PEs, which execute them with a myopic view, achieves the virtualization.

- **Throughput, Real-time Constraints and Power Efficiency** These are achieved by all the VFP mechanisms (scheduling, synchronization, context s/w) and their

unique hardware implementation. These mechanisms offload the PE of all the task and flow management functions. Thus, the PEs are kept busy with only useful application/algorithm processing. Furthermore, the pipelining (task-level parallelism) further increases throughput. This hardware-based task management together with the scheduler policy and transparent data passing, increase the determinism in the system - a key requirement for meeting real time constraints. Avoiding the use of operating system or a CPU operating at very high speed helps power reduction.

## Chapter 4

# Virtual Flow Pipelining based SoC Architecture

In Chapter 3 we have presented the *Virtual Flow Pipelining* framework for satisfying the requirements of programmable and flexible radio processing. In this chapter we will eloborate on the development of the framework into a *system-on-chip* (SoC) architecture. Putting it differently, the previous chapter answers the "What" questions (What are the specs, the mechanisms, the programs?). This chapter will answers the "How" questions (How is the framework implemented? How is it organized?).

#### 4.1 Preliminaries

In this section we put forth the preliminaries that lead to the SoC architectural approaches and micro-architecure discussions. Strictly speaking this section while beginning to answer the *Hows* actually extends on the *Whats* discussed in the previous chapter. The reason for including these here is that they are closely associated with and naturally lead to the implementation discussions.

### 4.1.1 Control-code Memory Structures