# ASIP DATA-PLANE PROCESSOR FOR MULTI-STANDARD WIRELESS PROTOCOL PROCESSING

### BY MOHIT GOPAL WANI

A thesis submitted to the

Graduate School—New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of Prof. Predrag Spasojević and approved by

New Brunswick, New Jersey October, 2010 © 2010 Mohit Gopal Wani ALL RIGHTS RESERVED

#### ABSTRACT OF THE THESIS

# ASIP Data-plane Processor for Multi-Standard Wireless Protocol Processing

# by Mohit Gopal Wani Thesis Director: Prof. Predrag Spasojević

Evolving Multi-Protocol Multi-Band Software Defined Radio (SDR) devices aim at supporting multiple protocols seamlessly and efficiently. The design of such radios necessitates flexibility in physical layer processing, flexibility in routing packets through processing engines and flexibility in radio frequency reception/transmission. This dissertation addresses an efficient implementation of flexible physical layer processing (PHY) for Interleaving, De-Interleaving and linear *Minimum Mean Square Error* (MMSE) detection in *Multiple Input Multiple Output* (MIMO) receivers through *Application Specific Instruction Set Processors* (ASIPs). The thesis defines and develops a WINLAB cognitive radio (WiNC2R) compatible data-plane ASIP architecture along with suitable hardware-software partitioning of the Processing Engine unit.

Given the requirement of very significant design time and the lack of the flexibility after design, dedicated ASIC for PHY may not be a viable option although it has the best performance among all available options. The software application running on general purpose processor cannot satisfy the throughput requirements of the wireless standards. ASIPs provide a better trade-off between flexibility and performance, with the advantage of considerably lower design time than ASICs. We design an efficient multi-standard (802.11a, 802.16e/m) supporting Interleaver/De-Interleaver ASIP, satisfying the throughput requirements for all the modulation-schemes/data-rates in both of the standards. It can be programmed to scale for supporting future wireless standards (that use Block Interleaving/De-Interleaving). We also study viability of a flexible MIMO MMSE detector ASIP supporting variable  $M_R$  (Number of receiving antennas) \*  $M_T$  (Number of transmitting antennas) operations. We have analyzed the implementation of an hardware-centric algorithm for MIMO detection on an ASIP and also improved its performance with the help of techniques such as fixed point implementation, Single Instruction Multiple Data (SIMD) and Very Long Instruction Word (VLIW). Analysis of the design performance results for MIMO ASIP indicates the limitations of hardware-implementation-specific algorithms on ASIP. We also provide the account of design decisions such as custom ports, memory interfaces and registers that are added to the data-plane processor ASIPs in order to substitute them for dedicated hardware engines in the WiNC2R platform.

## Acknowledgements

First, I would like to thank my advisors Prof. Zoran Miljanić and Prof. Predrag Spasojević for their continuous support, vision, guidance and encouragement in the development of this thesis work. I am indebted to them for their confidence about my work in this challenging area in the intersection of communication processing and computer architecture fields. They gave me complete freedom in my work, although I had to literally start without any substantial background in both of the areas. Many thanks to them for clarifying my concepts from time to time and for the care they provided throughout the period.

I am thankful to Jerry Redington (Tensilica, Inc.) for his patient support. The thesis was not possible without getting the insights of computer architecture from Jerry. I was lucky to have him as someone whom I can approach for any silly doubt on Tensilica architecture. I would also like to thank Khanh Le for all those brainstorming sessions and lively discussions that helped me getting better in understanding the hardware design. I truly appreciate his readiness to help anytime, be it related to this project or otherwise. Thanks to Ivan Seskar for providing help whenever requested for.

It was an enjoyable experience to work with WINLAB mates: Akshay, Onkar, Madhura, Prashant and VLSI-lab mates: Wen and Raghuveer. I thank them for their friendship and support. Special thanks to Chandru for providing daily rides to WIN-LAB and helping me numerous times during my entire stay at Rutgers.

Most importantly, I would like to thank my parents, Mrs. Lata Wani and Mr. Gopal Wani, my brother Mr. Milind Wani and sister Mrs. Meghana Amritkar, for always supporting me in all my pursuits academic, personal or otherwise. My every success, big or small, is owed to their love, support and sacrifices.

# Table of Contents

| A             | ostra | .ct    |            |            |           |        | • •  |      |      |     |     |     | •  |     |     |    |    | ii   |

|---------------|-------|--------|------------|------------|-----------|--------|------|------|------|-----|-----|-----|----|-----|-----|----|----|------|

| A             | cknow | wledge | ements .   |            |           |        |      |      |      |     |     |     | •  |     |     | •  |    | iv   |

| $\mathbf{Li}$ | st of | Table  | s          |            |           |        |      |      |      |     |     |     | •  |     |     |    |    | viii |

| $\mathbf{Li}$ | st of | Figur  | es         |            |           |        |      |      |      |     |     |     | •  |     |     | •  |    | ix   |

| 1.            | Intr  | oducti | ion        |            |           |        |      |      |      |     |     |     | •  |     |     |    |    | 1    |

|               | 1.1.  | Softwa | are Define | d Radio    |           |        |      |      |      |     |     |     | •  |     |     |    |    | 2    |

|               | 1.2.  | Implei | mentation  | of Softw   | are Defi  | ned R  | adio |      |      |     |     |     | •  |     |     |    |    | 3    |

|               | 1.3.  | WiNC   | 2R Archi   | tecture .  |           |        |      |      |      |     |     | • • | •  |     |     | •  |    | 5    |

| 2.            | Dat   | a-Plan | e Proces   | ssor       |           |        |      |      |      |     |     |     |    |     |     |    |    | 8    |

|               | 2.1.  | Introd | uction     |            |           |        |      |      |      |     |     |     |    |     |     |    |    | 8    |

|               |       | 2.1.1. | Data Pla   | ane        |           |        |      |      |      |     |     |     |    |     |     |    |    | 8    |

|               |       | 2.1.2. | Control    | Plane      |           |        |      |      |      |     |     |     |    |     |     |    |    | 9    |

|               |       | 2.1.3. | ASIP as    | a Data I   | Plane Pr  | ocesso | or.  |      |      |     |     |     |    |     |     |    |    | 10   |

|               |       |        | 2.1.3.1.   | ASIPs a    | and Othe  | er Mic | ropr | oce  | ssor | s . |     |     |    |     |     |    |    | 12   |

|               |       |        | 2.1.3.2.   | Advanta    | ages of A | ASIPs  |      |      |      |     |     |     |    |     |     |    |    | 13   |

|               |       |        | 2.1.3.3.   | Place of   | Data Pl   | lane P | roce | ssoi | s in | Pr  | ogı | ran | ım | abl | e R | ad | io |      |

|               |       |        |            | Platform   | ns        |        |      |      |      |     |     |     |    |     |     |    |    | 14   |

|               | 2.2.  | Tensil | ica Xtensa | a ASIP a   | rchitectı | ure    |      |      |      |     |     |     |    |     |     |    |    | 14   |

|               |       | 2.2.1. | Why Te     | nsilica Pr | cocessor? | ?      |      |      |      |     |     |     |    |     |     |    |    | 17   |

|               | 2.3.  | Config | gurability |            |           |        |      |      |      |     |     |     |    |     |     |    |    | 18   |

|               | 2.4.  | The A  | SIP Desig  | gn Cycle   |           |        |      |      |      |     |     |     |    |     |     |    |    | 19   |

| 3. | Pro          | cessing | g Engine                                                     | 22 |

|----|--------------|---------|--------------------------------------------------------------|----|

|    | 3.1.         | Virtua  | al Flow Description                                          | 24 |

|    | 3.2.         | Integr  | ation of ASIP based PE into WiNC2R platform                  | 25 |

|    |              | 3.2.1.  | Designing ASIP Processor for dedicated PE framework: Method- |    |

|    |              |         | ology                                                        | 26 |

|    |              | 3.2.2.  | Communicating with the outside logic                         | 27 |

|    |              |         | 3.2.2.1. Import wires                                        | 27 |

|    |              |         | 3.2.2.2. Interrupts                                          | 28 |

|    |              |         | 3.2.2.3. Export States                                       | 30 |

|    |              |         | 3.2.2.4. Queues                                              | 30 |

|    |              | 3.2.3.  | Memories                                                     | 32 |

|    | 3.3.         | Softwa  | are application flow                                         | 33 |

| 4  | ACT          | D f     | Multi Standard Interlandian and De Interlandian              | 26 |

| 4. |              |         | Multi-Standard Interleaving and De-Interleaving              | 36 |

|    | 4.1.         |         | description                                                  | 36 |

|    | 4.2.         |         | eaving algorithm                                             | 37 |

|    |              | 4.2.1.  | Algorithm Improvement                                        | 41 |

|    | 4.3.         | De-Int  | cerleaving algorithm                                         | 45 |

|    |              | 4.3.1.  | Algorithm Improvement                                        | 46 |

|    | 4.4.         | Cost b  | penefit analysis                                             | 49 |

|    |              | 4.4.1.  | Conclusion                                                   | 54 |

| 5  | 4.51         | P for   | MIMO MMSE Detection                                          | 55 |

| 0. | <b>5</b> .1. |         | ) systems introduction                                       | 55 |

|    |              |         |                                                              |    |

|    | 5.2.         |         | MMSE detection requirements and algorithm                    | 56 |

|    | 5.3.         | •       | mentation on ASIP                                            | 58 |

|    |              | 5.3.1.  | Complexity analysis and Performance improvement analysis     | 68 |

|    |              | 5.3.2.  | Cost Analysis                                                | 70 |

|    | 5.4.         | Conclu  | usion                                                        | 71 |

| 6. | Con   | clusion and | Future | Work | <br> | <br> | <br>• | <br> |   |   | • |       |   | • | 79 |

|----|-------|-------------|--------|------|------|------|-------|------|---|---|---|-------|---|---|----|

|    | 6.1.  | Future work |        |      | <br> | <br> | <br>• | <br> | • | • | • | <br>• | • | • | 80 |

| Gl | ossai | r <b>y</b>  |        |      | <br> | <br> |       | <br> |   |   | • |       | • | • | 81 |

| Re | efere | nces        |        |      | <br> | <br> |       | <br> | • |   | • | <br>• |   | • | 83 |

# List of Tables

| 3.1. | Control Options for Interrupt/Polling facilitator module          | 29 |

|------|-------------------------------------------------------------------|----|

| 5.1. | Complexity Analysis of MIMO MMSE detection using Burg's algorithm | 58 |

# List of Figures

| 1.1.  | WiNC2R top level SoC view                                                                | 6  |

|-------|------------------------------------------------------------------------------------------|----|

| 2.1.  | Control-Plane vs. Data-Plane                                                             | 9  |

| 2.2.  | Classification of Microprocessors                                                        | 13 |

| 2.3.  | Data Plane Processors in WiNC2R Layered Radio Architecture                               | 15 |

| 2.4.  | Processor Design Space - Baseline Options                                                | 17 |

| 2.5.  | How a custom instruction is added in ASIP                                                | 20 |

| 2.6.  | ASIP design algorithm                                                                    | 21 |

| 3.1.  | Functional Unit Architecture                                                             | 23 |

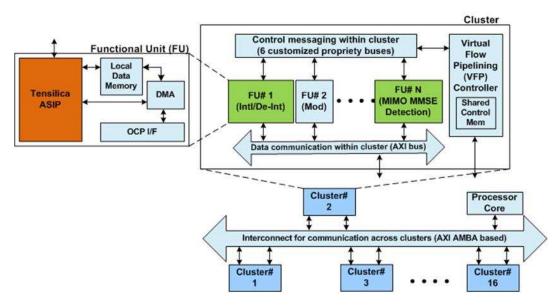

| 3.2.  | Processing Engine Architecture                                                           | 24 |

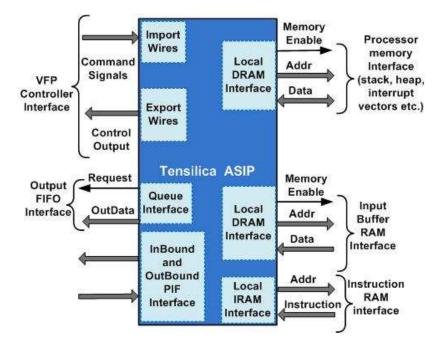

| 3.3.  | Tensilica ASIP Interface                                                                 | 28 |

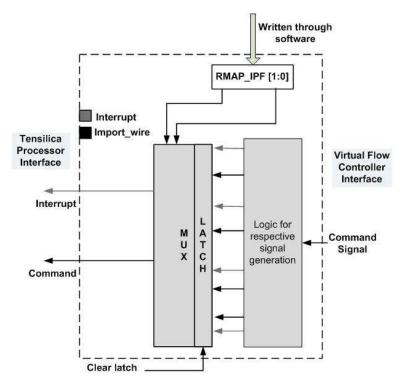

| 3.4.  | Interrupt and Polling facilitator Module                                                 | 29 |

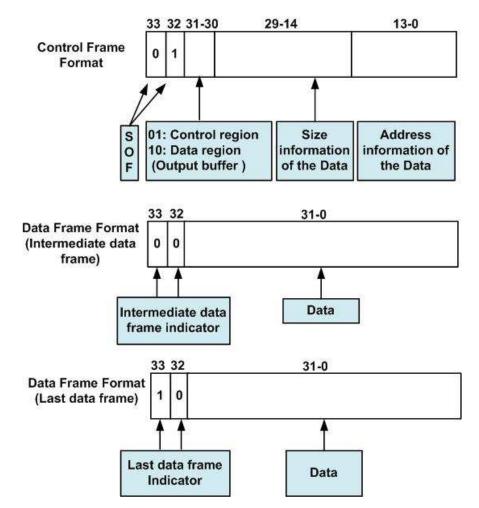

| 3.5.  | Output Queue Data Format                                                                 | 31 |

| 3.6.  | Custom ports declaration in TIE                                                          | 32 |

| 3.7.  | Instructions for accessing custom ports                                                  | 32 |

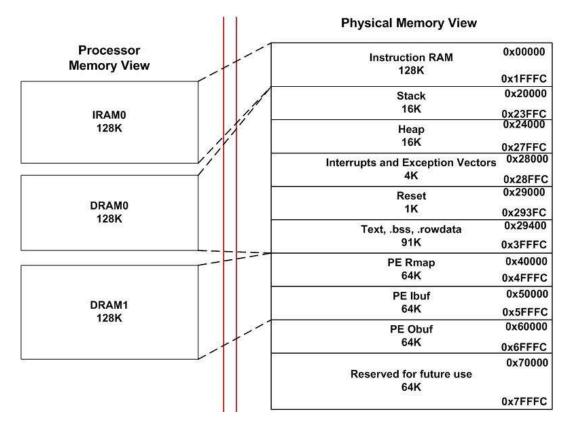

| 3.8.  | Memory map for Tensilica ASIP based functional units                                     | 33 |

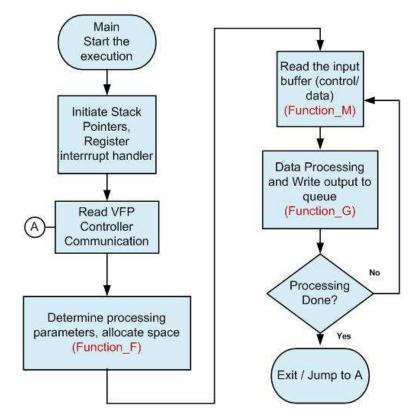

| 3.9.  | Software flow on the ASIP                                                                | 34 |

| 3.10. | ASIPs in WiNC2R SoC                                                                      | 35 |

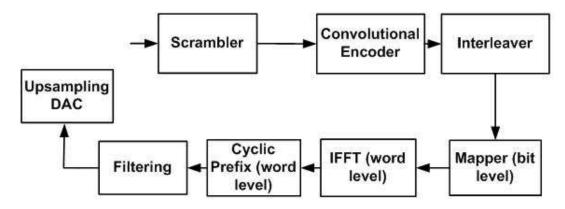

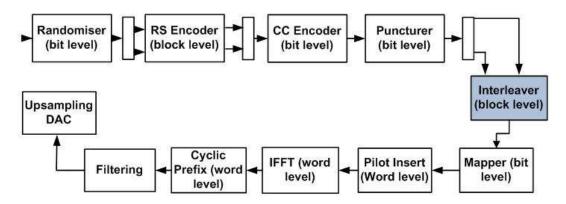

| 4.1.  | 802.11a Transmitter Block Diagram                                                        | 37 |

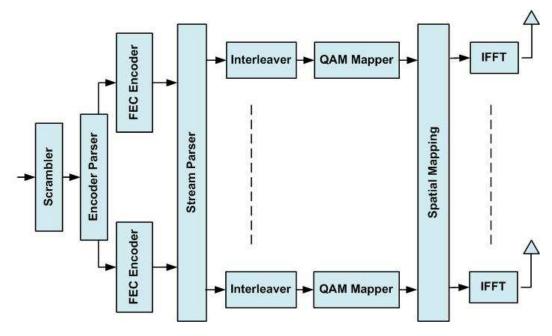

| 4.2.  | 802.11n Transmitter Block Diagram                                                        | 38 |

| 4.3.  | 802.16e/m Transmitter Block Diagram                                                      | 39 |

| 4.4.  | WiFi (802.11a) and WiMax (802.16e/m) Details $\hfill \ldots \ldots \ldots \ldots \ldots$ | 39 |

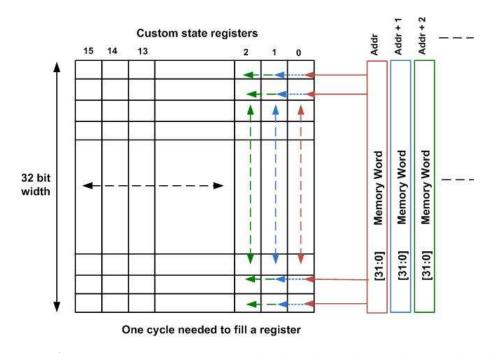

| 4.5.  | Interleaving: Bit Shuffling in the Register Matrix                                       | 40 |

| 4.6.  | A custom instruction removing bottleneck in the interleaving algorithm                   | 42 |

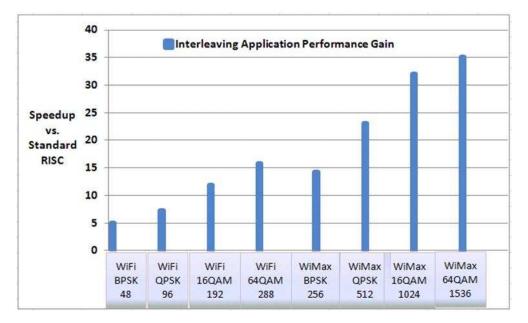

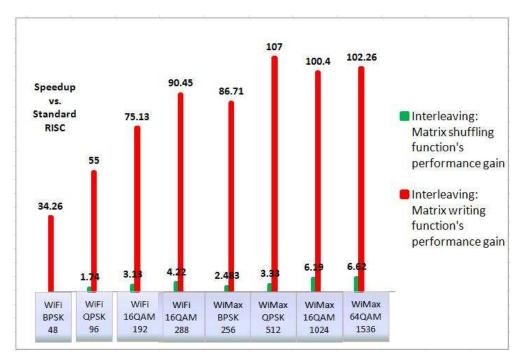

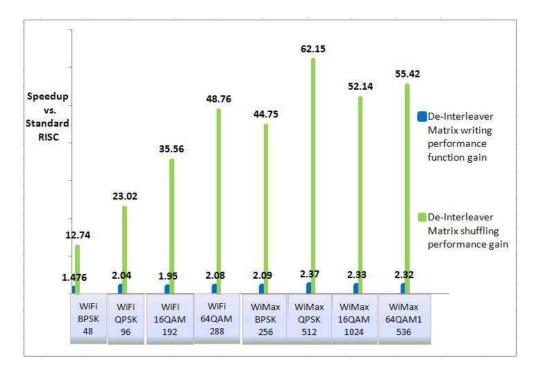

| 4.7.  | Interleaving application performance gain (in multiple times) $\ . \ . \ .$              | 43 |

| 4.8. Interleaving application: Performance improvement of Matrix Writing          |    |

|-----------------------------------------------------------------------------------|----|

| function and Matrix shuffling (processing) function $\ldots \ldots \ldots \ldots$ | 44 |

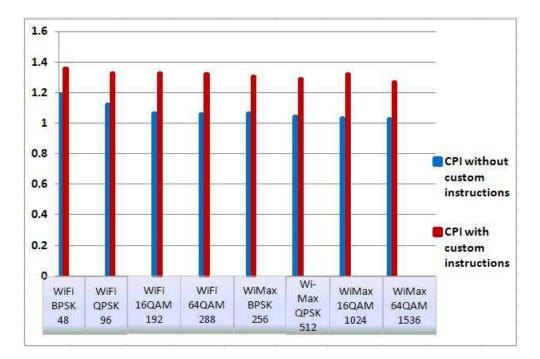

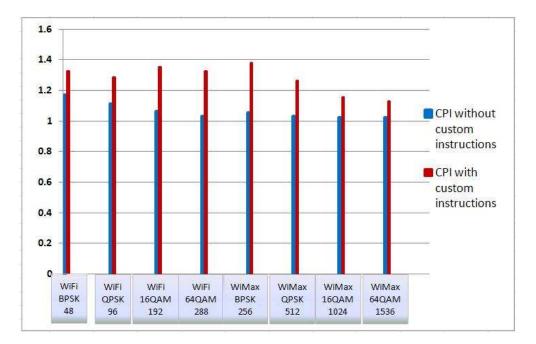

| 4.9. Custom instructions' impact on the CPI (Interleaving application) $\ .$ .    | 45 |

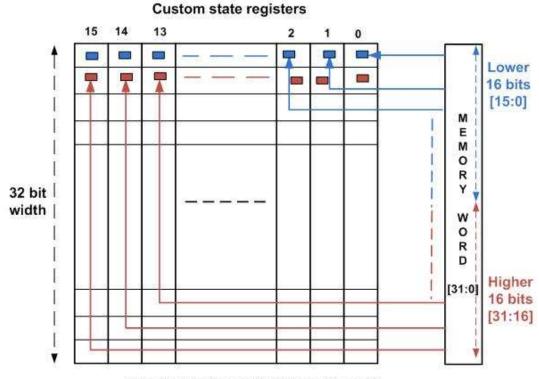

| 4.10. Custom instruction for filling registers row-wise                           | 47 |

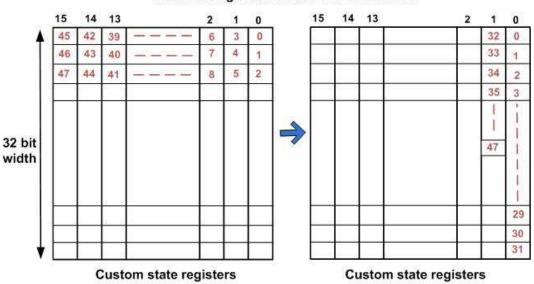

| 4.11. After processing, rearrangement of bits for reading out                     | 48 |

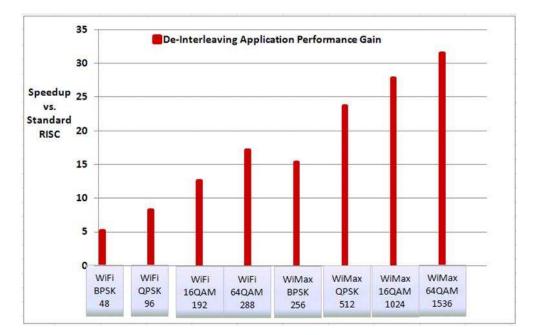

| 4.12. De-Interleaving application performance gain (in multiple times) $\ldots$   | 49 |

| 4.13. De-Interleaving application: Performance improvement of Matrix writing      |    |

| function and Matrix shuffling (processing) function $\ldots \ldots \ldots \ldots$ | 50 |

| 4.14. Custom instructions's impact on the CPI (De-Interleaving application) .     | 51 |

| 4.15. A snippet of custom instruction filling the register matrix                 | 52 |

| 4.16. Snippet of instruction scheduling through TIE                               | 53 |

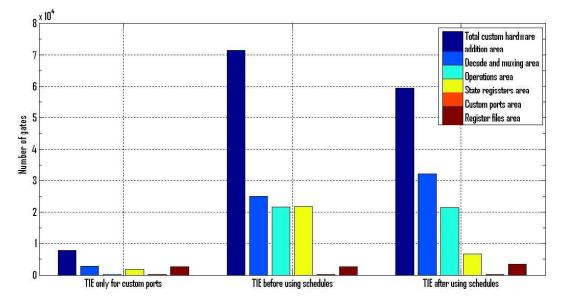

| 4.17. Comparison of custom hardware addition cases                                | 53 |

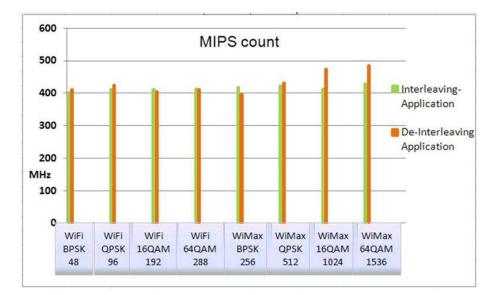

| 4.18. ASIP performance in MIPS                                                    | 54 |

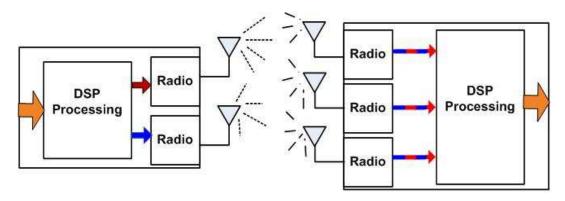

| 5.1. MIMO System                                                                  | 55 |

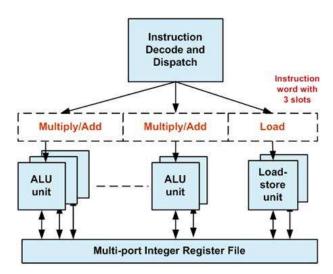

| 5.2. VLIW logical layer                                                           | 64 |

| 5.3. Snapshot of instructions on 3 issue VLIW processor                           | 65 |

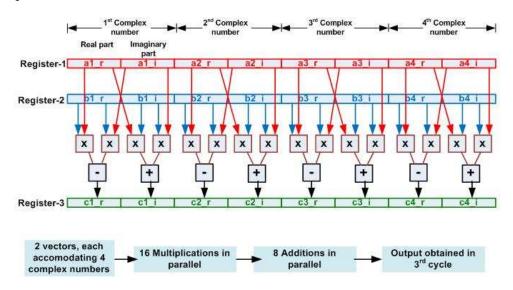

| 5.4. SIMD implementation using state registers                                    | 66 |

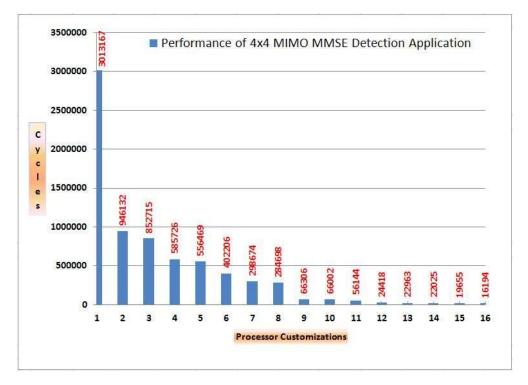

| 5.6. MIMO Application Performance (4x4 Matrix)                                    | 76 |

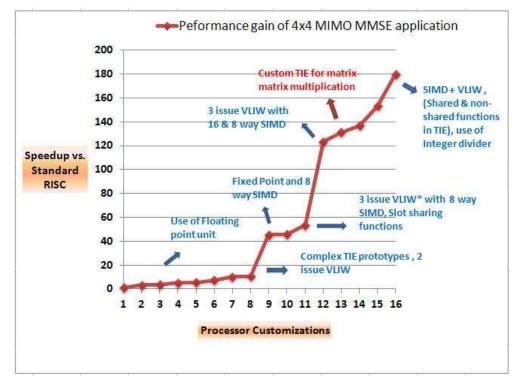

| 5.7. Gain in MIMO Application Performance (4x4 Matrix)                            | 76 |

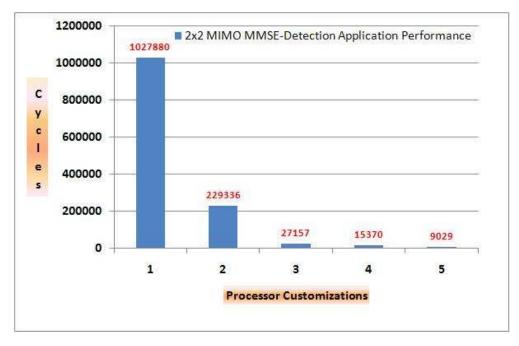

| 5.8. MIMO Application Performance (2x2 Matrix)                                    | 77 |

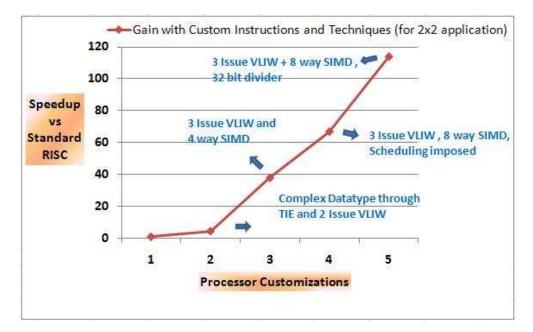

| 5.9. Gain in MIMO Application Performance (2x2 Matrix)                            | 77 |

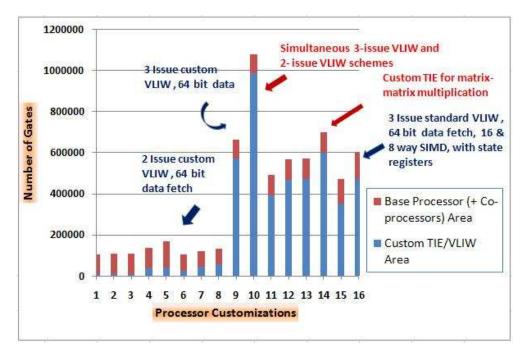

| 5.10. 4x4 MIMO MMSE ASIP area trend-details                                       | 78 |

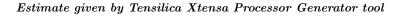

| 5.11. Flexible MIMO MMSE ASIP area analysis                                       | 78 |

|                                                                                   |    |

# Chapter 1

# Introduction

This section briefly provides overview of the idea of *Cognitive Radio* (CR) and in general *Software Defined Radio* (SDR) devices, requirements and trends in their architectures. We also discuss about WiNLAB Network Centric Cognitive Radio (WiNC2R) platform architecture with detailed view of the *Virtual Flow Pipelining* concept.

The objective of cognitive radio is to solve spectrum scarcity problem by means of dynamic spectrum access. A Cognitive Radio (CR) is required to constantly sense its environment and dynamically reconfigure its own parameters so as to communicate reliably and efficiently. It should be able to alter its transmission rate, power, frequency, modulation scheme and any combination of these to support wireless standards throughput requirements. The switching between the available channels across different standards should be transparent to the user and fast enough to have no data loss [1].

The main features of Cognitive Radios are listed below [2].

- Spectrum Sensing: A CR scans a wide spectrum and determine frequencies being used as well as determines its own transmission characteristics

- Policy and configuration: A CR is subject to certain policies in each of the environment which it should adhere to and has configuration setting pertaining to each of the policy.

- Modular architecture: CR should have modular level architecture within which they can direct the flow of data dynamically

- Application oriented profiles: CRs can Create/maintain application specific (example: long distance, moving with high speed etc.) profiles and incorporate those

transparent to the user

- Adaptive algorithms: CRs switch operating algorithms to improve their efficiency of a network collectively.

- Distributed collaboration: CRs share their knowledge of operating environment and application requirements, to determine policies for optimal network resources utilization.

- Security: The security of the data won't be compromised while CRs entering or leaving network.

Cognitive radios are estimated to be useful in number of applications such as:

- Spectrum sensing and frequency adaptive abilities are useful where guaranteed communication links are a necessity

- Flexibility to support various communication technologies is big advantage for military applications

- Multiple Networks supporting ability can serve as a bridge between two devices/ networks based on different communication standards

- CRs can create separate user profiles which suite applications in specific environments and hence useful for providing location dependent services

- CR is always a secondary user if the spectrum is licensed even though it can sense a free portion of spectrum and tune to it. This feature avoids priority conflicts and leads to efficient network utilization.

### 1.1 Software Defined Radio

Software Defined Radio (SDR) is a technology that enables reconfigurable system for wireless networks. SDR defines a combination of hardware and software technologies on which the radios operating functions are implemented [3]. Cognitive Radio sits above the SDR and lets it determine which mode of operation and parameters to choose [4].

#### 1.2 Implementation of Software Defined Radio

There are several requirements that are identified for a SDR architecture as defined in [5]:

- SDR platforms usually consists of a combination of different processing devices such as *Field Programmable Gate Arrays* (FPGA), *Digital Signal Processors* (DSPs), General Purpose Processors (GPPs), programmable System on Chip (SoC) or other application specific programmable processors. The use of these technologies allows new wireless features and capabilities to be added to existing radio systems without requiring new hardware. Thus a component model defining semantics of components, the interfaces and the protocols for managing information exchange is necessary.

- The flows should be developed independent of the platform since there may be several platform under different application requirements. This independence also assumes a common operational environment from the platforms.

- Launching of an application requires finding, loading, and instantiating each individual component on the appropriate device of the platform, connecting the components (virtually) and performing any initialization tasks necessary to have application running properly. There should be a module/processor for launching the application.

- The applications should be stored in some kind of memory. Hence, there should be a way to store, organize and access memory.

- There should be a communication mechanism *(transport layer)* to exchange information and data across different nodes in the platform.

- A mechanism *(manager)* is needed to manage and keep track of all the hardware and software resources and provide interface with the user.

- There should be a way to interact with the heterogeneous hardware components to configure them and facilitate control/data information exchange.

- The validation of platform's capacity and available resources (*capacity model*) is required for each application to be supported

- The flexibility of:

- Per packet selection that is required in computationally intensive PHY processing

- Interoperability

- Support of new protocols that are in development and will emerge with the completely new applications domain

Traditional SDR platforms consist of General Purpose Processors and DSP Processors which are inadequate for future high data-rate communications in terms of processing speed and energy efficiency. The advances in VLSI technology has directed the future development of SDR platforms towards Multi-Processor System-on-Chip (MP-SoC) based platforms consisting of several heterogeneous processors tailored for different processing tasks. A number of MPSoC based architectures have been proposed till date. [6] proposes MPSoC where number of processing elements (GPP/DSP/ASIC/ reconfigurable hardware units are inter-connected to the Network-on-Chip (NoC). Both the Programs running on each of the processing elements as well as flows between them are dynamically configured at run-time. [7] describes a design paradigm for extensible SDR architecture for including support for newer protocols. But it cannot dynamically (per packet seamless) support multiple protocols. [8] has described an SDR architecture where four processing engines (2-LIW processor with 32 bit SIMD ALU and local memory), a global memory and one Control processor (ARM) is connected to a central bus. The powerful PEs offer performance for compute-intensive tasks (WCDMA, 2MHz). However the architecture is not enough for supporting higher data-rates required in WiFi and WiMax standards. [9] describes fine grain processing reconfigurable FPGAlike fabrics connected through arrays. These are difficult to program for achieving throughput.

The processing complexity of wireless protocol experiences the *Compound Annual Growth Rate* (CAGR) of 78, while the SOC performance is increasing at CAGR of 22 [10]. This necessitates novel network centric architecture solutions that will suffice new processing paradigms. WiNC2R is one of such solutions [1].

#### 1.3 WiNC2R Architecture

Winlab Network Centric Cognitive Radio (WiNC2R)[1] is a programmable MPSoC (based on hardware assisted virtualization) SDR platform. It is aimed at providing a high performance platform for experimentation with various adaptive wireless network protocols ranging from simple etiquettes to more complex ad-hoc collaboration. It is designed for flexible processing of both Physical and MAC/network layers with sustained bit rates of 10 MBpS and higher with adaptability to variety of network interference conditions and protocol conditions. This is step towards an architecture that will be scalable to adapt to future throughput increases, modifications of radio and higher layers and complexity requirements of portable and fixed devices.

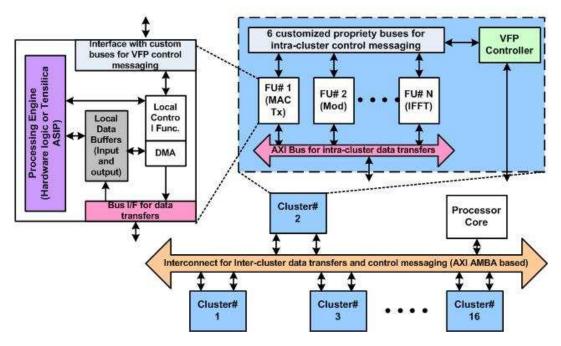

WinC2R is based on the concept of Virtual Flow Pipelining (VFP) [10] where the underlying PHY resources are hidden from the higher network layers. It consists of multiple clusters, each made up of several heterogeneous Processing Engines(ASIPs, RTL modules and Software entities running on GPP) connected via hierarchical AMBA AXI bus. Each cluster has a VFP local-function module, while the centralized VFP Controller is connected to the central AXI bus along with a global control memory structure called as Global Task Table (GTT). Figure 1.1 shows the top level SoC architectural view. The key features of platform are:

- Virtualization technique [10] is introduced to provide common interface to higher layers which will hide the necessary details for resource reservations and sharing.

- Dynamic sharing of bandwidth is observed in IP packet based world by following Service Level Agreement (SLA) Parameters.

- The allocations of the 'resources-share' to the flow create the virtual flow consisting of the sequence of the processing steps on the required processing modules.

- Resource scheduler takes care of full flow latency requirements of wireless protocol

Figure 1.1: WiNC2R top level SoC view

Source: Onkar Sarode. WinC2R architecture document (Centralized\_UCM\_arch.vsd), www.svn.winlab.rutgers.edu/cognitive, March 2010

processing

- The virtualization layer handles hardware resources to manage communication bandwidth with responsibility for SLA reinforcement among sessions and protecting each of them.

- Each session treats its share of the physical bandwidth as a separate channel.

Virtual Flow consists of a set of functions and their scheduling requirements associated with a higher protocol entity (application, session, IP or MAC address). VFP functions are executed as tasks, where task can run on potentially multi functional hardware engines or software programmable CPUs. VFP controller is responsible for selecting each step of the task function and its associated parameters on each of the processing engines. The sequencing is enforced by ordering, function (or thread on CPU) selection and synchronization between processing units. The data flow paths can be configured during the setup and initialization and also during the actual operation. WiNC2R provides a backbone architecture with a uniform interface to all modules, which supports plug-and-play ability. WiNC2R also supports run time reconfigurability inside the modules currently implemented.

The thesis focuses on designing the Application Specific Instruction Set Processors (ASIPs) to be plugged as data-plane processors in VFP based programmable framework of WiNC2R platform. Chapter 2 presents a detailed account of data-plane processors. We will analyze the features of several processors design choices. Chapter 3 presents the architectural customizations of the ASIP for porting into the WiNC2R platform. It also gives the account of architectural decisions and hardware-software partitioning. Chapter 4 includes the design and performance improvement achieved through Instruction Set Architecture (ISA) extensions for the processing engines of Interleaving/De-Interleaving. Chapter 5 illustrates the analysis of implementation of hardware-centric algorithm for MIMO MMSE detection. Chapter 5 also gives details about the steps involved in the algorithm improvement, with the use of VLIW/ SIMD techniques and other processor customizations. Chapter 6 completes the thesis work by providing conclusion and future work.

## Chapter 2

## **Data-Plane** Processor

This section provides the background of concepts: data-plane processing and Application Specific Instruction Set Processors. We also discuss the trade-offs of using ASIPs as data-plane processors, with the comparison of options such as general purpose RISC processors and dedicated ASIC implementations. This also includes general discussion about processor design and ASIP design aspects.

#### 2.1 Introduction

Multi-core System on Chips (SoCs) have become prominent in the high performance real-time systems. The decision about the right kinds of processors to be put in to this multi-processor chip is based on the concept of presence of two planes in the design: Control plane and Data plane. In a typical SoC, control plane manages the user interface, the system synchronization, and few more functions while the data plane processing manages compute intensive tasks [11]. A tighter integration of these planes is necessary for achieving optimal performance. Figure 2.1 shows the clear distinction between these planes.

### 2.1.1 Data Plane

In networking or communications systems, the data plane processes each packet as it passes through the system [12]. Data-plane tasks may include converting packets from one protocol to another, encrypting or decrypting data, filtering unwanted packets, prioritizing packets, routing them to their next destination and computational processing of the physical layer. In short, all the data-intensive operations are carried out by data plane. Data plane typically uses specialized CPUs (lacking caches and with limited

| Data<br>Plane    | Baseband PHY<br>Processing (RTL/<br>ASIP) | Protocol   | Video<br>Processing |  |  |

|------------------|-------------------------------------------|------------|---------------------|--|--|

| Flatte           | Baseband<br>MAC/Control (RTL/<br>ASIP)    | Processing | Audio<br>Processing |  |  |

| Control<br>Plane | CPU running main application              | Men        | nory                |  |  |

Figure 2.1: Control-Plane vs. Data-Plane *Source: http://www.tensilica.com*

memory size) or Application Specific Integrated Circuits (ASIC) or dedicated FPGA processing unit. A small local memory holds instructions, limiting the available code space, often to several thousand instructions. These engines may include special instructions to extract and manipulate fields of arbitrary bit length, as these operations are useful in some packet protocols. Short pipelines can be advantageous in data-plane processing. Clock rates are often modest (1GHz or less) to minimize power dissipation. They may include accelerators to offload specific tasks.

#### 2.1.2 Control Plane

The control plane handles packets that require extra processing, user interface, higher levels of protocol stacks, system synchronization and all other non-data intensive applications [11]. Moreover control plane handles the tasks of configuring data-plane layer and managing the data-flow. The control plane typically uses standard General Purpose Processors (GPP) since they are easily programmable. Control plane software is designed assuming it will be running on a general purpose processor. It has fewer computations and more conditional branches than typical applications. Hence, it will perform better with short pipeline (small branch prediction penalty).

The control plane and data plane can share the same memory space to reduce cost and eliminate the latency in moving the data across memories. Data-plane processors architecture and analysis is the focus of this research thesis. The data-plane engines can be organized in two ways [12]. In a parallel model, one CPU is designated as the master, receiving all packets and assigning them to engines as needed. The data-plane engines can be arranged in a pipeline. For example, the first engine could classify packets, the second could perform filtering, the third could perform encapsulations, and the fourth could perform traffic management. It also ensures proper ordering and deterministic latency.

### 2.1.3 ASIP as a Data Plane Processor

System developers are working to significantly reduce the resource levels required to develop systems by making it easier to design the chips in those systems and also to make SOCs sufficiently flexible so that every new system design does not require a new SOC design. Hence, the data plane processor design is facing a very strong push towards higher flexibility and computational requirements with power consumption constraints. The algorithmic requirements are increasing at far higher rate than that of architectural improvements to support it [13]. The important characteristics of ASIPs from an algorithmic perspective are:

- 1. Highly regular computation intensive operations;

- 2. Considerable I/O /memory accesses;

- 3. Complicated controlling in less computationally intensive tasks.

The limits on the general purpose processor performance due to instruction level parallelism and power consumption in the compute intensive applications (that require flexibility also) have given rise to an interesting idea. The idea is to take a general purpose processor and improve its performance by moving often executed sequences (functions) into a special hardware execution units requiring only one instruction to implement such a function. The result is Application Specific Instruction-set Processors (ASIPs) which can perform specific tasks as efficiently as possible [14]. ASIP design is a promising technique to meet the performance and cost goals of high-performance systems. In recent years, ASIPs have become popular because they simultaneously offer high performance and short design cycles. In contrast to off-the-shelf processor cores, ASIPs include dedicated functional units and ISA customizations that speed up execution of the 'hot spots' in a given application. Whereas, they cannot offer the same performance as ASICs due to limitations imposed by micro architectural constraints and the tighter control exerted for the data movement in the processors. Dedicated hardware is also cheaper in terms of cost and power as compared to ASIPs.

The programmability of ASIPs enables a larger volume, as multiple related applications, as well as different generations of an application can be mapped onto the same ASIP. A programmable solution also provides a much lower risk as well as a predictable and shorter time-to-market solution since writing and debugging software is cheaper than designing, debugging and manufacturing working hardware [15]. ASIPs allow designers to extend the base processor with custom instructions, memories, ports and even VLIW/SIMD extensions, making possible the best performance possible with processor-centric implementation. Given the high customization in ASIPs, they have essentially created a class for 'Data-plane Units' (DPUs).

Hardwired RTL design has many attractive characteristics: small area, low power, and high throughput. With the advent of multi million-gate SOCs, RTLs have become difficult to design and have issues such as slow verification, and poor scalability for increasingly complex problems. ASIP is a design methodology that retains most of RTLs benefits while reducing design time and risk. ASIPs can implement data-path operations that closely match those of RTL functions. The functional equivalents of RTL logic blocks are implemented using application-specific processors by adding execution units to the processors existing integer pipeline, additional registers and register files to the processors state, additional I/O ports, and other functions as needed by the specific application.

Due to the high degree of specialization, there will be dedicated processors for different application domains like digital video, wireless communication, multimedia, etc. Quantitative analysis has been done in [16], that shows energy efficiency measured in mega-operations/instructions per mW (MOpS/mW) for different architectures running the same benchmark along-with area required for each of the architectures. It shows that there is roughly one order in magnitude of energy efficiency between a RISC embedded processor, a domain specific DSP, and an ASIP optimized for this particular benchmark. Also proved is a fact that in terms of architectural choices of flexibility and efficiency, ASIP provides a best compromise between flexibility and performance.

#### 2.1.3.1 ASIPs and Other Microprocessors

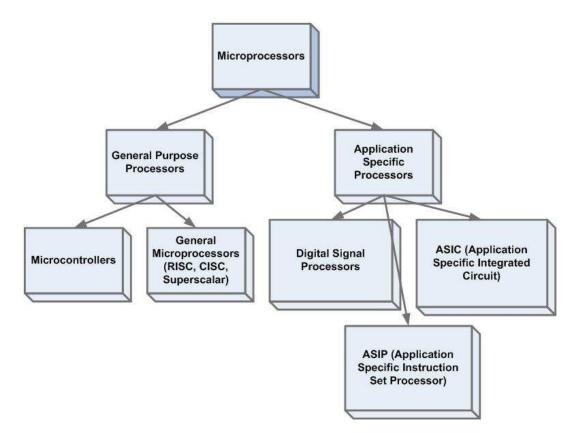

The microprocessors can be classified [17] on the basis of:

- 1. The Hardware (ISA) micro architecture:

- Reduced Instruction Set Computer (RISC)

- Complex Instruction Set Computer (CISC)

- Very Large Instruction Word (VLIW)

- Superscalar

- 2. Characteristics of the Application Areas

- General Purpose Processor (GPP)/ Micro-controller

- Special purpose processor (SPP)

- Application Specific Integrated Circuit (ASIC)

- Application Specific Instruction Set Processor (ASIP)

- Digital Signal Processor (DSP)

The classification of Microprocessors is also shown in the Figure 2.2.

The specialized nature of individual embedded applications creates two issues for general-purpose processors in data-intensive embedded applications [18]. First, there is a poor match between the critical functions needed by many embedded applications and a fixed-ISA processor's basic integer instruction set and register file. As a result of this mismatch, these critical embedded applications often require an unacceptable number of computation cycles when run on general-purpose processors. Second, narrowly focused, low-cost embedded devices cannot take full advantage of a general-purpose processor's broad capabilities. Consequently, expensive silicon resources built into the processor

Figure 2.2: Classification of Microprocessors

#### Original concept: Daniel Kästner. Lecture on Embedded systems. 2002-2003

are wasted in these applications because they are not needed by the specific embedded tasks assigned to the processor.

An ASIP sits between the high efficiency of an ASIC and the low cost of a GPP and provides a good balance of hardware and software to meet requirements such as flexibility, performance, fast time to market and power consumption.

#### 2.1.3.2 Advantages of ASIPs

The benefits of ASIPs are [13]:

- Non permanent customization and application development after fabrication

- Time to market considering evolving requirements and new applications/ideas

- Economies of scale

- Flexible I/O and Interface functionality required for embedded systems

- Supports refinement and co-design of hardware and software, as well as behavior and architecture

- All important metrics including Power-Delay-Area perspective are considered continuously in the design phase

These ASIP advantages do not come free but with certain disadvantages such as

#### 2.1.3.3 Place of Data Plane Processors in Programmable Radio Platforms

New Multiprocessor System-on-Chip (MPSoC) based platforms are being defined at the architecture - micro-architecture boundary which are inevitable for complex communication systems of the future. The goals are how to simultaneously optimize flexibility, cost , energy and performance. System-on-Chip development has fostered platform as well as communication based design [13]. These platforms tend to be component-based and aim at providing a range of choices from custom structures to fully programmable solutions at various cost-benefit ratios. There are two types of platforms: Software platforms and Hardware platforms. Software platforms run the application on general processor and offer maximum flexibility while the Hardware platforms are limited in terms of flexibility but much faster in processing. In these platforms, application-architectural exploration is focal part of implementation methodology.

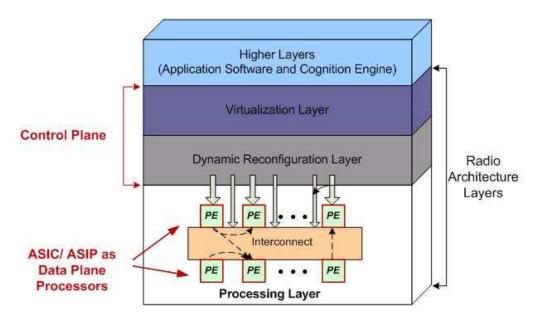

WiNC2R [1] is such a programmable platform where ASIPs/ASICs are used as data-plane processors providing an additional degree of freedom in functional processing. Data-plane processors are essentially multi-standard protocol processing engines in WiNC2R SoC platform. Figure 2.3 shows the data plane processors in WiNC2R architecture.

We have designed the data-plane processors for WiNC2R platform using Tensilica Xtensa® ASIPs. The next section gives details of the Xtensa ASIP architecture.

#### 2.2 Tensilica Xtensa ASIP architecture

The Xtensa architecture is highly flexible due to configurability. The following aspects of the processor can be configured at the build time:

Figure 2.3: Data Plane Processors in WiNC2R Layered Radio Architecture

Base source: Onkar Sarode. Scalable VFP-SoC architecture poster at WINLAB-IAB, Dec.2009. Modified here to show control plane, data-plane and place of ASICs/ASIPs

- Core micro-architecture

- Core instructions (Width, floating point instructions, DSP instructions)

- Co-processors

- Memory system

- Caches

- Processor interface

- Local memories

- Exceptions and Interrupts

- Test and debug

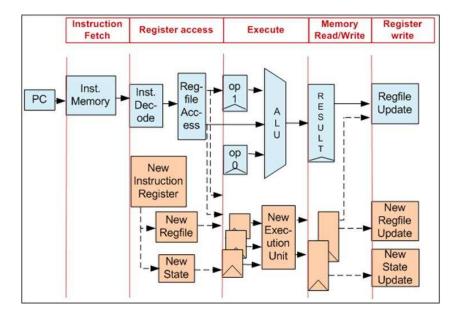

The basic architecture can be pruned or augmented depending on the data processing performance requirement of the application. The native processor pipeline is five stage (or seven stage) pipelined architecture. The five stage pipeline has stages:

I: Instruction fetch

R: Register read

E: Execute

M: Memory write

W: Register write-back

The core pipeline is augmented or additional pipeline is added through the Tensilica Instruction Extension (TIE) language defined instructions, optimizing the target algorithm's performance.

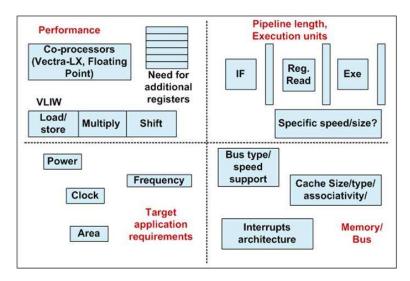

Extensive architecture exploration and refinement process is needed to realize an optimal architecture for a given set of applications. Specifically following aspects in the design space are to be taken into consideration [16].

- Instruction Set: The degree of parallelism in the application code that can be explored by the instruction-set using VLIW (Very Long Instruction-Word) instructions as well as the definition of special purpose instructions to accelerate specific portions of the application code while reducing power consumption.

- 2. The processor micro-architecture: This includes definitions of instruction and data pipelines, bypassing logic as well as the memory subsystem to reduce data and instruction access latencies.

- 3. Implementation of the Processor: A reasonable estimate of on power consumption, clock frequency and gate count can be gathered after a synthesis run with the target technology. The design decisions would need to be revisited if any of the parameters are out of the specification range.

- 4. System impact on the processor's performance: The system behavior and interaction with the processor has an immediate impact on the optimal processor micro-architecture. For ex. If the shared memory is going to be shared by a number of processors, it would be wise to have sufficient data-cache included in the architecture.

For Tensilica xtensa processors, the baseline processor design-space is illustrated in Figure 2.4.

Figure 2.4: Processor Design Space - Baseline Options

Original concept: Heinrich Meyr. System-on-Chip for Communications: The Dawn of ASIPs and the Dusk of ASICs, IEEE Workshop on Signal Processing Systems (SIPS), Seoul, Korea, 2003. (Modified here with respect to Tensilica Xtensa context)

### 2.2.1 Why Tensilica Processor?

Following points are precisely the reason for choosing Tensilica processors.

- Processors are modifiable through

- Instruction Sets

- \* Can simultaneously issue 24 bit and 16 bit instructions. If extended for VLIW, it can issue 32 bit TIE instructions along with basic 16 and 24 bit instructions

- Processor I/O ports to exactly match extensive computational application needs

- \* Local and system interfaces

- \* Designer defined I/O interfaces

- Possibility for multi-processor design

- Availability of Single and Double precision floating point co-processors

- Availability of DSP specific Vectra processor

- Defining scheduling of extended instructions is possible

- Provided tools for design environment for:

- Multi-Processor System-on-Chip (MPSoC) architecture

- Exploration of design space for Cache and memory parameters such as locality, associativity etc.

- Simultaneous power analysis for variety of configurations

- Tensilica Instruction Extension (TIE) language is similar to Verilog HDL and hence easier to learn if Verilog is familiar

- Multi Issue VLIW technology: The base LX3 processor can be configured as 3-issue VLIW (Flexible Length Instructions (FLIX)) processor

Since any set of DSP operations can be encapsulated into custom instructions, customized Xtensa LX cores are capable of outperforming most DSPs and general-purpose processors on most of DSP applications [19]. Custom instructions target a specific application. An Xtensa LX may be more area-efficient than a processor core that attempts to perform well on a wide range of applications but is only used for one specific application.

### 2.3 Configurability

There are several approaches to a configurable processor design [19]:

- Manually inserting instructions (hand-coded RTL ) into the RTL description of the processor

- Cannot guarantee operational correctness of the manually inserted instructions

- Associated software tools will not know about manually inserted instructions and hence they cannot exploit the instructions. Hence, ASIC firmware developers have to write assembly function calls and subroutines to exploit such instructions.

- Use specialized language to define the custom processor extensions

- Facilitates the high-level specification of new data-path functions in the form of new processor instructions, registers, register files, I/O ports, and FIFO queue interfaces.

- A configurable processor can implement wide, parallel, and complex datapath operations that closely match those used in custom RTL hardware. The equivalent data-paths are implemented by augmenting the base processor's integer pipeline with additional execution units, registers, and other functions developed by the chip architect for a target application.

The later option is widely used nowadays. The customized configuration is architected through:

- Selecting from standard configuration options, such as bus widths, interfaces, memories, and pre-configured execution units (floating-point units, DSPs, etc) [19].

- Adding new registers, register files, and custom task-specific instructions that support specialized data types and operations. If a custom instruction is added to the xtensa processor, the execution logic and register files are added in the datapath as can be seen from Figure 2.5. In this figure, the blue path denotes the base pipeline of the processor whereas the orange portion denotes the custom data-path created due to addition of custom instructions and supplimentary register files.

- Using programs that automatically analyze the C code and determine the best processor configuration and ISA (instruction-set architecture) extensions

### 2.4 The ASIP Design Cycle

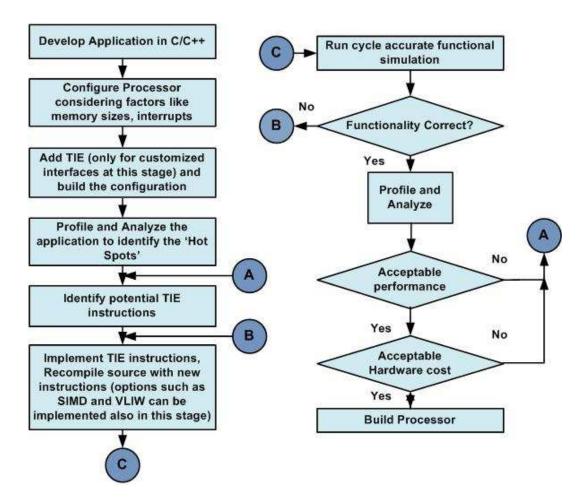

Here onwards, the terminology 'ASIP' will be used interchangeably with 'Tensilica Xtensa LX2/LX3' processor. The Figure 2.6 illustrates the design methodology for the ASIP design. The decisions such as whether to have SIMD/VLIW or only manual

Figure 2.5: How a custom instruction is added in ASIP Source: Tensilica Xtensa LX2 product documentation

instructions to be inserted etc. depend completely on the kind of application to be executed and power/area/frequency budget of the SoC. Once built, the processor can be co-simulated with external RTL logic and SystemC simulation models to gauge the performance of the complete SoC. The configuring of baseline processor has been explained earlier in Figure 2.4 on Page 17. When the potential custom instructions are decided, the register file and functions that can be called from custom instructions, also need to be considered. Moreover depending on the memory load/store operation frequency more custom/user registers may be included.

Figure 2.6: ASIP design algorithm

## Chapter 3

## **Processing Engine**

In this section, we discuss about the Processing Engine present in WiNC2R architecture. We also discuss issues that were handled in the transition from dedicated hardware processing engine architecture to ASIP-based architecture, the account of decisions made and strategy adopted to have an efficient transition.

The WiNC2R platform is a cluster-based System-on-Chip (SoC) architecture where each cluster contains a group of Functional Units (FUs) connected by low hierarchy AMBA-AXI bus. Each of the FU is responsible for certain step in protocol processing and is specific for that step. As shown in Figure 1.1 the clusters are connected through centralized AMB-AXI bus. FUs are autonomous units of the SoC engaged by event driven mechanisms. The reconfigurability of the data-flow is achieved using two memory structures: *Global Task-descriptor Table* (GTT) and *Task-Descriptor* (TD) table [20] [21]. GTT is connected to central AMBA AXI bus while TD table is present in each of the FU respectively. Both of these tables are configured by the software for setting up the flows. The processing in FU can be divided into two parts; data processing and control processing. The data processing includes the core radio signal processing functionality while the control processing is to achieve flexibility in the flow. FUs are implemented in:

- 1. Register Transfer Logic (RTL) using hardware description languages: VHDL and Verilog

- 2. Application Specific Instruction Set Processors (ASIPs)

- 3. C functions called through DPI interface in System Verilog logic block

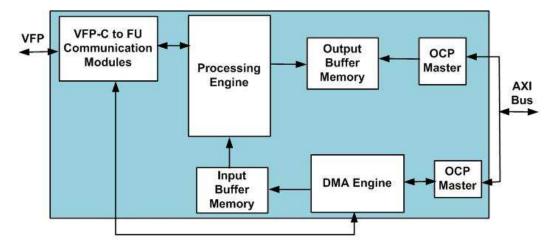

The Processing Engine (PE) forms the core computing block inside a FU. Alongside

the PE (Figure 3.1), there are other hardware blocks such as DMA Engine, the Input and Output Buffers, the Open Core Protocol-Intellectual Property (OCP-IP) master and modules for communicating with the VFP controller.

Figure 3.1: Functional Unit Architecture

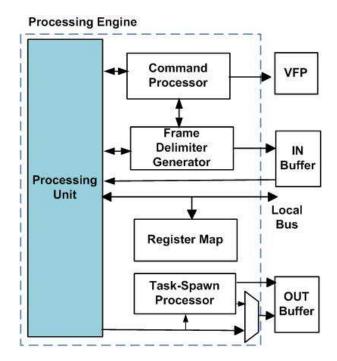

The architecture of the processing engine is shown in the Figure 3.2 [22]. The *Processing Unit* (PU) is the actual algorithm processing block.

The *Command Processor*(CP) module maps the command received from VFP controller into appropriate action signals that is sent to processing unit. Each command has a corresponding Action signal which is active high for one clock cycle. The user provides a Command Table, where each entry has a corresponding Action signal. CP also sets other modules in the preparation for the command processing.

The *Field Delimiter Generator*(FDG) resides between processing unit and the input buffer. The FDG fetches the data from input buffer depending on the address and size information provided by the PU. The FDG with the help of special signaling from PU facilitates non-sequential memory access as well.

The Task Spawn Processor TSP fetches the corresponding output pointer to the buffer region requested by PU for writing into the output buffer. Once the pointers are fetched, it communicates with the PU to send data to be written to the output buffer.

The Register MAP called *RMAP* maintains the output buffer partition pointer sets. It also maintains control/status information related to the CP, FDG and TSP modules.

The input buffer and output buffer store the data to be processed and data after

Figure 3.2: Processing Engine Architecture

Source: Khanh Le. WiNC2R platform programming interface document, www.svn.winlab.rutgers.edu/cognitive, 2008

processing.

#### 3.1 Virtual Flow Description

The PE gets command from the VFP controller. Upon receiving a valid command (data or control), PU initiates a fetch cycle by first requesting a pointer fetch cycle followed by a data/parameter fetch cycle [23]. If Context information is available, then PU shall complete Context information fetch operation prior to initiating a data fetch cycle. and *Control Word* from the Input Buffer. The control word contains the parameters pertaining to the processing. For example, in the case of *Modulator PE*, the control word gives details of the modulation scheme and the standard for which the modulation is to be performed. After the processing is done, PU signals done signal to the CP and writes data to the output buffer using TSP module. It also sends signals of next task vectors indicating the buffer information to the next PE (consumer for the current PE). The *NextTaskStatus* bits indicate the location of the processed data in the output buffer. Depending on the flow and type of processing, the output data may be

stored at more than one location. The *NextTaskRequest* signal indicates the VFP *Task Termination* (TT) block how the output data at locations indicated by status bits is to be processed. The TT processing includes transferring the data to next FU/FUs in the data flow. The NT Request tells the TT to which FU the data is to be sent.

### 3.2 Integration of ASIP based PE into WiNC2R platform

The most important issue while designing SDR based devices is flexibility along with efficiency. The RTL design is certainly not flexible to add newer standards/protocols on ad-hoc basis due to huge design time. Naturally to satisfy the programmability requirement and also maintain a comparable performance, ASIP was considered as a logical alternative. The design migrating from RTL to firmware control has following implications [18]:

- 1. Flexibility: The block's function can be changed or newer functions can be added through firmware.

- 2. Sophisticated and low-cost software development methods can be used to develop and debug most of the chip features

- 3. Faster system modeling is possible with the help of higher abstract description and simulation ability

- 4. Control and Data processing is now integrated into the processor, which is easier to manage

- 5. Design productivity increases due to processor-based SOC design approach, since it sharply reduces risks of fatal logic bugs and permits graceful recovery when a bug is discovered

For WiNC2R PHY layer functions, ASIP is handled at SoC architecture level and programming model is maintained same as hardware based Processing Engines. To augment the platform with processor-centric PEs, we had to deal with mainly the following issues:

- An optimal combination of partitioned hardware and software is required. Some of the functionality for supporting hardware in PE can be moved to software;

- Communication with the other Processing Engines should be transparent to them and without hampering the performance;

- Memory organization: An optimal instruction and data memory size should be chosen so as to accommodate all current and future application needs;

- Possibility of general enhancement to Xtensa architecture for one PHY function proving useful for other PHY function;

- Strategies to achieve an optimal context switching between different tasks;

- Analysis of achievable throughput on ASIP implementation. For example in the case of MIMO MMSE detection PE as explained in chapter 5, we had to sacrifice precision accuracy since the throughput with floating point implementation was outside acceptable rate.

# 3.2.1 Designing ASIP Processor for dedicated PE framework: Methodology

The CP module as explained in the earlier section, is responsible for interfacing with the VFP controller, setting up other modules present in PE for data processing and mapping the data/control command (sent by VFP) to action signals (sent to PU). The processor (with the help of custom ports to be added) and programmable interrupt/exception architecture would be able to communicate efficiently with the VFP controller. Setting up other modules can also be done in synchronization when the command from VFP comes. The mapping of the command to action signals can be efficiently done in software. Hence, it is reasonable to remove the CP unit completely.

The FDG can also be scrapped completely since the ASIP to be substituted inherently has load and store unit which can handle data fetching from the input buffer memory. Similar to FDG, TSP module should also be removed since the processor is capable of storing the processed data into output buffer memory due to presence of inherent load-store unit.

# 3.2.2 Communicating with the outside logic

The ASIP base version does not have any custom ports but only general *Processor* Interface (PIF) and interrupts/exceptions structure defined at the time of the configuration. The input buffer and output buffer can be connected to a bus where the ASIP is connected through PIF. With this type of connection, the processor has to go to the bus every time it wants to fetch the data or send the data. Moreover this scheme won't work if it has to send pulse to the outside RTL logic. In that case, there is no guarantee that the outside RTL logic would receive the response in the definite estimate of time, due to possible contention on the bus as well as set priorities of incoming and outgoing data-signals to use the communication resources. All these issues have hindered the inclusion of a general purpose processor in the data-plane of computationally intensive/real-time systems.

# 3.2.2.1 Import wires

The inclusion of custom ports for communicating with the external RTL logic is the only way to solve the above mentioned issues. Xtensa architecture allows the addition of custom ports the processor interface. To use the external ports, they need to be defined in the *Tensilica Instruction Extension* (TIE) language [24] as *Operations*(custom instructions) and should be compiled with the desired processor configuration before start building the configuration. Before describing the details of the interfaces and how the data is used in the pipeline, we recall the stages in the 5-stage pipelined processor as described in section 2.1.3.3 on Page 14.

The *import\_wire* construct defines an input to the ASIP that can be read by designerdefined instructions [24]. The import\_wire is typically to read the status of some external logic, device, or another processor in a system. The name of the import\_wire can be included in the state-interface-list of an operation. The name of the import\_wire then becomes a valid variable name inside the operation or semantic body that can appear on the right side of any assignment in a C/C++ application. The instruction reading the import\_wire can use the data in the 'E stage' of the pipeline. Since the data is registered before use in any of the instructions, the instruction semantic and the external logic that drives this port have no timing contention in a cycle. Declaring an import\_wire adds a new input port named TIE\_<name> to the Xtensa processor. We have added the input interfaces from the VFP controller as import\_wires in the processor, shown in Figure 3.3. The detail interface architecture can be found in [25].

Figure 3.3: Tensilica ASIP Interface

## 3.2.2.2 Interrupts

An interrupt is defined for the control command. If the processor is in the midst of the data-processing and gets a control command interrupt, it has to stop data execution, store the existing register state (along with Program Counter) and jump to the interrupt routine. Once the interrupt processing is done, the interrupt register is cleared and program jumps back. We have provided the facility to have both Data as well as Control command valid signals to be defined as either Import wire(s) or Interrupts. This is a very useful scheme since the processor can poll for the command valid signal when there is nothing to process for it (before getting the data-command). But when

it starts processing it can not poll without hampering the performance; and hence the control command comes as an interrupt although its costlier to implement. The mapping of either or both of the command valid signals on either interrupt or just a import\_wire is achieved with the help of intr\_poll\_facilitator block [25]. The Figure 3.4 shows the interrupt facilitator block, while Table 3.1 refers to the programmability feature of the module.

Figure 3.4: Interrupt and Polling facilitator Module

| Table $3.1$ : | Control | Options for | : Interrupt | /Polling | facilitator | module |

|---------------|---------|-------------|-------------|----------|-------------|--------|

|               |         |             |             |          |             |        |

| Case Description                                           | RMAP Bits [1:0] |

|------------------------------------------------------------|-----------------|

| Control-command as interrupt and Data-command polling      | 00              |

| Control-command as interrupt and Data-command as interrupt | 01              |

| Control command as polling and Data-command as interrupt   | 10              |

| Control command as polling and Data command as polling     | 11              |

#### 3.2.2.3 Export States

A state defines a construct to create registers where the values are stored prior to the instruction execution [24]. An instruction can also assign a value to a state, which is then updated with this new value after the execution of the instruction. Instructions that provide a well-defined, but general purpose way to read and write states, are automatically created by the TIE compiler when a state is declared with the optional argument  $add\_read\_write$ . When a state is defined with export keyword, it is made primary output of the processor. The externally visible value on the port changes only when the architectural value of the state changes. The exact cycle in which the port is updated (with the value of a recent write to the state) is implementation dependent. To avoid synchronization problems with the outside logic, base instruction EXTW helps ensuring that all externally visible actions from earlier instructions from the processor prior to the EXTW instruction are executed before the pipeline can proceed to the next instruction. All the signals going to VFP are defined as export states, as shown in Figure 3.3 on Page 28.

# 3.2.2.4 Queues

Once the ASIP finishes data-processing, it has to write the processed data into the output buffer. In order to reduce the time taken by the ASIP for this operation, there should be no waiting time for the processor to carry out this operation. To achieve this, we have segregated output buffer from the ASIP by a synchronous *First-In First-Out* (FIFO) buffer. The ASIP is connected to the FIFO by a custom interface called *Queue*. The data port TIE\_<name> is the output of the Xtensa processor that is connected to the data input of the queue and has the same name and width as specified in the queue declaration. Like any operand input to the processor, a queue read request is issued in E stage and used in the M stage of the pipeline. For output queue data must be available in M stage and sent to the output queue in W stage. The width of the queue interface for the ASIP is kept at 34 bit. The lower 32 bits are used for the data, and the upper 2 bits are used for controlling purposes indicating either start of the burst

or intermediate data (data word continual) or end of the burst. Figure 3.5 depicts the output word format to be sent to the queue. The first word will be a control word indicating the information such as region (control/data), size of the data to be written and the address where the data should be written. The control word is followed by the required data.

Figure 3.5: Output Queue Data Format

The Figure 3.6 shows the snippet of declaration of ports through TIE, whereas Figure 3.7 shows the snippet of instructions to access TIE custom ports.

There is a logic module called *Obuf\_to\_Memory\_Writer*[25], that reads the data from the FIFO and writes it to the output buffer memory. The format of the *Queue data* has been made such that the design of the this module is a very straightforward state-machine. The presence of a synchronous FIFO and the hardware logic for reading

```

import_wire wireInFlowConPtr 16

import_wire wireNextTaskAck 1

state NextTaskReqV 16 16'b0 add_read_write export

state CmdDecErr 1 1'b0 add_read_write export

queue OutQ 34 out

```

Figure 3.6: Custom ports declaration in TIE

```

operation xi_Read_wireNextTaskAck {out AR NextTaskAckIn} {in wireNextTaskAck]

{

assign NextTaskAckIn = {31'b0, wireNextTaskAck[0]};

}

operation xi_Write_CmdAck {in imm1 varCmdAck} {out CmdAck}

{

assign CmdAck = varCmdAck[0];

}

```

Figure 3.7: Instructions for accessing custom ports

FIFO and writing to the output buffer, makes the processor spend maximum time on the data-processing and minimum on the data transfer. The inclusion of the queue interface was one of the key decisions in the design of the ASIP.

# 3.2.3 Memories

The Xtensa ASIP is a *Harvard Architecture* [26] based processor and hence the instruction memory and data memory are stored in different locations. (Give details about the memory access cycles needed to access data, single port/multi-port memories advantages/options in xtensa, modes of adressing (register indirect/direct)).

Considering future application requirements, the Instruction RAM (IRAM) was decided to be of 128 KB size. While the Data RAM (DRAM) was decided to be of 256 KB size but divided into 2 separate RAMs and connected to the processor through separate data memory interfaces [25]. The first data memory (DRAM0) buffer contains all the Stack, Heap, Reset Vectors and literals present in the program. The other data memory (DRAM1) buffer serves as an input buffer to the processor. The DRAM1 is further divided into two equal portions 64 KB each. One region will be PE RMAP region and the other will be the region for storing the data to be processed. The PE RMAP region is further split into common RMAP region and the RMAP specifically pertaining to the respective PE which is substituted by Processor-centric solution, PU-RMAP. The Output buffer memory is not visible to the processor and hence it won't be writing to it directly but via the queue interface to the FIFO. The top level memory partition is shown in Figure 3.8.

Figure 3.8: Memory map for Tensilica ASIP based functional units

There is no requirement of data-cache in the ASIP as the load handled will be real time data which is updated in the input buffer continuously. However there is Instruction cache of size 1KB (2 way set-associative). This is the minimal size possible and no change in the performance was observed with the size/set associativity was changed.

### 3.3 Software application flow

In order to maintain modularity in the software and make it easily extensible, the functions are designed such that replacing few specific functions are needed to change the kind of PHY application rather than change entire program flow consisting of almost similar functions of communicating with VFP and reading processing parameters. Figure 3.9 shows the application algorithm. Function\_F, Function\_M and Function\_G are functions that are application specific. Rest of the functions are common for all ASIPs to be substituted as respective PEs in the WiNC2R platform.

Figure 3.9: Software flow on the ASIP

The custom instructions extensions file that is used for ASIP ISA extension, should be included as an header file in the C application in order to make compiler understand the instructions used in the C application and map it accordingly. If more than one files are used (which is a case many times due to modular design approach), all those files also should be included as separate header files in the application. The Figure 3.10 shows ASIPs (Interleaving/De-Interleaving, MIMO MMSE detection) in the WiNC2R SoC architecture view.

Figure 3.10: ASIPs in WiNC2R SoC

Concept: Onkar Sarode. Scalable VFP SoC architecture, Winlab-IAB meet, Dec. 2009. Modified here to include ASIPs of Interleaving/DeIntelreaving and MIMO-MMSE detection

# Chapter 4

# ASIP for Multi-Standard Interleaving and De-Interleaving

In this section, we describe the design of the ASIP. We also describe the performance vs. cost trade off analysis of the ASIP for multi-standard (Currently 802.11a, 802.11n [27] and 802.16e/m [28] standards) Interleaving and De-Interleaving operations of the PHY layer. The ASIP design methodology was highlighted in Figure 2.6 on Page 21. Accordingly the first step was to study and implement the algorithm on the Xtensa base processor.

# 4.1 PHY description

802.11a is IEEE standard for wireless communication. It was adopted first in 1997 and then revised in 1999. IEEE defines a MAC sublayer, MAC management protocols and services, and three physical (PHY) layers. The goals of the standard are:

- Deliver services same as found in wired networks

- Guaranteed high throughput

- Provide very reliable data delivery

- Provide continuous network connection

The transmitter block digram for 802.11a is shown in the Figure 4.1.

For 802.11n, the only difference is that there will be multiple streams to be operated upon simultaneously. These can be handled by having a processor each stream. The transmitter for 802.11n is shown in the Figure 4.2. Similarly, the 802.16e/m transmitter is also shown in Figure 4.3.

Figure 4.1: 802.11a Transmitter Block Diagram

# 4.2 Interleaving algorithm

Interleaving is used in digital data transmission technology to protect the transmission against burst errors. The interleaving operation is data-intensive operation, hence the processing time increases with the size of the data. The interleaving algorithm [27] [28] is described below :

Lets assume:

- k is the index of the bit to be coded before the first permutation;

- i is the index after the first and before the second permutation;

- j is the index after the second permutation, just prior to modulation mapping;

- $N_{CBPS}$  is the number of coded bits per symbol;

- $N_{BPSC}$  is the number of bits per sub-carrier;

Then, the first permutation is defined by the rule:

$$i = (N_{CBPS} \div 16) \times (k \mod 16) + \lfloor (k \div 16) \rfloor$$

$$(4.1)$$

for  $k = 0, 1, \dots, N_{CBPS} - 1$

and the second permutation is,

$$j = s \times \lfloor (i \div s) \rfloor + (i + N_{CBPS} - \lfloor (16 \times i/N_{CBPS}) \rfloor) \mod s$$

$$(4.2)$$

Figure 4.2: 802.11n Transmitter Block Diagram

Source: http://www.wirelessnetdesignline.com, PHY layer tutorial

for  $i = 0, 1, \dots, N_{CBPS} - 1$

where,

$$s = max(N_{BPSC} \div 2, 1) \tag{4.3}$$

As shown in Equations 4.1 and 4.2, each bit index of the symbol is permuted twice and the final address is derived. In simple words, the algorithm can be visualized with the help of a matrix where each element of the matrix contains a bit of the OFDM symbol [29].

- Number of bits per OFDM symbol depends on the standard (WiFi /WiMax) and modulation scheme used (BPSK/QPSK/16-QAM/64-QAM) as shown in Figure 4.4

- Matrix has number of rows from 3 to 96 and 16 columns

- Bits are filled row-wise

The first permutation just transposes this matrix. This is a special kind of transposing because the number of rows and columns before transposing remains same as

Figure 4.3: 802.16e/m Transmitter Block Diagram

| Standard | Modulation<br>Scheme | Number of Coded<br>Bits per Symbol<br>(N <sub>CBPS</sub> ) | Number of Coded<br>Bits Sub-Carrier<br>(N <sub>BPSC</sub> ) |

|----------|----------------------|------------------------------------------------------------|-------------------------------------------------------------|

| WiFi     | BPSK                 | 48                                                         | 1                                                           |

|          | QPSK                 | 96                                                         | 2                                                           |

|          | 16-QAM               | 192                                                        | 4                                                           |

|          | 64-QAM               | 288                                                        | 6                                                           |

| WiMax    | BPSK                 | 256                                                        | 1                                                           |

|          | QPSK                 | 512                                                        | 2                                                           |

|          | 16-QAM               | 1024                                                       | 4                                                           |

|          | 64-QAM               | 1536                                                       | 6                                                           |

Figure 4.4: WiFi (802.11a) and WiMax (802.16e/m) Details Source: IEEE 802.11a and 802.16e/m standards [27], [28]

number of rows after transposing. The bits are thus spread column-wise. After this operation, the second permutation interchanges bits amongst rows of the respective columns. This interchanging is dependent on the standard and modulation scheme. The bits are read row-wise after the two permutations. The details of bit shuffling are also shown in Figure 4.5. Naturally, instead on working on bit indices, it is more efficient to work on a matrix containing the block of bits in the memory.

- Instead of normal bit level addressing , this is byte/word level addressing, resulting in much faster algorithm

- A complete row can be written in one cycle and complete column can be read in one cycle

| Standard       | Modulation<br>Scheme | Bit Shuffling Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| WiFi and WiMax | BPSK                 | No Shuffling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| WiFi and WiMax | QPSK                 | No Shuffling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| WiFi and WiMax | 16 QAM               | If Column number mod 2 = 0: No shuffling ;<br>If Column number mod 2 = 1:<br>$1^{st}$ row bit => $2^{nd}$ row<br>$2^{nd}$ row bit => $1^{st}$ row<br>(Respectively in each pair of rows in a column starting<br>from $0^{th}$ row)                                                                                                                                                                                                                                                                                 |  |  |  |

| WiFi and WiMax | 64 QAM               | If Column number mod 3 = 0: No shuffling<br>If Column number mod 3 = 1:<br>$1^{st}$ row bit => $2^{nd}$ row<br>$2^{nd}$ row bit => $3^{rd}$ row<br>$3^{rd}$ row bit => $1^{st}$ row<br>(Respectively in the group of 3 rows in a column<br>starting from 0 <sup>th</sup> row)<br>If Column Number mod 3 = 2:<br>$1^{st}$ row bit => $3^{rd}$ row<br>$2^{nd}$ row bit => $1^{st}$ row<br>$3^{rd}$ row bit => $2^{nd}$ row<br>(Respectively in the group of 3 rows in a column<br>starting from 0 <sup>th</sup> row) |  |  |  |