# A MONOLITHICALLY INTEGRATED POWER JFET AND JUNCTION

# BARRIER SCHOTTKY DIODE IN 4H SILICON CARBIDE

by

# RAHUL RADHAKRISHNAN

A Dissertation submitted to the

Graduate School-New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Graduate Program in

Electrical and Computer Engineering

written under the direction of

Professor Jian H. Zhao

and approved by

New Brunswick, New Jersey

January, 2012

#### ABSTRACT OF THE DISSERTATION

# A Monolithically Integrated Power JFET and Junction Barrier Schottky Diode in 4H Silicon Carbide

#### by RAHUL RADHAKRISHNAN

**Dissertation Director**

Professor Jian H. Zhao

Efficiency of power management circuits depends significantly on their constituent switches and rectifiers. The demands of technology are increasingly running up against the intrinsic properties of Si based power devices. 4H-Silicon Carbide (SiC) has superior properties that make it attractive for high power applications. SiC rectifiers are already a competitive choice and SiC switches have also been commercialized recently. Junction Barrier Schottky (JBS) diodes, which combine the advantages of PN and Schottky, have higher Figure of Merit (FOM) as rectifiers. Among switches, a robust and mature process has been developed for Silicon Carbide Vertical Junction Field Effect Transistors (VJFETs), which currently gives it the highest unipolar FOM.

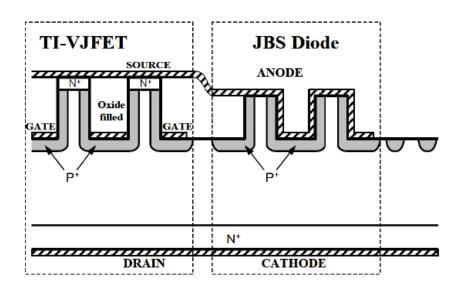

Switches are frequently combined with anti-parallel diodes in power circuits. This thesis describes the development of a SiC-based monolithically integrated power switch and diode. Monolithic integration increases reliability and efficiency, and reduces cost. Because of their superior properties and similarities in fabrication, we chose the SiC VJFET and JBS diode as the switch and rectifier. Detailed design, fabrication and characterization of the integrated switch to block above 800 V and conduct current beyond 100 A/cm<sup>2</sup> is explained. In this process, the first physicsbased 2-D compact model is developed for reverse leakage in a JBS diode as a function of design parameters. Since the gate-channel junctions of SiC VJFETs cannot be assumed to be abrupt, an existing analytical model for Si VJFETs is extended to account for graded gate-channel junctions. Using these analytical models, design rules are developed for the VJFET and JBS diode. Finite element simulations are used to find the best anode layout of the JBS diode and optimize electric field termination in the integrated device to ensure their capability to operate at high voltage. Finally, a spin-on glass based process is developed for filling the gate trenches of the VJFET to improve long-term robustness in extreme environments.

The integrated power switch developed in this thesis points to the attractions of monolithic integration in SiC power circuits. Analytical compact design equations derived here will facilitate faster and easier design of switches and rectifiers for desired circuit operation. To my mother Smt. P. V. Vasanthi

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my thesis advisor Prof. Jian H. Zhao for introducing me to the field of power devices, encouraging me to work hard, guiding my progress over many years and teaching me how to do independent research. I would like to express my indebtedness to Prof. Wei Jiang and Prof. Jaeseok Jeon for critically reading my dissertation and contributing in its development. I am also obliged to Dr. Richard L. Woodin for agreeing to examine my dissertation and for much fruitful technical discussion and encouragement.

I would like to acknowledge financial support received from United Silicon Carbide Inc., Dow Corning Corp. and Global Power Device Co. for carrying out parts of the research in this thesis.

I would also like to take this opportunity to thank Prof. Kuang Sheng, Dr. Tony Witt, Prof. Yicheng Lu and Prof. Warren Lai for valuable insight gained from much technical discussion over the years. I also appreciate the friendship and kindness of many current and former graduate students at Rutgers whom I have had the pleasure to work with including Mr. Gokul Ramamani, Dr. Xiaobin Xin, Dr. Xueqing Li, Dr. Yongxi Zhang, Dr. Yuzhu Li, Dr. Petre Alexandrov, Mr. Lei Lin and Mr. Keerthivarman Annajayaprakash. They all contributed in myriad ways to helping my research along.

Finally, I would like to thank Ms. Divya Mirchandani and Smt. P. V. Vasanthi for their constant support and love that helped me persist amidst the vicissitudes of graduate school.

# TABLE OF CONTENTS

| ABSTRACT                                            | ii |

|-----------------------------------------------------|----|

| DEDICATION                                          | iv |

| ACKNOWLEDGEMENTS                                    | v  |

| LIST OF TABLES                                      | ix |

| LIST OF ILLUSTRATIONS                               | X  |

| 1. INTRODUCTION                                     | 1  |

| 1.1 Power Devices                                   | 1  |

| 1.2 4H-SiC for Power Devices                        | 3  |

| 1.3 SiC VJFET as Power Switch                       | 5  |

| 1.4 SiC JBS Diode as Rectifier                      | 8  |

| 1.5 Monolithic Integration of Switch and Diode      | 9  |

| 1.6 Field-Termination in Power Devices              | 10 |

| 1.7 Outline of Ph. D. Thesis                        | 12 |

| 2 ANALYTICAL MODELING OF VJFET AND JBS DIODE        | 14 |

| 2.1 Analytical Modeling of JBS Diode                | 14 |

| 2.1.1 Notation                                      | 16 |

| 2.1.2 Reverse Voltage and Electric Field            | 18 |

| 2.1.3 Electric Field and Leakage Current            | 31 |

| 2.1.4 Experimental Results                          | 35 |

| 2.1.5 Forward Bias                                  |    |

| 2.1.6 Compact I-V model for JBS diode               |    |

| 2.2 Analytical Modeling of SiC VJFET                |    |

| 2.2.1 Blocking Mode- Drain Induced Barrier Lowering | 43 |

| 2.2.2 Conduction- ON Resistance                     | 47 |

| 2.2.3 Compact I-V model for SiC VJFET                    | 47  |

|----------------------------------------------------------|-----|

| 3. DESIGN OF VJFET, JBS DIODE AND MONOLITHIC INTEGRATION | 48  |

| 3.1 JBS Diode                                            | 49  |

| 3.1.1 Anode Geometry                                     | 50  |

| 3.2 VJFET                                                | 56  |

| 3.3 Monolithic Integration                               | 57  |

| 3.4 Edge-Termination                                     | 60  |

| 4. FABRICATION                                           | 64  |

| 4.1 Mask Design                                          | 64  |

| 4. 2 Wafer Structure                                     | 65  |

| 4.2 Source Mesa Etching                                  | 67  |

| 4.3 Ion Implantation                                     | 68  |

| 4.4 Passivation                                          | 71  |

| 4.5 Ohmic Contact                                        | 72  |

| 4.6 Trench Filling & Planarization                       | 74  |

| 4.7 Overlay Formation                                    | 74  |

| 5. CHARACTERIZATION AND MODELING                         | 77  |

| 5.1 Static Characteristics                               | 77  |

| 5.2 Temperature Characterization                         | 83  |

| 5.3 TCAD Modeling and Dynamic Characterization           | 86  |

| 5.4 Methods of Monolithic Integration                    | 89  |

| 6 SPIN-ON GLASS FOR FILLING VJFET TRENCHES               | 93  |

| 6.1 Trench filling process                               | 96  |

| 6.2 VJFET Metalization                                   | 99  |

| 6.3 VJFET Static Characteristics                         | 100 |

| 6.4 Summary                           | 102 |

|---------------------------------------|-----|

| 7 CONCLUSIONS AND SUGGESTIONS         |     |

| 7.1 Conclusions                       |     |

| 7.2 Suggestions for Future Work       | 104 |

| APPENDIX-1 ANALYTICAL MODEL FOR VJFET | 106 |

| REFERENCES                            |     |

| CURRICULUM VITA                       | 111 |

# LIST OF TABLES

| Table 1 Properties of semiconductors for power device applications              | .4 |

|---------------------------------------------------------------------------------|----|

| Table 2 Performance of best reported power switches                             | .6 |

| Table 3 Comparison of maximum electric field at Schottky contact from the model |    |

| and simulation for different implantation-straggle profiles at $V_R$ = 1000V    | 29 |

| Table 4 Comparison of anode layouts for the same reverse voltage                | 53 |

| Table 5 Sequence of Al ion implantation into SiC to form p+ gate                | 70 |

# LIST OF ILLUSTRATIONS

| Figure 1 Electric field along the drift region of a semiconductor device2           |

|-------------------------------------------------------------------------------------|

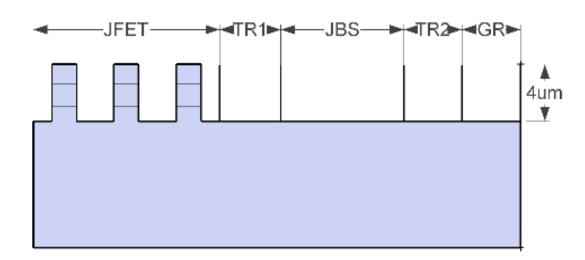

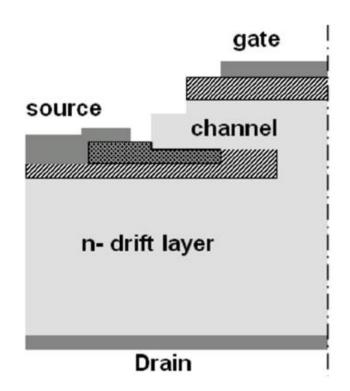

| Figure 2 Cross-section of a SiC VJFET7                                              |

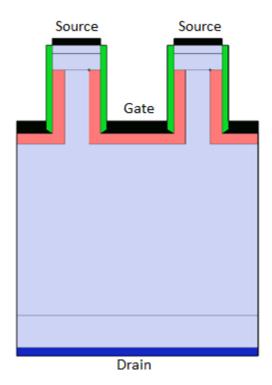

| Figure 3 Cross-section of a JBS diode                                               |

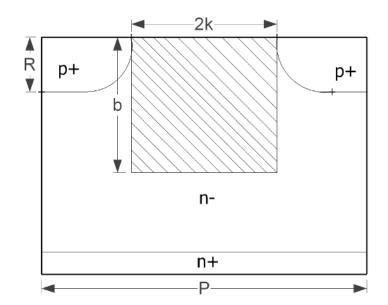

| Figure 4 3-phase inverter circuit with switch and anti-parallel diode10             |

| Figure 5 Cross-sectional views of a planar JBS diode20                              |

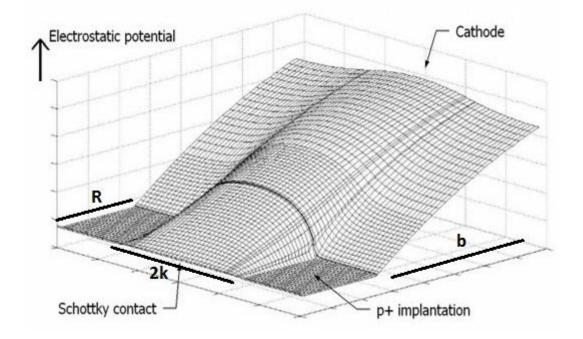

| Figure 6 Electrostatic potential near the anode of a JBS diode under reverse bias21 |

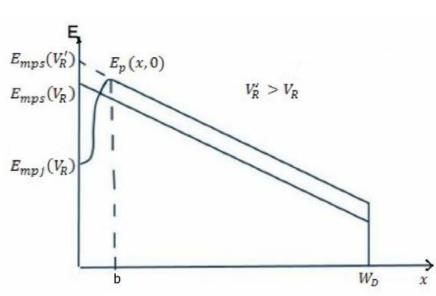

| Figure 7 Electric field distribution in corresponding JBS and Schottky diodes23     |

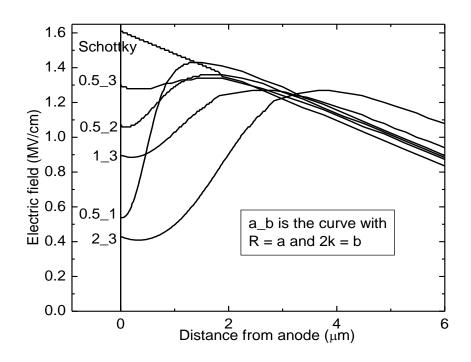

| Figure 8 Dependence of the electric field at (x,0) on R and 2k                      |

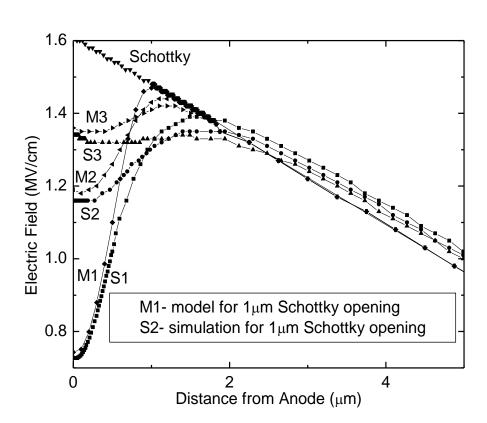

| Figure 9 Comparison at $V_R$ =1000V of model (M) and simulation (S)28               |

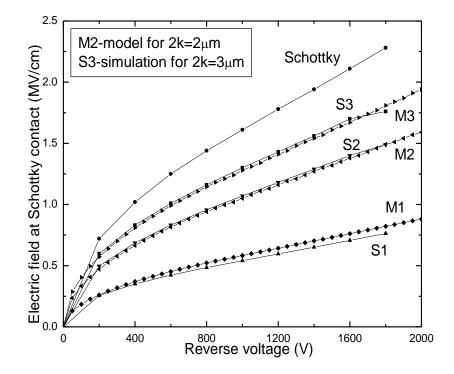

| Figure 10 Comparison of model and simulation with circular side-implantation30      |

| Figure 11 Comparison of model and simulation with no side-implantation              |

| Figure 12 Variation of normal electric field across the Schottky contact            |

| Figure 13 Variation of reverse leakage of JBS and Schottky diodes                   |

| Figure 14 Model and experimental SiC JBS diode reverse I-V curves at 300K37         |

| Figure 15 Comparison in reverse bias of the proposed model with other published     |

| models                                                                              |

| Figure 16 Simulation of doping profiles with implantation into 4H-SiC41             |

| Figure 17 Cross-section of an n-channel VJFET with design parameters41              |

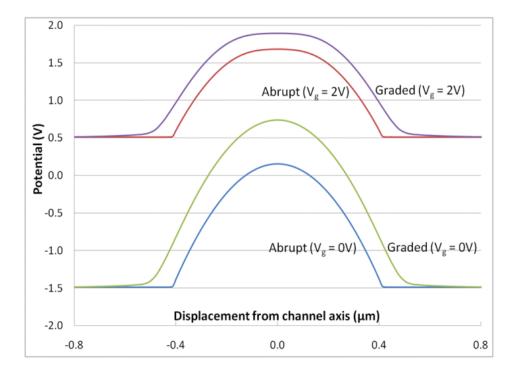

| Figure 18 Potential perpendicular to the axis of a VJFET at its saddle point42      |

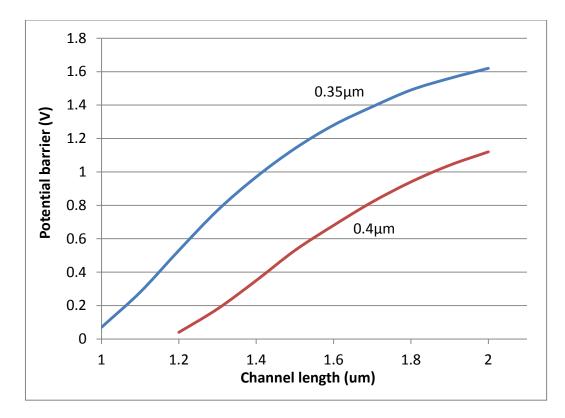

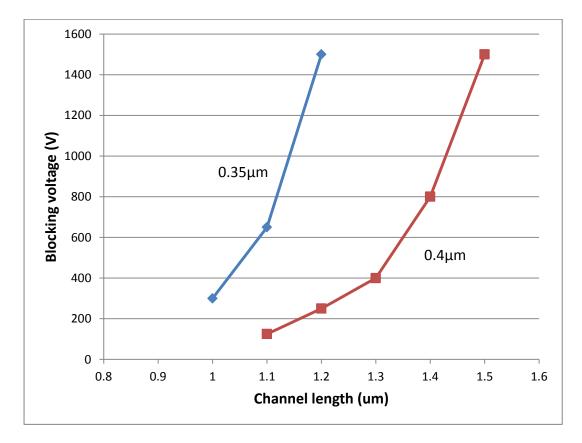

| Figure 19 Analytical model of variation of channel potential barrier with channel   |

| length at 1500V46                                                                   |

| Figure 20 TCAD results showing onset of DIBL versus channel length46                |

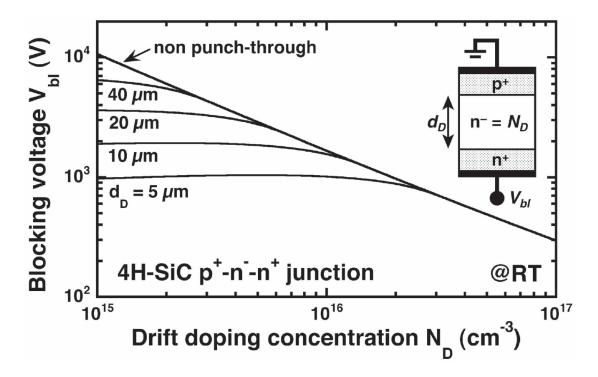

| Figure 21Blocking voltage for SiC epitaxial structures                              |

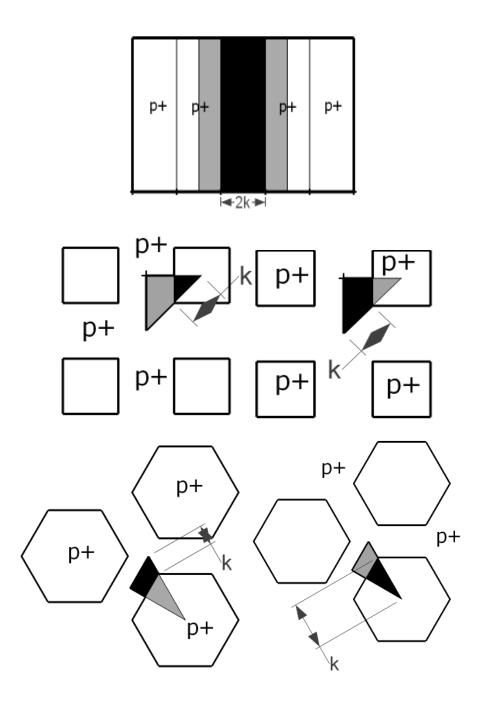

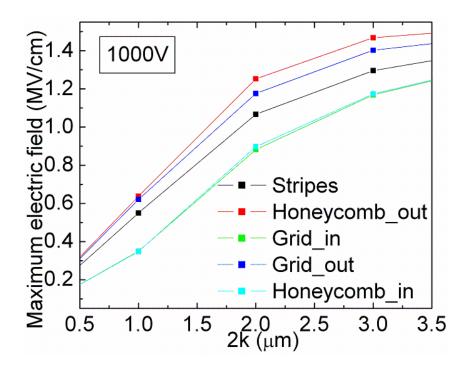

| Figure 22 Top views of various anode layouts of JBS diode                           |

| Figure 23 Maximum electric field versus width of Schottky region                   | 52 |

|------------------------------------------------------------------------------------|----|

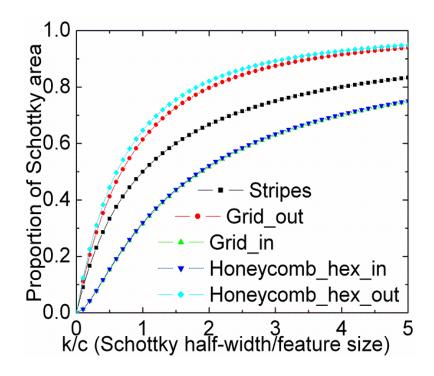

| Figure 24 Proportional Schottky area (FOM) of different layouts                    | 53 |

| Figure 25 Equipotential lines showing effect of small feature sizes on field       | 55 |

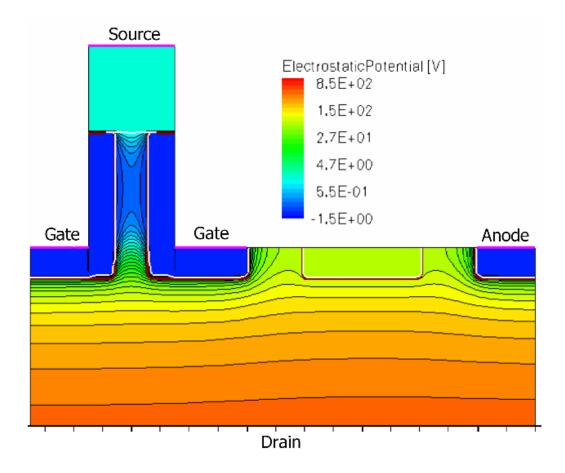

| Figure 26 Electric field along a vertical line across the PN junction              | 55 |

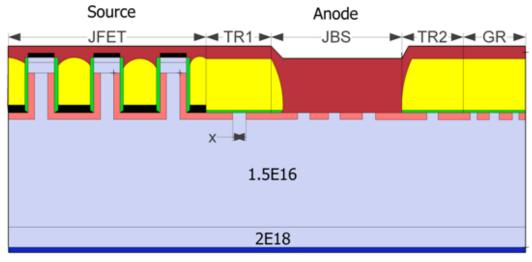

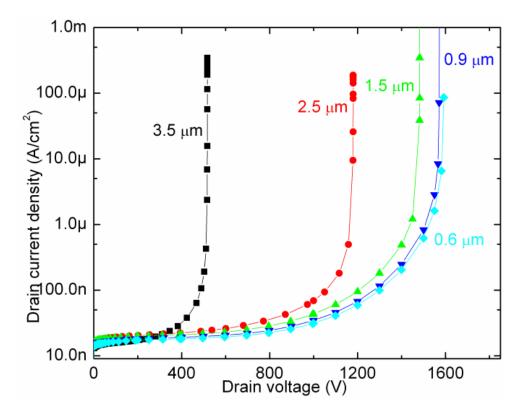

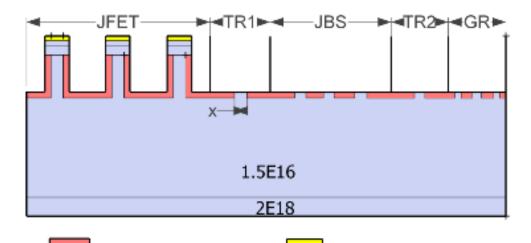

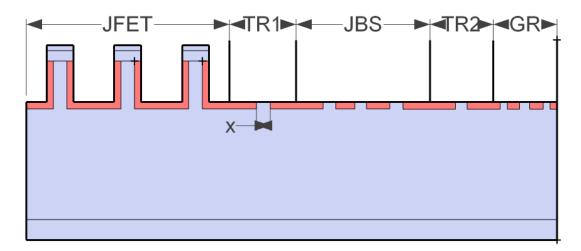

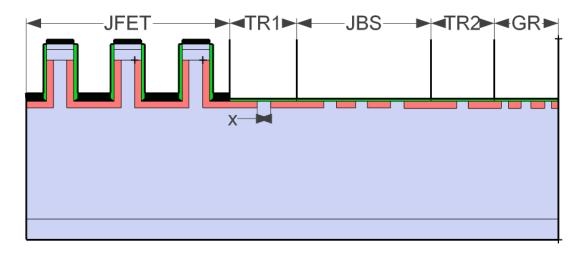

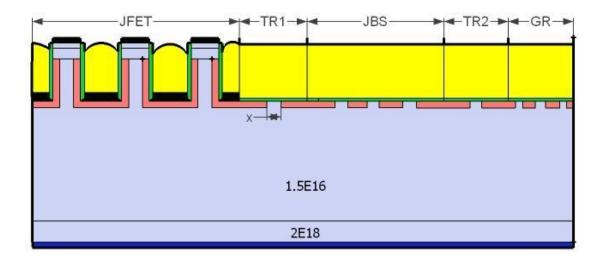

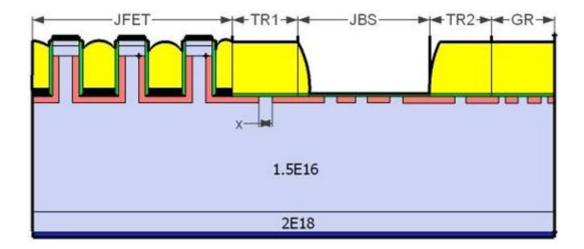

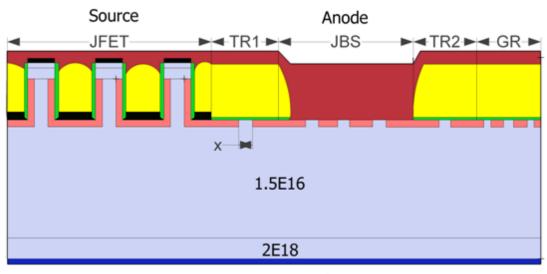

| Figure 27 Cross-section of the monolithically integrated device                    | 57 |

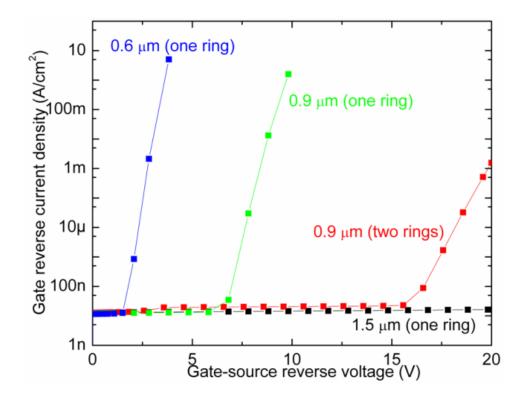

| Figure 28 Potential contours in blocking more in the transition region             | 59 |

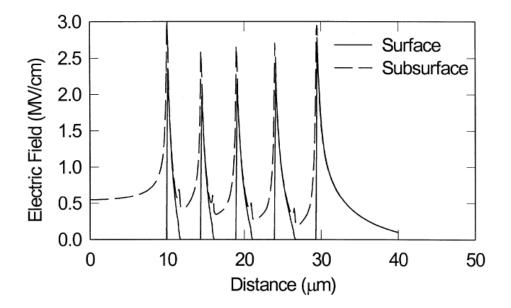

| Figure 29 Drain leakage current for different spacings between transition rings    | 59 |

| Figure 30 Gate-source reverse leakage cureent for combinations of transition rings | 60 |

| Figure 31 Electric field in non-uniform guard ring termination                     | 62 |

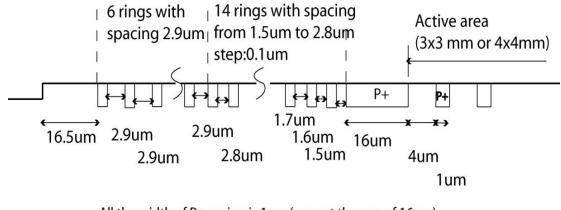

| Figure 32 Cross-section of guard rings to block 1200V                              | 63 |

| Figure 33 Fundamental block of devices on mask for fabrication                     | 64 |

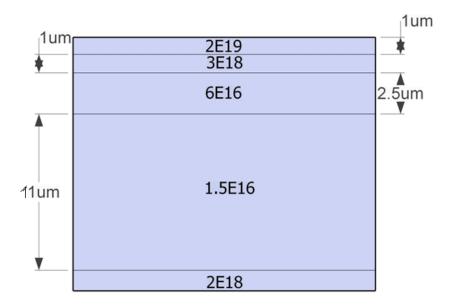

| Figure 34 Cross-sectional view of the wafer (not to scale)                         | 66 |

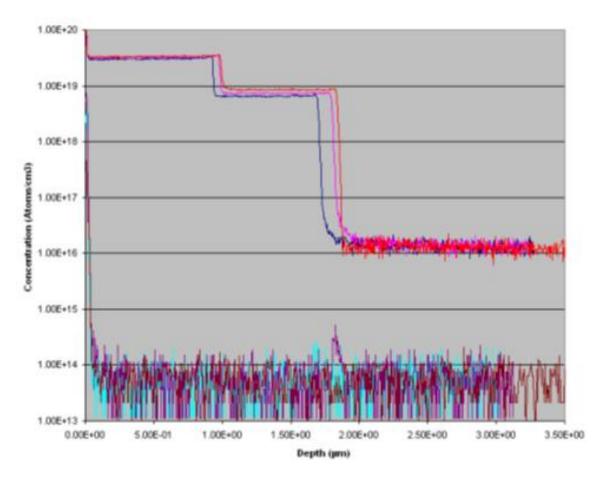

| Figure 35 SIMS results on Al concentration in the epitaxial layers                 | 67 |

| Figure 36 Cross-section after source mesa etching                                  | 67 |

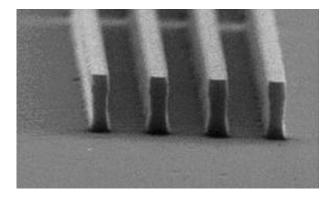

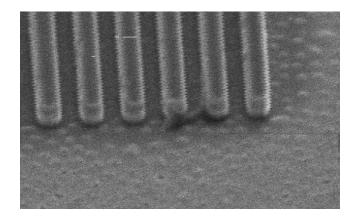

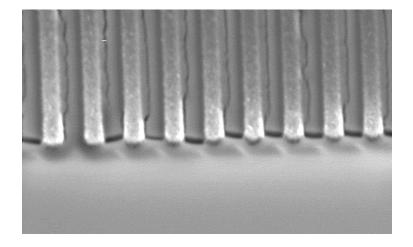

| Figure 37 SEM view of trenches in SiC obtained after ICP Bosch etching             | 68 |

| Figure 38 Cross-sectional view after ion-implantation                              | 70 |

| Figure 39 Cross-section after removing p-implanted mesa-top                        | 71 |

| Figure 40 Cross-section after formation of gate and source ohmic contacts          | 72 |

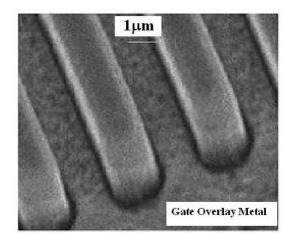

| Figure 41 SEM view of mesas after depositing gate overlay                          | 73 |

| Figure 42 Cross-section after filling VJFET trenches with dielectric               | 74 |

| Figure 43 Cross-section of the device just before final metallization              | 75 |

| Figure 44 Cross-section of the fabricated integrated switch                        | 75 |

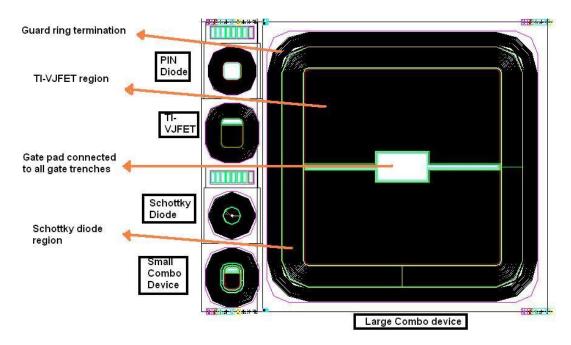

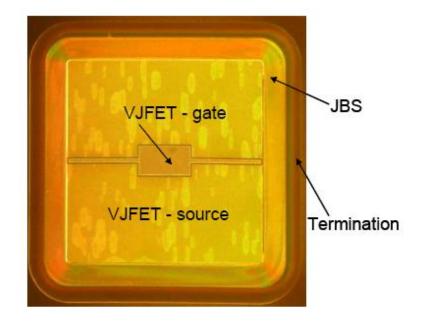

| Figure 45 Top view of the integrated switch showing layout of constituent elements | 76 |

| Figure 46 Optical photo of a 3" SiC wafer after device fabrication                 | 76 |

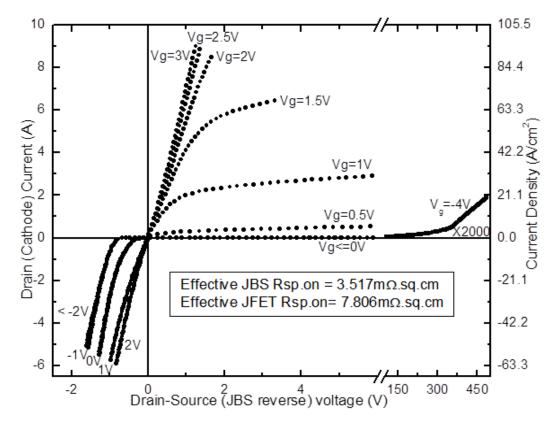

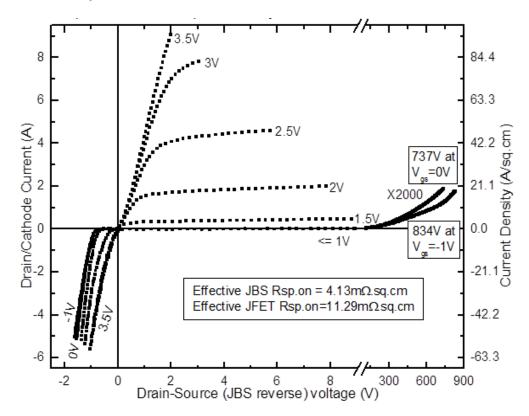

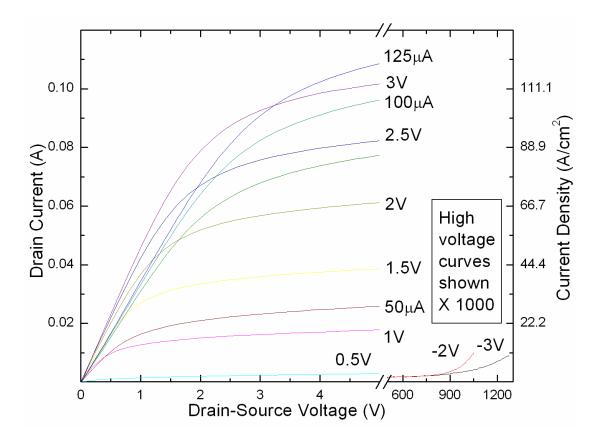

| Figure 47 Static I-V curves of normally-on integrated switch                       | 78 |

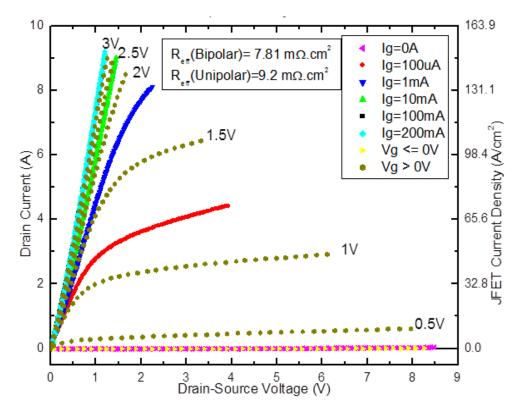

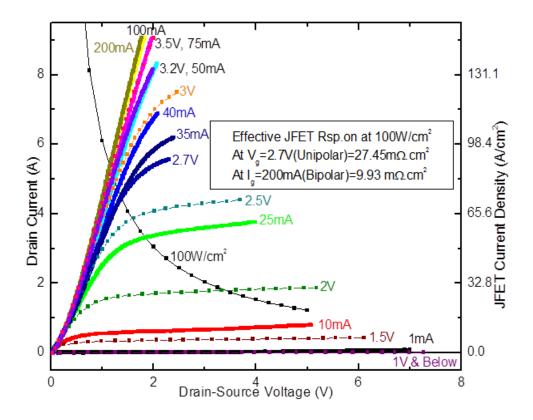

| Figure 48 Gate current and gate voltage controlled output curves from fig. 47             |

|-------------------------------------------------------------------------------------------|

| Figure 49 Static I-V curve of normally-on integrated switch80                             |

| Figure 50 Gate current and gate voltage controlled conduction curves from fig. 4981       |

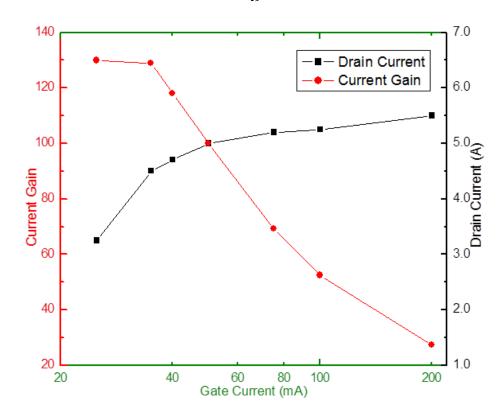

| Figure 51 Variation of current gain and drain current in normally off device              |

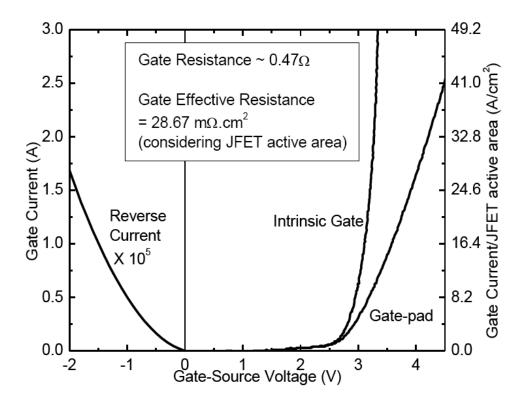

| Figure 52 Gate-source I-V of the normally-off device                                      |

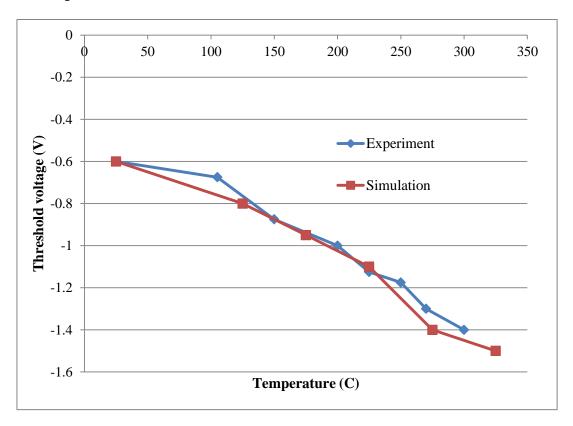

| Figure 53 Variation of threshold voltage of VJFET with temperature                        |

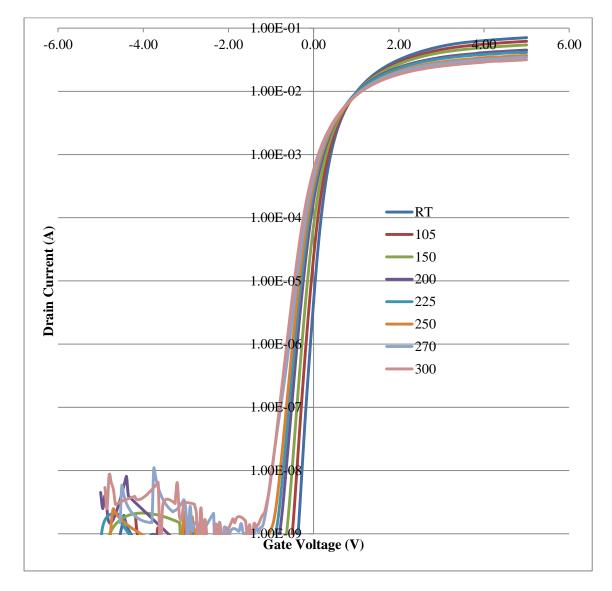

| Figure 54 Variation of transfer curve of VJFET with temperature                           |

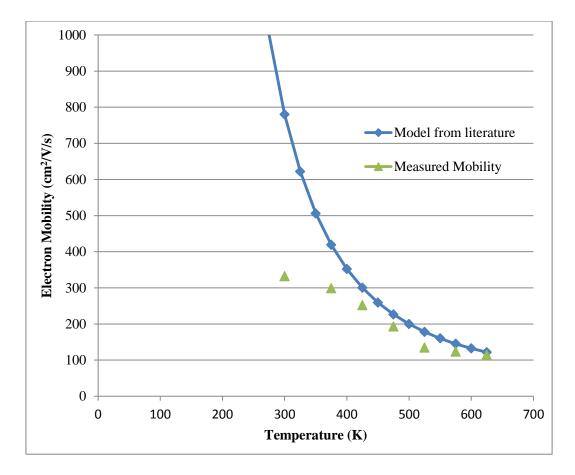

| Figure 55 Variation of mobility with temperature from model and experiment86              |

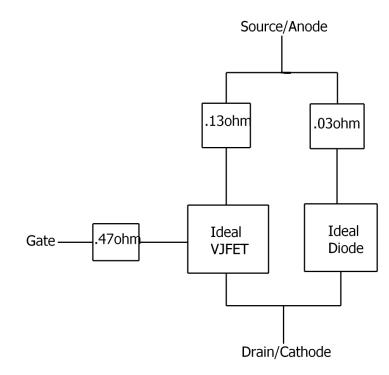

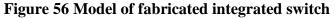

| Figure 56 Model of fabricated integrated switch                                           |

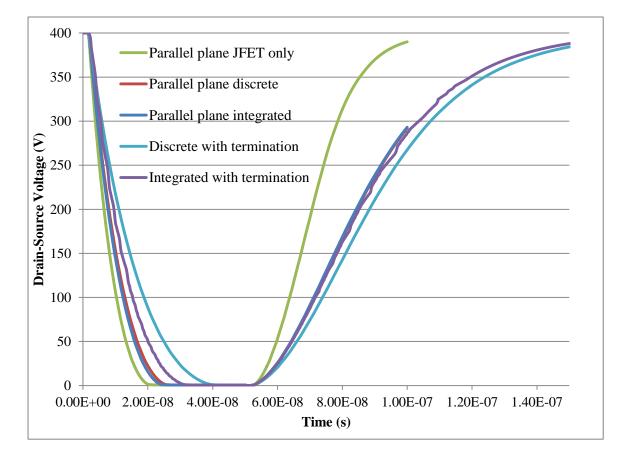

| Figure 57 Mixed mode TCAD switching curves under model in fig. 56                         |

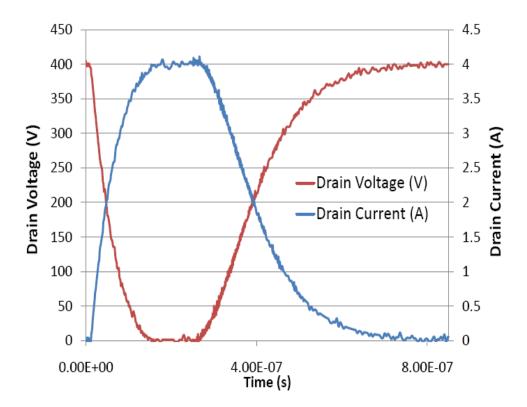

| Figure 58 Experimental switching curves of the integrated device                          |

| Figure 59 An unsuccessful scheme for integration of VJFET and diode90                     |

| Figure 60 An alternative scheme for integrated SiC JFET and antiparallel diode91          |

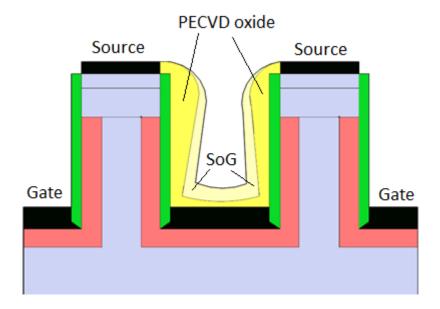

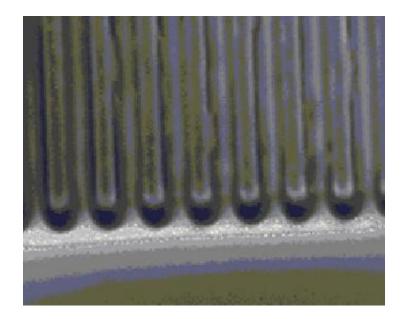

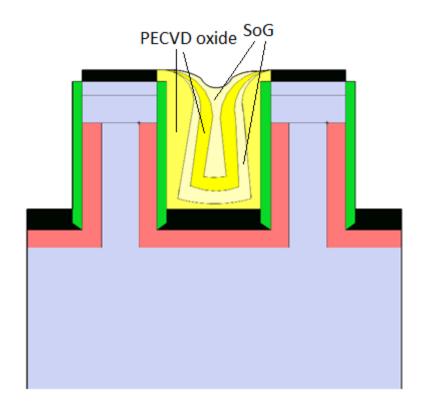

| Figure 61 Cross-section of VJFET before trench-filling                                    |

| Figure 62 SEM image of VJFET mesas before trench filling96                                |

| Figure 63 SEM image of VJFET mesas with SOG etched back97                                 |

| Figure 64 Cartoon of cross-section of VJFET with one layer of SiO <sub>2</sub> and SOG98  |

| Figure 65 SEM view of VJFET mesas after SiO <sub>2</sub> and SOG planarization            |

| Figure 66 Cartoon of cross-section of VJFET with SiO <sub>2</sub> and SOG planarization99 |

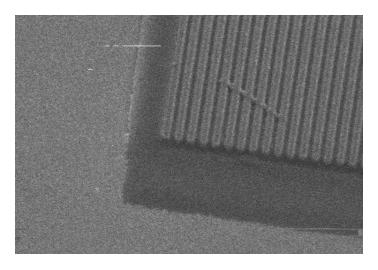

| Figure 67 SEM view of gate-pad and trenches in VJFET before final metalization. 100       |

| Figure 68 Static I-V curves of a VJFET with SOG-based trench filling101                   |

| Figure 69 Cross-section of VJFET showing domain of 2-D solution106                        |

#### **1. INTRODUCTION**

#### **1.1 Power Devices**

As we grapple with burgeoning demand for energy, efficiency of power management is often identified as an area for continuous improvement. Electric power inevitably has to go through multiple transformation and management steps between its generation and end-use. In the early days, such systems worked on mechanical, hydraulic, magnetic and later vacuum tube principles. But with the advent of semiconductor electronics, it became cheaper and more efficient to use Silicon-based electronic devices to manage power and deliver it at the voltage, current and frequency required.

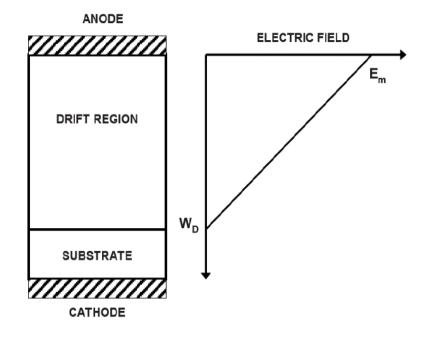

Losses in power devices are either static losses when they are in steady state or dynamic losses when they are switching between states. Majority carrier or unipolar devices like MOSFETs and Schottky diodes have negligible switching losses and are hence preferred in power circuits. The ideal device will be unipolar and have low onresistance, low leakage current while off and high breakdown voltage. These are conflicting requirements because to have a low on-resistance ( $R_{on}$ ), the drift region of the device should be thin and heavily doped. In that case though, slope of electric field v/s distance from junction in reverse bias shown in fig. 1 is high and the voltage that the device can block ( $V_B$ ) before the maximum electric field reaches the critical value for onset of breakdown ( $E_c$ ) is lower. This trade-off between the on-state and off-state static losses leads to a "unipolar limit" for the on-resistance of power devices, which can be expressed as

$$R_{on} \propto \frac{V_B^2}{\varepsilon \mu E_c^3} - - - (1)$$

$\mu$  is the mobility of majority carriers and  $\varepsilon$  the absolute permittivity of the material.

Since  $R_{on}$  is proportional to the square of  $V_B$ , the on-state loss at high voltages increases prohibitively for unipolar devices. At a certain high voltage, the reduction in  $R_{on}$  due to conductivity modulation in bipolar devices outweighs the increased dynamic losses for many applications. So whereas the Si power MOSFET is the most popular power switch up to ~600V, the Si Insulated Gate Bipolar Transistor (IGBT), a bipolar device, is more popular at higher voltages.

To break the unipolar limit of Silicon, either the rate of increase of  $R_{on}$  with  $V_B$  or the material constants in (1) has to be changed. The former can be achieved by various "charge coupling" methods which utilize 2 and 3 dimensional variation of carrier concentration to make the electric field v/s x plot flat without reducing the drift layer concentration very much. One such technique has been implemented in "superjunction" MOSFETs [2] which have increased the range of useful operation of Si MOSFETs above 800 V. At the basic level, this involves forming p and n columns in the drift layer such that when the charges are balanced and the columns completely

depleted, electric field will be uniform along x. Using this technique,  $R_{on}$  can at best be made proportional to  $V_B$  rather than  $V_B^2$  [1]. This is impressive but only an incremental improvement over traditional technology. However, by using materials for which the material constants in (1) are much higher,  $R_{on}$  can be reduced by orders of magnitude for the same  $V_B$ .

#### **1.2 4H-SiC for Power Devices**

Many properties of semiconductors relevant to power device operation are given in Table 1. The outstanding properties of 4H-SiC include wide band-gap, high electron saturation velocity and high thermal conductivity [3]. They make 4H-SiC a remarkable material for high power, high temperature and high frequency devices.

Wide band-gap allows 4H-SiC devices to operate at much higher temperatures (up to 600C) compared to Silicon devices without undue leakage current. Wide band-gap also endows 4H-SiC with a critical electric field of 2-3 MV/cm (depending on doping and temperature), which is an order of magnitude higher than that of Silicon. 4H-SiC devices exceed the Si unipolar limit by more than two orders of magnitude, which allow 4H-SiC devices to be designed with a thinner drift layer and hence lower on-resistance than Si for the same blocking voltage requirement. This also allows a single 4H-SiC device to operate beyond the 11 kV range.

High thermal conductivity and inertness also make SiC suitable for applications at high temperature. The power density is higher and cooling demand much lower in SiC, which saves installation cost as well as costs of weight and bulk of the system. This is especially attractive in applications like hybrid cars where weight loss very clearly translates to improved efficiency.

| Material | $\mathbf{E}_{\mathbf{g}}$ | ni                    | ε <sub>r</sub> | μ <sub>n</sub>       | Ec    | Vsat                 | λ      | Direct   |

|----------|---------------------------|-----------------------|----------------|----------------------|-------|----------------------|--------|----------|

|          | eV                        | cm-3                  |                | cm <sup>2</sup> /V·s | MV/cm | 10 <sup>7</sup> cm/s | W/cm·K | Indirect |

| Si       | 1.1                       | 1.5×10 <sup>10</sup>  | 11.8           | 1350                 | 0.3   | 1.0                  | 1.5    | Ι        |

| Ge       | 0.66                      | 2.4×1013              | 16.0           | 3900                 | 0.1   | 0.5                  | 0.6    | Ι        |

| GaAs     | 1.4                       | 1.8×10 <sup>6</sup>   | 12.8           | 8500                 | 0.4   | 2.0                  | 0.5    | D        |

| GaP      | 2.3                       | 7.7×10 <sup>-1</sup>  | 11.1           | 350                  | 1.3   | 1.4                  | 0.8    | Ι        |

| InN      | 1.86                      | ~103                  | 9.6            | 3000                 | 1.0   | 2.5                  | -      | D        |

| 3C-GaN   | 3.27                      | 8×10 <sup>-9 *</sup>  | 9.9            | 1000                 | 1     | 2.5                  | 1.3 *  | D        |

| 2H-GaN   | 3.39                      | 1.9×10 <sup>-10</sup> | 9.0            | 900                  | 3.3   | 2.5                  | 1.3    | D        |

| 3C-SiC   | 2.2                       | 6.9                   | 9.6            | 900                  | 1.2   | 2.0                  | 4.5    | Ι        |

| 4H-SiC   | 3.26                      | 8.2×10-9              | 10             | 720ª                 | 2.0   | 2.0                  | 4.5    | Ι        |

|          |                           |                       |                | 650°                 |       |                      |        |          |

| 6H-SiC   | 3.0                       | 2.3×10-6              | 9.7            | 370ª                 | 2.4   | 2.0                  | 4.5    | Ι        |

|          |                           |                       |                | 50°                  |       |                      |        |          |

| Diamond  | 5.45                      | 1.6×10-27             | 5.5            | 1900                 | 5.6   | 2.7                  | 20     | Ι        |

| BN       | 6.0                       | 1.5×10-31             | 7.1            | 5                    | 10    | $1.0^{*}$            | 13     | Ι        |

| AlN      | 6.1                       | ~10-31                | 8.7            | 1100                 | 11.7  | 1.8                  | 2.5    | D        |

#### **Table 1 Properties of semiconductors for power device applications**

High electron saturation velocity allows 4H-SiC devices to be operated at higher current density and frequency when compared to Silicon devices. The applications of 4H-SiC power electronics could lead to lower energy loss and weight of power electronic components. In addition, higher chemical inertness and radiation resistance makes SiC devices suitable for harsh environments like nuclear power systems or outer space.

Other wide band-gap semiconductors which match or exceed the properties of SiC for power applications are GaN and diamond. However, SiC has many advantages over them which include its high compatibility with established Si processing technology, mature substrate and epitaxial growth technology which is already being commercialized and its exclusive (among wide band-gap semiconductors) property of growing natural oxide (SiO<sub>2</sub>) on the surface. GaN grown on Si or SiC substrates is an attractive alternative for lateral devices. However, lateral devices have much higher on-resistance than vertical devices, especially at higher voltages. So, while GaN devices are making inroads in high frequency (AlGaN/GaN High Electron Mobility Transistors (HEMTs)) and low voltage (< 600V) applications, they will not be as competitive at higher voltages until the quality of GaN substrates improves.

Commercially, micropipe defect free 4-inch 4H-SiC wafers with customized epi-layers are provided by many companies, like Cree, Dow Corning and II-VI. 4H-SiC power Schottky barrier diodes and Junction-Barrier Schottky (JBS) diodes are also commercially available up to 1700V from Infineon technologies, Cree etc 4H-SiC JFET is available from SemiSouth, United Silicon Carbide etc and Cree recently commercialized the SiC MOSFET. SiC power switches are nearing a tipping point and is widely predicted to take-off as a serious challenger to the dominance of Sibased devices in power electronics.

#### **1.3 SiC VJFET as Power Switch**

The most important characteristics of a good power switch are- high blocking voltage, low specific on-resistance with a small positive temperature coefficient to facilitate paralleling, high current gain and high switching speed. Bipolar devices, with conductivity modulation, are capable of very low on-resistance but they are not able to achieve high switching speed. Unipolar FETs on the other hand, are majority carrier devices which switch much faster and have high current gain. Among SiC unipolar FETs, MOSFETs will ideally be better since they have very high current gain. There has been great progress in power SiC MOSFETs [4, 5]. However, the reliability of the gate oxide of SiC MOSFETs under high electric field is still a major concern, which has led to many convoluted designs [6] being proposed that shield the gate oxide from high field but are difficult to manufacture. Other problems include poor temperature stability of the gate threshold voltage in the SiC MOSFET and low mobility in the enhancement channel which increases on-resistance. There is a

significant research effort underway to address these issues with the SiC MOSFET [7]. Meanwhile, SiC JFETs are much more reliable and capable of high voltage and current switching with lower power loss. A comparison between the best reported power switches in the 1000-2000 V range is shown in table 2. The SiC VJFET has more than an order of magnitude lower  $R_{sp.on}$  compared to charge compensated Si MOSFETs and under current technology performs better than SiC MOSFETs.

| Device                       | Blocking (V) | $R_{sp.on} (m\Omega.cm^2)$ |

|------------------------------|--------------|----------------------------|

| SiC VJFET [8]                | 1900         | 2.8                        |

| SiC MOSFET [9]               | 1500         | 3.7                        |

| Si Superjunction MOSFET [10] | 1100         | 54                         |

## Table 2 Performance of best reported power switches

With dedicated high temperature packages, 4H-SiC JFETs have been characterized at 450 °C [11] and have demonstrated life of at least 500 hours at 500 °C [12]. This enables SiC JFET switching circuits to operate over extremely wide temperature ranges. A DC-DC converter built with 4H-SiC JFETs and 4H-SiC Schottky diodes was tested at ambient temperature up to 400 °C [13] and 4H-SiC JFET switching experiments down to 30K have been reported [14].

JFETs can be designed, in terms of device structure, to be lateral (source, gate and drain terminals on the front side of the wafer) or vertical (source and gate terminals on the front side and drain terminal on the back side of the wafer). The lateral JFET is suitable for integrated circuits [15] but it is the VJFET that allows higher cell packing density and thus lower on-resistance. Hence it is the structure of choice for a power switch unless it is otherwise necessary that all three terminals are on the front side of the wafer.

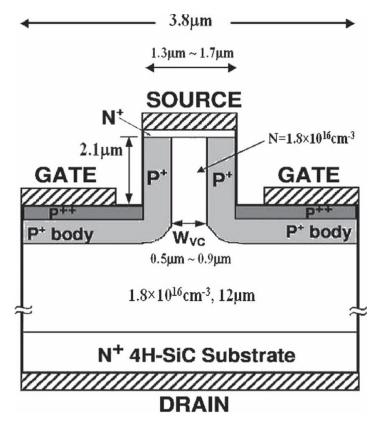

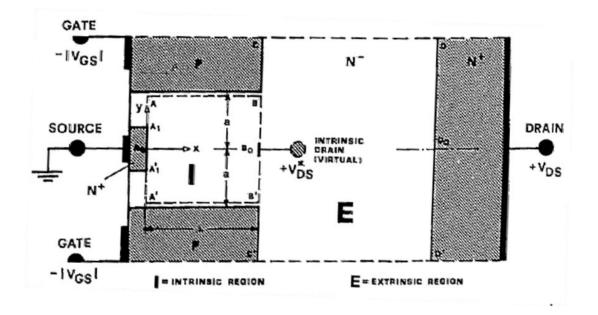

Figure 2 Cross-section of a SiC VJFET [16]

Cross-sectional view of a SiC Trenched and Implanted VJFET (TI-VJFET) is shown in fig. 2. SiC VJFETs need oppositely doped gate and source, which can be fabricated either with epitaxial re-growth or with ion implantation. Epitaxial regrowth in the middle of device fabrication is not desirable since it increases manufacturing costs. So, ion-implantation is preferred and robust processes for tilted ion implantation to form the vertical gate and channel in VJFETs have been developed [17]. Early SiC-VJFETs were developed with a combined vertical and lateral channel but the technology soon improved to realize a purely vertical VJFET, which provides lower on-resistance [16].

SiC VJFETs can be designed either to be normally-on (depletion mode; conducting high drain current at 0V gate bias) or normally-off (enhancement mode; blocking high drain-to-source voltage at 0V gate bias). Normally-on structures are always unipolar and can conduct higher current and provide lower specific on-

resistance than otherwise similar normally-off devices due to the wider channel opening. However, the normally-off structure is preferred for practical applications because it is fail-safe. The normally-off VJFET will not be short-circuited simply because the gate-drive fails. Normally-off devices can also be designed to have low on-resistance under unipolar operation [8].

#### **1.4 SiC JBS Diode as Rectifier**

The best power diode is the one that approaches the ideal of an open circuit (high blocking voltage) in one direction, a short circuit (low on-resistance and forward voltage drop) in the other and fast low-energy switching between the two states. The Schottky diode, where current is carried only by electrons (unipolar), is able to switch between the on and off states very fast. With the right choice of metal for the Schottky contact, the Schottky barrier can also be lowered enough to reduce the voltage drop in the on-state. However, the leakage current increases significantly with reverse voltage and for many applications it will be intolerably high well before the breakdown voltage. The 4H-SiC PN diode has much lower leakage current until breakdown but, the forward voltage drop is high and since it is a bipolar device, the switching speed is constrained by minority carrier storage in on-state.

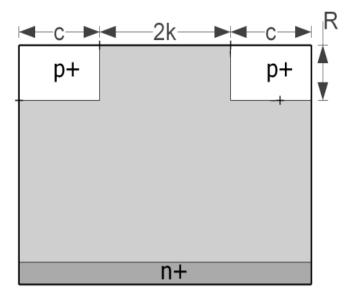

The JBS diode was proposed [18] to combine the good features of both PN and Schottky diodes. As shown in fig. 3, it has closely spaced PN and Schottky junctions such that under forward bias, most of the current is carried across the Schottky junction which has a lower voltage drop and under reverse bias, the depletion regions from the PN junctions widen to cover the Schottky junction and shield it from high electric field and the consequent high leakage current. Although proposed initially for Silicon, this concept is even more suited to SiC where the forward voltage drop of PN diodes is higher and reverse leakage current lower. Many SiC JBS diodes have been reported [19, 20] over the years and it has now been commercialized in Infineon's second generation SiC Schottky diodes [21].

Figure 3 Cross-section of a JBS diode

#### **1.5 Monolithic Integration of Switch and Diode**

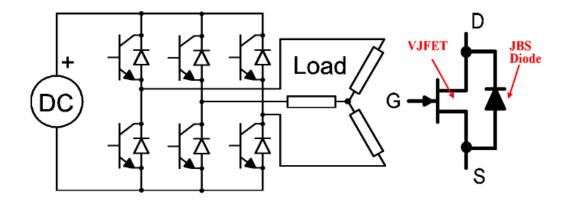

Power semiconductors are used to manage power delivery to many types of loads, most of which operate with current and voltage out of phase. In particular, the induction motor draws current at a significant lag compared to voltage because of its high inductance. When the switch serving such a load is suddenly turned off, the current only falls gradually. Since this switch itself is then open, a parallel path needs to be provided such that the current can loop through the load and this path. This path needs to be uni-directional since it should not conduct any forward current when the switch is finally in the off-state. So, a diode is connected anti-parallel to the power switch, called the flyback diode or freewheeling diode, in most power circuits like the 3-phase inverter shown in fig. 4.

Figure 4 3-phase inverter, a typical power circuit with switch and anti-parallel diode

Another advantage of the switch-antiparallel diode pair is in "synchronous rectification". In this scheme, the switch is turned on when the diode is conducting and turned off when it is blocking such that it can add to the diode's forward current and reduce on-state loss.

The common combination of the power switch and anti-parallel diode has prompted many manufacturers to provide such integrated chips [22]. Such modules reduce chip area and make it easier for manufacturers to parallel smaller area higher yield devices for a particular current rating rather than using higher area devices. To reduce component count, circuit parasitics, cost & chip size and to improve reliability, it is desirable to integrate the power switch and anti-parallel diode monolithically. Such a monolithically integrated power SiC BJT and diode has been reported [23]. Methods for monolithic integration of the SiC VJFET and diode have also been patented [24] but such devices have not yet been demonstrated.

### **1.6 Field-Termination in Power Devices**

Power devices operate at high voltages in the blocking mode. Along the direction of current transport, the space-charge region drops this voltage such that the electric field decreases linearly away from the junction. Under this 1-D

approximation, iso-electric field contours are parallel to the junction. But since a power device is of finite size, edges of the device are formed by cleaving the substrate. If this irregular surface were to be exposed to high electric field, voltage will not be dropped smoothly across the epitaxial layer. So, while the back side (non-junction) contact of a discrete power device covers the entire face, front side contacts cover a smaller area outside which the potential rises to that at the backside. Hence, the high voltage at the junction also has to be dropped across the surface of the device. If no special "edge-termination" schemes are used, this voltage drops abruptly at the edge, causing a high electric field which leads to device breakdown well below the parallel plane breakdown limit. So, various electric field termination schemes have been developed to spread the lateral electric field at the edge of the device over a wide enough region such that lateral breakdown voltage approaches the parallel-plane breakdown voltage [1].

Edge-termination schemes can generally be divided into two types- chargesensitive and dimension-sensitive. Charge-sensitive edge termination schemes extend the lateral junction using an area with just the right number of implanted carriers at avalanche, the most popular of which is Junction Termination Extension (JTE)[25]. JTE is very sensitive to the implant dose. Dimension-sensitive schemes like implanted field rings [26] or metal rings create multiple PN junctions such that potential is equalized around the rings and gradually dropped from the anode to the edge. Guard ring termination is very sensitive to the width and spacing of the rings. However, it is particularly advantageous for SiC VJFETs and JBS diodes since those devices already use high dose p+ implantation.

When multiple power devices are monolithically integrated, field termination is required not only at the edges, but also between them. For example, when the VJFET and anti-parallel diode are integrated, the gate of the VJFET has to be isolated from the anode of the diode with field termination structures. The design considerations of such inter-device field termination are different from that of edge-field termination and need to be optimized for each particular case, one example of which will be provided in this thesis.

#### 1.7 Outline of Ph. D. Thesis

This thesis aims to advance the field of power devices by designing and demonstrating a monolithically integrated SiC based switch and anti-parallel diode for power electronic applications. In pursuit of that central objective, this work develops

- 1. The first 2-D compact model for reverse leakage current in high voltage JBS diodes which completes the analytical theory of the JBS diode.

- 2. A new 2-D analytical model for forward blocking performance of a SiC VJFET with realistic gate-channel junction by extending previous such models for abrupt gate-channel junction.

- Closed form design equations for the design parameters of the SiC VJFET and JBS diode based on the analytical models presented above.

- 4. Design of a SiC VJFET with a monolithically integrated JBS diode without adding any steps to the VJFET fabrication process.

- 5. Design of masks and cleanroom fabrication of the integrated switch to block high voltage, handle high current and exhibit expected "third quadrant" operation as well as synchronous rectification.

- 6. Static, dynamic and temperature characterization of the fabricated device and analysis of the effects of monolithic integration on electrical characteristics.

- 7. Development of a novel spin-on glass based process for filling VJFET trenches and demonstration of operation of such a VJFET.

These steps in pursuit of the thesis objective involve original contributions to the current state of the art of power devices and will be detailed in the subsequent chapters of this work.

#### 2 ANALYTICAL MODELING OF VJFET AND JBS DIODE

The advantages of monolithic integration of a 4H-SiC power switch and antiparallel diode were elaborated in section 1.5. In section 1.3, it was seen that the best developed power switch technology is that of the 4H-SiC VJFET. In section 1.4, the advantages of the SiC JBS diode have been explained. 4H-SiC VJFET and JBS diode are uniquely suited for monolithic integration as a power electronic building block, not only because of their superior properties as power switch and power diode, but also because they share many fabrication steps and the integrated device can be fabricated without any additional process steps from that of the VJFET.

To design optimized power switches and diodes, it is desirable to have relationships between design parameters and electrical characteristics. While finiteelement Technology Computer Aided Design (TCAD) simulations are more accurate, they only yield results for particular design parameters and not a continuous relationship showing trends in performance based on device parameters. Analytical continuous models can be developed empirically from TCAD simulations but their validity is doubtful beyond the contours of the specific simulation data from which they were built. Analytical models derived from fundamental laws of physics are inherently more reliable and easier to use within the limits of the assumptions made in their derivation. This chapter develops a new 2-D analytical model for the JBS diode and extends an existing 2-D analytical model for SiC VJFETs.

#### 2.1 Analytical Modeling of JBS Diode

A 1-D analytical model, which provided closed form equations for forward and reverse I-V curves [18] was developed for low voltage Silicon JBS diodes in the 1980s, but the following assumptions made there do not hold at high reverse voltages and high electric fields that are found in wide band-gap devices.

- Rise of electric field at the Schottky contact was assumed to be independent of the surrounding P-N junctions before pinch-off, where pinch-off is calculated by one-dimensional analysis in the Schottky channel. But electric field at the Schottky contact in a JBS diode actually falls behind that of the corresponding Schottky diode well before such a pinch off point as the effect of P-N junctions increases gradually.

- 2. After pinch-off, electric field at the Schottky contact was assumed to remain constant as reverse voltage increases, in effect assuming that the entire rise in reverse voltage is absorbed by the potential barrier forming in the channel. But from simulations, it is obvious that electric field at the contact continues to rise smoothly, apparently under the same dynamics as before pinch-off.

For Silicon diodes, the assumptions above, especially 2, don't introduce much error because electric field under reverse bias remains low enough that current conduction is mainly due to thermionic emission which is not very sensitive to the electric field. But wide band-gap diodes, where the avalanche limit is higher, can sustain higher electric fields at which tunneling through the barrier gives much higher current than thermionic emission over it. Tunneling is very sensitive to electric field at the Schottky contact and hence assuming the electric field to be constant post pinchoff leads to unacceptable error. [27] proposes a model that works for high voltage JBS diodes, but it relies on curve-fittings of simulation data rather than physical considerations to arrive at the important relationship between voltage and maximum electric field under reverse bias. That model also has to be re-built as doping of the epitaxial layer changes and it fails to include the effect of punch-through of the drift layer at high voltages. [28] proposes an analytical model but it ignores punch-through, restricts implantation straggle to a circular profile and assumes the depletion region to have circular symmetry with respect to the P-N junction. This ignores the effect of the Schottky junction on the ionized donors and assumes the electric field to be influenced only by surrounding P-N junctions like in a guard-ring field termination region.

In this work, we develop for the first time a fully analytical model in reverse bias for a high voltage punch-through JBS diode leading to a closed form I-V relationship and validate these design equations using simulations and experimental data from SiC diodes.

## 2.1.1 Notation

- (x, y)- Co-ordinates with reference to origin at the center of the Schottky region with x into the anode surface and y perpendicular to P-N and Schottky stripes.

- 2k- Width of Schottky region.

- b- Distance from anode at which the variation of potential in a JBS diode can be approximated to be one-dimensional.

- $\Phi$  Electrostatic potential with reference to zero at the origin.

- $\Phi_{p}$  Poisson component of the electrostatic potential  $\Phi$ .

- $\Phi_{l}$  Laplace component of the electrostatic potential  $\Phi$ .

- ρ- Local space charge density.

- ε- Permittivity of the semiconductor medium.

- R- Depth of ion implantation.

- $k_{0-3}$  Integration constants in the solution of Poisson equation.

- N<sub>d</sub>- Ionized donor concentration in the epitaxial (drift) layer.

- $V_b$  Potential at (b,0).

- W- Thickness of the depletion region when the drift layer has not been punched through.

- W<sub>d</sub>- Thickness of the drift layer.

- E<sub>m</sub>- Electric field at the junction of a 1-D diode without punch through.

- E<sub>mp</sub>- Electric field at the junction of a 1-D diode after punch through.

- E<sub>p</sub>- Electric field in a diode after punch through.

- V<sub>R</sub>- Reverse voltage applied to a JBS diode.

- $V_{R}$  Reverse voltage applied to a Schottky diode at which it has the same  $V_b$  as the corresponding JBS diode at reverse voltage  $V_R$ .

- E<sub>mps</sub>- Electric field at the junction of a Schottky diode after punch through.

- E<sub>mpj</sub>- Electric field at the junction of a JBS diode after punch through.

- (x',y')-Point on the boundary of the P-N junction.

- $J_{Sch}$  Current density over the metal-semiconductor junction due to thermionic emission.

- J<sub>T</sub>- Current density through the metal-semiconductor junction due to tunneling.

- A\*- Effective Richardson constant.

- T- Temperature in °K.

- q- Charge of electron.

- $\Phi_{\rm B}$  Schottky barrier height.

- k- Boltzmann constant.

- m<sub>0</sub>- Rest mass of electron.

- m\*- Effective mass of electron in the semiconductor.

- $\hbar$  Planck's constant.

- h- Length of a Schottky finger in a striped JBS diode.

- I<sub>s</sub>- Current carried by one Schottky finger.

$J_{R}$ - Reverse current density in the JBS diode.

P- Pitch of the interdigitated stripes of P-N and Schottky regions in the JBS diode.

- 2k'- Width of a Schottky region such that uniform thermionic emission current density across it will yield the same total current as in a JBS diode with the same thermionic emission current density at the center of its Schottky region.

- 2k"- Width of a Schottky region such that uniform tunneling current density across it will yield the same total current as in a JBS diode with the same tunneling current density at the center of its Schottky region.

- $\alpha_{R}$  Proportional Schottky area in a JBS diode with interdigitated stripes of P-N and Schottky regions.

- α<sub>O</sub>- Proportional Schottky area in a JBS diode with honeycomb layout of P-N and

Schottky regions with Schottky region outside the hexagon.

- c- Ratio of the half-widths of P-N and Schottky regions in a JBS diode with a layout of interdigitated stripes.

- m- Distance from center to edge of the hexagonal patterns in a JBS diode with honeycomb layout.

- 2n- Width of the streets between hexagonal patterns in a JBS diode with honeycomb layout.

- d- Ratio of the minimum half-widths of P-N and Schottky regions in a JBS diode with honeycomb layout having Schottky region outside the hexagon.

### 2.1.2 Reverse Voltage and Electric Field

In a JBS diode under reverse bias, almost all the current conduction takes place through the Schottky junction. Under the high electric field that SiC JBS diodes operate at, thermionic emission current across the Schottky barrier, which by itself is of a similar order of magnitude as the reverse current across a P-N junction, is enhanced due to image-force induced lowering of the Schottky barrier and quantummechanical tunneling, both of which are many orders of magnitude greater than it. So, under reverse bias, current carried across the Schottky junction is significantly larger than that across the P-N junction and hence the error resulting from restricting the analysis to the current flowing across only the Schottky barrier is miniscule. To find the current density in a JBS diode, we find the electric field at the Schottky barrier as a function of the reverse voltage by solving Maxwell's electrostatic equation (Poisson equation) and then relate this electric field to the current. The former approach, by splitting the 2-D Poisson equation, is similar to published analytical solutions of Silicon power FETs and SITs [29], whereas the latter is based on attempts to form closed-form solutions to SiC Schottky diodes [27, 30].

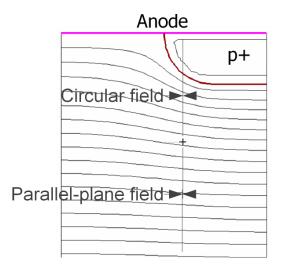

In cross-section, width of the un-implanted region of the anode is 2k and depth of implantation is R. Electric field at the Schottky contact is expected to be highest at the center of the un-implanted region since it is farthest from the shielding P-N junctions. To find the electric field at the contact, it is sufficient to solve the 2-D Poisson equation in a rectangular region which stretches across the Schottky junction and from the anode to a distance b away, as shown in fig. 5. "b" is the distance from the anode till which the P-N junctions will affect potential distribution. At distances greater than b from the anode, the JBS diode is assumed to have a 1-D potential variation quite like a Schottky diode. Considering the anode to be the zero-potential reference, Dirchlet boundary conditions [31] for voltage in the rectangular domain are zero at the anode,  $V_p$  (a function of the cathode voltage) at x=b and on the sides, a voltage which varies with distance from anode.

Figure 5 Cross-sectional views of a planar JBS diode

The Poisson equation to be solved is

$$\nabla^2 \phi(x, y) = \frac{-\rho(x, y)}{\varepsilon} - - - (2)$$

Numerical solution to this equation using the DESSIS simulator in Synopsys-TCAD Sentaurus [32] yields  $\Phi(x, y)$  as shown on the vertical axis in fig. 6. In reverse bias, potential under the Schottky junction is always greater than that under the P-N junction for the same value of x. But as x increases, they converge until at x= b they are nearly equal. To solve the 2-D Poisson equation analytically, it can be split into a 1-D Poisson equation along x- axis and a 2-D Laplace equation [29].

$$\phi(x, y) = \phi_p(x) + \phi_l(x, y) - - - (3)$$

Such that

$$\nabla^2 \phi_p = \frac{d^2 \phi_p}{dx^2} = \frac{-\rho}{\varepsilon} - - - (4)$$

and

$$\nabla^2 \phi_l = 0 - - - (5)$$

### Figure 6 Electrostatic potential near the anode of a JBS diode under reverse bias

Assigning the entire Poisson component to the x- axis is valid due to the mirror symmetry of the problem across the x-axis. This problem has exact solutions, dependent on boundary conditions, as follows.

$$\phi_p(x) = k_2 x - \frac{q N_d}{2\varepsilon} x^2 + k_0 - - -(6)$$

and

$$\phi_l(x,y) = k_1 Cosh\left(\frac{\pi y}{b}\right) Sin\left(\frac{\pi x}{b}\right) + k_3 - - (7)$$

Combining the two,

$$\emptyset(x,y) = k_1 Cosh\left(\frac{\pi y}{b}\right) Sin\left(\frac{\pi x}{b}\right) + k_2 x - \frac{qN_d}{2\varepsilon} x^2 - - - (8)$$

In (8), the constant  $k_0 + k_3$  has been set to zero to have zero potential at x = 0.

Now, the electric field at (x, y), (x, 0) and (0, 0) are

$$\frac{\partial \phi}{\partial x}(x,y) = \frac{\pi k_1}{b} Cosh\left(\frac{\pi y}{b}\right) Cos\left(\frac{\pi x}{b}\right) - \frac{qN_d}{\varepsilon}x + k_2 - - - (9)$$

$$\frac{\partial \phi}{\partial x}(x,0) = \frac{\pi k_1}{b} Cos\left(\frac{\pi x}{b}\right) - \frac{qN_d}{\varepsilon}x + k_2 - - - (10)$$

$$\frac{\partial \emptyset}{\partial x}(0,0) = \frac{\pi k_1}{b} + k_2 - - -(11)$$

Electric field here is defined as positive along the negative x direction so as to have a positive electric field under reverse bias. To determine  $k_1$  and  $k_2$ , we set the voltage at the bottom of the domain

$$\phi(b,0) = k_2 b - \frac{q N_d}{2\varepsilon} b^2 = V_p - - - (12)$$

(12) relates  $k_2$  and b to the potential  $V_p$  at (b, 0). Since effects of the P-N junctions on both sides are confined to x < b, electric field for x > b decreases linearly with increasing x as in a 1-D diode. So, V<sub>p</sub> can be found by comparison with a Schottky diode of the same drift layer. The parameter b, a function of 2k and R, is then used to account for the shape of the side-implantation profile. In choosing b, we'll also be guided by simulation results as b is the distance from the Schottky contact up to which the slope of electric field v/s x is different from that found in the corresponding Schottky diode. Finally, k1 will be found by using the boundary condition that  $\Phi$  is zero along the p-n junction. Considering a circular P-N interface for the model (other lateral implantation profiles can be modeled by changing b) and assuming that the P-N interface is equipotential with zero potential, k<sub>1</sub> can be suitably designed. Since the Schottky junction is considered the zero potential point, the voltage at the P-N junction will actually be offset by the voltage drops at the metal-p+ contact and the part of the reverse voltage dropped on the p-side of the junction. But these voltages are negligible at high reverse bias for extremely one-sided P-N junctions as are found in high voltage diodes.

To find  $V_b$  and b, electric field at the junction of a 1-D Schottky diode is first related to the applied reverse voltage as shown in fig. 7. We consider the drift layer here to already have punched through, which is a fair assumption at the rated reverse voltage in a JBS diode. The diode before punch through can also be treated in an analogous fashion. Punch through takes place at a reverse voltage given by

## Figure 7 Electric field distribution in corresponding JBS and Schottky diodes

After punch through,

$$\left\{E_{mp} - \frac{qN_dW_d}{\varepsilon}\right\}W_d + \left(\frac{qN_dW_d}{\varepsilon}\right)\frac{W_d}{2} = V_R - - -(14)$$

But from the Poisson equation,

$$E_p(x) = E_{mp} - \frac{qN_d x}{\varepsilon} - - - (15)$$

From (14) and (15),

$$E_p(x) = \frac{V_R}{W_d} + \frac{qN_dW_d}{2\varepsilon} - \frac{qN_dx}{\varepsilon} - --(16)$$

$$\therefore V(x) = \int_0^x E_p(x)dx = \frac{V_Rx}{W_D} + \frac{qN_DW_Dx}{2\varepsilon} - \frac{qN_Dx^2}{2\varepsilon} - --(17)$$

Now,  $V_R$ ' is that voltage at which the corresponding Schottky diode will have the same  $E_p(b,0)$  as  $E_p(b,0)$  of the JBS diode at  $V_R$ . From fig. 7, it is clear that  $V_{R'} > V_R$ . To arrive at  $E_{mpj}$  v/s  $V_R$ , starting with the Schottky diode at  $V_R$ ' from (16),

$$E(b,0) = \frac{V_R'}{W_d} + \frac{qN_d}{2\varepsilon} \{W_d - 2b\} - - - (18)$$

But from (10),

$$E(b,0) = \frac{\partial \phi}{\partial x}|_{(b,0)} = \frac{-\pi k_1}{b} + k_2 - \frac{qN_db}{\varepsilon} - - - (19)$$

From (18) and (19),

$$k_{2} - \frac{k_{1}\pi}{b} = \frac{V_{R}'}{W_{D}} + \frac{qN_{D}W_{D}}{2\varepsilon} - - - (20)$$

To uniquely determine  $k_1$  and  $k_2$  in terms of b, we need another relationship involving at least one of them For that, we use the boundary condition of having a zero-potential P-N junction. At a point (x', y') on the circular P-N junction at angle  $\theta$ from the anode contact,

$$(x', y') = (RSin\theta, k + R - RCos\theta) - - - (21)$$

From (8),

$$\emptyset(x',y') = k_1 Cosh\left(\frac{\pi y'}{b}\right) Sin\left(\frac{\pi x'}{b}\right) + k_2 x' - \frac{qN_D}{2\varepsilon} (x')^2 = 0 - - (22)$$

A crucial assumption here is the extrapolation of Poisson equation solution from the rectangular domain to its neighbourhood. The trade-off is that for the criterion of constant voltage independent of y at the lower edge of the rectangle to be valid, the rectangle should have a small width (range of y) and for (21) to be valid at (x', y'), the width of the rectangle should be larger. The significance of the errors due to these conflicting requirements will be assessed by comparing results with those from simulation.

We can now derive an equation to calculate E and  $\Phi$  in the domain as a function of b and reverse voltage  $V_R$ '. But E and  $\Phi$  thus calculated are for another Voltage  $V_R$ . To relate  $V_R$  and  $V_R$ ', we use the areas under the curves in fig. 7.

$$\int_{0}^{b} E_{p} dx + \int_{b}^{W_{D}} E_{p} dx = V_{R} - -(23)$$

or

$$\int_{0}^{b} \left[ \frac{\pi k_{1}}{b} \cos\left(\frac{\pi x}{b}\right) - \frac{q N_{d} b}{\varepsilon} + k_{2} \right] dx + \int_{b}^{W_{D}} \left[ \frac{V_{R}'}{W_{D}} + \frac{q N_{D}}{2\varepsilon} (W_{D} - 2x) \right] dx$$

$$= V_{R} - -(24)$$

This becomes

$$\left[\frac{V_R'}{W_D} - \frac{qN_Db}{2\varepsilon}\right](W_D - b) + k_2b - \frac{qN_db^2}{\varepsilon} = V_R - - - (25)$$

From (10), (22) and (25),  $k_1$ ,  $k_2$  and  $V_R$  are related to the only remaining parameter b. The two extremes of side-implantation are zero side-implantation (rectangular profile) and 1:1 side-implantation (circular profile). From simulation, there is significant difference in E (0, 0) between the two cases. The parameter b will be used to adjust the model for these two conditions. Since b is the extent of the effect of the P-N junctions on potential, it increases with increasing k and R. For the circular profile, by comparing model and simulation data, the best linear fit is found to be for-

$$b = \frac{k}{2} + 3\frac{R}{2} - - - (26)$$

For the rectangular profile, it is

$$b = \frac{k}{2} + 2R - - -(27)$$

Both (26) and (27) have b > R, and are only valid when  $R \ll W_D$ . Similarity in the effects of R and k on the electric field can also be seen in fig. 8 which presents simulation results from Synopsys Sentaurus [32] for the case with no sideimplantation. It is clear that reducing k is as potent in lowering E(0,0) as increasing R. But increasing R increases the on-resistance at a much higher rate than reducing k. The effect of R and k on the on-resistance is shown in (44). Increasing R reduces the drift layer "seen" by the P-N junction, causing the diode to break down at lower reverse bias. Narrower k is also much easier to fabricate that deeper R. Thus, reduction of electric field at the anode contact is best achieved by reducing k. So, in the validation of this work, we assume a constant R of 0.5µm and vary k to control E(0,0). R = 0.5µm is a depth that is easy to achieve by implantation in SiC and has also been used in the experimental results presented later in this work. However the model we present is appropriate for all R<<W<sub>D</sub>.

Figure 8 Dependence of the electric field at (x,0) on R and 2k

In (26) and (27), as the coefficient of R is higher without side-implantation, b is greater and reduction in electric field at the Schottky interface is more pronounced. This supports the intuitive understanding that a more rectangular side-implantation profile brings the P-N junctions closer to the channel thereby enhancing the potential barrier created in the channel and shielding the electric field at the Schottky contact better. The value of  $\theta$  chosen to identify the point (x', y') is not found to affect the model parameters significantly. This is understandable as in the circular implant case used for the model, with increasing x', both y' and  $\Phi(x', 0)$  increase. Higher  $\Phi(x', 0)$  requires a higher y-value for the hyperbolic cosine factor to reduce  $\Phi$  to zero. For the model solutions found in the next section,  $\theta = 30^{\circ}$  is used. Throughout this analysis, we assume abrupt P-N junctions and implantation with constant box profile, i.e. constant p+ and n- doping.

Summarizing the model, to find E(0,0) we use (10) which relates it to  $k_1$  and  $k_2$ . Using b from (26) or (27), we solve (20), (22) and (25) simultaneously to obtain  $k_1$  and  $k_2$ . This leads to the following closed form relationship, after punch through, between the maximum electric field and reverse voltage.

$$E_{max} = E(0,0) = \frac{k_1 \pi}{b} + k_2 - - - (28)$$

The constants  $k_1$  and  $k_2$  are given by

$$k_{1} = \frac{V_{R} + \frac{qN_{D}}{2\varepsilon}(b^{2} + W_{D}^{2} - x'W_{D})}{\pi - \frac{W_{D}}{x'}Cosh\left(\frac{\pi y'}{b}\right)Sin\left(\frac{\pi x'}{b}\right) - \frac{\pi W_{D}}{b}} - - - (29)$$

$$k_{2} = \frac{V_{R}}{W_{D}} + \frac{qN_{D}}{2\varepsilon}\left(\frac{b^{2}}{W_{D}} + W_{D}\right) + k_{1}\pi\left(\frac{1}{b} - \frac{1}{W_{D}}\right) - - - (30)$$

Before punch-through, appropriate modifications to (20) and (25) will easily give electric field that will now depend on  $\sqrt{(V_R)}$  rather than  $V_R$  itself. But in that case, while the same method as above gives electric fields at particular reverse voltages, a closed form solution involves solving cumbersome quadratic equations. Since design of JBS diodes requires leakage current at and near rated reverse voltage, which is best designed to be after punch-through, the closed form solution for lower voltages is not explicitly worked out here, although the proposed model can be suitably modified for that purpose. Before punch-through, an approximate closed form solution for E (0, 0) is-

$$E_{max} = E_{max}|_{(W=W_D)} \sqrt{\frac{V_R}{V_{R(W=W_D)}}} - - - (31)$$

Figure 9 Comparison at V<sub>R</sub>=1000V of model (M) and simulation (S)

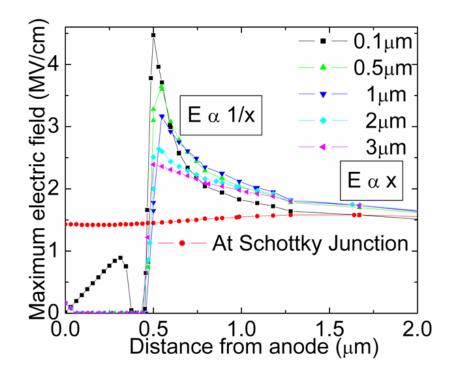

Electric field at (0, 0) with  $V_R$ = 1000V,  $W_d$  = 12µm and  $N_d$ = 7 X 10<sup>15</sup>cm<sup>-3</sup> is compared between the model and simulation results in Table 1 for both the rectangular and circular side-implant profiles. For the latter, E(x, 0) v/s x is also shown near the Schottky junction in fig. 9. Despite discrepancies in the exact shape of E(x, y), the model does predict very well the amount by which electric field reduces at the Schottky junction, which is key to JBS diode operation. In table 3, it is obvious that lateral spread of implantation makes a big difference in the electric field shielding achieved in a JBS diode. Smaller the lateral spread, more the shielding achieved (for the same effective Schottky region width). Practical implantation conditions will all lie between the squared and rounded side-implant assumptions. The simulation and model results were also compared at  $V_R$ =1600V with similar agreement as that obtained at 1000V. So, the validity of model, as expected, is independent of reverse voltage. At a low Schottky opening of 1µm, the maximum electric field "seen" by the Schottky contact is < 50% of the Schottky diode with same epitaxial layer thickness and doping.

|          | E(0,0) from Simulation |             | E(0,0) from Analytical Model |             |

|----------|------------------------|-------------|------------------------------|-------------|

|          | (MV/cm)                |             | (MV/cm)                      |             |

| 2k (µm)  | Circular               | Rectangular | Circular                     | Rectangular |

| 1        | 0.73                   | 0.54        | 0.74                         | 0.58        |

| 1.5      | 1.00                   | 0.87        | 1.02                         | 0.86        |

| 2        | 1.16                   | 1.07        | 1.19                         | 1.05        |

| 2.5      | 1.27                   | 1.19        | 1.29                         | 1.18        |

| 3        | 1.34                   | 1.30        | 1.36                         | 1.28        |

| Schottky | 1.61                   | 1.61        | 1.59                         | 1.59        |

Table 3 Comparison of the maximum electric field at the Schottky contact from the model and simulation for different implantation-straggle profiles at  $V_R$ =

## 1000V

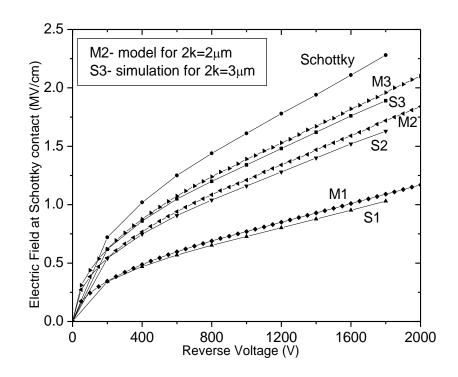

Variation of maximum electric field at the Schottky contact with applied reverse voltage at various Schottky openings, as predicted by the model and from simulation, are shown in fig. 10 for circular side-implantation and in fig. 11 for rectangular side-implantation. There is very good agreement between the model and simulation.

Figure 10 Comparison of model and simulation with circular side-implantation

Figure 11 Comparison of model and simulation with no side-implantation

At constant k, lower side-implantation reduces the maximum electric field at the Schottky contact without affecting the area available for forward conduction, which is clearly preferred. In the next section, the relationship between electric field and reverse leakage current is explored, which in combination with the relationship between voltage and electric field leads to final closed form solutions to the leakage current of JBS diodes under reverse bias.

#### 2.1.3 Electric Field and Leakage Current

The mechanisms for reverse current conduction in a JBS diode are thermionic emission across the Schottky barrier and quantum mechanical tunneling through it. Local current density due to thermionic emission is given by

$$J_{Sch} \approx A^* T^2 \exp\left(-\frac{q(\phi_B - \sqrt{\frac{qE}{4\pi\varepsilon}})}{kT}\right) \left(\exp\left(\frac{qV}{kT}\right) - 1\right) - - - (32)$$

In (32), the latter voltage-varying exponential can be neglected under high reverse bias [18]. At low electric fields, thermionic emission dominates. But, as electric field increases  $J_{Sch}$  pales in comparison with the tunneling current density through the barrier, which can be approximated by the Fowler-Nordheim equation [33, 34] as

$$J_T = -CE^2 \exp(-\beta/E) - - - (33)$$

Negative sign in (33) is necessary because current is opposite to the direction of electron tunneling. The constants are

$$C = \frac{q^2 m_0}{16\pi^2 \hbar m^* \phi_B} Amperes/Volts^2 - - - (34)$$

$$\beta = \frac{4}{3} \frac{\sqrt{2m^*}}{q\hbar} (q\phi_B)^{\frac{3}{2}} Volts/meter - - - (35)$$

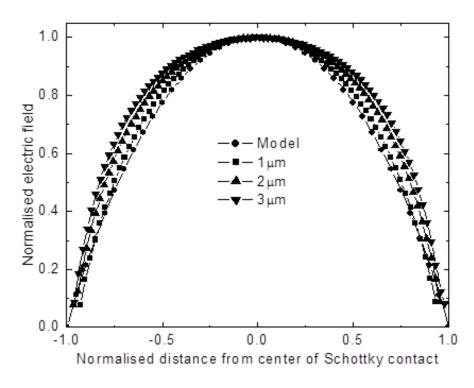

Tunneling in (33) is derived considering electron emission into a dielectric which gives a triangular potential barrier. Due to stored charge in the semiconductor, the potential barrier faced by electrons tunneling through a Schottky barrier is not exactly triangular but might be approximated as that in the interest of a closed-form relationship, especially under high reverse bias. A more accurate relationship can be obtained using WKB approximation [33] of the potential barrier obtained by (8). The ratio  $m^*/m_0$  in (34) and (35) depends on many factors and has been studied at the SiC interface in [35-37]. The combination of  $J_T$  and  $J_{Sch}$  has been fitted, using m<sup>\*</sup> as a parameter, with experimental Schottky diode reverse leakage currents in [27]. [27] and [28] also use the same approach for the JBS diode, accounting only for the reduced Schottky area in the JBS diode and the reduction in electric field at the center of the Schottky region. In effect, that makes an unjustified assumption that the normal electric field all across the Schottky contact in a JBS diode is the same as that at its center. Fig. 12 shows the variation of the normal component of the electric field at the Schottky contact with y, as predicted by our model and simulation. The abscissa is scaled to vary from -1 to 1 across the Schottky length and the ordinate from 0 to 1 as the normal electric field varies from 0 to its maximum value at the center. Electric field from the model can be re-stated from (9) as

$$E_x(0, y) = k_2 + \frac{k_1 \pi}{b} Cosh\left(\frac{\pi y}{b}\right)$$

$$\approx E_x(0, 0) * \left(2 - Cosh\left(\frac{y}{l} Cosh^{-1}(2)\right)\right) - - - (36)$$

The approximation in (36) models  $E_x(0, y)$  from its maximum at (0, 0) to zero at the P-N interface as a hyperbolic cosine. From fig. 12, the analytical model's prediction is most accurate at smaller 2k, which is due to the same reasons as detailed in the previous section. At all values of 2k, it models the variation of  $E_x(0, y)$  with little error compared to an assumption of independence of  $E_x(0, y)$  with y.

Figure 12 Variation of normal electric field across the Schottky contact

Two distributions of the Schottky and P-N regions that have been favoured at the anode of a JBS diode are interdigitated stripes of P-N and Schottky fingers and a honeycomb structure [20]. Assuming for now that we have interdigitated stripes (other structures will be comparatively evaluated in the next chapter), the total current through one Schottky finger is

$$I_{S} = \int (J_{Sch} + J_{T}) dA = \int_{-k}^{k} h(J_{Sch} + J_{T}) dy - - (37)$$

Then, the reverse leakage current density of the JBS diode is

$$J_R = \frac{I_S}{hP} = \frac{2(k'J_{Sch} + k''J_T)_{E(0,0)}}{P} - - - (38)$$

In (38), 2k' and 2k" are the effective Schottky widths that if E(0, y) = E(0, 0)would give the same  $J_{Sch}$  and  $J_T$  respectively. From (32), (33), (36) and (37), the integrals to find k' and k" are difficult to solve exactly. First order linear approximation of the exponential in (36) and (37) are used to simplify the calculation. This is valid because  $J_{Sch}$  is a significant part of  $J_R$  at lower electric fields when

$\sqrt{qE/4\pi\epsilon} \ll 1$  and  $J_T$  is significant only at higher electric fields when  $\beta/E \ll 1$ . The

variation of E(0, y) in fig. 12 can be modeled, for this approximation, as a parabola without much error. Then, we obtain

$$\frac{k'}{k} \approx \frac{1 + \frac{\pi}{4} \sqrt{\frac{q^3 E}{4\pi\varepsilon (kT)^2}}}{1 + \sqrt{\frac{q^3 E}{4\pi\varepsilon (kT)^2}}} - - - (39)$$

$$\frac{k''}{k} \approx \frac{\frac{8E}{15} - \frac{2\beta}{3}}{E - \beta} - - - (40)$$

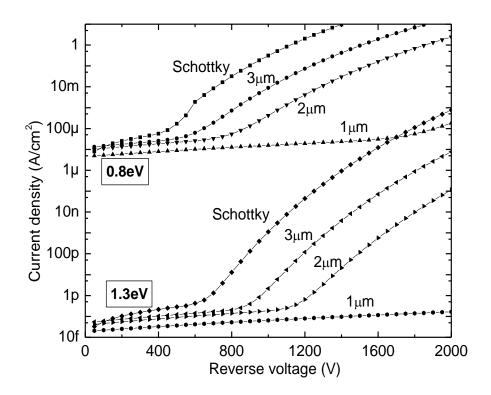

k'/k in (39) is approximately 1 for low electric fields when the thermionic emission component is significant. This agrees with our understanding that thermionic emission current across the Schottky barrier is not very sensitive to electric field at the barrier. At high electric fields starting well below the rated reverse voltage, k"/k for the tunneling component in (40) approaches 8/15. Using these approximations, fig. 13 shows the model's predictions of reverse leakage currents for Schottky diodes and JBS diodes with various Schottky widths and barriers. Suppression of reverse current relative to Schottky diode is seen at barriers of 0.8eV and 1.3eV. The voltage at which tunneling current becomes significant relative to thermionic emission increases when the Schottky barrier increases. The model's predictions for 1.3eV Schottky barrier and  $2k= 1\mu m$  is not fully accurate as the current is so low that P-N junction leakage current cannot be neglected in comparison to it. But if a JBS diode is so designed, well known P-N junction leakage current formulae can be used to supplement the leakage current across the Schottky barrier.

Figure 13 Variation of reverse leakage of JBS and Schottky diodes

## **2.1.4 Experimental Results**

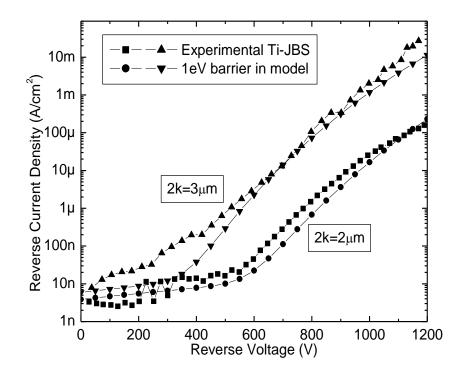

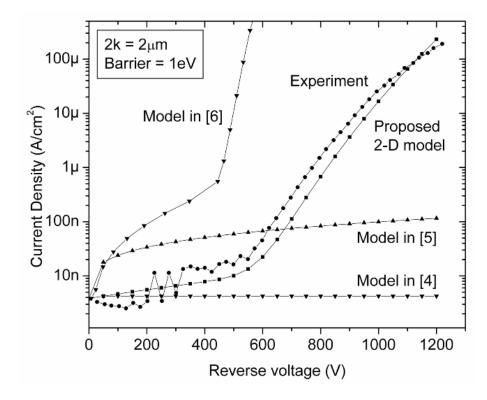

SiC JBS diodes with a drift layer thickness of  $12\mu m$ , carrier concentration of 7 X  $10^{15}$  cm<sup>-3</sup>, and 2k of  $2\mu m$  and  $3\mu m$  were fabricated. Reverse I-V curves of these devices were then compared with those predicted by the model, as shown in fig. 14. Schottky barrier at the Ti-SiC junction is assumed to be 1eV. As deposited, Ti has a barrier around 0.8eV with SiC but the metal was annealed at 500C for 10 minutes, after which the barrier was expected to have risen to around 1eV [19]. Excellent fit, as shown in fig. 14, is obtained at high voltages with m\*=0.24m<sub>0</sub> for 2k of both 2 $\mu m$  and 3 $\mu m$ . While the value of m\* in the experimental case considered has previously been reported as 0.33m<sub>0</sub> [36], agreement of our model with experiment at the same m\* for different Schottky openings supports its validity in our case. Divergence at low currents might be attributed to limitations in the accuracy and noise suppression

capabilities of the measurement apparatus. On comparison with the fully analytical Si-JBS diode model in [18], as shown in fig. 15, the proposed model presents great improvements in predicting the I-V curves of high voltage JBS diodes. The 1-D models in [27] and [28] are also included for comparison. Thermionic emission in [27] and [28] are high because E(0,0) predicted by them are high. Using m\* reported in them, tunneling current given by [27] is too low whereas that predicted by [28] is too high. Those 1-D models were optimized for a wide variety of 2k,  $\Phi$  and N<sub>D</sub> whereas the proposed 2-D model applies more widely.

Considering the JBS diode as a modified Schottky diode, excellent agreement of the electric field at the barrier between model and simulation suffices as a validation of the JBS diode model. But in practice, predictive power of the model hinges on the accuracy of Schottky diode theory. However, the leakage current of the Schottky junction is extremely sensitive to poorly defined effective mass values. Further investigation into tunneling models for current through the metalsemiconductor junction and accurate measurements of the effective mass of electrons along different crystal directions are needed to improve the reliability of Schottky diode theory.

Figure 14 Model and experimental SiC JBS diode reverse I-V curves at 300K

Figure 15 Comparison in reverse bias of the proposed model with other

published models

### 2.1.5 Forward Bias

Besides reverse leakage current, the other circuit design parameter for JBS rectifiers is specific on-resistance. An adequate analytical model for specific on-resistance which has already been provided in [27] and supported by experimental data is reproduced below.

$$R_{sp.on} = R_{channel} + R_{spread} + R_{Drift} + R_{substrate} + R_{contact} - - - (41)$$

$$R_{channel} = \frac{RP}{2q\mu_n N_D(k - W)} - - - (42)$$

$$R_{spread} = \frac{\rho_D P}{2} ln \left(\frac{P}{2(k - W)}\right) - - - (43)$$

$$R_{Drift} = \rho_D \left(W_D - R - \frac{1}{2}(P - 2(k - W))\right) - - - (44)$$

$R_{sp.on}$  is the specific on-resistance and various subscripts indicate the specific resistance components from the respective regions of the diode.  $\mu_n$  denotes electron mobility,  $J_F$  forward current density,  $V_F$  forward voltage and W the part of the Schottky region depleted by the P-N junction even in forward bias. In this breakdown of  $R_{sp.on}$ , the channel and spreading components depend on the proportion of the area of Schottky regions (k/P) in the diode. When the proportion of Schottky area decreases, the rate at which reverse current density (from (32-37) and fig. 13) is suppressed is faster than the rate at which specific on-resistance increases. So, with good edge termination and material quality, when reverse leakage is due only to thermionic emission and tunneling, a low value of 2k can be chosen to take advantage of JBS action. Active area of the JBS diode can then be increased to achieve the required low on-resistance.

To retain Schottky-diode like switching characteristics, JBS diodes under forward bias should be operated in unipolar mode. Then, the forward current-voltage characteristics can be modeled as thermionic emission over a barrier that is in series with the specific on-resistance.

$$V_F = \phi_B + \frac{kT}{q} \ln\left(\frac{P}{2(k-W)} \frac{J_F}{A^*T^2}\right) + J_F R_{sp.on} - - - (45)$$

#### 2.1.6 Compact I-V model for JBS diode

Physics-based closed form equations connecting reverse current and voltage of a punch-through JBS diode as a function of its design parameters have been developed [38]. For the same Schottky width, lateral spread of implantation is shown to reduce the electric field shielding effect of the JBS diode in reverse bias. Closed form equation derived for maximum electric field at the Schottky contact of the JBS diode helps compare JBS diodes of various Schottky widths. Predictions of reverse IV characteristics made using this model are validated against experimental JBS diode IV curves. In conjunction with the forward bias model in [27], a complete analytical theory for JBS diodes is provided which can easily be used in their design.

An approach similar to that in this work can be employed to form a theory of the Trench MOS barrier Schottky rectifier [39], among other shielded power diodes. A fuller understanding of the metal-semiconductor contact and formulation of accurate Fowler-Nordheim like closed form equation for tunneling at the metalsemiconductor junction will also improve the predictions of the model. Finally, the proposed JBS diode theory will be most successful if the insight gleaned from it on the effects of various design parameters helps introduce refinements that lead to performance improvements.

#### 2.2 Analytical Modeling of SiC VJFET

In an n-channel VJFET, the n+ drain is on the back side and the source and gate are on the front side of the wafer. Under sufficient negative (or zero if the channel is thin enough) gate bias, there is a potential barrier built up in the channel that prevents current from the source. But as drain voltage increases, the potential inside the channel rises from the drain side and if the channel is short, overcomes the potential barrier before the gate-drain avalanche limit, a phenomenon called drain-induced barrier lowering (DIBL). So, the performance of VJFETs with short channels is controlled not only by gate voltage but also by drain voltage. Hence, they are also called Static Induction Transistors (SIT). While long-channel JFETs can be modeled well using Shockley's classical 1-D analysis [40], the most popular model for Si SITs was provided by Bulucea et al. in 1987 [41] and Spirito et al. in 1990 [29].

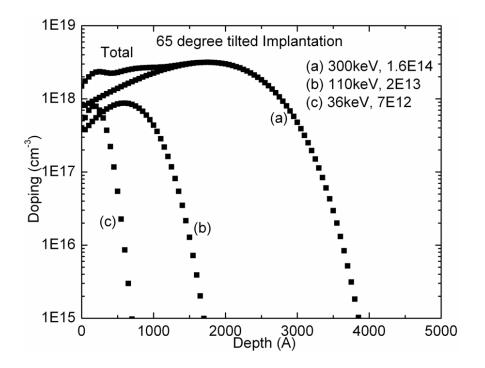

SIT models solve Maxwell's electrostatic equation in two dimensions in the JFET channel by assuming some boundary conditions. They provide I-V relationships in the blocking and conduction modes but assume an abrupt gate-channel junction. This assumption might be valid for Silicon devices where fabrication processes are so advanced that a near-abrupt junction can be realized. However, for SiC VJFETs, the analytical model has to be extended to realistic gate-channel doping profiles as obtained from advanced tilted gate implantation used for their fabrication. Fig. 16 shows ProfileCode [42] simulations showing the results of individual and combined tilted implantations at various energies and doses into SiC.

Figure 16 Simulation of doping profiles with implantation into 4H-SiC

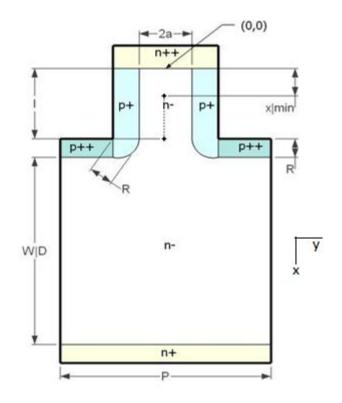

Figure 17 Cross-section of an n-channel VJFET with design parameters

The tail of implanted ions is significant and the gate-channel junction far from abrupt. This can be better modeled as a linearly graded junction than as an abrupt junction. For a linearly graded gate-channel junction with channel half-width "a" and net acceptor concentration linearly increasing from 0 to  $N_A$  between "a" and "b" (the cross section is shown in fig. 17), the acceptor and donor concentrations are given by

$$N_{A}(y) = \begin{cases} N_{A}; y > b\\ N_{A}\left(\frac{y-a}{b-a}\right); a < y < b \end{cases} - - - (46)$$

$$N_{D}(y) = \begin{cases} N_{ch}; y < a - \frac{N_{ch}}{N_{A}}(b-a)\\ N_{A}\left(\frac{a-y}{b-a}\right) \text{ otherwise} \end{cases} - - - (47)$$

Figure 18 Potential perpendicular to the axis of a VJFET at its saddle point