## EXPLOITING PHASE-CHANGE TECHNOLOGY IN SERVER MEMORY SYSTEMS

### BY LUIZ EDUARDO DA SILVA RAMOS

A dissertation submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Doctor of Philosophy Graduate Program in Computer Science Written under the direction of Ricardo Bianchini and approved by

> New Brunswick, New Jersey January, 2012

© 2012 Luiz Eduardo da Silva Ramos ALL RIGHTS RESERVED

#### ABSTRACT OF THE DISSERTATION

## Exploiting Phase-Change Technology in Server Memory Systems

## by Luiz Eduardo da Silva Ramos Dissertation Director: Ricardo Bianchini

Main memory capacity is becoming a critical issue for modern server systems. Unfortunately, current trends suggest that meeting these capacity requirements using DRAM will not be ideal. DRAM consumes significant amounts of energy (idle, refresh, and precharge energies) and will soon reach its density limit.

Many researchers in industry and academia point to Phase-Change Memory (PCM) technology as a promising replacement for DRAM. PCM is byte-addressable as DRAM, but presents higher density and lower idle power consumption than DRAM. However, PCM is also slower than DRAM and has limited endurance. For these reasons, hybrid memory systems that combine a small amount of DRAM and a large amount of PCM have become attractive.

In this dissertation, we propose two hybrid memory systems for servers. The first system (called Rank-aware Page Placement or RaPP) is a hardware-driven page placement policy. The policy relies on the memory controller (MC) to monitor access patterns, migrate pages between DRAM and PCM, and translate the memory addresses coming from the cores. The second system (called Rank-aware Cooperative Cache or RaCC) is a software-driven policy for object placement in server clusters that implement cooperative memory caches. RaCC monitors object popularity and leverages that information in placing the objects. Our extensive results show that our hybrid memory systems provide robust and consistent memory performance without sacrificing energy.

Based on our experience and results, we conclude that PCM is a promising main memory technology for future servers, especially when combined with a small amount of DRAM. However, such hybrid designs will require careful data placement and migration for best performance and robustness.

### Acknowledgements

I would like to thank my mentor and friend Ricardo Bianchini for his many lessons, for his character, competence, patience, and generosity. I extend those acknowledgments to his family Marcia and Daniel.

I heartily thank all my past and present PhD committee members Abhishek Bhattacharjee, Ulrich Kremer, Bhuvan Urgaonkar, Badri Nath, and Andrew Nealen. In special, I also thank my professors Daniel A. Jiménez, Richard Martin, Thu Nguyen, Dinesh Pai, Endre Szemerédi, Liviu Iftode, and all our teaching staff.

I thank my lab mates from Dark and Panic Lab, specially Rekha Bachwani, Ana Paula Centeno, Guilherme Cox, Qingyuan Deng, Íñigo Goiri, Md. Haque, Taliver Heath, Kien Le, Cheng Li, Kiran Nagaraja, Fábio Oliveira, Chris Peery, Tuan Phan, Longhao Shu, Andrew Tjang, and Wei Zheng. They enlightened every "Dark moment".

I would like to thank our collaborators David Meisner and Thomas F. Wenisch (University of Michigan), and Eugene Gorbatov (Intel Corporation); our reviewers and people who somehow contributed to our work. Among those, we thank Luiz Barroso (Google), Frank Bellosa (University of Karlsruhe), Yung-Hsiang Lu (Purdue University), Stijn Eyerman (Ghent University), Yoshio Turner (HP Labs), and Hongzhong Zheng (University of Illinois at Chicago).

I sincerely acknowledge the Computer Science administrative and technical staff, as well as the CIFSS staff. Special thanks to those who I bothered the most throughout the years: Friedrick Crispin, Carol DiFrancesco, Maryann Holtsclaw, Hans Makmur, Charles McGrew, Mohini Mukherjee, Douglas Motto, Urmi Otiv, Robert Toth, Regina Ribaudo, Aneta Unrat, Joanne Walsh, and Donald Watrous. I thank all my Computer Science colleagues and friends, in particular John McCabe, John-Austen Francisco, Jerry Hom, Rodrigo Toso, Daniela Viana, Wei Chen, Brian Russell, Brian Thompson, Desirée Ottoni, Christopher Woithe, Pravin Shankar, Lu Han, Reswana Nawrin, Mangesh Gupte, Gayatree Ganu, Konstantinos Kleisouris, Minji Wu, Pavel Kuksa, Monica Vroman, Robert Moore, Arzoo Zehra, Nikita Lytkin, Bruno Dufour, Carlos Diuk, Miguel Mosteiro, Nikolaos Leonardos, Cristopher Lauderdale, Shakeel Butt, Mohan Dhawan, Antonio Giovannelli, Enrique M. De Cote, Denitsa Tilkidjieva (in Memoriam), and Sérgio de Biasi (in Memoriam).

I would like to thank the United States for being my home during the PhD, and all the people and friends I was fortunate to meet here. I am very grateful to Diogo, Letícia, Gabriel, and Tomás Andrade and family, who literally adopted me into their household in the last months of my PhD. I also thank the very supportive friends: Tamanna Bhanot, Tibérius and Mara Bonates, Luís Castro, and family, Débora Espósito, Naomi Fleming, Michael Freitas, Lisa Giacumo, Aritanan Gruber, Slavko Komarnytsky, André and Eliane Madeira and family, Kelsie McClendon, Roberto Moratore Jr., Roberto, Vane, and Luisa Nicosia, Miguel Mosteiro and family, Carlos, Janaína and Lucas Oliveira, Guilherme Ottoni, Pooja Parek, Roy Pitta and family, Aline Ramires, Fernando Guerrero-Reyes, and so many others.

I am forever grateful to my parents Fernando and Sônia, my brother Paulo, and my entire family for their love and kindness. I love you all. I thank my dear wife Caroline for her priceless companionship, love and encouragement in critical times (I thank Sofia, Sky, and Jackson for the same reasons). I am also grateful to Caroline's family Anibal Savio, Maria Amalia Valiente, and Daniel Savio.

Finally, I would like to thank our sponsors: NSF (grant #CCF-0916539), Intel, CAPES (Brazil) and Fulbright. In particular, I am very grateful for support and patience of Silvio dos Santos Salles, Maria Luiza Lombas, and Jorge Pereira (CAPES), Michelle Lagos, Rosita Veluyia and Cinthya Alvarez (Fulbright), Glayna Braga, and Giselle Melo (Fulbright Brazil).

## Dedication

To God, my parents Fernando and Sônia, my brother Paulo, and my wife Caroline.

# Table of Contents

| Ał | ostra           | $\mathbf{ct}$                          |

|----|-----------------|----------------------------------------|

| Ac | cknov           | wledgements                            |

| De | edica           | tion                                   |

| Li | st of           | Tables                                 |

| Li | st of           | Figures                                |

| 1. | $\mathbf{Intr}$ | oduction                               |

|    | 1.1.            | Problem Statement                      |

|    | 1.2.            | In This Dissertation                   |

|    |                 | 1.2.1. Rank-aware Page Placement       |

|    |                 | 1.2.2. Rank-aware Cooperative Cache    |

|    | 1.3.            | Contributions                          |

|    | 1.4.            | Dissertation Structure                 |

| 2. | Bac             | <b>kground</b>                         |

|    | 2.1.            | Server Main Memory System              |

|    |                 | 2.1.1. Synchronous Dynamic RAM (SDRAM) |

|    | 2.2.            | Candidate Replacements for DRAM        |

|    |                 | 2.2.1. Phase-Change Memory             |

| 3. | Ran             | k-aware Page Placement                 |

|    | 3.1.            | Overview                               |

|    | 3.2.            | Hybrid Main Memory Design              |

|    |                 | 3.2.1. Rank-based Page Placement       |

|    |      | 3.2.2. | Comparable Hybrid Memory Systems                                                                                                            | 22 |

|----|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 3.3. | Evalua | $tion \ldots \ldots$ | 24 |

|    |      | 3.3.1. | Methodology                                                                                                                                 | 24 |

|    |      | 3.3.2. | Results                                                                                                                                     | 28 |

|    |      |        | 3.3.2.1. Performance and energy                                                                                                             | 28 |

|    |      |        | 3.3.2.2. Endurance                                                                                                                          | 33 |

|    |      | 3.3.3. | Sensitivity analysis                                                                                                                        | 34 |

|    | 3.4. | Summ   | ary                                                                                                                                         | 38 |

| 4. | Ran  | ık-awa | re Cooperative Cache                                                                                                                        | 40 |

|    | 4.1. | Overvi | ew                                                                                                                                          | 40 |

|    | 4.2. | Coope  | rative caching in Internet services                                                                                                         | 41 |

|    |      | 4.2.1. | Memcached                                                                                                                                   | 41 |

|    |      | 4.2.2. | PRESS                                                                                                                                       | 42 |

|    | 4.3. | The R  | aCC Policy                                                                                                                                  | 42 |

|    |      | 4.3.1. | Basic mechanisms                                                                                                                            | 44 |

|    |      | 4.3.2. | RaCC for PRESS                                                                                                                              | 47 |

|    |      | 4.3.3. | RaCC for Memcached                                                                                                                          | 49 |

|    | 4.4. | Evalua | tion                                                                                                                                        | 50 |

|    |      | 4.4.1. | Methodology                                                                                                                                 | 50 |

|    |      | 4.4.2. | Performance                                                                                                                                 | 56 |

|    |      | 4.4.3. | Energy                                                                                                                                      | 61 |

|    |      | 4.4.4. | Endurance                                                                                                                                   | 63 |

|    | 4.5. | Summ   | ary                                                                                                                                         | 65 |

| 5. | Rela | ated W | /ork                                                                                                                                        | 66 |

|    | 5.1. | Using  | technologies other than DRAM for main memory $\ldots \ldots \ldots$                                                                         | 66 |

|    | 5.2. | Tackli | ng PCM's Endurance Problem                                                                                                                  | 67 |

|    | 5.3. | Page M | Migration in Main Memory                                                                                                                    | 68 |

|    | 5.4. | Coope  | rative Caching                                                                                                                              | 69 |

| 6. | Conclusion           | 71 |

|----|----------------------|----|

|    | 6.1. Future Research | 72 |

| Re | eferences            | 74 |

| Vi | ta                   | 82 |

# List of Tables

| 2.1. | Comparing DRAM [36,37,55], FeRAM [20,24,43], STT-RAM [30,58,85],        |    |

|------|-------------------------------------------------------------------------|----|

|      | PCM [47,67], and Flash [14,56,80]                                       | 8  |

| 3.1. | Workload described by tag, memory footprint in MB, LLC misses per       |    |

|      | 1000 instructions (MPKI), and percentage of LLC write-backs as a        |    |

|      | fraction of all memory accesses (WB%). Applications marked with $^\ast$ |    |

|      | belong to Spec 2006                                                     | 25 |

| 3.2. | System settings                                                         | 26 |

| 4.1. | Workload details                                                        | 52 |

| 4.2. | Cluster node features                                                   | 54 |

| 4.3. | Influence of average RBHR on memory accesses $[47, 68]$                 | 56 |

# List of Figures

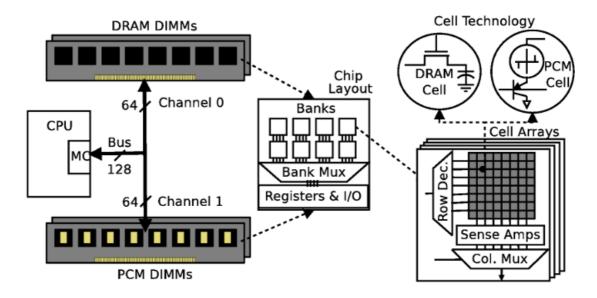

| 2.1. | Memory system using DRAM and PCM DIMMs. DRAM and PCM                                                |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | arrays are slightly different (cells and sense amplifiers)                                          | 7  |

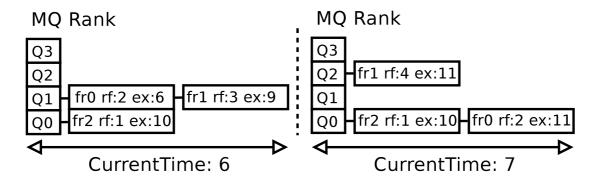

| 3.1. | MQ example with M=4 and $LifeTime=4$ . At $CurrentTime 6$ , the rank                                |    |

|      | contains three frames, represented by a tag (fr0-2), a reference counter                            |    |

|      | (rf) and an $ExpirationTime$ (ex). When fr1 receives a reference at                                 |    |

|      | CurrentTime 7, it is promoted into queue 2, whereas fr0 gets demoted                                |    |

|      | to queue 0                                                                                          | 15 |

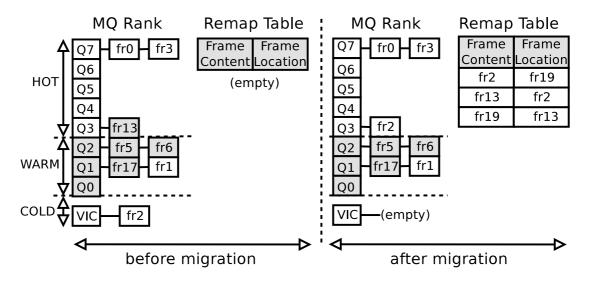

| 3.2. | RaPP example. Before and after we migrate a PCM page (stored in                                     |    |

|      | frame 13) that crossed over to the DRAM side of the ranking to a frame                              |    |

|      | from the victim list (frame 2). Dark shading represents PCM frames and                              |    |

|      | no shading represents DRAM frames                                                                   | 18 |

| 3.3. | Memory controller with RaPP's new modules highlighted                                               | 20 |

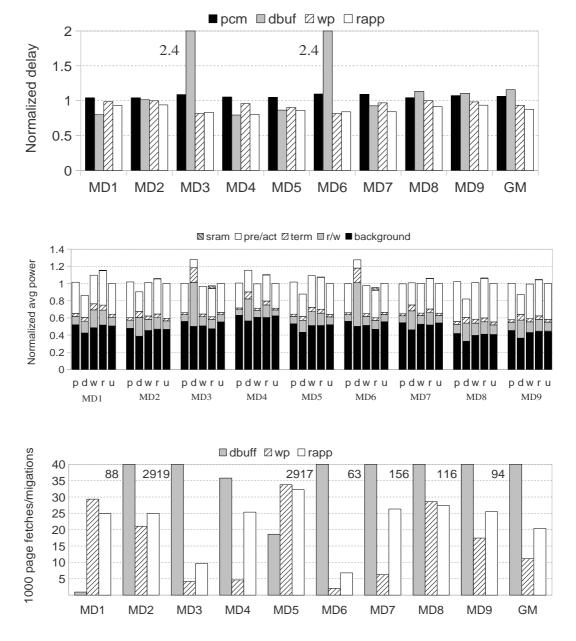

| 3.4. | Comparing performance, average power, and page transfers for the MD                                 |    |

|      | workloads. In the middle figure, $p = PCM$ -only, $d = DBUFF$ , $w = WP$ ,                          |    |

|      | r = RaPP and $u = Unmanaged$ .                                                                      | 30 |

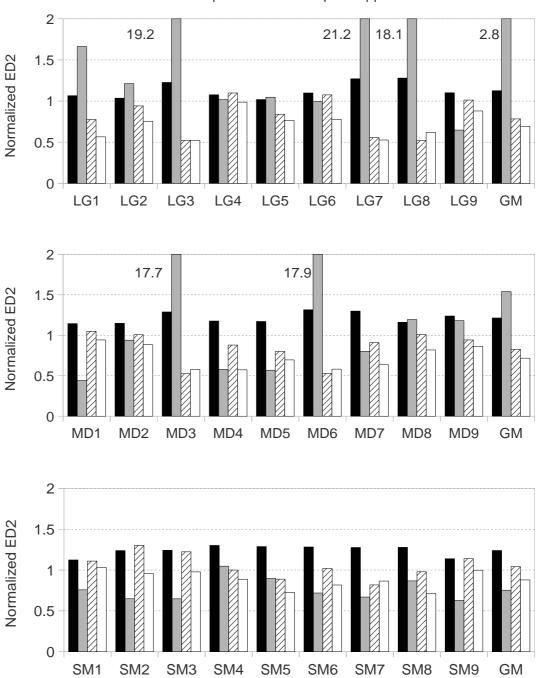

| 3.5. | Comparing energy-delay <sup>2</sup> for all workloads. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 32 |

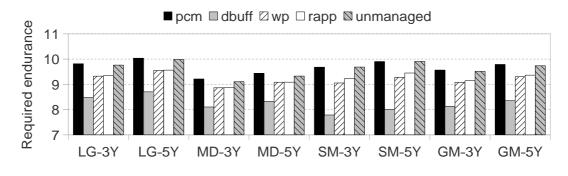

| 3.6. | Required Endurance projected over 3 and 5 years                                                     | 34 |

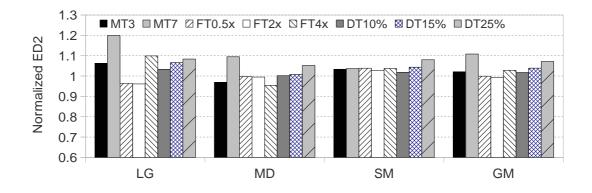

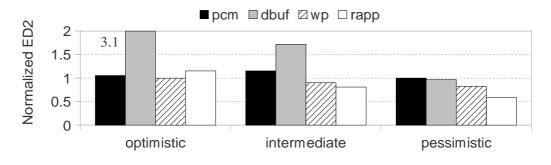

| 3.7. | RaPP's sensitivity to migration threshold (MT), filter threshold (FT),                              |    |

|      | disable threshold (DT).                                                                             | 35 |

| 3.8. | Sensitivity to PCM's characteristics.                                                               | 36 |

| 3.9. | Comparing RaPP to different flavors of WP                                                           | 37 |

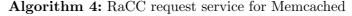

| 4.1. | CDF of object popularity in our workloads                                                           | 52 |

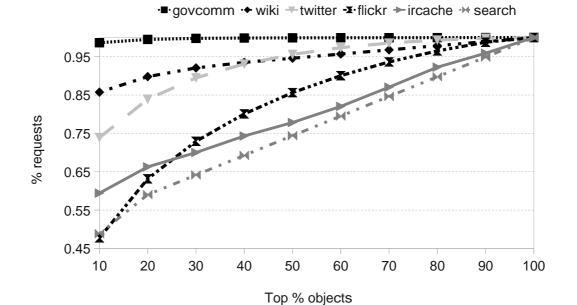

| 4.2. | Response times for a real server, simulated servers (assuming $1\%$ , $6\%$ ,                       |    |

|      | and $12\%$ RBHRs), and the average across the simulated response times.                             | 55 |

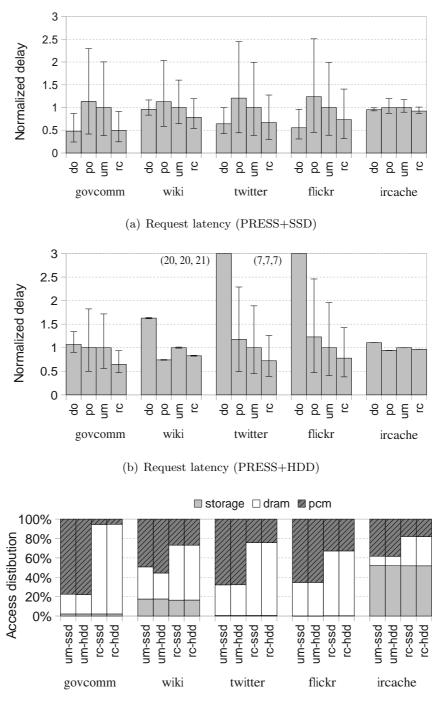

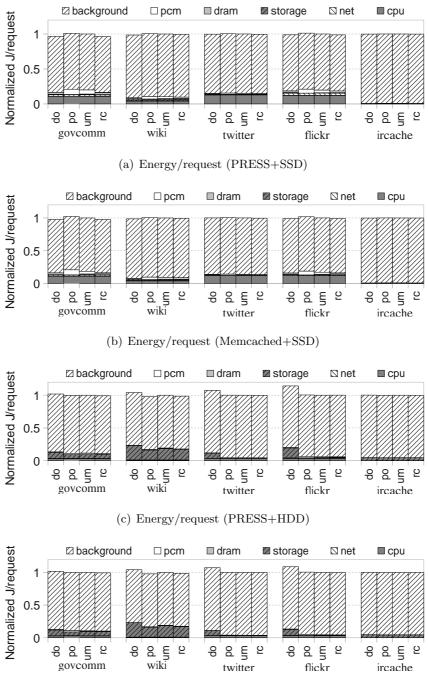

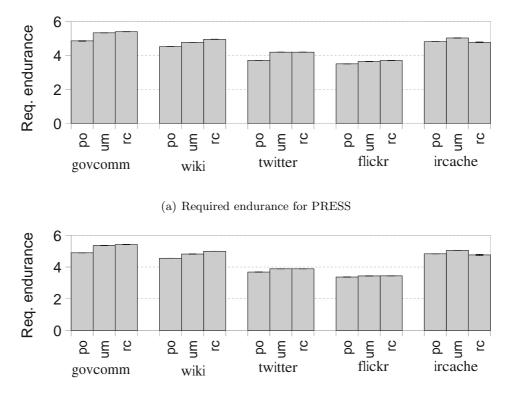

- 4.3. Average latency per request served by PRESS, using either SSD or HDD storage devices, and percentage of requests served from each memory and storage device. Each bar represents the average latency per served request across the multiple RBHR scenarios (1%, 6% and 12%) normalized to Unmanaged. The error bars show the worst and the best average latency per request across all RBHRs. Do, po, um, and rc represent respectively DRAM-only, PCM-only, Unmanaged, and RaCC.

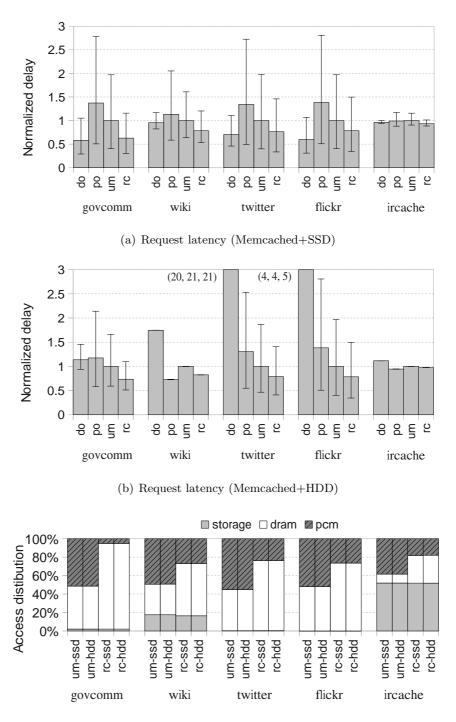

- 4.4. Average latency per request served by Memcached, using either SSD or HDD storage devices, and percentage of requests served from each memory and storage device. Each bar represents the average latency per served request across the multiple RBHR scenarios (1%, 6% and 12%) normalized to Unmanaged. The error bars show the worst and the best average latency per request across all RBHRs. Do, po, um, and rc represent respectively DRAM-only, PCM-only, Unmanaged, and RaCC. 59

58

## Chapter 1

# Introduction

Memory capacity is becoming a scarce resource in modern server systems, as the number of CPU cores increases, application and thread concurrency escalate, virtual machines require simultaneous co-location of large working sets in main memory, and data objects grow in size and quantity [28, 82]. Future projections suggest that at current rates, server systems will meet a "memory capacity wall", where memory capacity will limit the performance of servers [50, 63].

Unfortunately, current trends suggest that meeting the future capacity requirements using DRAM will not be ideal. DRAM exhibits low access times, but consumes significant amounts of energy (idle, refresh, and precharge energies). As a result, the amount of energy consumed by the memory is approaching (and sometimes surpassing) that consumed by the processors in many servers [4, 48]. Moreover, DRAM's storage elements are reaching their scalability limit. According to the latest ITRS report, DRAM will not scale below the 21nm technology node [37]. The alternative of adding memory modules is not cost-effective [10,72], increases power consumption significantly [27, 55], and may be impossible due to design constraints (e.g., DDR3 supports at most two memory modules per channel) [51]. Thus, since DRAM is the dominant main memory technology, limiting DRAM chip densities ultimately jeopardizes the scalability of server memories.

For these reasons, architects have started to consider emerging memory technologies as potential replacements for DRAM [20, 24, 31, 47, 49, 85]. One of the most mature candidate technologies is Phase-Change Memory (PCM) [47, 67, 89, 90]. PCM is byteaddressable, consumes little idle energy, does not require refreshing or precharging (its contents are persistent), and exhibits access times in the nanosecond range. Furthermore, PCM cells have feature size comparable to DRAM cells, but can store more information in the same physical area. However, PCM's read/write times, read/write energies, and write endurance are worse than those of DRAM.

#### 1.1 Problem Statement

To overcome the limitations of DRAM and PCM, researchers have proposed hybrid memory systems that combine small amounts of DRAM and large amounts of PCM [59, 67, 89, 90]. Those systems can exploit the high performance of DRAM and the high capacity and scalability of PCM. However, for best performance and robustness, hybrid memory systems require careful management, as we demonstrate. In addition, existing approaches fail to leverage higher-level information available the workloads and services executed on servers. We demonstrate that high-level information can also benefit performance and robustness, while requiring lower complexity than existing hybrid memory systems.

#### 1.2 In This Dissertation

In this dissertation, we propose two novel hybrid memory systems that combine DRAM and PCM. Both our systems seek to improve memory performance and robustness, without increasing energy consumption significantly. Our first design manages individual servers that run memory-intensive workloads. Our second design leverages service-level information in server clusters to attain better performance and robustness for I/O-intensive workloads. In fact, it entails the first study of the implications of PCM and hybrid main memory systems for server clusters.

#### 1.2.1 Rank-aware Page Placement

Our first design comprises a sophisticated memory controller (MC) that implements a page placement policy called "Rank-based Page Placement" (RaPP). The policy efficiently ranks pages according to popularity (access frequency) and write intensity, migrating top-ranked pages into DRAM. For robustness, our MC may disable RaPP when it is unlikely to produce benefits.

We evaluate our memory system design and RaPP with regard to energy, performance, and endurance, using detailed simulations. For comparison with our system, we simulate two state-of-the-art hybrid memory designs [67,89].

#### 1.2.2 Rank-aware Cooperative Cache

Our second design targets server clusters that implement cooperative memory caches. These caches are extensively used in modern Internet services, and are a great target for hybrid memory systems, since they require low latency and high memory capacity at the same time.

Our design, called "Rank-aware Cooperative Cache" (RaCC), is a software-driven object placement policy for hybrid memory systems in server clusters. RaCC monitors object popularity and leverages that information in placing the objects across servers and memory technologies. Specifically, RaCC concentrates popular cached objects in the collective DRAM of the server cluster, while taking advantage of PCM's large capacity to increase the hit ratio of the cooperative cache. We apply RaCC to two state-of-the-art cooperative caches [12, 26].

We evaluate these RaCC-based systems with regard to energy, performance, and endurance, using simulation of real and synthetic traces of Internet services.

#### 1.3 Contributions

In summary, our contributions in this dissertation are:

- We propose RaPP, a robust page placement policy for hybrid main memory systems;

- We evaluate RaPP and compare it to two state-of-the-art approaches;

- We study the implications of PCM and hybrid main memory systems for server clusters for the first time;

- We propose RaCC, a policy for managing object location in cooperative caches made from hybrid main memories; and

- We evaluate Memcached and PRESS, with and without RaCC, for PCM-based main memories.

We conclude that PCM is a promising main memory technology for future servers, especially when combined with a small amount of DRAM. However, such hybrid designs will require careful data placement and migration for best performance and robustness.

### 1.4 Dissertation Structure

The remainder of this dissertation is organized as follows. Chapter 2 provides background on server memory systems and main memory technologies. Chapters 3 and 4 present the details and evaluation of our hybrid memory systems. Chapter 5 discusses the related work and Chapter 6, contains our conclusions and future work.

## Chapter 2

# Background

In this chapter, we describe how architects typically organize main memory in server systems. We also provide deeper background on DRAM, discuss candidate technologies to replace DRAM (including PCM), and describe our assumptions for PCM.

#### 2.1 Server Main Memory System

A server's memory system typically comprises a few key elements, namely a memory controller (MC), a few memory channels, and a number of dual-inline memory module (DIMMs). Each DIMM includes memory devices (chips) that contain a memory cell array and peripheral circuitry.

The MC is responsible for handling memory access requests from the CPU, resulting from last-level cache (LLC) misses or write-backs. The MC operates the memory chips to fetch and store data, as well as refresh their memory arrays (in the case of DRAM). Operating the memory chips entails forwarding physical addresses to the peripheral circuitry, and issuing commands to drive the chips while respecting certain timing constraints. Due to its central role, an MC can be designed with varying complexity to optimize the memory system for different purposes. For example, to improve access throughput, the MC may choose to buffer particular requests (e.g., LLC write-backs) and/or reorder requests according to the system's current state [5, 39, 71].

At a high level, a memory chip can be logically viewed as an array of bit cells with some interface circuitry. Memory chips are read and written in groups called ranks. A rank can transfer a number of bits equal to the memory channel's width (e.g., 64 bits) in one memory cycle, so it takes several memory cycles to transfer an entire LLC line. At a low level, the memory chips are subdivided into banks that can be accessed concurrently, and further into bitcell arrays. On a read to a bank, part of the target address (provided by the MC) is used to activate a row of bitcells, and amplify and latch their contents into a row buffer. Then, a column (subset of a row) can be selected, causing its data to be transferred from the row buffer to the MC. The MC then delivers the data to the CPU. An access to a column of another row causes the activation of the new row. On a LLC write-back, the data flows in the opposite direction, is stored in the row buffer, and eventually written to the memory array.

#### 2.1.1 Synchronous Dynamic RAM (SDRAM)

A DRAM cell is a transistor-capacitor pair (1T/1C) where each transistor allows reading and writing, and the capacitor stores a bit as an electrical charge (Figure 2.1). Since DRAM's capacitors discharge over time, they need to be refreshed at regular intervals to prevent data loss. In addition, reading a DRAM cell destroys its original content; the "precharge" operation restores the data from the row buffer into the array. Under a close-page management scheme, the MC precharges (closes) a row after every column access, unless there is another pending access for the same row. If there is a pending access, the row buffer remains open and the access can be serviced from there. Under open-page management, the row buffer remains open until another row needs to be loaded into it; only at that point is the precharge operation performed. Close-page management typically works better than open-page management for multi-core systems [77].

Double Data Rate 3 (DDR3) is the current standard for Synchronous DRAM interfaces. DDR3 channels are 64-bit wide (72-bit wide with ECC), so it takes four memory cycles (8 transfers) to access a 64-byte LLC line. In server systems, typically one, two, or four ranks of 8 (x8) or 16 (x4) chips (plus additional chips when using ECC) are laid out on each DIMM. When designed to operate at high frequencies, only one or two DDR3 DIMMs can lie on a single memory channel due to electrical limitations.

DRAM energy can be broken down into background, activation/precharge, read/write, and termination energies. Background energy is independent of activity and

Figure 2.1: Memory system using DRAM and PCM DIMMs. DRAM and PCM arrays are slightly different (cells and sense amplifiers).

is due to the peripheral circuitry (e.g., row decoder, column muxes, sense amplifiers, and bus drivers), transistor leakage, and refresh operations. The activation/precharge energy is due to these two operations on the memory arrays. The read/write energy is due to column accesses to row buffers. The termination energy is due to terminating data and strobe signals at each chip, as well as signals of other ranks on the same channel. The three latter classes are often referred to as "dynamic DRAM energy". Most of the energy consumed by DRAM is background and activation/precharge energy.

### 2.2 Candidate Replacements for DRAM

For over a decade, DRAM has been the dominant main memory technology. Its adoption was fueled by its high scalability, energy-efficiency, and low cost per bit compared to Static RAM, and high performance compared to Flash memory [36]. Unfortunately, the DRAM storage element will soon reach its scalability limit [37, 38]. Physical space constrains the memory design mainly because cell capacitance becomes too low (and leakage power too high), requiring impractical refresh rates [37]. The latest ITRS report (2009 with an update in 2010) mentions stack capacitor cells as a workaround that enables the non-scaling DRAM capacitors to be used in smaller DRAM cells. That solution entails non-planar structures with high aspect ratio and smaller size  $(4F^2 \text{ instead of } 6F^2)$ . However, that solution has its own problems and should enable DRAM to scale further down to somewhere between 21 and 18nm feature sizes [38], beyond which this technique cannot scale further. Without the scalability advantage and with increasing contribution of main memory to capital costs and power consumption in servers, architects have been searching for alternative memory technologies to replace DRAM. Table 2.1 compares DRAM to other memory technologies.

Table 2.1: Comparing DRAM [36, 37, 55], FeRAM [20, 24, 43], STT-RAM [30, 58, 85], PCM [47, 67], and Flash [14, 56, 80].

| Features              | DRAM      | FeRAM     | STT-RAM   | PCM               | NOR Flash        | NAND Flash      |

|-----------------------|-----------|-----------|-----------|-------------------|------------------|-----------------|

| Cells size $(F^2)$    | 6 - 8     | 15 - 32   | 36        | 4 - 12            | 10               | 4               |

| Erase block / latency | N.A.      | N.A.      | N.A.      | N.A.              | 64–256KB / 900ms | 8–64KB / 2ms    |

| R / W page size       | 64b       | 64b       | 64b       | 64b               | 64b              | 512b-4KB        |

| Read latency          | 10's ns   | 10's ns   | 10's ns   | 10's ns           | 100's ns         | $10$ 's $\mu$ s |

| Write latency         | 10's ns   | 10's ns   | 10's ns   | 100's ns          | 10's $\mu s$     | 100's $\mu s$   |

| Non-volatility        | no        | yes       | yes       | yes               | yes              | yes             |

| Endurance             | $10^{16}$ | $10^{14}$ | $10^{15}$ | $10^{8} - 10^{9}$ | $10^{5}$         | $10^{5}$        |

Despite the advanced maturity level of NOR and NAND Flash, they are unsuitable for main memory. NOR Flash is byte-addressable for reads and writes, but does not support in-place overwrite of a modified bit without first erasing the block (typically 64–256KB) that contains that bit. The erase procedure must occur for the entire block simultaneously and takes milliseconds to seconds to complete [14]. NAND Flash is slower than NOR for reads and writes, but erases faster. NAND also has higher density than NOR and is page-oriented (512b–4KB reads, writes, and erases), which makes it more suitable for storage and less suitable for main memory. In addition to these features, both NOR and NAND Flash have very poor endurance (10<sup>5</sup> erases, or less for feature sizes below 25nm).

Due to the limitations of DRAM and Flash, Storage Class Memories (SCM) have emerged as possible future replacements, and have been gaining increasing attention. Three of the most mature SCMs are: Ferroelectric RAM (FeRAM), Spin-Torque Transfer RAM (STT-RAM), and Phase-Change Memory (PCM). These technologies

9

are currently under development and first-generation devices have already been used in embedded systems [20,25,61,79]. However, they have not been developed commercially for main memory at this point.

In particular, FeRAM and STT-RAM are promising replacements for SRAM (e.g., in caches, CPUs and embedded systems) [30, 58, 78, 85]. However, they have shown somewhat limited scalability, high cost and integration issues [37, 38], which hinder their use in main memory. In contrast, PCM devices of higher density have already been produced [73] (512Mbit vs 4Mbit of FeRAM and STT-RAM), and the current roadmap depicts PCM scaling more aggressively than the other two [37]. In fact, one recent research work [1] has developed a prototype of PCM DDR2 DIMM 250MHz (using Micron's 128Mbit chips [57]) and a memory controller that implements the wearleveling algorithm in [69]. The DIMMs are, however, used in a storage device attached to the PCIe interface. For all these reasons, multiple works, including this dissertation, have focused on the PCM SCM. In the next section, we describe the PCM cell and interface in more detail.

#### 2.2.1 Phase-Change Memory

A PCM cell comprises an NMOS access transistor and a storage resistor (1T/1R) made of a chalcogenide alloy. With the application of heat, the alloy can be transitioned between physical states with particular resistances, used to represent binary values. When the alloy is heated to a very high temperature (>  $600^{\circ}C$ ) and quickly cooled down, it turns into an amorphous glass with high electrical resistance, representing 0. When the alloy is heated to a temperature between the crystallization ( $300^{\circ}C$ ) and melting ( $600^{\circ}C$ ) points and cools down slowly, it crystallizes to a state with lower resistance, representing 1. This programming process can be carried out by peripheral write drivers.

A cell's content can be read using current sense amplifiers to measure its electrical resistance, as opposed to DRAM's slower but smaller voltage sense amplifiers. PCM can thus interface with most CMOS peripheral circuitry used in DRAM [89]. Unlike in DRAM, PCM's reads are non-destructive and cells can retain data for several years. On the downside, PCM cells exhibit worse access performance than DRAM.

Regarding density, PCM has similar cell size  $(4F^2 \text{ to } 12F^2)$  compared to DRAM  $(6F^2 \text{ to } 8F^2)$ . However, PCM enables manufacturing of multi-level cells (MLC), which produce intermediate resistances (the alloy is partially crystalline and partially amorphous) and therefore can store multiple bits. Current MLC prototypes have twoor four-bit cells, capable of storing four and sixteen binary values, respectively [62]. Assuming the same cell size for both technologies, these MLCs hold twice and eight times more data than DRAM cells in the same area.

**Our assumptions for PCM.** In this dissertation, we assume that PCM is four times more storage-dense than DRAM, as in [67]. For easier adoption, we expect that the peripheral circuitry for PCM (e.g., row buffers, row and column decoders, DIMM interface) will be equivalent to that for DRAM, except for sense amplifiers. Thus, we assume this circuitry to have the same performance and power characteristics for both PCM and DRAM. Previous studies have made the same assumption [47,89]. Only the written cache lines in a row buffer are written back to the PCM cell array (DRAM needs the entire buffer to be written back to precharge its cells). Similar optimizations have been used before as well [47,90]. To expose the entire overhead of PCM accesses to the cores, we study a CPU with in-order cores and a single outstanding miss per core.

PCM does not require cell refreshing or precharging, thereby lowering background energy relative to DRAM and eliminating precharge energy. However, PCM increases activation and termination energies, since its activations (actual accesses to memory cells) are slower than with DRAM. Our assumptions for peripheral circuitry imply that row buffer read/write energy is the same for DRAM and PCM.

## Chapter 3

# **Rank-aware Page Placement**

### 3.1 Overview

In this chapter, we present a new DRAM+PCM memory system design that is robust across a wide range of workloads. The design comprises a sophisticated MC that implements a page placement policy called RaPP. The policy efficiently ranks pages according to popularity (access frequency) and write intensity, migrating top-ranked pages to DRAM. While monitoring popularity, RaPP penalizes pages that are unlikely to produce benefits if migrated. To improve PCM's endurance, each migration involves two PCM memory frames and one DRAM frame. The MC monitors access patterns and, when necessary, migrates pages. The migrations are not immediately visible by the OS, as the MC uses its own address translation table. Periodically (or when the table fills up), the OS updates its mapping of virtual pages to physical frames based on the translation table and clears it.

We evaluate our memory system design and RaPP using a detailed simulator that computes the energy, performance, and endurance of workloads running on an 8-core CPU. For comparison with our system, we simulate two state-of-the-art hybrid memory designs [67, 89], as well as a baseline hybrid system without page management (called "unmanaged") and a PCM-only system.

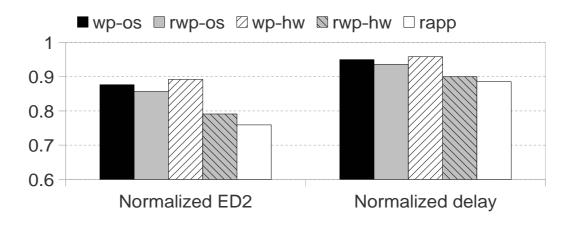

Our results for 27 workloads show that our system consumes roughly the same amount of power on average as its competitors and the baselines, but with significantly better performance. In terms of energy-delay<sup>2</sup>, for the workloads we study, our system is on average 36% better than the PCM-only baseline and 24% better than the unmanaged hybrid system. Compared to the state-of-the-art hybrid systems, our system exhibits at least 13% better energy-delay<sup>2</sup> on average, especially for workloads with large memory footprints. Our system also improves lifetime, as compared to the baselines, but not enough to enable system operation for 5 years assuming current PCM endurance. Nevertheless, PCM endurance is expected to increase by orders of magnitude in the next few years [17,36]. Until then, our system can be easily combined with previously proposed endurance-improvement techniques [16, 40, 47, 90].

#### 3.2 Hybrid Main Memory Design

As we mentioned in Section 1, given the speed of DRAM and the high density of PCM, there is a clear incentive for combining these two technologies into a single, hybrid memory system. However, PCM has undesirable characteristics (poor performance, dynamic energy, and endurance) that must be properly managed. Similarly, DRAM has a relatively high idle energy consumption compared to that of PCM.

A few previous works have realized the benefits of combining DRAM and PCM [67, 89] and the associated tradeoffs. Unfortunately, the previous approaches have serious limitations. Qureshi *et al.* [67] proposed to use DRAM as a buffer in front of PCM. Since the buffer is managed as an inclusive hardware cache, the DRAM space does not add to the overall memory capacity. More importantly, for workloads with poor locality, the cache actually lowers performance and increases energy consumption. Zhang *et al.* [89] combine the DRAM and PCM areas in a large flat memory and migrate pages between the areas. However, the migrations are performed by the OS and target the frequently written pages, leaving read-intensive pages in the slower PCM area.

Next, we describe our hardware-software page placement policy, called RaPP, which manages pages without the limitations of previous works. After that, we detail our implementation of the two prior hybrid systems. Throughout our descriptions, we differentiate between *virtual memory* pages (or simply pages) and *physical memory* frames (or simply frames).

#### 3.2.1 Rank-based Page Placement

Given the characteristics of DRAM and PCM, RaPP seeks to (1) place performancecritical pages and frequently written pages in DRAM, (2) place non-critical pages and rarely written pages in PCM, and (3) spread writes to PCM across many physical frames.

The justification for these goals is that previous works have shown that typically only a relatively small subset of pages is performance-critical during the execution of a workload [33]. This observation suggests that (a) this subset may fit entirely in the DRAM part of the hybrid memory, and (b) the majority of lightly accessed pages should consume little energy, if stored in the PCM part. Moreover, previous work has found that the subset of critical pages may change over time, along with the criticality of individual pages [33]. This second observation suggests that the system must dynamically identify the critical pages and adjust their placements accordingly.

Since the OS is not on the path of most memory accesses, RaPP must be collaboratively executed by the OS and the MC. An interesting challenge is that neither the MC nor the OS has complete information about the performance criticality of the pages in a workload. For example, the latency of the cache misses associated with a page may be hidden behind out-of-order execution or multithreading by the processor cores. Interestingly, previous work [6] has shown that the frequency of cache misses is a very good proxy for a thread's performance criticality, regardless of the details of the microarchitecture (in-order vs out-of-order execution). Thus, pages that experience more misses also tend to be more performance critical.

RaPP relies on the MC to monitor the misses in the LLC to each physical memory frame. In addition, the MC monitors the LLC write-backs directed to each frame. Using this information, RaPP dynamically ranks frames based on frequency and recency of accesses, as detailed below. Frames that rank high are called "popular", and frames that rank low are called "unpopular". Whenever the most popular PCM frame reaches a threshold number of accesses (called the "migration threshold"), the MC considers migrating its content into DRAM transparently to the OS. If the DRAM area is full, the MC selects the page stored in an unpopular DRAM frame to migrate to PCM.

**Ranking frames.** RaPP simultaneously considers frame access frequency and recency in its dynamic ranking of pages (i.e., the pages stored in the frames), using a modified version of the Multi-Queue (MQ) [91] algorithm for second-level buffer cache replacements. As originally designed, MQ defines M LRU queues of block descriptors, numbered from 0 to M-1. Each descriptor includes the block number, a reference counter, and a logical expiration time. The descriptors in queue M-1 represent the blocks that are most frequently used. On the first access to a block, its descriptor is placed in the tail of queue 0. In addition, the block's expiration time ExpirationTime is set to CurrentTime + LifeTime, where both times are measured in number of accesses and *LifeTime* specifies the number of consecutive accesses that must directed to other blocks before we expire the block. Every time the block is accessed, its reference counter is incremented, its expiration time is reset to CurrentTime + LifeTime, and its descriptor is moved to the tail of its current queue. The descriptor of a frequently used block is promoted to a higher queue (saturating at queue M-1, of course) after a certain number of accesses to the block. Specifically, if the descriptor is currently in queue *i*, it will be upgraded to queue i + 1 when its reference counter reaches  $2^{i+1}$ . Conversely, MQ demotes blocks that have not been accessed recently. On each access, the descriptors at the heads of all M queues (representing the LRU block of each queue) are checked for expiration (CurrentTime > ExpirationTime). If a block descriptor expires, it is placed at the tail of the immediately inferior queue, and has its expiration time again set to CurrentTime + LifeTime. Figure 3.1 shows an example of promotion and demotion in MQ.

We use the modified MQ to rank memory frames (it was originally designed to rank disk blocks). We do so for two main reasons: (1) as page migrations are expensive operations, it is important to select the pages to migrate as intelligently and accurately as possible. MQ has been proven superior to other algorithms in selecting the blocks to replace [91]; (2) modern memory controllers are becoming increasingly complex and sophisticated (as discussed below), as a result of the increasing importance of the

Figure 3.1: MQ example with M=4 and LifeTime=4. At CurrentTime 6, the rank contains three frames, represented by a tag (fr0-2), a reference counter (rf) and an ExpirationTime (ex). When fr1 receives a reference at CurrentTime 7, it is promoted into queue 2, whereas fr0 gets demoted to queue 0.

memory system (in terms of performance and energy) and relentless technology scaling. To avoid performance degradation, the updates to the MQ queues are performed by the MC off the critical path of memory accesses, using a separate queue of updates and a small on-chip SRAM cache. To find the MQ entry of a frame, the MC hashes the corresponding frame number.

We create 15 queues (numbered 0–14) plus a 16th victim list (described below). Pages stored in PCM frames that become popular (i.e., get to higher queues) are scheduled for migration to DRAM. However, we modified MQ in two important ways. First, instead of counting all accesses, we only count an access if it occurs more than a threshold time (measured in memory cycles) after the last access to the same frame. This latter threshold is called the "filter threshold". The MC stores the time of the last access in the descriptor for the frame. The reason for filtering rapid-fire accesses out is that there is no point in trying to migrate a page that is accessed in such a way; before we get to migrate the page, the needed data has already been loaded to the LLC (or evicted from it). In fact, it is possible that the page will not even be accessed again in memory. Using a 2-competitive approach, we set the filter threshold to be *MigrationCost/MigrationThreshold*, where *MigrationCost* is the uncontended number of memory cycles needed to migrate a page. (*MigrationCost* is roughly 1.6 $\mu$ s in our experiments.)

Second, we modified the demotion policy in the following ways: (a) we use time, not

number of accesses, as the metric for demotion to reduce space requirements (in our experiments, we set LifeTime to  $100\mu$ s, which works well for our workloads); (b) we only demote from one queue at a time (in round-robin fashion) to reduce runtime overhead; and (c) a DRAM frame that is demoted twice without any intervening accesses leaves the MQ queues and becomes a candidate to receive a popular PCM page. The reason for the latter modification is that frames that undergo multiple demotions tend to have already been cached in the LLC and will not be accessed in a while. We store the MQ queues and the victim list in the lowest DRAM addresses.

Migrating pages. As mentioned above, RaPP schedules the page stored in a PCM frame for migration to DRAM after its reference counter reaches the migration threshold. In particular, the page stored at any PCM frame that reaches queue 5 (i.e., the reference counter for the frame has reached  $2^5 = 32$ ) is scheduled for migration to DRAM. (Thus, the maximum number of frames that can be in queues 5–14 is the size of DRAM. For symmetry, the maximum size of queues 0–4 is also set to the size of DRAM.)

We find these values for M and the migration threshold to work well for our extensive set of workloads. The rationale is that in many workloads, a large number of pages would end up in queue M - 1 if M is small, compromising the accuracy of the hot page identification. On the other hand, if M is high, RaPP can correctly identify hot pages, but the MQ overhead increases. As for the migration threshold, we must select a value that enables early migrations but without migrating pages unnecessarily.

To select a destination DRAM frame for a page, the MC maintains an LRU list of victim DRAM frames. The victim frames are not in any of the LRU queues (the list is initialized with all DRAM frames). Whenever a frame on the victim list is accessed, it is removed from the list and added to queue 0. A frame demoted from queue 0 or demoted twice without intervening accesses is moved to the tail of the list. The destination DRAM frame is the first frame on the list. If the list is empty, no destination is selected and the migration is delayed until a frame is added to the list.

To effect a page migration to DRAM, the MC (1) migrates the page stored in the

selected DRAM frame to one of the unranked PCM frames, (2) migrates the content of this latter frame to the most popular PCM frame, and finally (3) migrates the content of the most popular PCM frame to the selected DRAM frame. Figure 3.2 shows an example, where shaded frames are PCM frames and non-shaded frames are DRAM frames. In the example, the MC migrates the content of frame 13 to frame 2, the content of frame 2 to frame 19, and the content of frame 19 to frame 13.

To allow the three migrations to proceed concurrently, the MC uses three intermediate frame-size buffers located in the MC itself. The contents of the frames are first copied to the buffers, and only later copied to the destination frames. In addition, to avoid excessively delaying LLC misses due to row conflicts while migrating, the PCM DIMMs are equipped with an extra pair of row-buffers per rank, used exclusively for migrations. Operated by the MC, these buffers communicate with the internal prefetching circuitry of the PCM DIMM [21, 22], bypassing the original bank's row buffer. Since our migrations occur in sequence, two of these buffers are necessary only when the migration involves two banks of the same rank, and one buffer would suffice otherwise. This modification is not applied to DRAM DIMMs to avoid their redesign. (The energy and delay costs of these extra PCM DIMM buffers are taken into account in our simulations.)

RaPP uses a different destination unranked (and thus unpopular) PCM frame every time it needs to migrate a page out of DRAM. The reason is that migrations involve writes to the PCM cells. Using different unpopular pages guarantees that these writes are evenly spread across the PCM area for wear leveling. We start picking unranked frames from the bottom of the physical address space (which maps to the end of the PCM area), and move upward from there whenever a new PCM frame is needed.

The set of scheduled migrations is maintained in a list. We deschedule migrations whenever the corresponding PCM pages cross back down to queue 4 before the migrations start. The MC performs migrations from the list whenever there are no LLC misses or write-backs to perform. Any misses that arrive for a page undergoing a migration are directed to the original address or to one of the intermediate buffers. Write-backs are buffered until the migration is concluded.

Figure 3.2: RaPP example. Before and after we migrate a PCM page (stored in frame 13) that crossed over to the DRAM side of the ranking to a frame from the victim list (frame 2). Dark shading represents PCM frames and no shading represents DRAM frames.

For best performance, our goal is to execute the migrations completely in the background and without OS involvement. Thus, the MC maintains the *RemapTable*, a hash table for translating frame addresses coming from the LLC to actual remapped frame addresses. Figure 3.2 shows an example *RemapTable*. The *RemapTable* is accessible by the OS as well. Periodically or when the *RemapTable* fills up (at which point the MC interrupts the CPU), the OS commits the new translations to its page table and invalidates the corresponding TLB entries. (When non-virtually addressed hardware caches are used, some lines may have to be invalidated as well.) We assume that the OS uses a hashed inverted page table, as in the UltraSparc and PowerPC architectures, which considerably simplifies the commit operation. Since a commit clears the *RemapTable*, the OS sets a flag in a memory-mapped register in the MC to make sure that the MC refrains from migrating pages during the commit process.

The RemapTable also includes two bits for communication between the MC and the OS. One bit is called MigratingNow, which when set means that the corresponding frame is currently scheduled for a migration. The other bit is called ReplacingNow, which when set means that the OS is replacing the page currently stored in that frame. The MC is responsible for MigratingNow, whereas the OS is responsible for MigratingNow.

ReplacingNow. Before the OS tries to replace a page, it must check the RemapTable first. There are three possible scenarios here. Scenario 1: If there is no entry for the physical frame in which the page lies, the OS creates one, sets ReplacingNow, and programs the DMA engine to use the frame. The MC does not migrate any page to that same frame while ReplacingNow is set. When the replacement is done, the OS resets ReplacingNow. Scenario 2: If there is an entry for the corresponding frame and MigratingNow is set, the OS should select another page for replacement. Scenario 3: If the frame has already changed addresses (i.e., the entry for the frame exists and MigratingNow is not set), the OS can set ReplacingNow and proceed using the new frame address.

Finally, for robustness, RaPP uses a self-disabling mechanism that disables access monitoring, queue maintenance, and migrations whenever too many "bad migrations" occur. A bad migration occurs in one of two cases: (1) when a page originally in PCM is migrated to DRAM and then back to PCM without being referenced enough times while in DRAM; or (2) when a page originally in DRAM is evicted to PCM and then back to DRAM with too many accesses while in PCM. To implement this mechanism, we use a single counter of bad migrations (CBM) and a 2-bit saturating counter per MQ entry. Whenever a ranked page is touched, the saturating counter is incremented. Whenever a migration is completed, using the *RemapTable*, RaPP can identify where the page was since the last commit to the OS page table. If the migration falls into case (1) and the counter is not saturated, or it falls into case (2) and the counter is saturated, CBM is incremented. The saturating counter for a page is reset whenever the page migrates. At the end of each 1ms epoch, if the number of bad migrations reached 5% (the "disable threshold") or more of the maximum number of migrations possible within the epoch, RaPP is disabled.

**Controller structure.** Our MC adds a few components to a vanilla MC. Our MC (Figure 3.3) extends a programmable MC from [86] by adding RaPP's own modules (shaded in the figure). The MC receives read/write requests from the LLC controller via the CMD queue. The Arbiter iteratively dequeues requests, which the Controller

| Memory controller | 1       |            |                            |                              |     |       |

|-------------------|---------|------------|----------------------------|------------------------------|-----|-------|

| CMD queue         | Arbiter | Controller |                            |                              |     |       |

| Migration control |         |            | Dedicated                  | DRAM<br>Physical             | ᡨ   | DRAM  |

| Input queue       |         |            | routing                    | Interface                    |     | DIMMs |

| Output queue      | Data    | apath      | &                          | PCM<br>Physical<br>Interface |     |       |

| Remap             |         |            | l/O<br>clocking<br>network |                              | ••• | PCM   |

| Ranking           |         |            |                            |                              |     | DIMMS |

Figure 3.3: Memory controller with RaPP's new modules highlighted.

converts into commands to be sent to the memory devices. The Controller routes those commands by frame address to the appropriate Physical Interface (DRAM or PCM), which converts commands into timing relationships and signals for operating memory devices and coordinating data transfers. The Interfaces also control the power states of their respective memory ranks. The Datapath handles the data flow from the memory devices to the LLC controller and vice-versa. The module places data read from memory into the Output queue, where the LLC controller can read it. On write-back requests, the Datapath reads data (provided by the LLC controller) from the Input queue. For consistency, the CMD queue logic checks if the target address of a read or write-back collides with older write-backs in the Input queue. A colliding read is serviced from the queue without actually reaching the memory devices, thus finishing faster. A colliding write-back invalidates the older write-back command and data.

RaPP's Ranking module (RKMOD) contains the small on-chip cache of MQ and victim entries (entry cache) and the queue for updates to the MQ queues and the victim list (update queue). Misses in the entry cache produce requests to DRAM. RKMOD's logic snoops the CMD queue, creating one update per new request. To reduce the lag between an access and its corresponding MQ entry update, the update queue is implemented as a small circular buffer (32 entries), where an entering update precludes any currently queued update to the same entry.

The Migration Control module (MIGMOD) contains the queue of scheduled migrations (migration queue) and three page-sized buffers for the migrations (transfer buffers). MIGMOD processes migrations sequentially, each one occurring in two stages: (1) read and buffer frames; and (2) write frames to their new locations. Stage (2) does not start until stage (1) is completed. MIGMOD latches the base addresses of the frames undergoing a migration, as well as an offset address within each frame. The Controller module detects memory accesses that target one of the frames undergoing migrations by checking the base addresses. The Controller serves an access that targets a migrating frame by accessing the appropriate structure (main memory or a transfer buffer).

The Remap module (REMOD) contains the *RemapTable* and the logic to remap target addresses. At the end of a migration, MIGMOD submits the three latched frame numbers to REMOD, which creates new mappings in the *RemapTable*. REMOD snoops the CMD queue to check if it is necessary to remap its entries. Each *RemapTable* lookup and each remapping take 1 memory cycle. However, these operations only delay a request if it finds the CMQ queue empty.

Note that many previous works have proposed MCs with similar levels of sophistication and complexity, e.g. [19,23,39,40,65,88,89]. For example, [39] implements a learning algorithm in the memory controller itself.

**Storage overhead.** The bulk of our MC design is in the storage structures that it contains. The total on-chip storage in our design is 126 KBytes. By design, the page buffers require 24 KBytes (3 pages). The other structures have empirically selected sizes: 28 KBytes for the *RemapTable* (4K entries), 64 KBytes for the cache of MQ and victim entries (4K entries), and 10 KBytes for the update and migration queues. This amount of on-chip storage is small compared to the multi-MByte shared LLC.

Our design also has limited DRAM space requirements. Taking a system with 1GB of DRAM + 32GB of PCM as a base for calculation, the total DRAM space consumed by descriptors is 6 MBytes (0.59% of the DRAM space). Each frame descriptor in the MQ queues or in the victim list takes 124 bits, which we round to 128 bits. Each

descriptor contains the corresponding frame number (22 bits), the reference counter (14 bits), the queue number, including victim list (4 bits), the last-access time (27 bits), three pointers to other descriptors (54 bits), a flag indicating that the frame has been demoted (1 bit) and the counter for bad migrations (2 bits). For the configurations with which we experiment, the space taken by the descriptors is 0.63 MBytes.

### 3.2.2 Comparable Hybrid Memory Systems

We compare our design to the two most closely related hybrid memory systems: DBUFF [67] and WP [89].

**DRAM Buffer (DBUFF)** relies on a DRAM buffer logically placed between the CPU and a main memory composed solely of PCM [67]. The DRAM buffer is implemented as a set-associative cache managed entirely by the MC and invisible to the OS. Cache blocks (corresponding to virtual memory pages) coming from secondary storage are initially installed in the DRAM buffer, but also take space in PCM. From then on, the memory accesses are directed to the DRAM buffer. On a buffer miss, the page containing the desired cache line is brought into the buffer from PCM. When a block is replaced from the buffer (using the clock algorithm), it is written to its PCM frame if this is the first eviction of the block or the block was written in the buffer. Block writes to PCM are enqueued in an write buffer and done lazily in background. Like in our design, only the cache lines that were actually written are written to PCM.

When workloads exhibit good locality, most accesses hit the DRAM buffer, which leads to good performance and dynamic energy. Endurance is also good since the lazy block writes and cache-line-level writes substantially reduce the write traffic to the PCM array. (In fact, our implementation of DBUFF does not include the Fine-Grained Wear Leveling and Page-Level Bypass techniques proposed in [67]. The reason is that the endurance produced by the other techniques is sufficient in our experiments; adding extra complexity does not seem justified for our workloads and endurance assumptions.) However, workloads with poor locality may lead to poor performance and energy consumption. In addition, the inclusive DRAM caching in DBUFF reduces the amount of available memory space, potentially leading to a larger number of page faults than our design.

Our simulations of DBUFF are optimistic in many ways. First, we consider a DRAM buffer of size approximately 8% of the total memory size (rather than the original 3%). Second, we assume no DRAM buffer lookup overhead in performance or energy. Third, we implement the DRAM buffer as a fully associative structure (rather than set associative) with LRU replacement (rather than clock). Fourth, on a DRAM buffer miss requiring a page write-back, the dirty blocks (only) are written back at the same time as the missing page's content is fetched from PCM or disk.

Despite these optimistic assumptions, RaPP improves on DBUFF in two fundamental ways: (1) it uses the entire memory as a flat space, relying on page migration rather than replication; and (2) it detects when most migrations are useless and turns itself off.

Hot-modified Pages in Write Partition (WP) places DRAM and PCM in a flat address space and treats DRAM as an OS-managed write partition [89]. All pages are initially stored in PCM. The idea is to keep the cold-modified (infrequently written) pages in PCM, trying to take advantage of its low idle power consumption, and the hotmodified (frequently written) pages in DRAM to avoid PCM's high write latency and poor endurance. The MC implements a variation of the MQ algorithm with 16 LRU queues, but only counts write accesses to the physical frames. Frames that reach queue 8 (receive  $2^8$  writes) are considered to store hot-modified pages. On a page fault, the OS brings the page from secondary storage to the PCM area. Over time, the pages that become hot-modified are migrated to DRAM by the OS. At the same time, a page currently in DRAM but with fewer writes may have to be migrated back to PCM.

Our simulations of WP are also optimistic, as we do not charge any performance or energy overheads for the data structures and hardware modifications necessary to implement WP.

Despite these optimistic assumptions, there are three main problems with WP. First, it can hurt the performance of read-dominated workloads under less optimistic assumptions about PCM read performance. Second, migrating pages using a core at the OS quantum boundary wastes opportunities to improve performance and energydelay within that timespan. Third, endurance also suffers because it takes a large number of writes until the OS will consider migrating a heavily written page to DRAM. Our evaluation studies mainly how WP compares to other approaches. However, in Section 3.3.3, we also isolate the impact of migrating frequently-read pages and enabling migrations within the OS quantum via hardware.

RaPP improves on WP by: (1) migrating pages that are read-intensive as well; (2) migrating pages in the background, without OS involvement; (3) including mechanisms for identifying pages worthy of migration and self-disabling for when migrations are mostly useless; and (4) spreading migrations across many physical frames. Moreover, our study improves on [89] by: (5) assuming more realistic PCM characteristics; (6) presenting a comparison of RaPP and WP to DBUFF, across a large set of workloads and parameters; and (7) evaluating other WP designs.

## 3.3 Evaluation

In this section, we evaluate hybrid memory systems using energy and performance as first-order metrics. Although we also report endurance results, we give them lower emphasis because our system can be easily combined with many previously proposed techniques to mitigate the PCM endurance problem (Section 5.2). Our evaluation is based on simulation, since PCM hardware is not yet available.

#### 3.3.1 Methodology

Workloads. We simulate combinations of benchmarks from the SPEC 2000, SPEC 2006, and Stream suites forming a total of 27 workloads (Table 3.1). Because our workloads have widely different memory footprints, we group them with respect to footprint size into Large (LG), Medium (MD), and Small (SM) classes.

Simulation infrastructure. To reduce simulation times, our simulations are done in two steps. In the first step, we use M5 [9] to collect memory access (LLC misses and write-backs) traces from our workloads running on an 8-core server. Each benchmark in

| Tag | Footprint (MB) | MPKI | WB% | Applications (x2 each)                                                                |  |

|-----|----------------|------|-----|---------------------------------------------------------------------------------------|--|

| LG1 | 993            | 12   | 33  | milc <sup>*</sup> , gobmk <sup>*</sup> , sjeng <sup>*</sup> , libquantum <sup>*</sup> |  |

| LG2 | 992            | 29   | 32  | S.add, S.copy, apsi, milc <sup>*</sup>                                                |  |

| LG3 | 746            | 24   | 27  | mcf <sup>*</sup> , S.triad, sjeng <sup>*</sup> , facerec                              |  |

| LG4 | 743            | 4    | 25  | vortex, milc <sup>*</sup> , sixtrack, mesa                                            |  |

| LG5 | 702            | 24   | 26  | sjeng <sup>*</sup> , S.triad, S.add, swim                                             |  |

| LG6 | 683            | 4    | 28  | perlbmk, crafty, gzip, milc <sup>*</sup>                                              |  |

| LG7 | 645            | 25   | 32  | lucas, gcc, $mcf^*$ , $sphinx3^*$                                                     |  |

| LG8 | 594            | 18   | 32  | wupwise, $vpr$ , $mcf^*$ , parser                                                     |  |

| LG9 | 557            | 17   | 32  | swim, eon, art, lucas                                                                 |  |

| MD1 | 486            | 13   | 49  | applu, lucas, gap, apsi                                                               |  |

| MD2 | 467            | 23   | 32  | S.scale, S.triad, swim, eon                                                           |  |

| MD3 | 414            | 20   | 30  | mcf <sup>*</sup> , parser, twolf, facerec                                             |  |

| MD4 | 407            | 8    | 24  | namd <sup>*</sup> , S.triad, sjeng <sup>*</sup> , wupwise                             |  |

| MD5 | 394            | 13   | 32  | art, lucas, mgrid, fma3d                                                              |  |

| MD6 | 385            | 24   | 28  | $\operatorname{art}, \operatorname{mcf}^*, \operatorname{gzip}, \operatorname{vpr}$   |  |

| MD7 | 381            | 14   | 23  | S.add, h264ref <sup>*</sup> , equake, hmmer <sup>*</sup>                              |  |

| MD8 | 367            | 46   | 33  | S.triad, S.add, S.copy, S.scale                                                       |  |

| MD9 | 356            | 30   | 27  | equake, S.scale, S.triad, mgrid                                                       |  |

| SM1 | 295            | 2    | 21  | wupwise, $gobmk^*$ , $vortex$ , $h264ref^*$                                           |  |

| SM2 | 285            | 5    | 33  | swim, perlbmk, namd <sup>*</sup> , eon                                                |  |

| SM3 | 283            | 6    | 33  | swim, crafty, twolf, gcc                                                              |  |

| SM4 | 276            | 16   | 33  | lucas, h264ref <sup>*</sup> , libquantum <sup>*</sup> , sphinx3 <sup>*</sup>          |  |

| SM5 | 271            | 15   | 27  | wupwise, equake, ammp, libquantum*                                                    |  |

| SM6 | 260            | 11   | 24  | fma3d, mgrid, galgel, equake                                                          |  |

| SM7 | 247            | 12   | 32  | fma3d, sphinx3 <sup>*</sup> , galgel, lucas                                           |  |

| SM8 | 243            | 15   | 21  | S.triad, h264ref <sup>*</sup> , fma3d, equake                                         |  |

| SM9 | 243            | 2    | 29  | ammp, gap, wupwise, vpr                                                               |  |

Table 3.1: Workload described by tag, memory footprint in MB, LLC misses per 1000 instructions (MPKI), and percentage of LLC write-backs as a fraction of all memory accesses (WB%). Applications marked with \* belong to Spec 2006.

|                    | Feature                        | Value                        |                  |

|--------------------|--------------------------------|------------------------------|------------------|

| CPU co             | ores (2.668GHz, Alpha ISA)     | 8 in-order, one thread/core  |                  |

| L                  | 1  I/D cache (per core)        | 64KB, 2-way, 1 CPU cycle hit |                  |

|                    | L2 cache (shared)              | 8MB, 8-way, 10 CPU cycle hit |                  |

| Cache              | e block size / OS page size    | 64 bytes / 8KB               |                  |

| Memo               | ory $(667 MHz/DDR3-1333)$      | 8KB rows, close-page         |                  |

| Memor              | ry devices (x8 width, $1.5V$ ) | DRAM                         | PCM              |

|                    | $\mathrm{tRCD}$                | 15ns                         | 56ns             |

|                    | $\mathrm{tRP}$                 | 15ns                         | 150 ns           |

|                    | $\mathrm{tRRDact}$             | 6 ns                         | 5ns              |

| Delay              | $\mathrm{tRRDpre}$             | 6 ns                         | 27 ns            |

|                    | Refresh time                   | $64 \mathrm{ms}$             | n/a              |

|                    | tRFC / tREFI                   | 110<br>ns / 7.8 $\mu s$      | n/a              |

|                    | Row Buffer Read                | 200mA                        | 200mA            |

|                    | Row Buffer Write               | $220 \mathrm{mA}$            | 220mA            |

| Current            | Avg Array R/W                  | $110 \mathrm{mA}$            | 242mA            |

| Curren             | Active Standby                 | $62 \mathrm{mA}$             | $62 \mathrm{mA}$ |

|                    | Precharge Powerdown            | $40 \mathrm{mA}$             | 40mA             |

|                    | Refresh                        | $240 \mathrm{mA}$            | n/a              |

| Normalized Density |                                | 1                            | 4                |

|                    | Data Retention                 | $64 \mathrm{ms}$             | > 10 years       |

| C                  | ell endurance (writes)         | $> 10^{16}$                  | $10^8 - 10^9$    |

Table 3.2: System settings.

a workload is represented by its best 100M-instruction simulation point (selected using Simpoints 3.0 [66]). A workload terminates when the slowest application has executed 100M instructions.

In the second step, we replay the traces using our own detailed memory system simulator. This simulator models all the relevant aspects of the OS, memory controller, and memory devices, including inverted page tables, contention, memory device power and timing, and row buffer management. Our decision to develop our simulator stemmed from our need, at the time, for a tool that simulated DDR3 in detail, in reasonable time, and that was simple to expand.

The main architectural characteristics of the simulated server are listed in Table 3.2. We simulate in-order cores to expose the overheads associated with PCM accesses to workloads. The cores have private 64-Kbyte 2-way instruction and data L1 caches, as well as an 8-MByte 8-way combined shared cache. For this cache architecture, Table 3.1 reports the LLC misses per kilo instruction (MPKI) and the percentage of LLC writebacks (WB%) for each workload. The memory system has 4 DDR3 channels, each one occupied by a single-rank DIMM with 8 devices (x8 width) and 8 banks per device. In all simulations, we assume an initially warm memory (no cold page faults). The MC implements cache-block-level bank interleaving and page-level channel interleaving. Memory accesses are served on a FCFS basis. The MC uses close-page row buffer management. (More sophisticated access scheduling is not necessary for our simulated system and workloads, as opportunities to increase their bank hit rate via scheduling are rare, and such improvements are orthogonal to our study.)

A memory rank can be in (1) Active Standby state, when at least one of its banks is serving requests; or (2) Precharge Power Down, when all banks are idle and the clock enable line is turned off to save energy. Additionally, PCM is enhanced to avoid writing unmodified cache lines back to the cell array. The table shows power parameters [47] of DRAM and PCM chips, and the timing parameters that change across memory technologies [47, 67, 89]. The timing parameters are: the time between the issue of a row activation command and the data being accessible at the row buffer of a given bank (tRCD); the time between two row activation commands issued to the same rank after the evicted row was read (tRRDact) or written (tRRDpre); the time between a precharge and an activation to a same rank (tRP); the time between two refresh commands or a refresh and an activation (tRFC); the maximum time between refresh commands for a same row (Refresh time); and the average delay between refresh commands across all rows (tREFI). In addition to these parameters, we simulate 12 other timing constraints that are relevant for our study [55, 83].

Besides RaPP, we simulate the two hybrid approaches mentioned in Section 3.2 (DBUFF and WP) and an additional "Unmanaged" system, in which pages remain in the frames originally assigned to them by the OS. We use Unmanaged as the baseline for comparison. Only RaPP is assumed to have energy and performance overheads stemming from its data structures. Our assumptions for RaPP are consistent with those of other authors [30]. For example, the RaPP SRAM consumes 0.13W of background power and 0.017nJ per 16-byte operation; the transfer buffers consume

0.06W of background power and 0.06nJ per 64-byte operation; and each DIMM-level row buffer increases the rank background power by 12.5% when active (and as much dynamic power as a regular row buffer). The four hybrid systems have 1 channel equipped with 1 DRAM DIMM (128MB) and the remaining 3 channels with 1 PCM DIMM each (3x128x4MB=1536MB), totaling 1.664 GBytes of memory. We picked these small memory sizes to match the footprint of the workloads' simulation points.

As another basis for comparison, we use a PCM-only system with 2 GBytes of memory (4x128x4MB). Previous works have shown that the DRAM-only system exhibits much worse performance than PCM-only and hybrid systems [67], due to its lower storage capacity, so we do not consider it in this chapter.

## 3.3.2 Results

## 3.3.2.1 Performance and energy

We now compare the behavior of RaPP, DBUFF, WP, and the two baseline systems. Due to space limitations, we do not present separate performance and energy results for all workloads; instead, we plot these results for the MD workloads and discuss the results for other workloads in the absence of figures. Later, we plot energy-delay<sup>2</sup> (ED2) results for all workloads.

Figure 3.4 presents the running time (top graph, including the geometric mean of the MD results), average memory power consumption (middle graph, including the power consumed by the SRAM cache used in RaPP), and number of page migrations in RaPP and WP and page fetches from PCM in DBUFF (bottom graph, again including the geometric mean). We refer to page migrations and fetches collectively as page transfers. The performance and power results are normalized to Unmanaged. Note that we plot average power, rather than energy, to remove the impact of different running times (which are plotted in the top graph).