## THE STUDY OF CMOS BASED VCO WITH ACTIVE INDUCTOR AND ITS DESIGN METHODOLOGY

By

#### SY-MIN CHUENG

A thesis submitted to the

Graduate School-New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

written under the direction of

Jeffrey Walling

and approved by

New Brunswick, New Jersey

October 2012

© 2012

Sy-Min Chueng

ALL RIGHTS RESERVED

## **ABSTRACT OF THE THESIS**

# THE STUDY OF CMOS BASED VCO WITH ACTIVE INDUCTOR AND ITS DESIGN METHODOLOGY

By Sy-Min Chueng

Thesis director : Jeffery Walling

Active Inductors are useful in reducing the large chip area typically consumed by spiral inductors, as well as providing larger inductance values and higher quality factors that otherwise cannot be achieved by spiral inductors. Integrated inductors find application in many radio frequency (RF) front end integrated circuits, including impedance matching, filtering, biasing and in oscillator circuits. Nonetheless, because of the interdependent relationship of the self-resonant frequency and quality factor it is often difficult to meet desired circuit requirements. Additionally, active devices pose problems of higher power consumption , noise figure and potential instability. This thesis begins with the study of active inductors, the Wu active inductor in particular, and considers tuning methods based on the Wu active inductor topology. Starting with the small-signal model, the emulated inductance and quality factor expressions are derived. Next, the operation of active inductors under large-signal is closely examined. Comparisons between a passive and an active VCO are made. The active inductor based voltage-controlled oscillator (Active VCO) is studied extensively, and the methods of improving the performance under large signal-behavior are discussed. Then a design procedure based on  $g_{m}/I_D$  methodology is proposed. A Matlab script that can be applied to gyrator-C based active inductors is developed to determine the sizing of the transistors for a desired inductance and resonant frequency. Cadence Virtuoso is used for simulations, and extraction based on an IBM 8RF technology file. Finally, a low power active VCO is designed, simulated and laid out.

#### Acknowledgements

I would like to thank my thesis advisor Prof. Jeffery Walling for his constant guidance throughout the course of my thesis. His knowledge and insight into electrical engineering are sources of inspiration. Most importantly, he has always been patient and helpful when I encountered difficulty. He also contributed greatly to this work by sharing his Ocean Script and Matlab codes for creating the technology file and the look-up functions, as well as helping me revising the thesis thoroughly.

I would also like to thank Prof. Wei Jiang and Prof Predrag Spasojevic for being a part of my thesis committee. I have taken both their classes when I was an undergraduate student, and they are both very good professors. Special thanks to Prof. Wei. Jiang for recommending me for graduate study at Rutgers. I hope my time spent in Rutgers ECE program will help me become a competent engineer.

The appreciation is also given to the members of the group, Sumati Sehajpal and Ilya Chigirev, for the discussion and help. Yi Huang also gave me many valuable inputs.

Finally, I want to thank my family and my parents for their moral and financial support. Without them, I wouldn't have the opportunity to achieve this personal goal.

## **Table of Contents**

| ABSTRACT OF THE THESIS                                             | ii  |

|--------------------------------------------------------------------|-----|

| Acknowledgements                                                   | iii |

| Chapter 1                                                          | 1   |

| 1.1 Introduction                                                   | 1   |

| Chapter 2                                                          | 3   |

| 2.1 Active Inductor                                                | 3   |

| 2.2 Active Inductor Tuning                                         | 8   |

| 2.3 Negative Resistance Tuning                                     | 11  |

| Chapter 3                                                          | 16  |

| 3.1 Active VCO                                                     | 16  |

| 3.2 Voltage Swing                                                  | 20  |

| 3.3 Large Signal Analysis                                          | 23  |

| 3.4 Noise                                                          |     |

| 3.5 Oscillator Phase Noise                                         |     |

| 3.5.1 Injection Locked Active VCO                                  |     |

| 3.5.2 Constant Q active Inductor                                   | 37  |

| Chapter 4                                                          |     |

| 4.1 Active Inductor Design                                         |     |

| 4.2 Active VCO Design                                              | 47  |

| Chapter 5                                                          | 53  |

| 5.1 Conclusion and Further Work                                    | 53  |

| References                                                         | 54  |

| Appendix A: The Derivation of equations 2.2~2.5                    |     |

| Appendix B: Matlab Code for Calculation of Active Inductor and VCO | 60  |

# List of Figures

| Figure 1.1 Schematic diagram of a gyrator based active inductor                   | 2  |

|-----------------------------------------------------------------------------------|----|

| figure 2.1 Wu inductors with different types of feedback networks                 |    |

| Figure 2.2 Small-Signal Model of an Active Inductor                               |    |

| Figure 2.3 Active Inductor and Its equivalent circuit                             |    |

| Figure 2.4 Frequencies response of an active inductor                             |    |

| Figure 2.5 Schematic diagrams for active Inductors using negative feedbacks       |    |

| Figure 2.6 (a) Inductance vs. frequency of Figure 2.5(a)                          |    |

| Figure 2.6 (b) Inductance vs. frequency of Figure 2.5(b)                          |    |

| Figure 2.7 Negative-resistance tuning                                             | 11 |

| Figure 2.8 Active inductor with a negative-resistance circuit                     | 12 |

| Figure 2.9 (a) Real part of the frequency response                                | 13 |

| Figure 2.9 (b) Imaginary part of the frequency response                           |    |

| Figure 2.10 Schematic for independent tuning                                      |    |

| Figure 3.1 Feedback system                                                        |    |

| Figure 3.2 Frequency Selective network                                            |    |

| Figure 3.3 Cross-coupled pairs                                                    |    |

| Figure 3.4 Schematic for NMOS and PMOS voltage-controlled oscillators             |    |

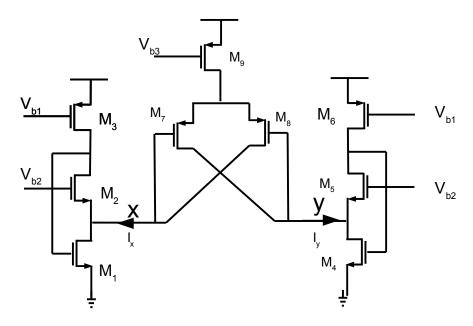

| Figure 3.5 schematic for active VCO                                               |    |

| Figure 3.6 Typical output waveforms of PMOS and NMOS VCOs                         |    |

| Figure 3.7 Large-signal voltage swing                                             |    |

| Figure 3.8 Signal swing between regions of operation                              |    |

| Figure 3.9 Average Capacitance.                                                   |    |

| Figure 3.10 An Active Inductor with Sine Wave at Its Input                        |    |

| Figure 3.11 Time-varying parameters under large-signal.                           | 30 |

| Figure 3.12 Resonant frequency vs. time. The frequency of input sine-wave is 3GHz | 34 |

| Figure 3.13 Equivalent noise circuit.                                             |    |

| Figure 3.14 A constant Q active inductor                                          | 38 |

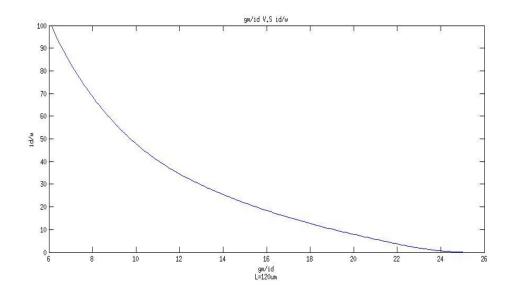

| Figure 4.1 (a) Vov vs. gm/Id                                                      | 41 |

| Figure 4.1 (b) gm/Id vs. Id/W                                                     | 41 |

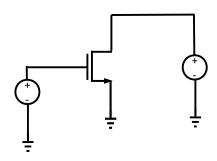

| Figure 4.2 Schematic for creating technology file                                 | 42 |

| Figure 4.3 Active inductor                                                        |    |

| Figure 4.4 Schematic for Active VCO                                               | 49 |

| Figure 4.5 (a) Output voltage of Active VCO                                       |    |

| Figure 4.5 (b) Output current of active VCO                                       |    |

| Figure 4.6 Complete layout                                                        | 52 |

## List of Tables

| Table 2.1 Sizing of the Transistors                                            | 8  |

|--------------------------------------------------------------------------------|----|

| Table 3.1 Resonant frequency for Different Amplitudes and Sweeping Frequencies |    |

| Table 4.1 List of look up functions                                            | 42 |

| Table 4.2 Transistors Sizing of Active VCO                                     |    |

## **Chapter 1**

#### 1.1 Introduction

Active inductors have gained great interests in low-power applications over the last decade in an effort to reduce the need for large chip area required to fabricate spiral inductors and transformers. Inductive impedances are essential in high speed application due to their ability to improve bandwidth and boost gain, and to perform impedance matching and frequency selection. Many architectures for active inductors have been proposed [1-6]. Some of the unique advantages of active devices compared to those of their passive counterparts are small layout area, larger inductance and quality factor with the ability to tune either parameter, and full compatibility with digitally oriented CMOS technologies. Nonetheless, active inductors have several drawbacks including: higher power consumption for biasing the transistors, relatively low power handling capability since the active inductors do not have the energy storage properties of physical inductors, higher noise figure owing to active components and limited bandwidth due to the active devices. Additionally, one side of the active inductor being always held at a constant DC bias restricts the possible applications. All these make active inductors difficult to integrate.

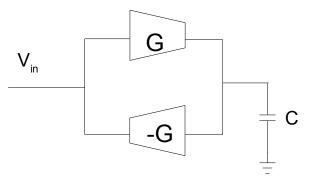

Active inductors are based on the gyrator principle. A symbol representing such inductors is shown in Figure 1.1. The forward path transconductor, G, has a positive transconductance while the transconductor in the feedback path, -G, has a negative transconductance. Inductance is simulated by the capacitance C. For this reason, the

synthesized inductor is called a gyrator-C active inductor with an inductance value [7]

Figure 1.1 Schematic diagram of a gyrator based active inductor.

```

C/G^2 (1.1)

```

where G is the gyration conductance. Cascading two ideal gyrators forms an ideal transformer suggests that two active inductor can be electrically coupled to form an active transformer. [8] The focus of this thesis is to study the Wu current-reuse active inductor[9], as well as its applications; specifically, the CMOS differential LC oscillator will be examined. First the small signal equivalent circuit will be examined, and then this knowledge will be expanded to predict the large signal behavior of the active inductor in an active-LC VCO. Finally, after considering many design issues, the goal is to create a procedure to design the active VCO systematically.

## **Chapter 2**

#### 2.1 Active Inductor

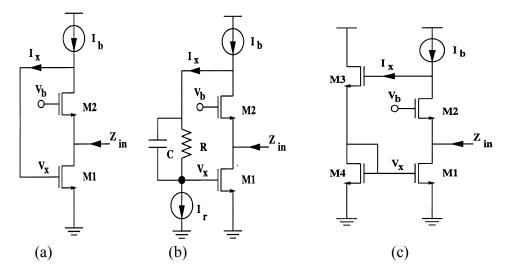

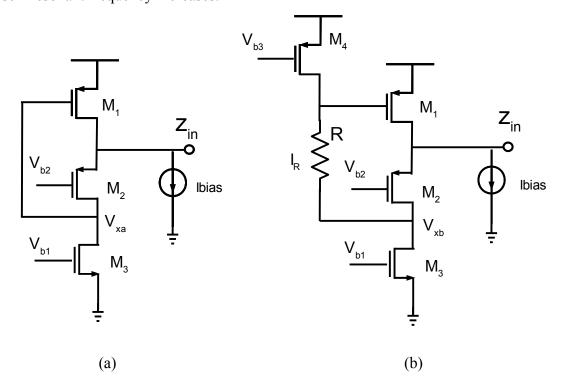

figure 2.1 Wu inductors with different types of feedback networks.

Three types of shunt-feedback active inductors shown in (Figure 2.1) were proposed in Wu's paper [9]. All operate in a similar manner. In Figure 2.1(a) the input signal at the drain of  $M_i$  generates a current  $gm_2v_i$ , that charges  $C_{gsi}$  through the feedback path. The voltage  $v_x$  then provides for the current  $gm_1v_{gsi}$  and generates an inductive loading effect. Shown in Figure 2.1(b), R, and current source,  $I_r$ , form a DC level shifter. The shunt capacitance acts to short the resistor at high frequencies. In Figure 2.1(c), transistors  $M_3$  and  $M_4$  are used as level shifter similar to (b). Another way to look at this is that at low frequencies the impedance at the input node is low due to the shunt feedback as the frequency increases, the current starts to flow through the gate-source capacitance and causes the loop gain to reduce. Hence, the impedance increases as the frequency increases, emulating the impedance of an inductor [10]. The active inductor shown in Figure 2.1(a) is chosen for this thesis because it works better at higher frequencies and has superior noise performance. The small-signal model of such an the active inductor is shown in Figure 2.2. Assuming an ideal current source, the input admittance of the active inductor can be written as<sup>1</sup>:

$$Y = go_1 + \frac{gm_1(gm_2 + go_2 + sCgd_1)}{sCgd_2 + sCgs_1 + go_2 + sCgd_1} + sCgs_2 + gm_2 + go_2 + sCgd_1 - \frac{go_2(gm_2 + go_2 + sCgd_1)}{sCgd_2 + sCgs_1 + go_2 + sCgd_1}$$

(2.1)

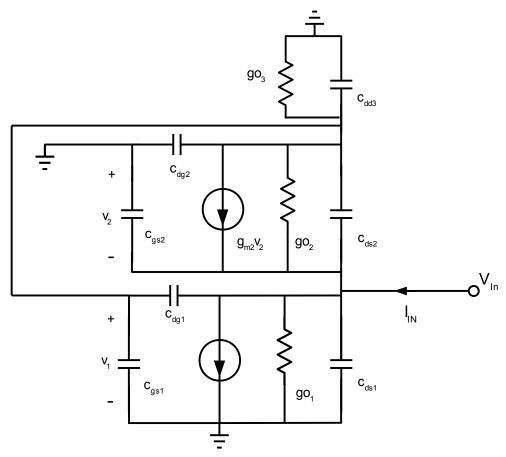

Figure 2.2 Small-Signal Model of an Active Inductor

where  $g_m$  and  $g_o$  are the transconductance and output conductance of the transistor. The body effect of M<sub>2</sub>,  $g_{mb2}$ , can be included in  $g_{m2}$ , or it can be eliminated using a triple

<sup>1</sup> Please see Appendix A for detailed derivation using a more complete circuit

well structure.  $C_{dd3}$  and  $g_{o3}$  are zero for an ideal current source and  $C_{ds1}$  and  $C_{ds2}$  are neglected since they are likely to be small when the transistors are saturated. The input impedance is given by [3]:

$$Z_{ln} = \frac{b_{1}s + b_{o}}{s^{2} + 2\alpha s + \omega_{0}^{2}} \quad (2.2)$$

$$b_{1} = \frac{1}{C_{gs2}} , \quad b_{0} = \frac{go_{2}}{C_{gs1}C_{gs2}} \quad (2.3)$$

$$2\alpha = \frac{g_{ol}C_{gs1} + go_{2}C_{gs2} + gm_{2}C_{gs1} + go_{2}Cgs_{1}}{C_{gs1}C_{gs2}} \quad (2.4)$$

$$\omega_{0}^{2} = \frac{gm_{1}gm_{2} + gm_{1}go_{2} + go_{1}go_{2}}{C_{gs1}C_{gs2}} \quad (2.5)$$

where  $\omega_o$  is the resonant frequency of the active inductor. The quality factor is defined by  $Q = \omega_o/2\alpha$ . The equivalent circuit is shown in Figure 2.3.

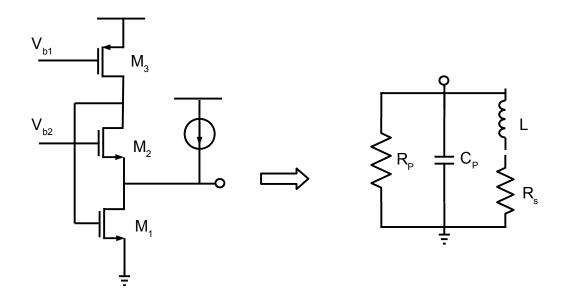

Figure 2.3 Active Inductor and Its equivalent circuit.

With the parameters of the equivalent circuit approximately given by:

$$C_{P} = C_{gs2} \quad (2.6)$$

$$R_{P} = \frac{1}{gm_{2}} \quad (2.7)$$

$$R_{S} = \frac{go_{2} + go_{3}}{gm_{1}gm_{2}} \quad (2.8)$$

$$L = \frac{Cgs_{1} + Cgd_{1} + Cgd_{2}}{gm_{1}gm_{2}} \quad (2.9)$$

From (6)-(9), it can readily be shown that changing the bias currents and aspect ratios of the transistors, the inductance value, center frequency and quality factor can be varied.

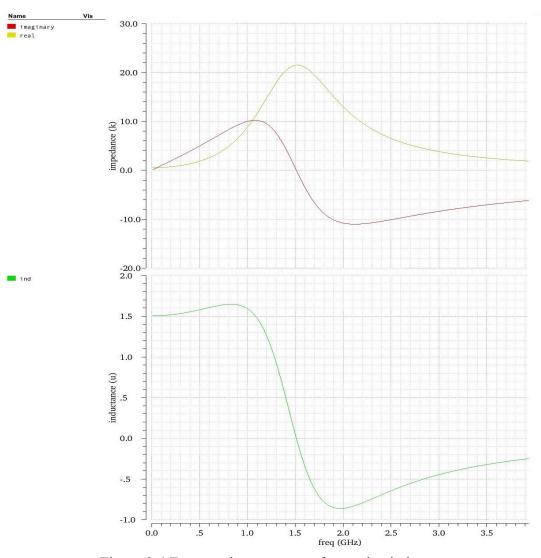

The real and imaginary portions of the impedance of the active inductor are plotted versus frequency in Figure 2.4. The circuit has the response of a second order bandpass filter, hence, the resonant frequency occurs as the imaginary portion of the impedance is equal to zero. The circuit behaves like an inductor below the resonant frequency, and a capacitor above the resonant frequency. The real portion of the impedance peaks at the resonant frequency; hence, this is a parallel RLC circuit.

Figure 2.4 Frequencies response of an active inductor.

### 2.2 Active Inductor Tuning

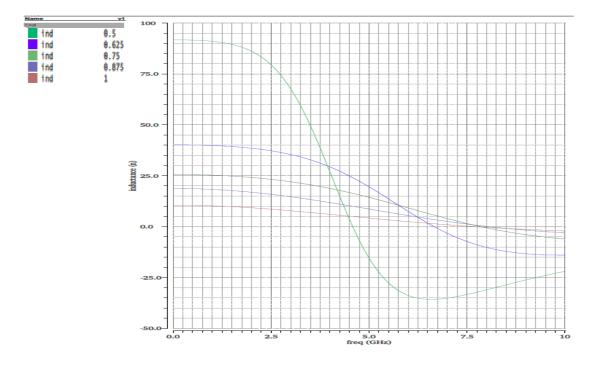

There are many ways to vary the inductance value. One such example is to use a DC level shifter as shown in Figure 2.1 (b) and (c). Another such circuit is shown in Figure 2.5(a) and (b), where the inductance value and resonant frequency can be tuned by varying  $V_{b1}$ . Figure 2.6 (a) shows the inductance looking into port  $Z_{in}$  of Figure 2.5(a) versus frequency. By increasing  $V_{b1}$  from 0.5V to 1V, the inductance decrease while the self-resonant frequency increases.

Figure 2.5 Schematic diagrams for active Inductors using negative feedbacks .

| M <sub>1</sub>                      | M <sub>2</sub> | M <sub>3</sub> | M4        | R   | V <sub>b1</sub> | V <sub>b2</sub> | V <sub>b3</sub> | ibais |  |

|-------------------------------------|----------------|----------------|-----------|-----|-----------------|-----------------|-----------------|-------|--|

| 3u/120n                             | 5u/120n        | 500n/120n      | 160n/120n | 10K | 500mV           | 0.4V            | 0.8V            | 10u   |  |

| Table 2.1 Sizing of the Transistors |                |                |           |     |                 |                 |                 |       |  |

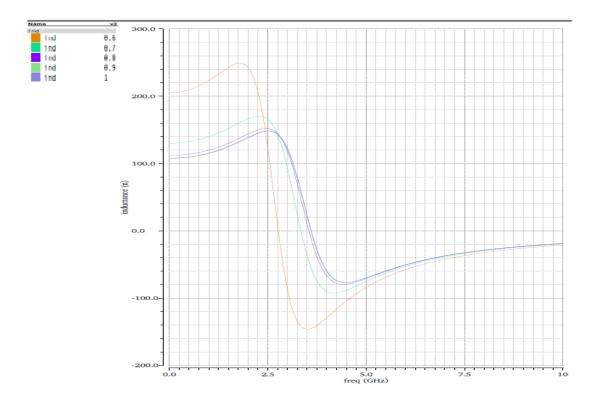

Figure 2.6 (b) shows the addition of a resistor in the feedback, along with an additional

current source; in this topology. the inductance can be greatly increased while marginally reducing the resonant frequency.

In Figure 2.5(a),  $V_{sg1}$  is given by  $V_{DD}$ - $V_{xa}$ , while in in Figure 2.5(b),  $V_{sg1}$  is equal to  $V_{DD}$ - $I_R*R + V_{xb}$ , where

$$I_{R} = \frac{1}{2} \mu_{p} C_{ox} \frac{W}{L} (V_{sg} - |V_{T}|)^{2} \quad (2.10)$$

$I_{D1}$  in both cases is given by  $i_{bias}+I_{D3}$ , so  $g_m$  remains constant if the region of operation does not change. In Figure 2.5(a).  $I_{D2} = I_{D3}$ , whereas in Figure 2.5(b),  $I_{D2}=I_{D3}-I_R$ . This implies that  $M_2$  need not provide as much current in the latter case as it does in the former case, thus the  $g_{m2}$  in case 2 is reduced. From (2.9), we can see that this reduction in  $g_{m2}$  results in an increased effective inductance *L*.

Additionally, passive capacitors and inductors can be used in combination with the active inductor to enhance the circuit performance. For example, by adding a physical inductor at  $Z_{in}$  in series, the inductance increases by the value of the physical inductor, or by adding a capacitance between source and gate of  $M_1$ , the increase in  $C_{GS1}$  also increases the inductance value as it can be seen in (2.9). However, adding a passive inductor in series with the active inductor tends to increase the voltage swing which adversely affects the stability of the DC bias.

Figure 2.6 (a) Inductance vs. frequency of Figure 2.5(a)

Figure 2.6 (b) Inductance vs. frequency of Figure 2.5(b)

### 2.3 Negative Resistance Tuning

By neglecting the output conductance from expressions (2.4) and (2.5), the relations for resonant frequency and quality factor are attained:

$$\omega_0 \approx \sqrt{\frac{gm_1gm_2}{C_{gsl}C_{gs2}}} = \sqrt{\omega_{tl}\omega_{t2}} \quad ; \quad Q_0 \approx \sqrt{\frac{gm_1C_{gs2}}{gm_2C_{gsl}}} = \sqrt{\frac{\omega_{tl}}{\omega_{t2}}} \quad (2.10)$$

where  $\omega_t$  is the transition frequency of the transistor. If two transistors are of similar size, the *Q* of the inductor is approximately unity. Because of the interdependence of these two parameters in (2.10), one cannot be changed independently of the other. In practice, the series parasitic resistance,  $R_s$ , also serves to decrease the quality factor of inductor. From (2.8), it can be seen that by maintaining high transistor output resistance (e.g.,  $g_{o2}=g_{o3}=0.$ ) the series resistance can be reduced. However, as the bias current increases the resonant frequency, the output resistance similarly increases [11].

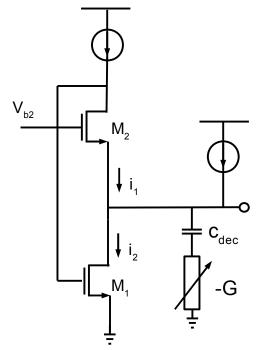

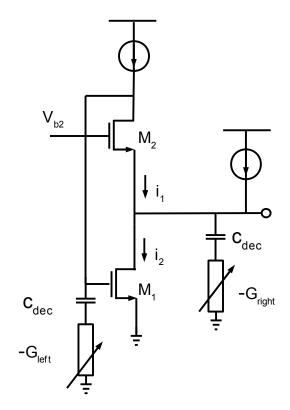

Figure 2.7 Negative-resistance tuning

Use of a negative resistance, as shown in Figure 2.7, improves the Q of the active inductor.

As shown in Figure 2.7,  $C_{dec}$  is a decoupling capacitance, it should be large enough to not adversely affect the frequency response, while decoupling the negative transconductance -G from the DC bias of the active inductor. While the negative resistance strongly increases the quality factor, the resonant frequency decreases at the same time. Expressions (4) and (5) now become [12]:

$$2\alpha = \frac{g_{ol}C_{gsl} + go_2C_{gs2} + gm_2C_{gsl} + go_2Cgs_1 - GCgs_1}{C_{gsl}C_{gs2}}$$

(11)

$$\omega_0^2 = \frac{gm_1gm_2 + gm_1go_2 + go_1go_2 - Ggo_2}{C_{gsl}C_{gs2}}$$

(12)

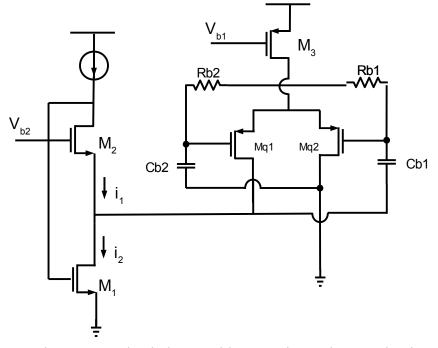

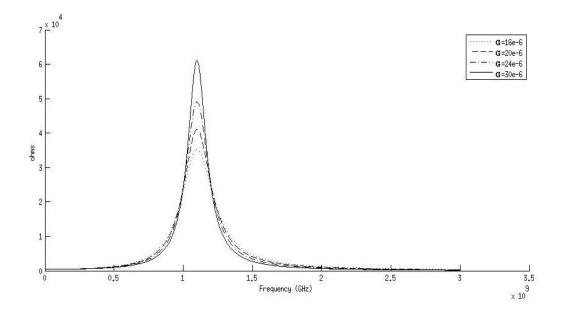

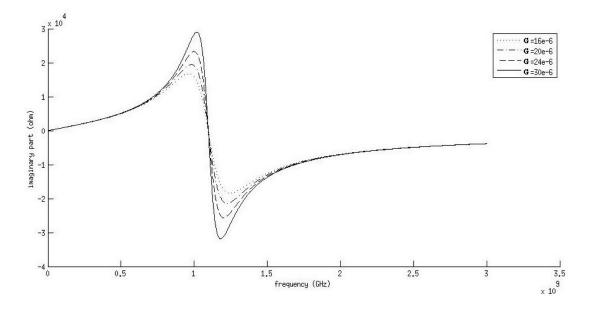

A single ended high Q active inductor is proposed in Figure 2.8 [12].

Figure 2.8 Active inductor with a negative-resistance circuit.

It can be seen in Figure 2.9(a) that the Q increases in real part of the frequency response as the negative conductance increases. The imaginary part is shown in Figure 8(b). Expressions (2.11) and (2.12) are used in the simulation. Notice that there are only slight changes in center frequency, but in reality an increase in voltage results in an increase in parasitic capacitance. These effects are not taken into account in (2.11) and (2.12).

Figure 2.9 (a) Real part of the frequency response ( $M_2 = M_2 = 5u/120n$ , ideal current

source = 1uA).

Figure 2.9 (b) Imaginary part of the frequency response.

There are two problems associated with using the additional negative resistance. All active inductors in the literature use DC cross-coupled negative resistances, which strongly affect the DC biasing of the transistors. The advantage of using the cross-coupled pair is current reuse, but this also means limited tuning range [11]. The other problem is the transistors parasitics. The gate-to-source capacitance of the transistor directly connected to the input node changes the frequency of the inductor. Thus, a way to compensate for this issue is to design the active inductor to have a higher resonant frequency.

Independent tuning is possible [11], but it requires a more complicated circuit and is likely to introduce more noise. It can be achieved by setting the values in Figure 2.10,  $G_{left} = g_{o1} \rightarrow$  "right tuning",  $G_{right} =$  any value, or  $G_{right} = g_{m1}+g_{o1}+g_{o2} \rightarrow$  "right tuning",  $G_{left} =$  any value.

Figure 2.10 Schematic for independent tuning.

In this configuration, the center frequency stays constant while Q changes. The type of tuning that is more appropriate depends on the ratio between the parasitic capacitances.

## **Chapter 3**

#### 3.1 Active VCO

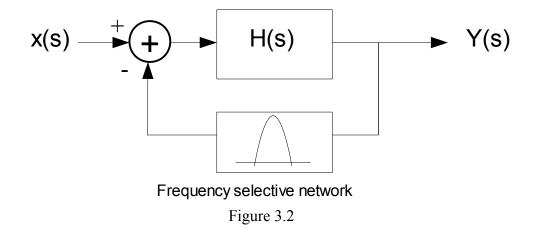

In order for oscillation to start, the Barkhausen stability criteria must be satisfied. For a system configured in feedback (e.g., Figure 3.1), oscillation will occur at the frequency,  $\omega_0$ , where the magnitude of the loop transfer function,  $|H(j\omega_0)| \ge 1$  and the phase of the transfer function is  $\angle H(j\omega_0) = 180^\circ$ . Simply satisfying the Barkhausen criteria does not guarantee oscillation, due to oscillation startup requirements. Hence, typically, the loop gain is chosen to be approximately 2-3 times the required values to guarantee startup [27].

Figure 3.1 Feedback system.

Note that the transfer function, H(s), is designed to produce 180° of phase shift in the forward signal path, and the additional 180° phase shift is achieved through negative feedback; the total phase shift around the loop must be an integer multiple of 360°. In many RF oscillators, a frequency selective network (e.g., LC tank) is included in part of loop as shown in Figure 3.2.

Because the gain of an LC filter rolls off at frequencies outside the resonant frequency, the Barkhausen criteria is only satisfied for systems operating at the resonant frequency. For a lossy LC resonant tank, energy is dissipated in the parasitic resistance associated with the components, hence, a negative resistance is added in parallel with the

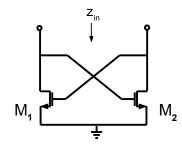

LC tank to compensate for the loss from the tank. In other words, additional energy is provided by an active circuit in order to sustain the oscillation. The negative resistance serves two purposes. First, for oscillation to begin, the circuit needs sufficiently large voltage gain. Second the oscillation amplitude continues to grow until the loop gain reduces at the peak voltage swing of the signal. For a practical circuit, the negative resistance should be two to three times higher than the resistance of the LC tank to account for process variation, supply voltage fluctuation, and temperature drift (PVT) [7]. The most commonly used negative-GM topology for a differential oscillator is the cross-

Figure 3.3 Cross-coupled pairs.

coupled pair, consisting of  $M_1$  and  $M_2$ , as shown in figure 3.3.

The impedance looking in to the cross-coupled pair is given by:

$$Z_{in} = -\frac{2}{g_m} \| \frac{1}{\frac{Cgs}{2} j \omega_0}$$

(3.1)

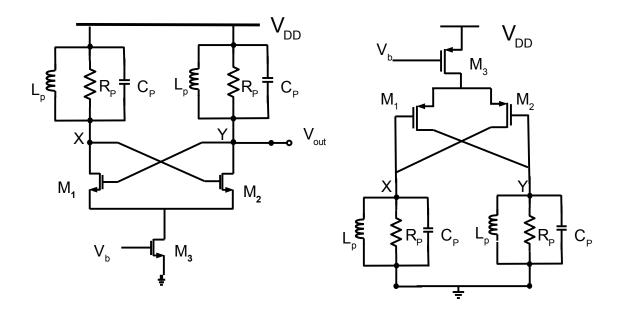

Figure 3.4 (a) and (b) shows the NMOS and PMOS versions of the LC oscillator; the circuits oscillates when the voltage gain is greater than unity,  $g_{m1*}R_p$  or  $g_{m2*}R_p \ge 1$  at resonance.

Figure 3.4 Schematic for NMOS and PMOS voltage-controlled oscillators.

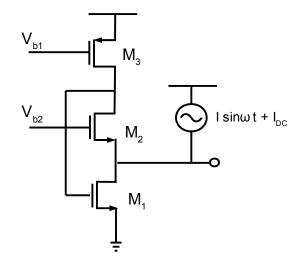

The RLC network can be replaced by an active inductor, as shown in Figure 3.5.

Figure 3.5 schematic for active VCO.

#### 3.2 Voltage Swing

The voltage swing when using a physical inductor can swing above the positive supply voltage in the NMOS version or below ground in the in the PMOS version.

Figure 3.6 Typical output waveforms of PMOS and NMOS VCOs.

The peak-to-peak voltage is given by the product of the tail current and the resistance of the tank, and the average voltage is given by the supply voltage, as shown in Figure 3.6 (a) and (b). The voltage swing is limited only by the cross-coupled pair transistors when they are driven to cutoff. This, however, is not the case for an active inductor VCO. Since there are active devices connected between the supply voltage rails, the transistors consume voltage headroom. Additionally, the active inductor does not behave like a physical inductor under large signals, because energy isn't stored in the magnetic field and it does not respond to instantaneous changes in current like a physical inductor. For the circuit in Figure 3.5, the minimum output voltage of  $V_x$  occurs when  $I_x$  is zero, where  $M_8$  is in cutoff, assuming  $M_1$  and  $M_2$  are in saturation. Ignoring the threshold voltages difference due to body effect and equating the current yields:

$$\frac{1}{2}\mu_{n}C_{ox}\left(\frac{W}{L}\right)_{1}(V_{GSI}-V_{Tn})^{2}=\frac{1}{2}\mu_{n}C_{ox}\left(\frac{W}{L}\right)_{2}(V_{GS2}-V_{Tn})^{2} \quad (3.2)$$

Dividing both side by  $(W/L)_2$ , and replacing  $V_{GS2}$  by  $(V_{b2}-V_{xmin})$ , where  $V_{b2}$  is the bias voltage yields:

$$\sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}} (V_{GSI} - V_{Tn}) = V_{b2} - V_{xmin} - V_{Tn} \quad (3.3)$$

$$V_{xmin} = V_{b2} - \sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}} V_{GSI} + V_{Tn} \left(1 + \sqrt{\frac{(W/L)_{1}}{(W/L)_{2}}}\right) \quad (3.4)$$

because the drain current,  $I_D$ , of  $M_1$ ,  $M_2$  and  $M_3$  are the same,  $V_{GS1}$  can be expressed in term of  $I_D$ ;

$$V_{GSI} = \sqrt{\frac{2I_D}{\mu_p C_{ox} \frac{W_3}{L}} + |V_T|}$$

(3.5)

Additionally, the phase difference between the differential outputs is  $180^{\circ}$ . When V<sub>x</sub> is at its minimum voltage, V<sub>y</sub> is at its maximum. For simplicity, assume M<sub>9</sub> is operating in saturation, and M<sub>7</sub> is operating in triode. This gives:

$$V_{ymax} = V_{DD} - V_{OV9} - V_{DS7}$$

(3.6)

where

$$V_{OV9} = V_{DD} - V_{b3} - |V_T| \quad (3.7)$$

Since M<sub>8</sub> is cutoff, all biasing current is conducted through M<sub>7</sub>:

$$\frac{1}{2}\mu_{p}C_{ox}\left(\frac{W}{L}\right)_{9}V_{OV9}^{2} = \mu_{p}C_{ox}\left(\frac{W}{L}\right)_{7}\left(\left(V_{SG7} - |V_{Tp}|\right)V_{SD7} - \frac{V_{SD7}^{2}}{2}\right)$$

(3.8)

Simplifying the expression yields:

$$\left(\frac{W}{L}\right)_{9} V_{OV9}^{2} = \left(\frac{W}{L}\right)_{7} \left(2(V_{SG7} - |V_{Tp}|)V_{SD7} - V_{SD7}^{2}\right) \quad (3.9)$$

and write the quadratic equation in term of  $V_{\mbox{\scriptsize SD7}}$

$$V_{SD7}^{2} - 2V_{OV7}V_{SD7} + \frac{(W/L)_{9}}{(W/L)_{7}}V_{OV9}^{2} = 0 \quad (3.10)$$

where:

$$V_{OV7} = V_{SG7} - |V_{Tp}| = V_{DD} - V_{OV9} - Vx_{min} - |V_{Tp}| \quad (3.11)$$

$V_{\mbox{\scriptsize SD7}}$  can be solved for:

$$V_{SD7} = \frac{2V_{OV7} \pm \sqrt{4V_{OV7}^2 - 4\frac{(W/L)_9}{(W/L)_7}V_{OV9}^2}}{2} = V_{OV7} \pm \sqrt{V_{OV7}^2 - \frac{(W/L)_9}{(W/L)_7}V_{OV9}^2}$$

(3.12)

Since the transistor is in triode, that means  $V_{OV} > V_{DS}$ , hence the solution that satisfies this condition is chosen:

$$V_{SD7} = V_{OV7} - \sqrt{V_{OV7}^2 - \frac{(W/L)_9}{(W/L)_7} V_{OV9}^2}$$

(3.13)

This shows that as the size of the cross-coupled pair increases, the voltage drop  $V_{SD7}$  decreases.

#### 3.3 Large Signal Analysis

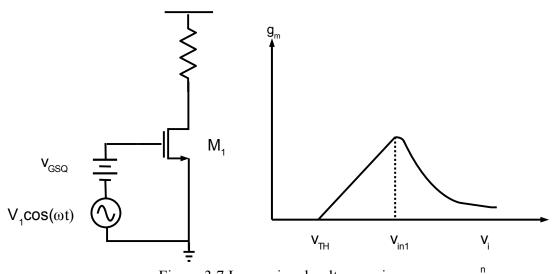

While the equivalent RLC circuit accurately describes the small-signal behavior of the active inductor, it does not apply to the large-signal behavior due to the dependence on the transistors DC bias condition and the maximum signal swing of the active inductor [14-15]. The transconductance decreases as the signal-swing increases, and the resonant frequency decreases as a result. Because the transconductance and capacitance of the transistors are time varying Fourier series analysis is used to examine the large-signal behavior. It should be expected that the large signal  $G_m$ , and  $C_{avg}$  are the weighted averages of the small-signal  $g_m$  and C over the varying DC bias condition with respect to time of the transistors.

Figure 3.7 Large-signal voltage swing.

For an NMOS operating in the saturation region on a small-signal, as shownin Figure 3.7, the large-signal  $G_M$  is the same as the small-signal  $g_m$ . [14] To see this, the drain current in the saturation region is given by:

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \left(\frac{W}{L}\right) V_{T}^{2} \left(\frac{V_{GS}}{V_{T}} - 1\right)^{2} \quad (3.14)$$

where  $V_{GS} = V_{GSQ} + V_1 \cos(\omega t)$ ,  $I_{DSS} = \frac{1}{2} \mu_n C_{ox} (\frac{W}{L}) V_T^2$ , and  $V_{TH} < V_{GS} < V_{in1}$ .

Equation (3.14) can be rewritten as:

$$I_{D} = I_{DSS} \left( \frac{V_{GSQ} + V_{1} \cos(\omega t)}{V_{T}} - 1 \right)^{2} = \frac{I_{DSS}}{V_{T}^{2}} \left( V_{GSQ} + V_{1} \cos(\omega t) - V_{T} \right)^{2}$$

(3.15)

Substitution of  $V_X = V_{GSQ} - V_T$ , and expansion of (3.15) as a Fourier series yields:

$$I_{D} = \frac{I_{DSS}}{V_{T}^{2}} (V_{X}^{2} - 2V_{X}V_{1}\cos(\omega t) + V_{1}^{2}\cos(\omega t)^{2}) \quad (3.16)$$

$$I_{D} = \frac{I_{DSS}}{V_{T}^{2}} ((V_{X}^{2} + \frac{V_{1}^{2}}{2}) - 2V_{X}V_{1}\cos(\omega t) + \frac{V_{1}^{2}}{2}\cos(2\omega t)) \quad (3.17)$$

The DC term is given by

$$I_{o} = \frac{I_{DSS}}{V_{T}^{2}} (V_{X}^{2} + \frac{V_{1}^{2}}{2}) \quad (3.18) \text{The second term is} \quad I_{1} = -2 \frac{I_{DSS}}{V_{T}^{2}} V_{X} V_{1} \quad (3.19)$$

Ignore the higher order term, and the large-signal,  $G_m$ , is defined as

$$G_{m} = \frac{I_{1}}{V_{1}} = -2 \frac{I_{DSS}}{V_{T}^{2}} V_{X} = 2 \frac{I_{DSS}}{V_{T}^{2}} (V_{GSQ} - V_{T}) = k' \frac{w}{L} (V_{GSQ} - V_{T}) = g_{m} \quad (3.20)$$

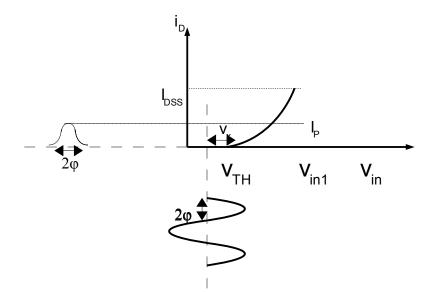

This suggests the large-signal  $G_m$  is the same as the small-signal  $g_m$  as long as the transistor is in saturation. However, if the transistor is switching between cutoff and

saturation, as shown Figure 3.8, the large-signal  $G_m$  will be smaller than the small-signal  $g_m$ .

Figure 3.8 Signal swing between regions of operation

If  $\varphi$  is defined to be the conduction angle  $\cos\varphi = \frac{V_x}{V_1}$ , the Fourier series analysis of

the signal for the fundamental frequency is derived in [14]:

$$I_{1} = \frac{2I_{p}}{\pi} \frac{\frac{3}{4}\sin\varphi + \frac{1}{12}\sin 3\varphi - \varphi\cos\varphi}{(1 - \cos\varphi)^{2}} \quad (3.21)$$

where  $I_P$  is the peak voltage of  $I_D$ :

$$I_{p} = \frac{I_{DSS}}{V_{T}^{2}} (V_{1} - V_{X})^{2} \quad (3.22)$$

The relation of the large signal  $G_m$  is given by

$$G_{m} = \frac{I_{1}}{V_{1}} = \frac{2I_{DSS}(\frac{I_{1}}{I_{p}})}{-2\frac{V_{1}}{V_{T}}} = \frac{g_{mo}(\frac{I_{1}}{I_{p}})}{-2\frac{V_{1}}{V_{T}}} \quad (3.23)$$

Here, it is assumed the transistor is cut off when  $V_{GS}-V_T < 0$ , however a more accurate model such as the EKV model or BSIM model is necessary for the transistor operating in the subthreshold region (e.g., in weak inversion). An empirical expression of  $I_D$  valid for all region of operations proposed by the EKV model is given by [18]:

$$I_{D} = 2N\mu_{n}C_{ox}\left(\frac{W}{L}\right)U_{t}^{2}\left[\ln\left(1+e^{\left(\frac{V_{GS}-V_{T}}{2U_{T}}\right)}\right)\right] = I_{S}\left[\ln\left(1+\exp\left(\frac{V_{GS}-V_{T}}{2U_{T}}\right)\right)\right] \quad (3.24)$$

where N is a device dependent parameter,  $U_t = kT/q$  and  $I_s = 2N\mu_n C_{ox}(W/L)U_t^2$

$$g_{m} = I_{D} \frac{\left| 1 - e^{(-\sqrt{I_{D}/I_{s}})} \right|}{N U_{t} \sqrt{I_{D}/I_{s}}} \quad (3.25)$$

If the voltage swing is large, the large-signal capacitance is given by the weighted average of the small-signal capacitance over one period of oscillation []. Because the capacitance of the transistor is a function of voltage, a time-varying voltage swing causes the capacitance to also be time-varying. The current-voltage relationship is then given by:

$$i = C(v(t)) \frac{dv(t)}{dt} \quad (3.26)$$

The fundamental frequency rms current can be calculated by determining the Fourier coefficient.

$$a_{n} = \frac{1}{\sqrt{2}} \frac{2}{T} \int_{0}^{T} i(t) \cos(n\omega_{0t}) dt \quad (3.27)$$

For an input voltage  $v(t)=Asin(\omega_0 t)+B$ , the large-signal average capacitance is given by:

$$C_{AVG} = \frac{\omega_0}{\pi} \int_0^{\frac{2\pi}{\omega_0}} \left[ C(A\sin(\omega_0 t) + B)\cos(\omega_0 t) \right] \cos(\omega_{0t}) dt \quad (3.28)$$

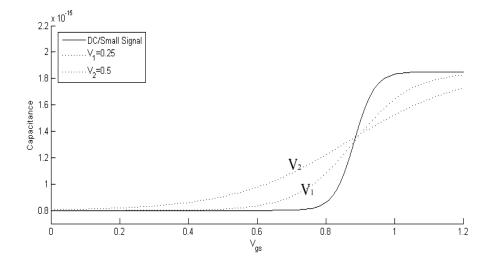

This result can be computed numerically. Figure 3.9 shows the C-V characteristic curve of an inversion mode NMOS. The dotted line represents the average capacitance at a given voltage amplitude.

Figure 3.9 Average Capacitance.

To see the effect of a large-signal amplitude swing on the active inductors resonant frequency, a test current source is connected to the input node as shown in Figure 3.10. The current source consists of a DC bias and a large-signal sinusoid.

For a parallel RLC circuit, the resonance occurs at the frequency where the impedance is maximum. To study the large-signal behavior, the transistors behavior at

Figure 3.10 An Active Inductor with Sine Wave at Its Input.

different operating points should be analyzed.

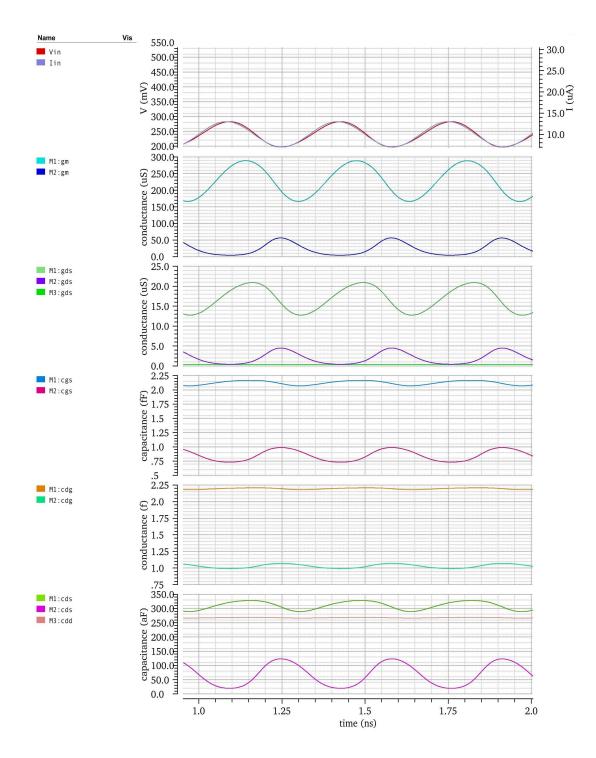

If the amplitude of the sine wave is zero (e.g., DC only), we expect both the transconductances and capacitances to be constant values. As the amplitude grows, all the parameters will change according to the size of the input signal. Figure 3.11 shows how all the transistor parameters change with respect to time. For this example, frequency of the input signal is set to 3GHz and the current amplitude swing is 5  $\mu$ A. The  $g_m$  of  $M_1$  somewhat resembles a sine wave but the  $g_m$  of  $M_2$  is distorted; This is the is the primary cause of the reduction of the resonant frequency. Since  $V_{b2}$  is held at a constant voltage, as the source voltage increases, the transistor overdrive voltage can become negative.

A small signal model has been drawn in Figure 2.2. The output conductances,  $g_o$ , of  $M_1$  and  $M_2$  change similarly to  $g_m$  since they are functions of current. We also expect  $C_{gs2}$  to swing more than  $C_{gs1}$  since the voltage swing is highest at the input node, and the change in  $V_{gs1}$  of  $M_1$  is much smaller due to the negative feedback. Similarly,  $C_{dg2}$  and  $C_{ds2}$  fluctuate more than  $C_{dg1}$  and  $C_{ds1}$  for this reason.  $C_{dd3}$  accounts for all the capacitance looking into the drain of  $M_3$ . Because a very high impedance,  $g_{o3}$ , is seen looking in to the drain,  $C_{dd3}$  remains fairly constant.

Figure 3.11 Time-varying parameters under large-signal

To examine the resonant frequency of the circuit, the "instantaneous resonant frequency"  $\omega_0(t)$  can be numerically computed. After the result is obtained, it can then be compared to the measurement result to decide how the resonant frequency should be estimated. One thing to keep in mind is that, because of the nonlinear capacitance that is dependent on frequency, the frequency being swept will affect the result. Furthermore, time-varying capacitors distort the current waveform [17], so the transconductances are also impacted. Nonetheless, to simplify the analysis, the frequency of the input is maintained unchanged throughout the simulation.

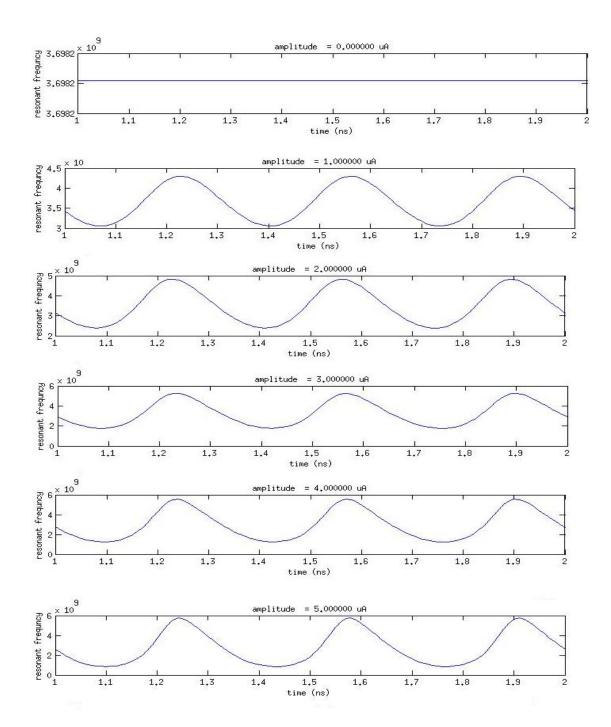

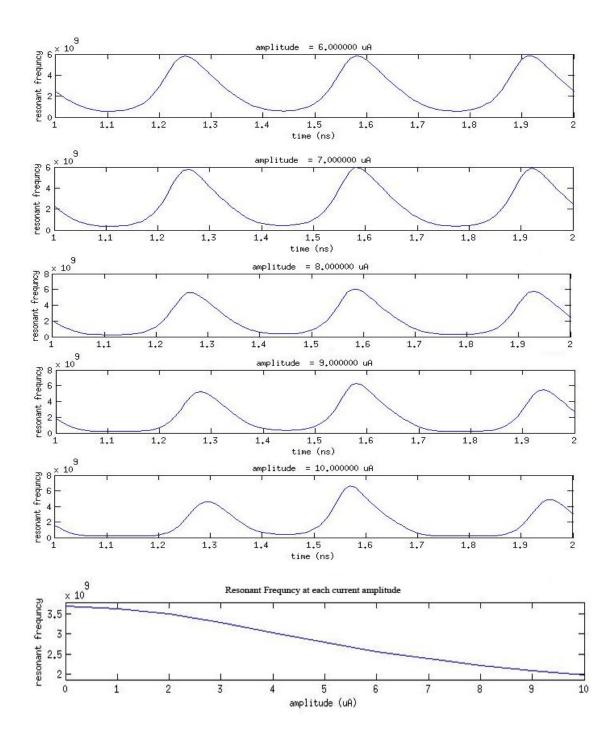

Shown in Figure 3.12 is a plot from the transient analysis in Cadence SpectreRF, and then exported to Matlab to obtain a similar figure to that shown in obtained in Chapter 2. The last figure shows the average resonant frequency over 30 periods at each amplitude. As expected, when the current swing is zero, it is seen that the resonant frequency is time invariant. Between 0 and 1uA, the resonant frequency only reduces by approximately 100 MHz, but it reduces more rapidly as the current amplitude increases. This agrees with the analysis that the large-signal  $G_m$  diverges from the small-signal  $g_m$  as the transistor transitions between different regions of operation. It can be observed that the waveforms appear less like sine waves as the amplitude is increased. The numerical results are tabulated in table 3.1.

| Amplitude (uA) | Sweeping Frequency(3.5GHz) | Sweeping Frequency(3GHz) | Sweeping Frequency(1GHz) | Measurement |

|----------------|----------------------------|--------------------------|--------------------------|-------------|

| 0              | 3.1102467                  | 3.1138655                | 3.1138655                | 3.15        |

| 1              | 3.0717220                  | 3.0732560                | 3.1085358                | 3.06        |

| 2              | 2.9592346                  | 2.9504856                | 3.0907238                | 2.93        |

| 3              | 2.7979444                  | 2.7654732                | 3.0586686                | 2.71        |

| 4              | 2.6132728                  | 2.5487988                | 3.0085847                | 2.56        |

| 5              | 2.4339291                  | 2.3388632                | 2.9334426                | 2.48        |

| 6              | 2.1344696                  | 2.1514546                | 2.8208732                | 2.36        |

| 7              | 2.1188016                  | 1.9900242                | 2.6534550                | 2.16        |

| 8              | 1.9822391                  | 1.8521528                | 2.4187026                | 2.00        |

| 9              | 1.8635719                  | 1.7343766                | 2.1301333                | 1.85        |

| 10             | 1.7456735                  | 1.6355452                | 1.8287985                | 1.59        |

Table 3.1 Resonant frequency for Different Amplitudes and Sweeping Frequencies

Figure 3.12 Resonant frequency vs. time. The frequency of input sine-wave is 3GHz

#### 3.4 Noise

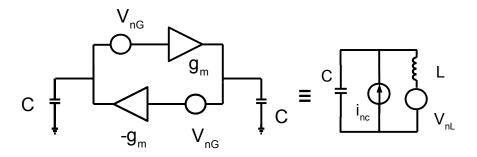

Noise in active inductors is higher than that in spiral inductors because in a passive RLC circuit the noise source is derived mainly from the parasitic damping resistor, whereas in an active inductor, the thermal noise generated from the MOS Transistor channel contributes most of the noise [24]. To see this, a gyrator-C inductor, shown in Figure 3.13, consists of two anti-parallel transconductances,  $g_m$ .  $V_{nG}$  is the equivalent noise voltage  $4kT\gamma/g_m$ .

Figure 3.13 Equivalent noise circuit

The noise equivalent circuit is then transformed to the equivalent model RLC circuit with series noise voltage  $V_{nL} = V_{nG}$  and shunt noise current  $I_{nc} = g_m V_{nG}$ . This implies that unlike a passive resonator whose L and C are ideally noiseless, active LC circuits are noisy due to ohmic conductance. At resonant frequency the noise of the active inductor is at least 2Q higher than its passive counterpart. [13] Therefore, the mean-square noise voltage of the active inductor is 2QkT/C instead of kT/C.

The noise analysis has been completed in [9]. The intrinsic quality factor Qo is defined :

$$Q_0 = \frac{1}{g_{m2}} \sqrt{\frac{C_P}{L_{eff}}}$$

(3.29)

where  $C_P$  and  $L_{eff}$  are defined in (2.6) and (2.9) respectively. The enhance quality factor  $Q_n$  when the negative resistance is included is defined as follows:

$$Q_{n} = \frac{1}{g_{m2} - g_{nic}} \sqrt{\left(\frac{C_{P} + C_{nic}}{L_{eff}}\right)} \quad (3.30)$$

where  $C_{nic}$  is the parasitic capacitance of the cross-coupled pairs. The total mean-square noise is given by the following:

$$\overline{V_{n,tot}^{2}} = \sqrt{\frac{C_{P}}{C_{P} + C_{nic}}} \frac{Q_{n}}{Q_{0}} \frac{kT}{C_{gg2}} \frac{\xi C_{gg2} + \gamma Q_{0}^{2} (C_{gg1} + C_{gg2} + C_{nic})}{C_{gg2} + C_{nic}}$$

(3.31)

where  $\gamma$  is the thermal channel coefficient of the MOS transistors and  $\xi$  is the noise coefficient for the cross-coupled pairs [25]. Expression 3.31 shows that a large C<sub>gs2</sub> reduces the output noise at the cost of reducing the resonant frequency. A higher quality factor of the cross-coupled pairs boosts the noise floor.

An optimum quality factor exists and is given by the following:

$$Q_{0,opt} = \sqrt{\frac{\xi C_{gs2}}{\gamma (C_{Ggs2} + \gamma C_{gs1} + C_{gs2} + C_{nic})}} \quad (3.32)$$

#### 3.5 Oscillator Phase Noise

Noise perturbs the amplitude and phase of an oscillator. However, in most RF systems, the output of an oscillator is amplitude limited, hence, usually only phase noise is considered. Phase noise in oscillator is expressed in units of "decibels below the carrier per hertz," or dBc/Hz at a particular offset frequency [26].

#### 3.5.1 Injection Locked Active VCO

There are methods to improve the phase noise of an active inductor based oscillator.

The injection locked active inductor oscillator can have a lower phase noise level than that of the external injecting signal [15]. A numerical example of a free running active VCO that resonates at 2.4 GHz and consumes 1.1mW is given in [15]. It has a phase noise of -70dBc/Hz at 1 MHz frequency offset. With the injection of a sinusoidal signal, the phase noise of the active VCO improves to -118dBc/Hz at 1 MHz frequency offset.

#### 3.5.2 Constant Q active Inductor

From the large-signal analysis, it is shown that the self-resonant frequency and quality factor all vary with signal swing. If the mean quality factor is defined to be [16]:

$$Q_m(\omega_0) = \frac{1}{I_{max} - I_{min}} \int_{I_{max}}^{I_{min}} Q(\omega_0, J) dJ \quad (3.32)$$

where  $I_{max}$  and  $I_{min}$  are the maximum and minimum of the reuse-current bias, respectively. The closed loop transfer function of the oscillator is offset from the oscillation frequency by  $\Delta \omega$ , where  $\Delta \omega \ll \omega_0$ , is given by:

$$|H_{C}(\omega_{0}+\Delta\omega)|^{2}\approx\frac{1}{4Q^{2}(\omega_{0})}\left(\frac{\omega_{0}}{\Delta\omega}\right)^{2}$$

This implies that the reduction of quality factor has a negative impact on the phase noise. A constant Q active inductor (shown in Figure 3.14) is proposed based on the Wu inductor [16]. For a 4GHz LC- tanks oscillator, it is able to achieve -118dBc/Hz at 1Mhz. The total power consumption is 23.4mW.

Figure 3.14 A constant Q active inductor.

### Chapter 4

#### 4.1 Active Inductor Design

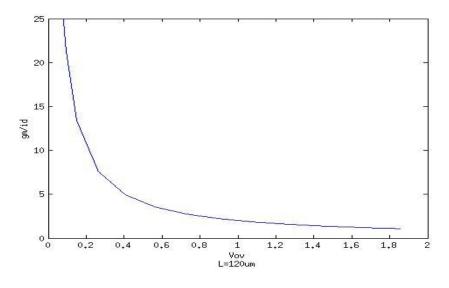

The  $g_m/I_D$  method is the chosen method used to design the transistors, because hand calculation methods usually assume the transistors operate in the strong inversion region and neglect short-channel transistor effects. In weak to moderate inversion, transistors operate with smaller overdrive voltage,  $V_{ov}=V_{gs}-V_T$ [20].

$$\frac{W}{L} = \frac{g_m}{\mu C_{ox} V_{ov}} \quad (4.1)$$

With transistor length, L, and  $g_m$  fixed, a smaller  $V_{ov}$  leads to larger transistor width, and hence larger capacitance. Hence, it is not a good design parameter.[21] As was previously stated, the formulas describing the square law operation of the MOS device provide poor estimated operating points for deep sub-micron devices, the design methods should be based on accurately extracted I-V characteristic plot of the transistor from a DC simulation using a BSIM transistor model. The so called gm/I<sub>D</sub> methodology, which is the ratio of of the transconductance,  $g_m$  to the DC drain current, I<sub>D</sub> is a tabular method that does not depend on the devices physical dimension, but rather the current density,  $I_{dw}=I_d/W$ . Additionally, the parasitic capacitance is proportional to the width of the transistor, hence the corresponding capacitance can be found using a lookup table for a given  $I_{dw}$  value if we know what the length of the device is. Thus, the first step in design is to decide the desired length of the transistor, then bias them properly according to the proper current density. The goal here is to develop a Matlab script that provides good estimation for a given design specification, because there are many variables to design and likely require multiple iterations before arriving at a final design.

For brevity, only the NMOS version of the active inductor is considered in this example because of its higher transition frequency for the same  $g_m/I_d$ , however, a PMOS design can be produced in a similar fashion.

For the following example,  $g_m$  is the small-signal transconductance,  $g_o$  is the small signal output conductance, given by:

$g_o = I_D / V_A$

where  $V_A$  is the Early voltage. The transition frequency is defined as  $\omega_T$  and is a "figure of merit" (FOM) of the switching speed of a transistor. Beyond the transition frequency the transistor cannot fully charge and discharge its intrinsic capacitance each cycle and, hence, stops acting like voltage dependent current source. The transition frequency is an FOM that indicates the quality of the transistor since we want large  $g_m$  but small width which means small  $C_{gs}$ . Additionally it is desired for  $g_m$  to be large while keeping  $I_D$  small, for increased energy efficiency.

The  $g_m/I_D$  relationship can be derived as follows:

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{\partial \ln I_D}{\partial V_G} = \frac{\partial \left[ \ln \left[ \frac{I_D}{\left( \frac{W}{L} \right)} \right] \right]}{\partial V_G} \quad (4.2)$$

Figure 4.1 (a)  $V_{ov}$  vs.  $g_m/I_d$

The derivative of (4.2) is maximum when the transistor is in weak inversion, implying that the best transconductance efficiency occurs in the subthreshold region. Figure 4.1 (a) shows the V<sub>ov</sub> vs.  $g_m/I_d$  when V<sub>ds</sub> = 0.75v. Figure 4.1 (b) shows  $g_m/I_d$  vs.  $I_d/W$ .

Figure 4.1 (b)  $g_m/I_d$  vs.  $I_d/W$

A lookup table that contains all the necessary small signal parameters is created over a multiple dimensional space consisting of bias point (e.g., Vgs and Vds) and physical dimension (e.g., L) of the circuit in figure 4.2 All data for a family of transistors is stored as data to a file. Such a file can easily be accessed using lookup table techniques using analytical software (e.g., Matlab).

Figure 4.2 Schematic for creating technology file

The following is a catalog of the lookup functions that were developed for sizing transistors along with a description of the function. Because the lookup functions interpolate data from a discrete table, the accuracy of the lookup table depends on the spacing of the points used to collect the data. A full Matlab script for designing an active inductor and active VCO using such lookup tables can be found in appendix B.

Table 4.1 List of look up functions

| gmid | lookup_gmid_3d(techfile,device,length,vds,idw) |

|------|------------------------------------------------|

| id/w | lookup_idw_3d(techfile,device,length,vds,gmid) |

-look up gmid and id/w. All the lookup functions share the same format. Where *techfile* is the path to the lookup table, *device* is the name of the device, for example, 'pfet' and 'nfet'. *length* is the length of the transistor in nm. *vds* is the voltage across drain

and source of the devie. The last field is either in  $gm/I_D$  or  $I_D/W$ .

| V <sub>ov</sub> | lookup_vov_3d(techfile,device,length,vds,gmid) |

|-----------------|------------------------------------------------|

| V <sub>GS</sub> | lookup_vgs_3d(techfile,device,length,vds,gmid) |

-look up  $V_{OV}$  or  $V_{GS}$ .

| ft lookup_ft_3d(techfile,device,length,vds,gmid) |  |  |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|--|--|

|                                                  |  |  |  |  |  |  |  |

-look up transition frequency, it should be larger than the resonant frequency of the

inductor.

go

-look up the output conductance.

| Cgs | lookup_cgswVsIdw_3d(techfile,device,length,vds,idw)*W*1e6/20*1e-15                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cgg | lookup_cggwVsIdw_3d(techfile,nDevice,Ln2,vdsn2,idwn2)*wn2*1e6/20*<br>1e-15                                                                                                                         |

| Cdd | (lookup_cdwVsIdw_3d(techfile,nDevice,Ln1,vdsn1,idwn1)+lookup_covlgdwV<br>sIdw_3d(techfile,nDevice,Ln1,vdsn1,idwn1)<br>-lookup_cdgwVsIdw_3d(techfile,nDevice,Ln1,vdsn1,idwn1))*wn1*1e6/20<br>*1e-15 |

| Cgd | lookup_cgdwVsIdw_3d(techfile,nDevice,Ln1,vdsn1,idwn1)*wn1*1e6/20*1e-<br>15                                                                                                                         |

| Cds | lookup_cdswVsIdw_3d(techfile,nDevice,Ln1,vdsn1,idwn1)*wn1*1e6/20*1e-                                                                                                                               |

|     | 15                                                                                                                                                                                                 |

- There are several functions for different parasitic capacitances. W is the width of the transistor, it is divided by 20 because the transistor used for creating the look up table have the width of 20u. The unit is in femto-farad (fF). Cgg is the total capacitance looking into gate. Cdd is the total capacitance looking into drain. Note that Cdd takes a more complex form due to the model used in cadence.

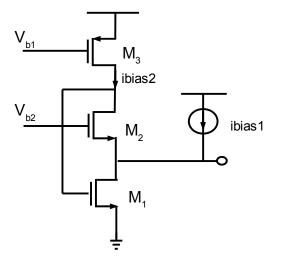

Figure 4.3 Active inductor

With the  $g_m/I_D$  method, the active inductor can now be designed. The schematic is shown in Figure 4.3. The supply voltage is set to  $V_{DD}$ .  $V_{b2}$  is chosen to be high enough so it can turn on  $M_2$ . It should be reasonable value as it will affect the  $V_{DS}$  of M1, as well as the large signal behavior. The  $V_{DS}$  of the transistors can't be determined exactly, so it would need to be estimated based on previous experience. A good starting point would be determining the bias currents. Ibias1 is designed to be much larger than ibias2, so set ibias1 = 10\* ibias2. Next, gm/I<sub>D</sub> of M<sub>1</sub> need to be determined. Choosing (gm/I<sub>D</sub>)<sub>1</sub> to be 15. gm of M<sub>1</sub> can be calculated.

>>gm1=gmid1 \* (ibias1+ibias2);

To determine the value of  $V_{GS1}$ ,

>>Vgs1=Lookup\_vgs\_3d(techfile,nDevice, Ln1, Vdd/2, gmid1);

$V_{DS1}$  is chosen to be Vdd/2 since the exact value  $V_{DS1}$  cannot be determined beforehand, but this won't affect the result too much.

$(I_D/W)_1$  is found to be

>> idwn1=Lookup\_idw\_3d(techfile, nDevice, Ln1, Vdd/2, gmid1);

and the width of the transistor is then

>>wn1=(ibias1+ibias2)/idwn1;

Once,  $(I_D/W)_1$  is known, width of M1, and all the parasitic capacitance can be calculated. All the output conductances and their parasitic capacitances can be obtained by using the function listed in Table 4.1.  $V_{DS}$  of  $M_3$  is just Vdd- $V_{GS1}$ . Since  $M_3$  acts as a current source and is not changed throughout the design. A fixed width is chosen, and the  $(I_D/W)_3$  ratio is obtained.

#### >> gmid3=lookup\_idw\_3d(techfile,device,length,vds,idw);

>> Vgs3= Lookup\_vgs\_3d(techfile,pDevice, Lp3, Vdd-Vgs1, gmid3);

Similarly, all other parameters of M<sub>3</sub> are calculated by using the corresponding functions.

The body effect is not taken into account when tabulating the tech file as it adds a lot more complexity,  $g_{mb}$  can be included in  $g_m$  by multiplying a factor here. The gate to source voltage of  $M_2$  cannot be easily determined since the higher threshold voltage increase the overdrive voltage for the same  $gm/I_D$  ratio. Thus, an estimation is used for  $V_{DS2}$ , then relate  $V_{DS1}$  and  $V_{DS2}$  as follows:  $V_{DS1} = V_{GS1} - V_{DS2}$ .

It is possible to write a while loop to sweep the  $gm/I_D$  of  $M_2$ , for simplicity, a value of  $(gm/I_D)_2$  is picked.

>> idwn2=Lookup\_idw\_3d(techfile, nDevice, Ln1, vdsn2, gmid2);

and the width of the transistor is then

>>wn2=(ibias2)/idwn2;

Once again, the functions from Table 4.1 to are used to compute the output

conductance and parasitic capacitances. With all the parameters determined, inductance value, resonant frequency and quality factor can be calculated by using the equations in chapter 2.

#### 4.2 Active VCO Design

To use the active inductor in the active VCO, the resonant frequency needs to be designed at a much higher frequency than the VCO operation frequency. This is due to large-signal behavior phenomena as explained in the previous chapter. The cross-coupled pair must provide enough negative resistance cancel out the resistance looking into the active inductor:

$>> R=\max(\operatorname{real}(Z));$

where Z is the impedance of the active inductor and is a function of frequency. The  $g_m$  of the cross-coupled pair should be designed to be twice the size of the input resistance, *R*:

>>

$$g_m = (1/R) * 2;$$

The bias current is  $i_{bias1}$ , hence  $g_m/I_D$  is then:

$$>> g_m/I_D = g_m/i_{biasl}$$

The width, W, can be determined by looking up  $I_D/W$ :

```

>> idw=Lookup_idw_3d(techfile, pDevice, Ln1, [], gmid);

```

$>> W = i_{biasl}/idw;$

likewise, all the parasitic capacitances and output resistance can be calculated using similar lookup tables.

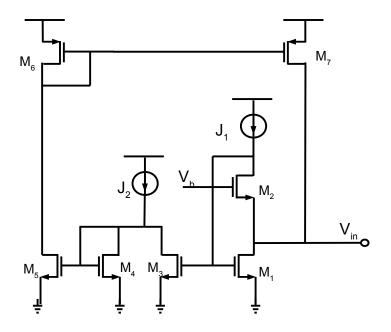

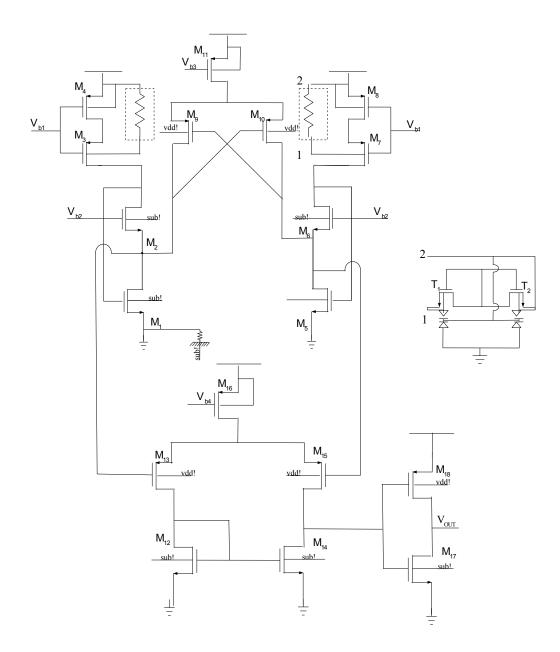

Figure 4.4 shows the schematic of the complete design. The parameters and the bias voltages are given in Table 4.2. Some modifications are made to the current source to improve its output impedance. Stacked transistors and a pseudo-resistor [22] are used to increase the output resistance and the resistance of the substrate. The resistance of the pseudo-resistor is greater than  $1M\Omega$ . This configuration improves phase noise because

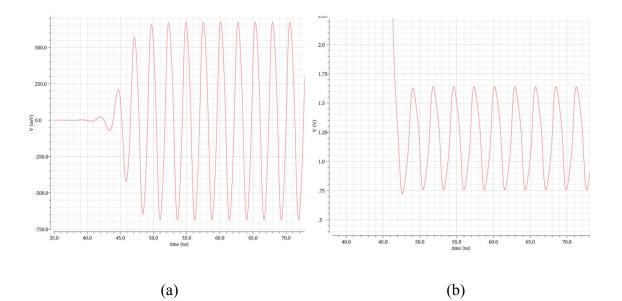

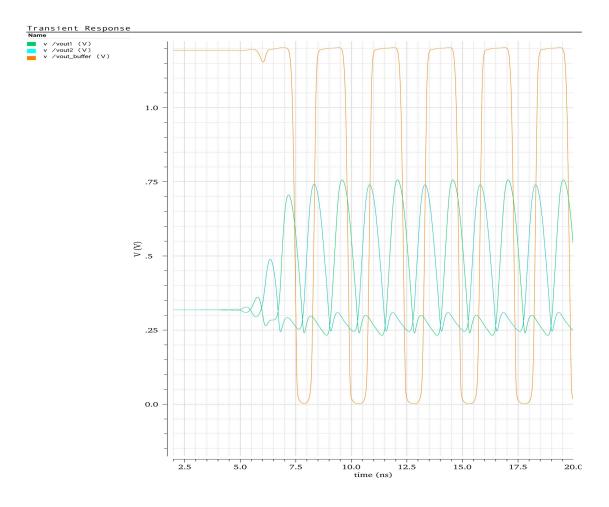

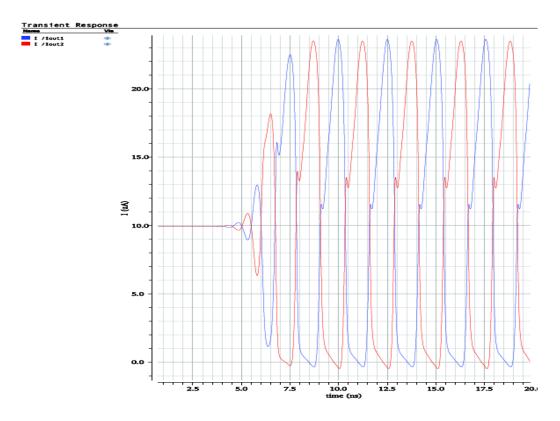

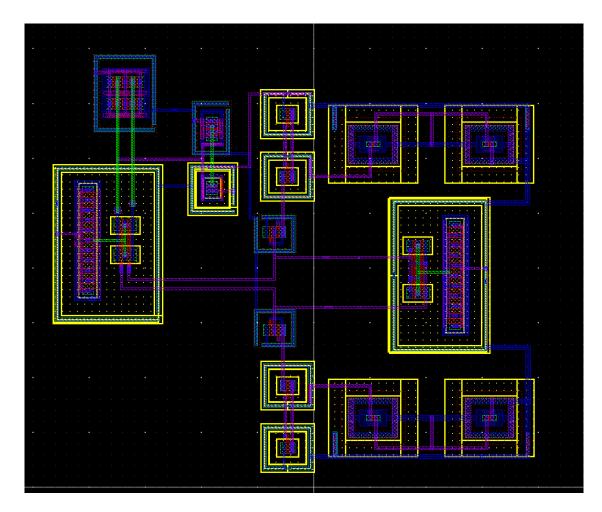

the fluctuation of voltage swing not only affects the DC operating points, but also changes the junction capacitance. Replica-biasing can also be used [23]. The Active VCO oscillates at 400MHz. The total power consumed is  $55.4\mu$ W. Phase noise is -77dbc/Hz @1MHz offset. Figure 4.5 (a) and (b) show the outputs of the VCO as well as that of the buffer. The tail transistor spends part of its time operating in the triode region; thus the tail current does not stay constant. This implies that the drain-to-source voltage of the NMOS cross-coupled pair can reduce significantly, resulting in a large reduction in their drain current, as shown in Figure 4.5 (b). This indicates that the Active VCO is operating in a voltage-limited regime. [19] The use of buffers reduces the overall frequency due to the additional capacitance, however, they increase the voltage swing. The reduction in resonant frequency can be compensated by increasing the bias current. The completed layout is shown in Figure 4.6

Figure 4.4 Schematic for Active VCO

| $M_1 \sim M_8$                   | 1μ                  | $T_1, T_2$       | 480n | M <sub>12</sub> ,M <sub>14</sub> | 4u   | M <sub>17</sub> | 1u   | $V_{b1}$ | 839mV |

|----------------------------------|---------------------|------------------|------|----------------------------------|------|-----------------|------|----------|-------|

|                                  | 240n                |                  | 120n |                                  | 240n |                 | 120n | $V_{b2}$ | 650mV |

|                                  |                     |                  |      |                                  |      |                 |      |          |       |

| $M_9, M_{10}$                    | 2μ                  | M <sub>11,</sub> | 10u  | M <sub>16</sub>                  | 1u   | $V_{\text{DD}}$ | 1.2V | $V_{b3}$ | 810mV |

| M <sub>13</sub> ,M <sub>15</sub> | $\frac{2\mu}{240n}$ | M <sub>16</sub>  | 480n |                                  | 120n |                 |      | $V_{b4}$ | 850mV |

|                                  |                     |                  |      |                                  |      |                 |      |          |       |

Table 4.2 Transistors Sizing of Active VCO

Figure 4.5 (a) Output voltage of Active VCO

Figure 4.5 (b) Output current of active VCO

Figure 4.6 Complete layout.

## **Chapter 5**

#### 5.1 Conclusion and Further Work

The focus of this thesis is on a structured design approach for gyrator-C active inductors. A Matlab<sup>TM</sup> script is developed based on the  $g_m/I_D$  methodology, and a low power active VCO is designed. The Wu active inductor topology is used for demonstration, however, with modifications made to the biasing currents, this approach can be applied to other gyrator-C based active inductors.

The large-signal behavior has been studied and discussed extensively throughout the thesis and the active VCO is carefully examined. It is shown that the resonant frequency of the active inductors is reduced under large signal, and such change needs to be compensated by adjusting the biasing points through many iterations. While active inductors have considerably more noise than physical inductors, they are useful when noise isn't the main concern. Furthermore, there are more complicated feedback circuit that can be employed to reduce noise.

Other possible applications for the active inductors includes using the active inductor as an RF choke in low-power power amplifier. Because the transient response of the active inductors are limited by the bandwidth and by power supply future work will be to reduce the sensitivity to large-signal swings.

# References

[1] A. Thanachayanont and A. Payne. "CMOS floating active inductor and its applications to band-pass filter and oscillator design". IEE Proceedings, Part G -Circuits, Devices, and Systems, 147(1):42-48, Feb. 2000.

[2] A. Thanachayanont. "A 1.5-V high-Q CMOS active inductor for IF/RF wireless applications". In Proc. IEEE Asia-Pacific Conf. Circuits Syst., volume 1, pages 654-657. 2000.

[3] L. Lu and Y. Liao. "A 4-GHz phase shifter MMIC in 0.18-µmCMOS". IEEE Microwave and Wireless Components Letters, 15(10):694–696, Oct. 2005.

[4] R.Weng and R. Kuo. "An  $\omega o$ -Q tunable CMOS active inductor for RF bandpass filters". In Proc. Int'l Symp. Signals, Systems, and Electronics, pages 571–574, Aug. 2007.

[5] A. Tang, F. Yuan, and E. Law. "A new CMOS active transformer QPSK modulator with optimal bandwidth control". IEEE Trans. on Circuits Syst. II., 55(1):11-15, Jan. 2008.

[6] A. Tang, F. Yuan, and E. Law. "CMOS class AB active transformers with applications in LC oscillators". In IEEE Int'l Symp. Signals, Systems and Electronics, pages 501-504,

Montreal, Aug. 2007.

[7]F. Yuan, CMOS Acitve Inductors and Transformers: Principle, Implementation, and Applications, Springer, 2008.

[8]F. Yuan, "CMOS active Transformers", Circuits, Device & Systems, IET, vol.1, pp 494-508, Dec. 2007.

[9]Y.Wu, Xi.Ding, M.smail,"Rf bandpass filter design based on cmos active inductors" ieee transactions on circuits and systems—ii: analog and digital signal processing, vol. 50, no. 12, december 2003

[10] Y. Wu, el al "A novel cmos fully differential inductorless rf bandpass filter" ISCAS 2000 - IEEE International Symposium on Circuits and Systems, May 28-31, 2000

[11] C. Andriesei and L. Goras, "On the Tuning Possibilities of an RF Bandpass Filter with Simulated Inductor", International Semiconductor Conference, CAS 2007, vol. 2, [12] C. Andriesei and L. Goras, "Negative Resistance Based Tuning of an RF bandpass Filter" Circuits and Systems for Communications, 2008.

[13] A. Abidi, "Noise in active resonators and the available dynamic range," IEEE Trans. Circuits Syst.-I, vol. 39, pp. 296–299, Apr. 1992.

[14]G. Gonzalez, *Foundations of Oscillator Circuit Design*, Artech House Publishers, Dec 2006.

[15]Y. Zhou "A comparative study of lock Range of Injuection-Locked Acitve Inductor Osillators. Circuits and Systems (MWSCAS), Aug. 2010.

[16]A. Tang A F. Yuan A E. Law. A new constant-Q CMOS active inductor with applications to low-noise oscillators, Oct, 2008

[17]R. Lee Bunch, *Large signal analysis of MOS varactors in CMOS -G<sub>m</sub> LC VCOs*, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 8, AUGUST 2003

[18]C.C.Enz, F.Krumenacher, and E.A.Vittoz," A Basic Property of MOS Transistor model valid in all regions of operation amd dedicated to low-voltage and low-current applications", Analog Integrated Circuits Signal Process., Vol.8, pp83-114,1995

[19]Design Issues in CMOS Differential *LC* Oscillators *IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 34, NO. 5, MAY 1999*

[20]gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-ion- insulator micropower OTA. IEEE Journal of Solid State Circuits. Vol. 31, pp 1314-1319, Sept. 1996.

[21]D. Flandre, A. Viviani, J.-P. Eggermont, P. Jespers,"Improved synthesis of regulated-cascode gain-boosting CMOS stage using symbolic analysis and gm/ID methodology", *IEEE Journal of Solid-State Circuits* (SpecialIssue on 22nd ESSCIRC conference), 32 (1997) 1006-1012.

[22]M.-T. Shiue, K.-W. Yao and C.-S.A. Gong. "Tunable high resistance voltagecontrolled pseudo-resistor with wide input voltage swing capability" Electronics Letters .vol 47, Issue: 6 pp 377 - 378 March 17 2011 [23] D. DiClemente and F. Yuan. "Current-mode phase-locked loops : a new architecture". *IEEE Trans. on Circuits Syst. II.*, 54(4):303–307, Apr. 2007.

[24] A. Abidi, "Noise in active resonators and the available dynamic range," *IEEE Trans. Circuits Syst.-I*, vol. 39, pp. 296–299, Apr. 1992.

[25]Kuhn, W.B., "Dynamic range of high-Q OTA-C and enhanced-Q LC RF bandpass filters," in *Proc. IEEE Midwest Circuits Systems*, 1995, pp. 767–771.

[26]Thomas H. Lee, Oscillator Phase Noise: A Tutorial IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 35, NO. 3, MARCH 2000

[27] B. Razavi. Design of analog CMOS integrated circuits. McGraw-Hill, Boston, 2001.

# Appendix A: The Derivation of equations 2.2~2.5

restart

with(CodeGeneration);

[C, Fortran, IntermediateCode, Java, LanguageDefinition, Matlab, Names, Save, Translate, (1) VisualBasic]

$Z_{\rm in} = \frac{\left(b_1 \cdot s + b_0\right)}{s^2 + 2 \ a \cdot s + w_0^2}, \text{ where } w_0^2 \text{ is the resonant frequency },$

capacitance at the current source can be included in Cgs1. gm2 = gm2 + gmb2

#transister as current source

$$Y := gol + \frac{gml \cdot (gm2 + go2)}{go3 + s \cdot Cgsl + go2} + s \cdot Cgs2 + gm2 + go2 - \frac{go2 \cdot (gm2 + go2)}{go3 + s \cdot Cgsl + go2};$$

$$z := simplify(\frac{1}{Y})$$

$$(go3 + s Cgs1 + go2) / (gol go3 + gol s Cgsl + gol go2 + gm1 gm2 + gm1 go2 (1.1))$$

$$+ s Cgs2 go3 + s^2 Cgs2 Cgsl + s Cgs2 go2 + gm2 go3 + gm2 s Cgsl + go2 go3 + go2 s Cgsl)$$

$$x := sort \left( \frac{collect}{(Cgsl \cdot Cgs2, s)}, (s, gml, gm2, gol, go2, Cgssl, Cgs2, ] \right)$$

$$\left( \frac{-s}{Cgs2} + \frac{go2 + go3}{Cgs1 Cgs2} \right) / (s^2 (1.2))$$

$$+ \frac{(gm2 Cgsl + gol Cgsl + go2 Cgsl + go2 Cgsl + go2 Cgs2 + go3 Cgs2) s}{Cgsl Cgs2}$$

$$+ \frac{gml gm2 + gml go2 + gol go2 + go3 gm2 + go3 gol + go3 go2}{Cgsl Cgs2} \right)$$

Mulab(x)

$$cg = (s / Cgs2 + (go2 + go3) / Cgs1 / Cgs2) / (s^2 + go3 * Cgs2) * s / (cgs1 + go3 * go2) / Cgs1 / Cgs2);$$

$$\#for anideal current source go3 * go1 + go3 * go2) / Cgs1 / Cgs2 ; 0 (1.1)$$

$$z := simplify(\frac{1}{Y})$$

$$(s Cgsl + go2) / (gol s Cgs1 + gol go2 + gm1 gm2 + gm1 go2 + s^2 Cgs2 Cgs1 (1.12))$$

$$+ s Cgs2 go2 + gm2 s Cgs1 + go1 go2 + gm1 go2 + gm1 go2 + s^2 Cgs2 cgs1 (1.12)$$

$$x := sort \left( \frac{collect \left( \frac{numer(z)}{(Cgs1 \cdot Cgs2)}, s \right)}{collect \left( \frac{denom(z)}{(Cgs1 \cdot Cgs2)}, s \right)}, [s, gm1, gm2, go1, go2, Cgs1, Cgs2, ] \right) \right)$$

$$\left( \frac{s}{Cgs2} + \frac{go2}{Cgs1 Cgs2} \right) / \left( s^2 + \frac{(gm2 Cgs1 + go1 Cgs1 + go2 Cgs1 + go2 Cgs2) s}{Cgs1 Cgs2} \right)$$

$$+ \frac{gm1 gm2 + gm1 go2 + go1 go2}{Cgs1 Cgs2} \right)$$

Matlab(x)

$$cg0 = (s / Cgs2 + go2 / Cgs1 / Cgs2) / (s^2 + (gm2 * Cgs1 + go2 * Cgs1 + go2 * Cgs1 + go2 * Cgs1 + go2 * Cgs2) + s / Cgs1 / Cgs2 + (gm1 * gm2 + gm1 * go2 + go1 * go2) / Cgs1 / Cgs2);$$

A more complex model used in simulation, including the cross-coupled pairs. (- $g_m$  and its parasitic capacitance)

$$\begin{split} Y &:= gol + gml \cdot \frac{(gm2 + go2 + s \cdot Cgd1)}{go3 + s \cdot Cdd3 + s \cdot Cgs1 + s \cdot Cgd1 + go2 + s \cdot Cdg2} + s \cdot Cgs2 + gm2 + go2 + s \cdot Cdg1 - (go2 + s \cdot Cdg1) \cdot \frac{(gm2 + go2 + s \cdot Cgd1)}{go3 + s \cdot Cdd3 + s \cdot Cgs1 + s \cdot Cgd1 + go2 + s \cdot Cdg2} + 2 \cdot (s \cdot Cds1 - gm + s \cdot Cds + 2 s \cdot Cdg + go) \\ z &:= sort\left(simplify\left(\frac{1}{Y}\right), s\right) \end{split}$$

after some rearranging the term, and put into the form given for  $Z_{\rm IN},$  we get  $Z_{\rm IN}{=}$

(

$$((Cgs1 + Cgd1 + Cdg2 + Cdd3) s) | (Cgs1 Cgs2 + 4 Cdg Cgs1 + Cdg1 Cgs1 + 2 Cds Cgs1 + 2 Cds1 Cgs1 + Cgd1 Cgs2 + Cdd3 Cgs2 + Cdg2 Cgs2 + 4 Cdg Cdg2 + Cdg1 Cdg2 + Cdg1 Cdd3 + 2 Cds1 Cdd3 + 2 Cds1 Cdg2 + 2 Cds Cdd3 + 2 Cds Cgd1 + 4 Cdg Cgd1 + 2 Cds Cdg2 + 4 Cdg Cdd3 + 2 Cds1 Cgd1) + (go2 + go3) | (Cgs1 Cgs2 + 4 Cdg Cgs1 + Cdg1 Cgs1 + 2 Cds Cgs1 + 2 Cds1 Cgs1 + 2 Cds1 Cgs1 + 2 Cds1 Cgs2 + Cdg2 Cgs2 + 4 Cdg Cdg2 + Cdg1 Cdg2 + Cdg1 Cdg3 + 2 Cds1 Cdd3 + 2 Cds1 Cdd3 + 2 Cds1 Cdg2 + 2 Cds1 Cdg2 + 2 Cds1 Cdd3 + 2 Cds1 Cdg2 + 2 Cds Cdd3 + 2 Cds1 Cdg2 + Cdg1 Cdg3 + 2 Cds1 Cdg2 + 2 Cds Cdd3 + 2 Cds1 Cdg1 + 4 Cdg Cgd1 + 2 Cds Cdg2 + 4 Cdg Cdg1 + 4 Cdg Cgd1 + 2 Cds Cdg2 + 4 Cdg Cdg2 + 2 Cds Cdd3 + 2 Cds1 Cdg2 + go1 Cgs1 + 2 Cds Cdg2 + 4 Cdg Cdg2 + 4 Cdg Cgd1 + 2 Cds Cdg2 + 4 Cdg Cdd3 + 2 Cds1 Cdg1)) / (s^2 + ((gm2 Cgs1 + go1 Cgs1))) / (s^2 + ((gm2 Cgs1 + go1))) / (s^2 + ((gm2 Cgs1 + go1)))$$

Function "Matlab(x)" is used to to export  $Z_{in}$  into matlab.

# Appendix B: Matlab Code for Calculation of Active Inductor and VCO

clear all close all clc

% This m script can be used to design an active inductor for a desired Q % and resonant frequency with no control over the actual value of % inductance. The schematic for the inductor is given as follows: % % % Vdd % % % % vb1 --o||\_\_\_\_ M3 % % % -----% %vb2--|--||\_\_ M2 % % % % % \_\_\_\_\_M1 ---|| % % % ----- Vgnd % \_\_\_ % -%

load /ece/grad/symin/matlab/ibm8rfTechfile.mat techfile = '/ece/grad/symin/matlab/ibm8rfTechfile.mat';

nDevice='nfet'; % device name pDevice='pfet'; Ln1 = 240; % Length of M1 in nm. Ln2 = 240; % Length of M2 in nm Lp3 = 240; %Length of M3 in nm

gmidn1=18; gmidn2=12;

Vdd=1.2;

vdsp3=800e-3; %vds of M3 Vgs1=lookup\_vgs\_3d(techfile,nDevice,Ln1,Vdd-vdsp3-.1,gmidn1);

Vgs2=lookup\_vgs\_3d(techfile,nDevice,Ln2,0.3,gmidn2);

Vb2=600e-3 vdsn2=Vgs1-(Vb2-Vgs2);%vds of M2 vdsn1=Vdd-vdsp3-vdsn2;

Resfreq=3e9; %desired resonant frequncy

ibias1 = 11e-6;%10e-6;%Desired additional bias current through transistor M1ibias2 = 1.0e-6;%Desired bias current through transistor M2

idwn1 =lookup\_idw\_3d(techfile,nDevice,Ln1,vdsn1,gmidn1) wn1=(ibias1+ibias2)/idwn1 fT = lookup\_ft\_3d(techfile,nDevice,Ln1,vdsn1,gmidn1)

gm1=gmidn1\*(ibias1+ibias2); go1=(1/lookup va 3d(techfile,nDevice,Ln1,vdsn1,gmidn1))\*(ibias1+ibias2);

Cgs1=-lookup\_cgswVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15 Cdg1=lookup\_cdwVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15 ... +lookup\_covlgdwVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15 ... -lookup\_cdgwVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15 ; Cgd1=-lookup\_cgdwVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15; Cds1=lookup\_cdswVsIdw\_3d(techfile,nDevice,Ln1,vdsn1,idwn1)\*wn1\*1e6/20\*1e-15;

idwn2 = lookup\_idw\_3d(techfile,nDevice,Ln2,vdsn2,gmidn2) wn2=(ibias2)/idwn2 fT = lookup\_ft\_3d(techfile,nDevice,Ln2,vdsn2,gmidn2)

gm2=gmidn2\*(ibias2)\*1.2 go2=(1/lookup va 3d(techfile,nDevice,Ln2,vdsn2,gmidn2))\*(ibias2)

Cgs2=lookup\_cggwVsIdw\_3d(techfile,nDevice,Ln2,vdsn2,idwn2)\*wn2\*1e6/20\*1e-15; Cdg2=lookup\_cdwVsIdw\_3d(techfile,nDevice,Ln2,vdsn2,idwn2)\*wn2\*1e6/20\*1e-15+... lookup\_covlgdwVsIdw\_3d(techfile,nDevice,Ln2,vdsn2,idwn2)\*wn2\*1e6/20\*1e-15... -lookup\_cdgwVsIdw\_3d(techfile,nDevice,Ln2,vdsn2,idwn2)\*wn2\*1e6/20\*1e-15;

Cds2=lookup\_cdswVsIdw\_3d(techfile,nDevice,Ln2,vdsn2,idwn2)\*wn2\*1e6/20\*1e-15;

wp3=1e-6;

gmid3=19.7/1.1; %lookup\_gmid\_3d(techfile,pDevice, Lp3, ,vdsp3) idwp3 =lookup\_idw\_3d(techfile,nDevice,Lp3,vdsp3,gmid3); go3=(1/lookup\_va\_3d(techfile,pDevice,Lp3,vdsp3,gmid3))\*(ibias2);

Cdd3=lookup\_cdwVsIdw\_3d(techfile,pDevice,Lp3,vdsp3,idwp3)\*wp3\*1e6/20\*1e-15 ... +lookup\_covlgdwVsIdw\_3d(techfile,pDevice,Lp3,vdsp3,idwp3)\*wp3\*1e6/20\*1e-15 ... -lookup\_cdgwVsIdw\_3d(techfile,pDevice,Lp3,vdsp3,idwp3)\*wp3\*1e6/20\*1e-15;

f=[1:1e6:10e9+1]'; s=2\*pi\*i\*f;

```

% Zin of active inductor

```

```

z=((Cgs1 + Cgd1 + Cdg2 + Cdd3) / (Cgs1 * Cgs2 + Cdg1 * Cgs1 + Cds1 * Cgs1 + Cdd3 * Cgs2 + Cdg2

* Cgs2 + Cgd1 * Cgs2 + Cds1* ...

Cgd1 + Cds1 * Cdd3 + Cdg1 * Cdg2 + Cds1 * Cdg2 + Cdg1 * Cdd3)* s + (go2 + go3) / (Cgs1 * Cgs2 +

Cdg1 * Cgs1 + Cds1 * Cgs1 + ...

Cdd3 * Cgs2 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cds1 * Cgd1 + Cds1 * Cdd3 + Cdg1 * Cdg2 + Cds1 *

Cdg2 + Cdg1 * Cdd3)) ./ (s .^ 2 + ...

(gm2 * Cgs1 + go1 * Cgs1 + go2 * Cgs1 + go2 * Cgs2 + Cgd1 * gm1+ Cgd1 * gm2 - Cdg1 * gm2 +

Cdg2 * gm2 + Cdd3 * gm2 + Cdd3 * ...

go1 + Cdg2 * go1 + Cgd1 * go1 + Cds1 * go2 + Cdd3 * go2 + Cdg2 * go2 + go3 * Cgs2 + Cdg1 * go3 +

Cds1 * go3) / (Cgs1 * Cgs2 ...

+Cdg1 * Cgs1 + Cds1 * Cgs1 + Cdd3 * Cgs2 + Cdg2 * Cgs2 + Cgd1 *Cgs2 + Cds1 * Cgd1 + Cds1 *

Cdd3 + Cdg1 * Cdg2 + Cds1 * Cdg2 \dots

+Cdg1 * Cdd3) * s + (gm1 * gm2 + gm1 * go2 + go1 * go2 + go3 * gm2 + go3 * go1 + go3 * go2 / /

(Cgs1 * Cgs2 + Cdg1 * Cgs1 + ...

Cds1 * Cgs1 + Cdd3 * Cgs2 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cds1 * Cgd1 + Cds1 * Cdd3 + Cdg1 * Cdd3 +

Cdg2 + Cds1 * Cdg2 + Cdg1 * Cdd3)); ...

w01=(gm1 * gm2 + gm1 * go2 + go1 * go2 + go3 * gm2 + go3 * go1 + go3 * go2) / ((Cgs1 * Cgs2 +

Cdg1 * Cgs1 + Cds1 * Cgs1 + Cdd3...

* Cgs2 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cds1 *Cgd1 + Cds1 * Cdd3 + Cdg1 * Cdg2 + Cds1 * Cdg2 +

Cdg1 * Cdd3));

resfreq1=sqrt(w01)/(2*pi)

figure;

subplot(211)

hold on

```

plot(f,real(z),'black');

plot(f,imag(z),'-.black');

legend('real','imag');

```

subplot(212)

plot(f,imag(z)./(2*pi*f),'r');

```

hold off

indc=imag(z(1,1)./(2\*pi\*1)) %

%active VCO

Lp=240 vdsp=500e-3

R=10e3%max(real(z)) gm=1/R\*2 id=5e-6;

Cds1 \* Cdg2 + Cds1 \* Cdd3);

gmid=gm/id

idw = lookup\_idw\_3d(techfile,pDevice,Lp,[],gmid) fT = lookup\_ft\_3d(techfile,pDevice,Lp,[],gmid) w=id/idw

Cgs=lookup\_cggwVsIdw\_3d(techfile,pDevice,Lp,vdsp,idw)\*w\*1e6/20\*1e-15 Cdg=lookup\_cdwVsIdw\_3d(techfile,pDevice,Lp,vdsp,idw)\*w\*1e6/20\*1e-15 go=(1/lookup\_va\_3d(techfile,pDevice,Lp,vdsp,gmid))\*(10e-6)

```

Cx=(Cdg+2*Cgs);

Cds=0.5e-15%lookup_cdsw_3d(techfile,pDevice,Lp,vdsp,idw)*w*1e6/20*1e-15

```

```

z_3 = ((Cgs_1 + Cgd_1 + Cdg_2 + Cdd_3) / (Cgs_1 * Cgs_2 + Cx * Cgs_1 + Cdg_1 * ...

Cgs1 + Cds1 * Cgs1 + Cds * Cgs1 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cdd3 * Cgs2 ...

+ Cds1 * Cgd1 + Cx * Cgd1 + Cx * Cdd3 + Cx * Cdg2 + Cds * ...

Cdd3 + Cdg1 * Cdg2 + Cdg1 *Cdd3 + Cds * Cgd1 + Cds * Cdg2 + Cds1 * Cdg2 + ...

Cds1 * Cdd3) * s+ (go2 + go3) / (Cgs1 * Cgs2 + Cx * Cgs1 + Cdg1 * Cgs1 ...

+Cds1 * Cgs1 + Cds * Cgs1 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cdd3 *Cgs2 + Cds1 * ...

Cgd1 + Cx * Cgd1 + Cx * Cdd3 + Cx * Cdg2 + Cds * Cdd3 + Cdg1 * ...

Cdg2 + Cdg1 * Cdd3 + Cds * Cgd1 + Cds * Cdg2 + Cds1 * Cdg2 + Cds1 * Cdd3)) ./ ...

(s.^2+(gm2 * Cgs1+ go1 * Cgs1 + go2 * Cgs1 + go2 * Cgs2 + Cgd1 * gm1 + Cdg2 ...

*gm2 + Cgd1 * gm2 - Cdg1 * gm2 + Cdd3 * gm2 + Cdg2 * go1 + Cgd1* go1 + Cdd3 * go1 ...

+ Cdd3 * go2 + Cx * go2 + Cds1 * go2 + Cdg2 * go2 + Cds * go2 - gm * Cgs1 + ...

go * Cgs1 + go3 * Cgs2 + Cds1 * go3 + Cx * go3 - gm * Cdd3 - gm * Cdg2 + Cdg1 ...

* go3+ Cds * go3 - gm * Cgd1 + go * Cgd1 + go * Cdg2 + go * Cdd3) /(Cgs1 * Cgs2 ...

+ Cx * Cgs1 + Cdg1 * Cgs1 + Cds1 * Cgs1 + Cds* Cgs1 + Cdg2 * Cgs2 + Cgd1 * ...

Cgs2 + Cdd3 * Cgs2 + Cds1 * Cgd1+ Cx * Cgd1 + Cx * Cdd3 + Cx * Cdg2 ...

+ Cds * Cdd3+ Cdg1 * Cdg2 + Cdg1 * Cdd3 + Cds * Cgd1 + Cds * Cdg2 + Cds1 * Cdg2 + ...

Cds1 * Cdd3) * s + (gm1 * gm2 + gm1 * go2 + go1 * go2 + go3 * gm2 + go3 * go1 + go3 ...

* go2 - gm * go2 + go * go2 - gm *go3 + go * go3) / (Cgs1 * Cgs2 + Cx * Cgs1 + ...

Cdg1 * Cgs1 + Cds1 * Cgs1 + Cds * Cgs1 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cdd3 * Cgs2 + Cds1 \dots

* Cgd1 + Cx * Cgd1 + Cx * Cdd3 + Cx * Cdg2 + Cds * Cdd3 + Cdg1 * Cdg2 ...

Cdg1 * Cdd3 + Cds * Cgd1 + Cds * Cdg2 + Cds1 * Cdg2 + Cds1 * Cdd3)); ...

w3=(gm1 * gm2 + gm1 * go2 + go1 * go2 + go3 * gm2 + go3 * go1 + go3 * go2 - gm * go2 + go * ...

go2 - gm *go3 + go * go3) / (Cgs1 * Cgs2 + Cx * Cgs1 + Cdg1 * Cgs1 + Cds1 * Cgs1 + Cds ...

* Cgs1 + Cdg2 * Cgs2 + Cgd1 * Cgs2 + Cdd3 *Cgs2 + Cds1 * Cgd1 + Cx * Cgd1 + Cx * ...

Cdd3 + Cx* Cdg2 + Cds* Cdd3 + Cdg1* Cdg2 + Cdg1* Cdd3 + Cds* Cgd1 + Cds* Cdg2 + \dots

```

resfreq3=sqrt(w3)/(2\*pi)