©2013

Lei Lin

ALL RIGHTS RESERVED

## **DESIGN AND FABRICATION OF 4H SILICON CARBIDE GATE**

## **TURN-OFF THYRISTORS**

by

## LEI LIN

A Dissertation submitted to the

Graduate School-New Brunswick

**Rutgers, The State University of New Jersey**

in partial fulfillment of the requirements

for the degree of

**Doctor of Philosophy**

Graduate Program in Electrical and Computer Engineering

written under the direction of

**Professor Zoran Gajic**

and approved by

New Brunswick, New Jersey

OCTOBER, 2013

## ABSTRACT OF THE DISSERTATION

## Design and Fabrication of 4H Silicon Carbide Gate Turn-off Thyristors

#### By Lei Lin

**Dissertation Director:**

#### **Prof. Zoran Gajic**

Power electronics systems require robust power switches to operate at high temperatures to meet the demand for smaller and higher power density systems. The improvement in material technology has made 4H–Silicon Carbide (SiC) a promising material for power electronics applications. This is because SiC has superior properties such as high electric breakdown field, high thermal conductivity and high bandgap. Compared to other devices made on SiC, such as BJTs and IGBTs, SiC gate turn-off thyristors (GTOs) are favorable devices for power electronic applications due to their ability to operate at high current and high voltage levels under high temperature, which is attributed to conductivity modulation in the drift layer of the device. Furthermore, SiC GTOs offer several advantages over Si thyristors and Si GTOs such as compactness, higher current density, faster switching, and higher temperature operation.

This dissertation presents the design, fabrication and characterization of 4H-SiC GTOs, along with the study of the multistep junction termination extension (MJTE) for high power 4H-SiC devices. The physics-based MJTE design and optimization via numerical simulations has been studied. The 3-step MJTE with the maximum blocking voltage of 7630 V, which is 90% of the ideal breakdown voltage, has been demonstrated.

The design of MJTE has been applied to the fabrication of GTOs.  $0.1 \text{ cm}^2$  4H-SiC greater than 6 kV GTOs have been demonstrated with MJTE utilized successfully. A relatively large area, high voltage 4H-SiC GTO that exhibits encouraging characteristic at the onand off-state, low leakage current and high yield is presented. Initial pulse testing results shows that the fabricated GTOs can handle both the high current density and the high turn-off speed.

## DEDICATION

To my family

### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to my dissertation advisor, Professor Zoran Gajic, for bringing out my potential, for his unwavering support, guidance, encouragement, and patience. I would like to thank Prof. Yicheng Lu, Prof. Kuang Sheng and Prof. Jian Zhao, for their technical guidance and continuous support, and for laying down the solid foundation for my future career. I would like to thank my dissertation committee members, Prof. Jaeseok Jeon, Prof. Wei Jiang, Prof. Leonard Feldman and Prof. George Celler for taking time off of their busy schedule to review and critique my dissertation.

I would also like to take this opportunity to thank Prof. Athina Petropulu, Prof. George Shoane and Prof. Warren Lai for valuable insight gained from much technical discussion over years. I also appreciate the friendship and kindness of many current and former graduate students at Rutgers whom I have had the pleasure to work with including Dr. Xiaobin Xin, Dr. Xueqing Li, Dr. Yongxi Zhang, Dr. Yuzhu Li, Dr. Petre Alexondrov, Dr. Hujun, Dr. Jianhui Zhang, Dr. Jian Wu, Dr. Rahul Radhakrishnan, Dr. Leonid Rursin, Dr. Ziqing Duan, Mr. Chieh-Jen Ku, Mr. Yang Zhang, Mr. Rui Li, Mr. Weiwei Song and Mr. Jun Tan. They all contributed in myriad ways to help my research along.

Finally, I would like to acknowledge financial support provided by Navy under the project of the SiC-based AC-link power converter, and APAR-E under the project of the completely new type of SiC bipolar switch (15kV-20kV) for utility scale inverters.

| TABI | LE OF | CONTENT |

|------|-------|---------|

|      |       |         |

| ABSTRACT OF THE DISSERTATION                         | ii   |

|------------------------------------------------------|------|

| DEDICATION                                           | iv   |

| ACKNOWLEDGEMENTS                                     | v    |

| TABLE OF CONTENT                                     | vi   |

| LIST OF TABLES                                       | viii |

| LIST OF ILLUSTRATIONS                                | ix   |

| CHAPTER 1 INTRODUCTION                               | 1    |

| 1.1 Silicon Carbide for Power Devices                |      |

| 1.2 4H-SiC Bipolar Switching Devices                 |      |

| 1.2.1 SiC BJTs                                       |      |

| 1.2.2 SiC IGBTs                                      |      |

| 1.2.3 SiC GTOs                                       |      |

| 1.3 4H-SiC GTO Fundamentals                          |      |

| 1.4 Edge Termination in Power Devices                |      |

| <b>1.5</b> Outline of the Dissertation               | 15   |

| CHAPTER 2 DESIGN AND DEMONSTRATION OF MJTE FOR 4H-Si |      |

| 2.1 Junction Termination Extension (JTE)             | 17   |

| 2.2 Design of 3-Step MJTE                            |      |

| 2.3 Simulation of 3-Step MJTE                        |      |

| 2.3.1 Breakdown Voltage                              |      |

| 2.3.2 Equipotential Lines                            |      |

| 2.3.3 Electric Field                                 |      |

| 2.4 Mask Layout for the NPN Structure                |      |

| 2.5 Fabrication of the NPN Structure with MJTE       |      |

| 2.6 MJTE Optimization                                |      |

| 2.7 Summary                                          |      |

| CHAPTER 3 DESIGN OF 4H-SiC GTOs                      |      |

| 3.1 Design of the GTO Structure                      |      |

| 3.2 Simulation of GTO                                |      |

| 3.2.1 Static Characteristics                         |      |

| 3.2.2 Dynamic Characteristics                        |      |

| 3.3 Mask Design                                      |      |

| 3.3.1 3-inch GTO Mask                                |      |

| 3.3     | 3.2 Interdigitated Design                             | 55       |

|---------|-------------------------------------------------------|----------|

|         | 3.3 0.1cm <sup>2</sup> GTO Design                     |          |

|         | 3.4 Small GTO and Testing Pattern design              |          |

|         | Summary                                               |          |

|         | •                                                     |          |

| CHAPTE  | <b>R 4 FABRICATION AND CHARACTERIZATION OF 4H-S</b>   | iC GTO62 |

| 4.1     | Device Fabrication                                    | 63       |

| 4.1     | .1 Wafer Structure                                    | 63       |

| 4.1     | .2 Mesa Formation                                     | 65       |

| 4.1     | .3 Gate Implantation and Post-implantation Annealing  | 67       |

| 4.1     | .4 Isolation and MJTE formation                       |          |

| 4.1     | .5 Oxidation and Passivation                          | 74       |

| 4.1     | .6 Ohmic Contact                                      |          |

| 4.1     | .7 Overlay Metallization and Dielectric Layer Filling | 82       |

| 4.1     | .8 Package                                            | 86       |

| 4.2     | Device Characterizations                              | 87       |

| 4.2     | 2.1 Off-State Characteristics                         | 87       |

| 4.2     | 2.2 On-State Characteristics                          | 91       |

| 4.2     | 2.3 Dynamic Characteristics                           |          |

| 4.3     | Summary                                               |          |

| CHAPTEI | R 5 SUMMARY AND FUTURE WORK SUGGESTIONS               |          |

| 5.1     | Conclusion                                            |          |

| 5.2     | Suggestion for Future Work                            |          |

| REFEREN | NCE                                                   | 100      |

| CURRICU | JLUM VITA                                             | 105      |

## LIST OF TABLES

| Table 1-1 Material properties of the well-known semiconductors                 | 2    |

|--------------------------------------------------------------------------------|------|

| Table 2-1 Key parameters for MJTE design                                       | 26   |

| Table 2-2 Breakdown voltage and the percent of the ideal breakdown voltage for | MJTE |

| design with $d2 = d3 = 0.14 \ \mu m$                                           | 28   |

| Table 2-3 Relation between d1 and dJTE1 at $d2 = d3 = 0.14 \ \mu m$            | 29   |

| Table 3-1 GTO mask set                                                         | 61   |

| Table 4-1 Photolithography recipe for mesa etching mask using AZ5214           | 66   |

| Table 4-2 Photolithography recipe for the mesa etching mask using AZ4400       | 69   |

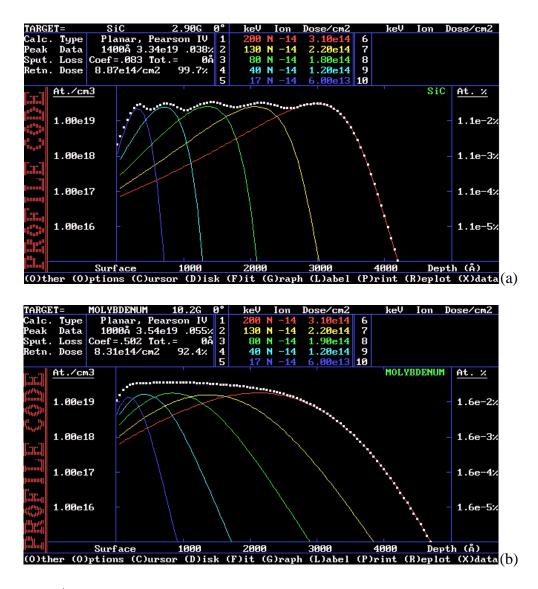

| Table 4-3 N implantation specification                                         | 69   |

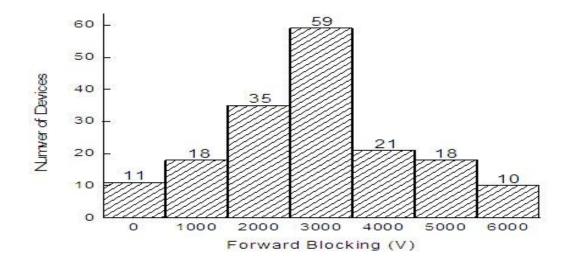

| Table 4-4 The blocking voltage mapping on 4H-SiC GTO devices                   | 88   |

## LIST OF ILLUSTRATIONS

| Fig. 1-1 Applications of power semiconductor devices                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1-2 Simplified cross-sectional view of the npn 4H-SiC BJT                                                                                                               |

| Fig. 1-3 SiC IGBT structures for p-channel                                                                                                                                   |

| Fig. 1-4 Increase in SiC GTO chip size over the past ten years demonstrated at CREE 10                                                                                       |

| Fig. 1-5 Cross-section of a GTO cell with circuit symbols                                                                                                                    |

| Fig. 2-1 Schematic cross section of a p-n junction with junction termination extension. 17                                                                                   |

| Fig. 2-2 Dependence of the breakdown voltage on the normalized JTE length                                                                                                    |

| Fig. 2-3 Schematic cross-section of a NPN structure with 3-step MJTE                                                                                                         |

| Fig. 2-4 1-step JTE structure cross section view and the breakdown voltage as a function                                                                                     |

| of extents on etching depth d <sub>1</sub> 23                                                                                                                                |

| Fig. 2-5 2-step JTE structure cross section view and the breakdown voltage as a function                                                                                     |

|                                                                                                                                                                              |

| of extents on etching depth d124                                                                                                                                             |

| of extents on etching depth d1                                                                                                                                               |

|                                                                                                                                                                              |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \ \mu m$                                                                                |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

| Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with $d_1 = 1.4 \mu m$<br>and $d_2 = 0.14 \mu m$ . Insert (a) & (b) are details at the encircled region |

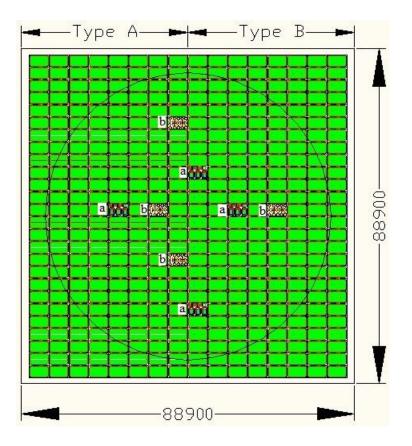

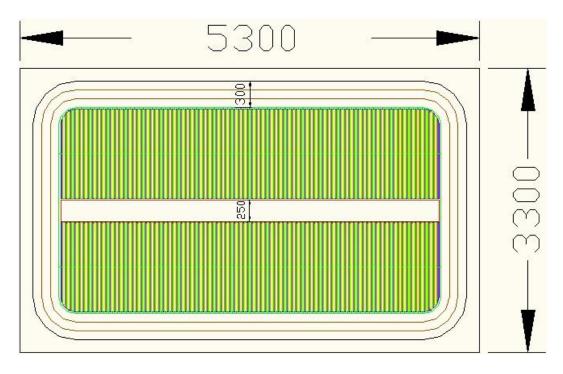

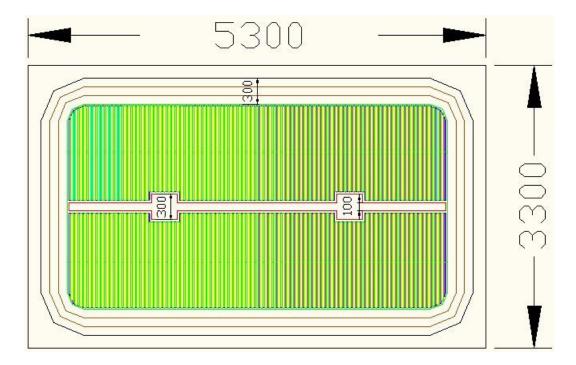

| Fig. 3-11 Top view of type A GTO design showing rectangle-shape gate bonding 57                 |

|-------------------------------------------------------------------------------------------------|

| Fig. 3-12 Top view of type B GTO design showing barbell-shape gate bonding 57                   |

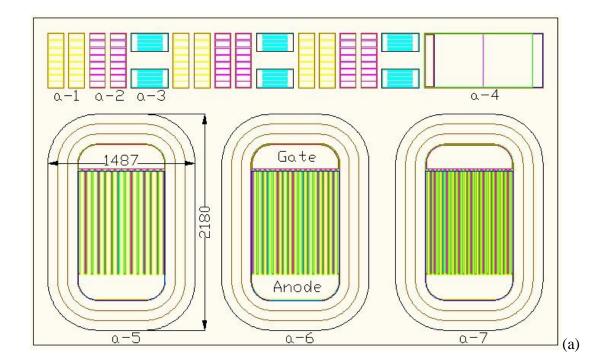

| Fig. 3-13 (a) Top view of small GTOs and testing patterns (unit: $\mu$ m), details in (b) TLM   |

| design and (c) mesa etching monitor                                                             |

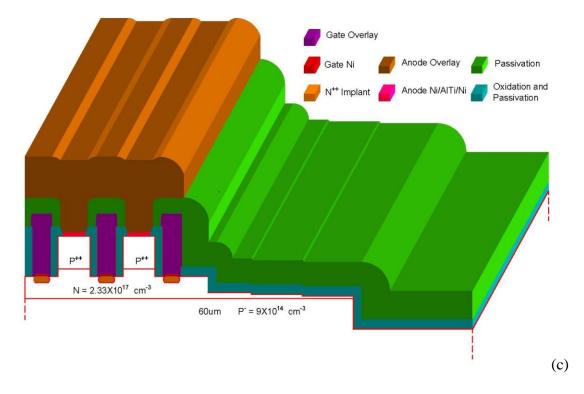

| Fig. 4-1 Schematic of 4H-SiC wafer structure 3D view                                            |

| Fig. 4-2 Schematic of the anode mesa 3D view                                                    |

| Fig. 4-3 N+ doping profile of the Gate vertical implantation in: (a)4H-SiC and (b) Mo. 68       |

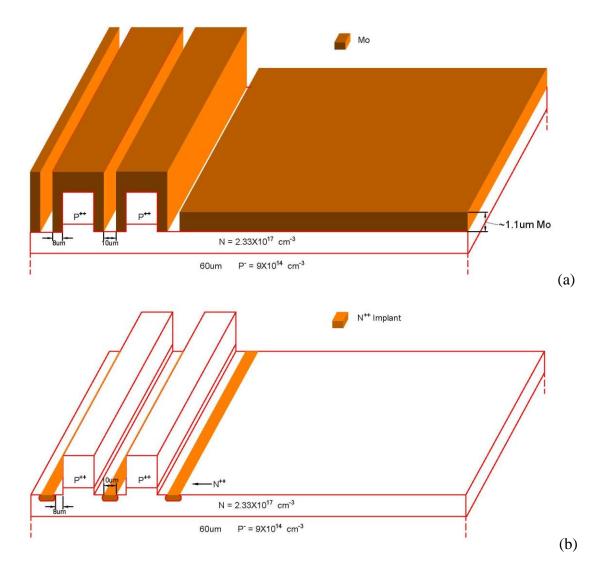

| Fig. 4-4 Schematics of 3D view on (a) Mo mask and (b) Implanted gate after Mo                   |

| removal 70                                                                                      |

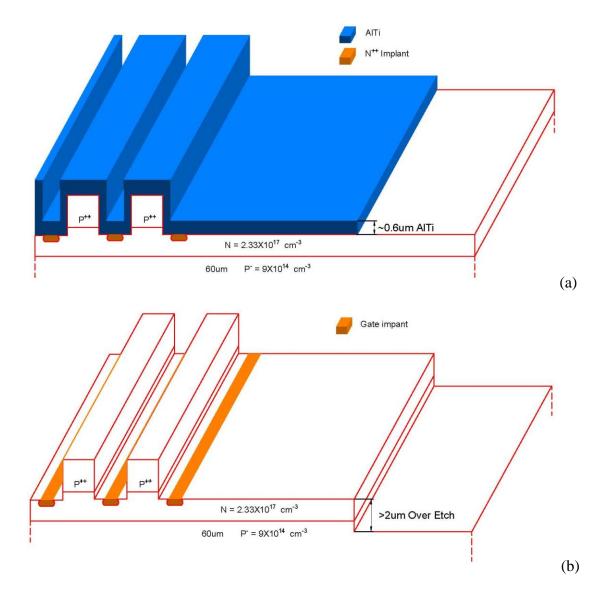

| Fig. 4-5 Schematics of 3D view on (a) AlTi mask and (b) isolation after AlTi removal. 71        |

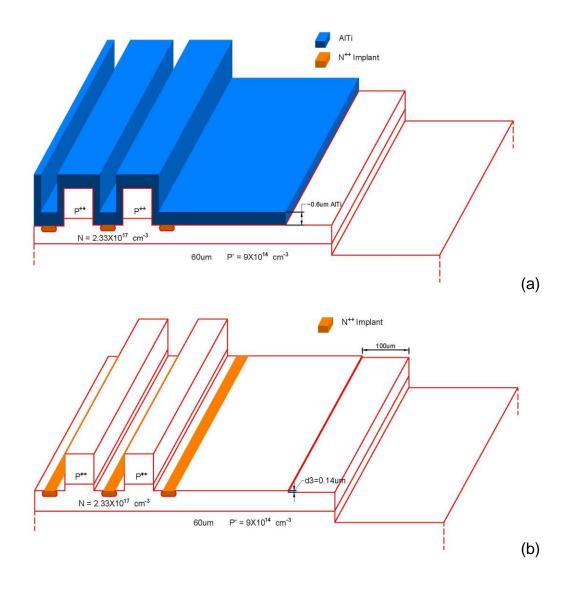

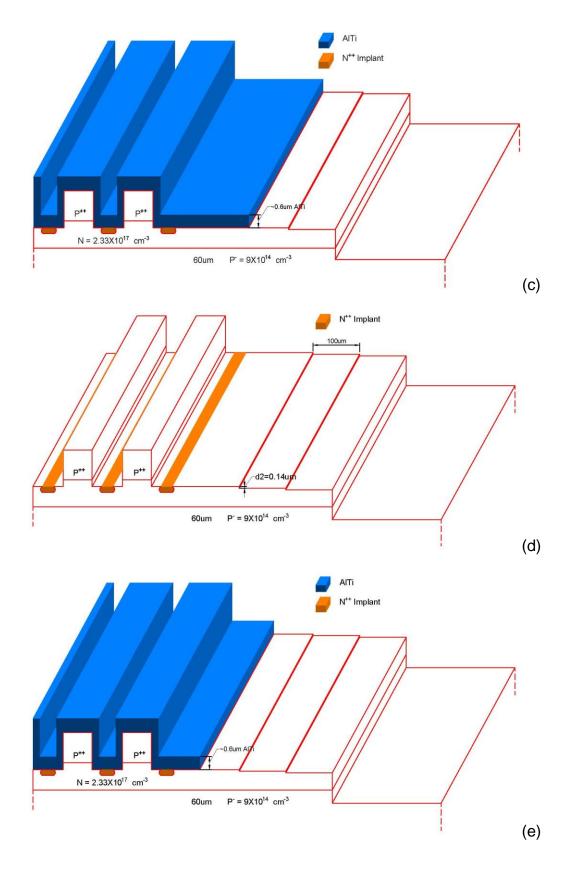

| Fig. 4-6 Schematics of 3D view on (a) $JTE_3$ mask; (b) $JTE_3$ after AlTi removal; (c) $JTE_2$ |

| mask; (d) $JTE_2$ after AlTi removal; (e) $JTE_1$ mask and (f) $JTE_1$ after AlTi removal 74    |

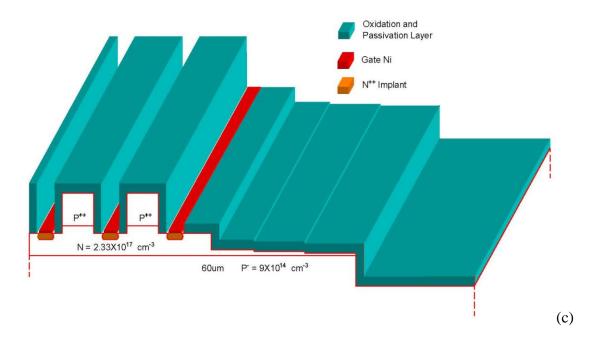

| Fig. 4-7 Schematic of 3D view on one GTO device after the formation of passivation              |

| layers                                                                                          |

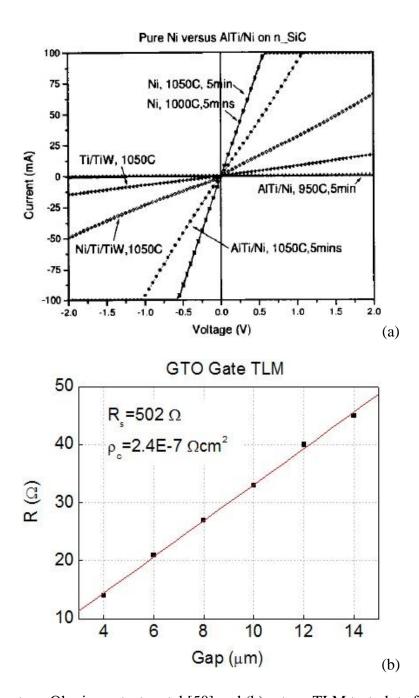

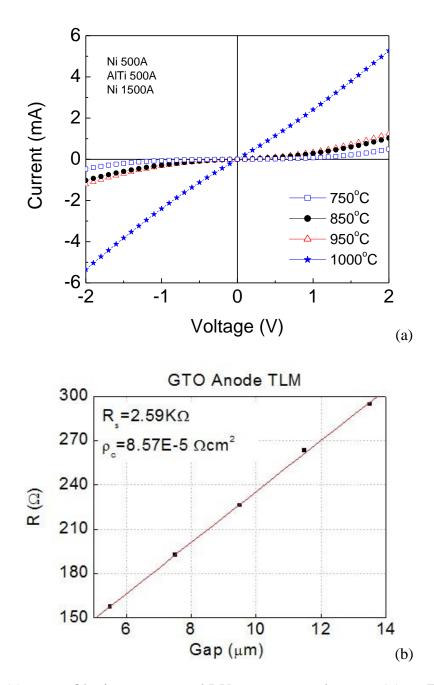

| Fig. 4-8 (a) n-type Ohmic contact metal and (b) n-type TLM test plot after 1050 $^{\circ}C$     |

| annealing                                                                                       |

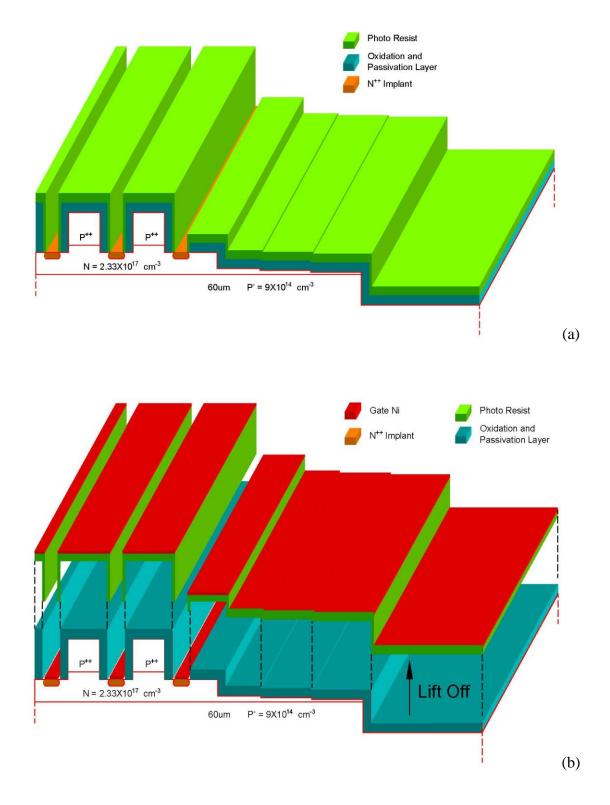

| Fig. 4-9 Schematics of 3D view on (a) Gate contact window open, (b) Metal lift-off and          |

| (c) Gate metal contact formation                                                                |

| Fig. 4-10 (a) p-type Ohmic contact metal I-V measurement between 15 $\mu$ m TLM pads            |

| and (b) p-type TLM test plot after 1000 °C annealing                                            |

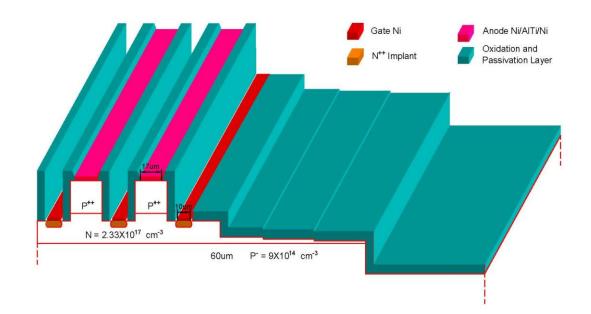

| Fig. 4-11 Schematics of a 3D view on anode metal contact formation                              |

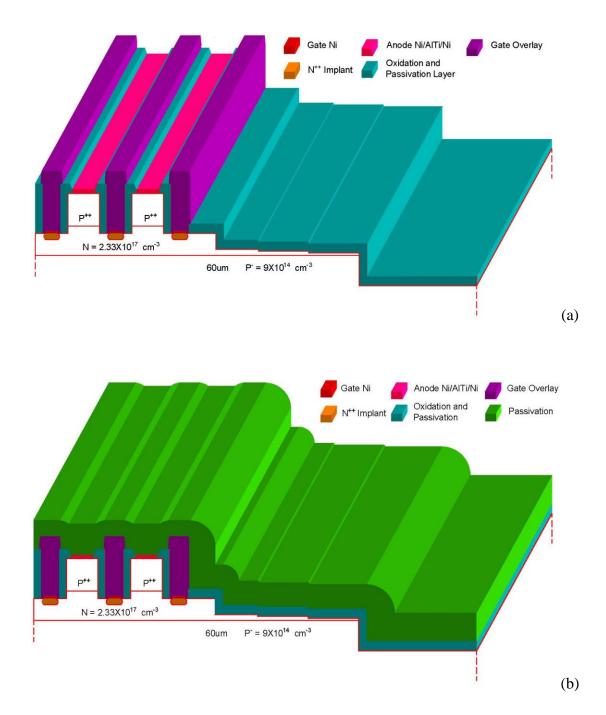

| Fig. 4-12 Schematics of 3D view on (a) gate overlay formation, (b) dielectric layer filling     |

| and (c) anode overlay formation                                                                 |

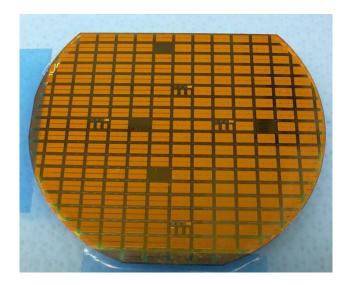

| Fig. 4-13 Optical photo of a 3 inch SiC wafer after GTO devices fabrication               |

|-------------------------------------------------------------------------------------------|

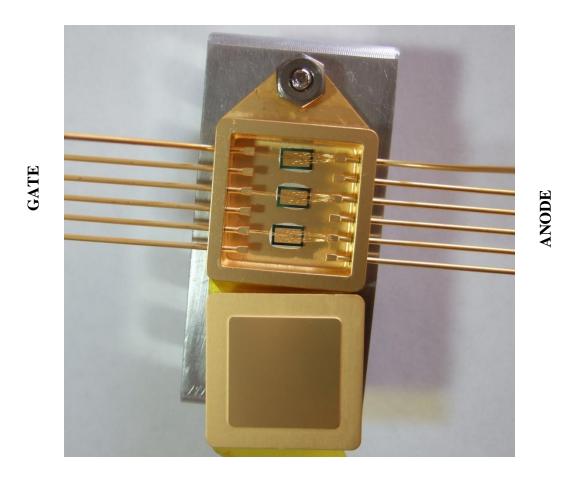

| Fig. 4-14 An optical photo for the 4H-SiC power integrated circuits after packaging 86    |

| Fig. 4-15 Histogram of forward blocking voltages measured on 0.1 cm <sup>2</sup> GTOs     |

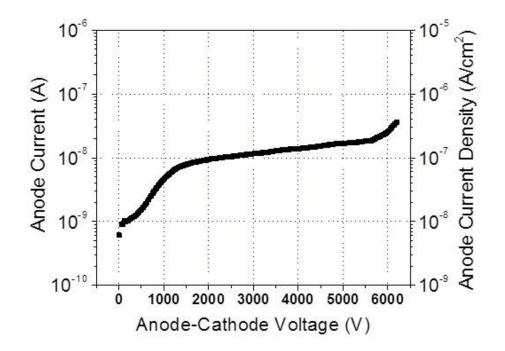

| Fig. 4-16 Forward I-V curve of a GTO with for over 6kV blocking                           |

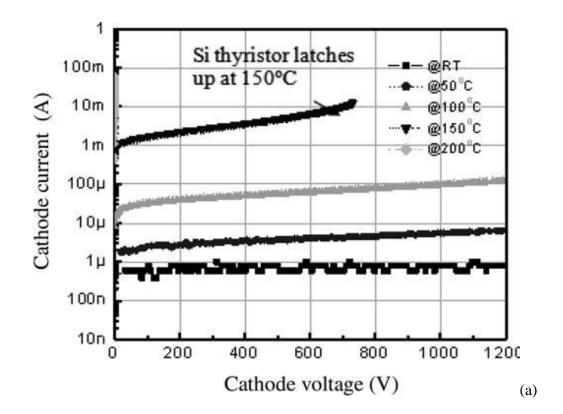

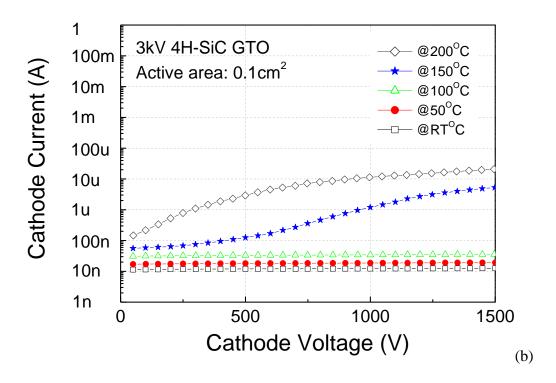

| Fig. 4-17 Leakage currents for (a) Si and (b) SiC Thyristors at elevated temperatures91   |

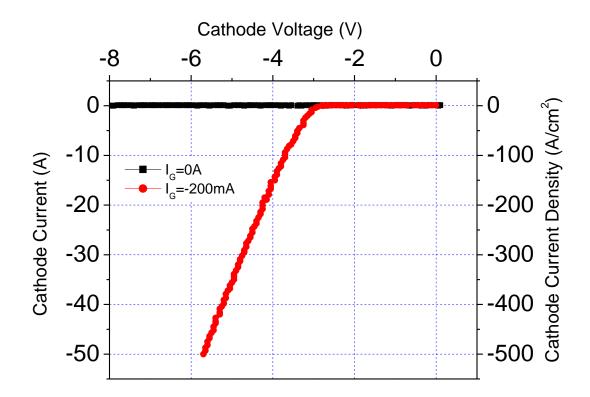

| Fig. 4-18 Static IV characteristics. Insert shows the packaged GTO devices for tests 92   |

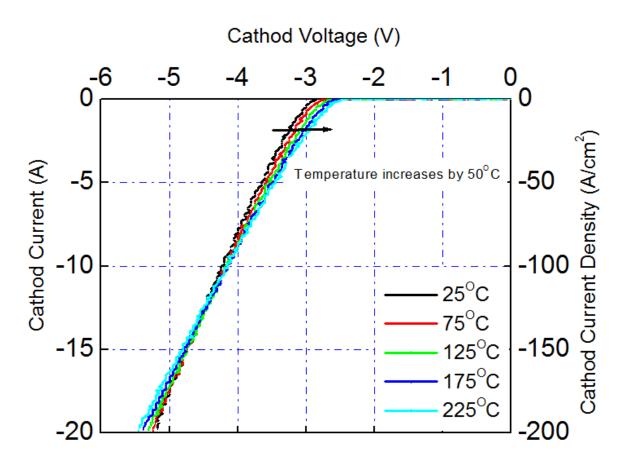

| Fig. 4-19 Output characteristics of a 2 kV SiC GTO at different temperature with $IG = -$ |

| 20 mA. Device active area: 0.1 cm <sup>2</sup>                                            |

| Fig. 4-20 GTO switching testing circuit                                                   |

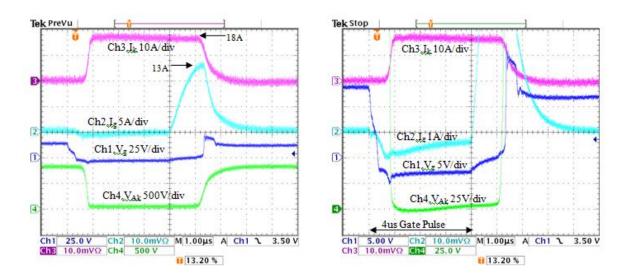

| Fig. 4-21 Hard-switching with a resistive load at 800 V-18 A (left) and detailed wave-    |

| forms (right)                                                                             |

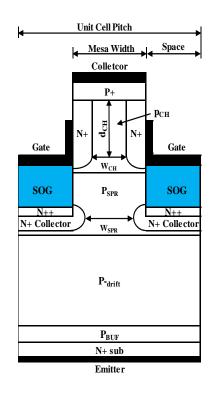

| Fig. 5-1 Cross sectional view of normally-off SiC VGBT                                    |

### CHAPTER 1 INTRODUCTION

#### 1.1 Silicon Carbide for Power Devices

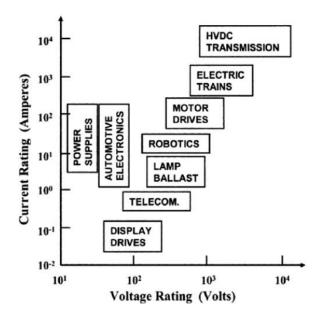

Power devices constitute the heart of modern power electronic apparatus. Depending on the specific application, power devices can be classified in terms of their current and voltage handling requirements as shown in Fig. 1-1, where the boxes indicate the device voltage and current ratings that the system requires [1]. Typically, a specific power device structure is only suitable for a certain voltage or power range application. The high-power end of this chart is dominated by power thyristors, like gate turn-off thyristors (GTOs). In the medium voltage range of 300 to 30 kV, insulated gate bipolar gate transistors (IGBTs) are usually an optimal choice with significant current handling capability. Power MOSFETs are normally used at lower voltage ratings for higher frequency applications, [1].

Fig. 1-1 Applications of power semiconductor devices, [1].

There is no doubt that silicon (Si) is the most commonly used semiconductor material in manufacturing power devices because of its high availability and a low production cost. However, devices based on Si are not able to operate at temperatures above 200 °C, because of excessive junction leakage currents. This limitation becomes even more severe when high operating temperatures are combined with high-power, high-frequency and high-radiation. High temperature circuits are used in various applications, such as aerospace applications, nuclear power instrumentation, space exploration, and automotive electronics. Wide band-gap materials have to be used in order to build devices capable of operation at high temperatures and high power under high frequencies. Some of the main materials of interest for such applications are shown in Table 1-1. The Baliga figure-of-merit (BFOM =  $\varepsilon_r \mu E_c^3$ [2]) values for all materials in the table have been standardized to that of silicon.

| Material | Eg<br>(eV) | ٤r   | $\mu_n (cm^2/V s)$ | E <sub>c</sub><br>(MV/cm) | $\frac{v_{sat}}{(10^7 cm/s)}$ | λ<br>(W/cm K) | BFOM |

|----------|------------|------|--------------------|---------------------------|-------------------------------|---------------|------|

| Si       | 1.12       | 11.8 | 1350               | 0.3                       | 1.0                           | 1.5           | 1    |

| Diamond  | 5.5        | 5.5  | 2200               | 5.6                       | 2.7                           | 20.0          | 4260 |

| GaN      | 3.39       | 9.0  | 900                | 3.3                       | 2.5                           | 1.3           | 676  |

| 4H-SiC   | 3.23       | 9.7  | 720                | 3.0                       | 2.0                           | 4.9           | 450  |

Table 1-1 Material properties of the well-known semiconductors [3,4]

Notes:  $E_g$  – bandgap,  $\varepsilon_r$  – dielectric constant,  $\mu_n$  – electron mobility,  $E_c$  – breakdown electric field,  $V_{sat}$  – saturated electron velocity,  $\lambda$  – thermal conductivity

From this comparison, we can see that the popular wide band-gap semiconductors are at least hundreds of times better than silicon for power devices. Even though, they do not yet challenge silicon's existing dominance in this market, their increasingly maturing technology is expected to lead to a great commercialization success in the years to come. Power devices based on wide band-gap semiconductors have following advantages:

- The intrinsic temperature, i.e., the temperature where the intrinsic carrier concentration becomes comparable to the doping concentration, is extremely high. For example, assuming a doping concentration of 10<sup>15</sup> cm<sup>-3</sup>, the intrinsic temperature, at which the intrinsic carrier concentration reaches 2x10<sup>14</sup> cm<sup>-3</sup>, is approximately 1100 °C for 4H-SiC, as compared to 245 °C for Si. This makes wide band-gap semiconductors extremely attractive for high-temperature application; a suitable high temperature semiconductor technology could allow bulky aircraft hydraulics and mechanical control systems to be replaced with heat-tolerant control electronics. On-site electronics, actuators, and sensors would reduce complexity and increase reliability.

- Because the wide band-gap does not degrade the electronic properties of wide band-gap semiconductors, so the power devices based on wide band-gap materials can be useful in aerospace applications with a reduced radiation shielding.

- Because of the high electric breakdown field, the drift region can be much thinner than that of their Si counterparts for the same voltage rating, thus a much lower specific-on resistance could be obtained. With a lower specific-on resistance, the wide band-gap based power devices have lower conduction losses and higher overall efficiency.

- Because of the high-saturated drift velocity, the power devices based on wide band-gap materials could be switched at higher frequencies than their counterparts. Moreover, the charge in the depletion region of a diode can be removed faster if the drift velocity is higher, and therefore, the reverse recovery time is shorter.

- Higher thermal conductivity allows heat generated in the power devices to be more easily transmitted to the case, heat-sink and then to the ambient. Thus power devices based on wide band-gap materials have high thermal stability.

Among these wide band-gap semiconductors, diamond is often cited as the ultimate materials [5], which is readily explainable by the BFOM criteria. However, the extreme difficulties in a single crystal growth and shallow doping have kept diamond from the successful electronics development for many years.

GaN, on the other hand, has been a notable alternative to SiC and is under active research worldwide by many teams. However, the difficulty in the GaN native substrate technology and the high defect density in GaN epilayers still raises serious concerns and questions, making it less successful than SiC for power device applications.

In short, although Silicon Carbide (SiC) does not possess the highest BFOM in the group, it is by far the most matured and commercially available wide bandgap material compared to its alternatives. In addition, 4H-SiC, the most commercially available polytype of SiC, offers more favorable properties compared to the others, such as 3C-SiC and 6H-SiC. Today's SiC material suppliers like Cree are already offering zero-micropipe density 4H-SiC wafers up to 100 mm in diameter. Given the vastly improved material technology as of today and the superior properties of SiC over silicon, we

strongly believe that this is the right time to engage in the development of novel power device and integrated circuit technologies on 4H-SiC.

#### **1.2 4H-SiC Bipolar Switching Devices**

There has been a rapid improvement in SiC materials and power devices during the last few years SiC unipolar devices such as Schottky diodes, JFETs and MOSFETs have been developed extensively and advantages of insertion of such devices in power electronic systems have been demonstrated [6, 7]. However, unipolar devices for high voltage systems suffer from high drift layer resistance that gives rise to high power dissipation in the on-state. For such applications, bipolar devices are preferred due to their low on-resistance.

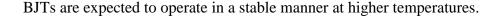

#### 1.2.1 SiC BJTs

SiC power BJT has been developed in recent years due to its unique properties such as low on-resistance, normally-off nature, positive temperature coefficient of the on-state resistance, negative temperature coefficient of the current gain, and fast switching speed. Fig. 1-2 [8] shows a typical 4H-SiC power BJT structure. Because of the high breakdown electrical field in 4H-SiC, both the base layer and the drift-layer can be much thinner and the doping could be much higher than in Si-BJT. The thinner drift layer leads to a lower specific on-resistance, a thinner base helps to get a higher current gain. Higher doping in the drift layer is important to prevent the secondary voltage breakdown.

SiC BJTs can address the device requirements in the 600 V to 10 kV range [8,9,10, 11]. It is currently the only normally-off device in SiC which could achieve an onresistance comparable to Silicon CoolMOS in the 600–900 V range, and exhibit the superior high temperature operation capability. Due to the absence of a gate oxide, SiC

Fig. 1-2 Simplified cross-sectional view of the npn 4H-SiC BJT, [8].

The above advantages of SiC BJTs allow the system to work at higher frequencies resulting in the reduced size and cost of the passive component. This is very attractive for applications that demand a higher power density or operating temperature, such as the traction drive used in hybrid electric vehicles and power supplies. SiC BJTs have several distinguishing features: (1) Compared to SiC MOSFETs, SiC BJTs have a lower on-resistance, are free of gate oxide problem and the fabrication cost is currently less than for MOSFETs; (2) SiC BJTs exhibit a positive temperature coefficient of the on state resistance and a negative temperature coefficient of the current gain, which allow easy paralleling of SiC BJTs; (3) SiC BJTs have demonstrated a square Reverse Bias Save Operating Area (RBSOA) boundary without second breakdown; (4) the conductivity modulation of the drift layer in SiC BJTs is very minimal, which allows the device to

operate at high frequency. Moreover, a current gain of 50–70 has been routinely achieved on SiC BJTs, which can significantly simplify the gate drive circuits. [12]

The obstacle for commercialization of SiC BJTs is the presence of degradation in the on-resistance and current gain. The recombination-induced stacking faults (SFs) have been identified as a prime cause. When nucleation sites are available, SF development results in the performance degradation in SiC BJTs. These SFs originate from basal plane dislocations (BPDs). A high density of SFs corresponds to an on resistance increase after electrical stress and a significant current gain reduction. When SiC BJTs are operated in the saturation region, the base and collector regions of the transistor are flooded with electron-hole pairs. It was speculated that the recombination of electron-hole pairs in the emitter, base, and collector regions gives rise to SFs. These SFs reduce the lifetime of the minority carriers in the emitter and base, which in turn results in the reduced current gain. The increase in the on-resistance of the BJT can be explained by SFs as follows: In the drift region, SFs act as carrier traps, effectively providing local areas of increased resistivity, thereby increasing the spreading resistance of the device; in the base region, SFs significantly suppress the conductivity modulation, thus dramatically increasing the base resistance, [13].

#### 1.2.2 SiC IGBTs

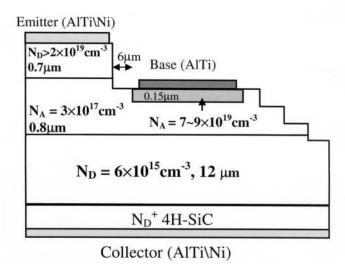

While SiC BJTs do not show substantial conductivity modulation, SiC IGBTs depend upon it for a low forward drop for more than 10 kV switches. IGBT is desirable due to its simple gate drive requirement and its great success in the silicon world. There are two types of IGBTs based on the channel polarity. A p-IGBT is composed of a p-channel MOS structure and a wide-base NPN transistor. On the other hand, an n-IGBT is

composed of an n-channel MOS structure with a wide-base PNP transistor. For typical power circuits, gate drive circuits usually reference the gate control signal to the cathode. However, in the case of p-IGBTs, the gate is referenced to the anode terminal. Technically, the SiC MOS structure has been demonstrated with high breakdown strength and a low interface charge density in recent years, paving the way for possible demonstration of IGBTs.

Both n-channel and p-channel IGBTs have been demonstrated on 4H-SiC with high blocking voltages [14, 15, 16]. Thanks to the great effort and progress made on SiC MOSFETs, n-IGBTs have been demonstrated with an excellent device performance for static and dynamic characteristics. On the contrary, p-IGBTs have taken a little longer because of the immaturity of p-MOS based design and fabrication. Theoretically, complementary SiC IGBTs should have identical specific on-resistances. With respect to the switching speed, n-IGBTs should be faster due to a much lower current gain of backside P+NP transistor than that of N+PN in p-IGBTs as shown in Fig. 1-3 [12]. However, the switching performance of p-IGBTs could be improved by optimization of the field-stop layer doping concentration, thickness and lifetime. One concern with n-IGBTs is the temperature coefficient of the forward voltage drop. The n-IGBT power handling capability might be significantly reduced at high temperatures due to the low hole mobility, [12].

After near 20 years of research since the first report of SiC IGBT, the gate oxide on SiC still continues to be the major reliability concern, especially if SiC IGBTs are to be operated at higher temperatures, although a great progress has been made for SiC MOSFETs [17]. It is widely know that the gate oxide reliability problem in actual power

switches, especially under the high electric field and temperature [18,19,20], is far from being solved because the source of the problems are fundamental: (i) hot carriers can more easily get into the gate oxide and be trapper because of the substantially smaller conduction band discontinuity in SiC/SiO<sub>2</sub> structure; (ii) oxidation of SiC does not lead to near perfect SiO<sub>2</sub> (unlike oxidation of Si) because C atoms always remain in SiO<sub>2</sub> while oxidation of Si leads to perfect SiO<sub>2</sub> (without C atom problem); (iii) n-channel carrier mobility is very low, in the range of 15 to 30 cm<sup>2</sup>/V/s when it should be in the range of 400 cm<sup>2</sup>/V/s (p-channel mobility is even lower, only about 1/8 of the n channel mobility).

Fig. 1-3 SiC IGBT structures for p-channel, [12].

#### 1.2.3 SiC GTOs

Some high voltage SiC MOSFETs and IGBTs have demonstrated performances superior to that of Si devices. However, the on-resistance of SiC MOSFETs and n-channel IGBTs increase significantly as the blocking voltage ( $\geq 5 \text{ kV}$ ) and the operating

junction temperature increase [21,22] because of the MOS reliability issue. In contrast, the SiC GTO, which not only does not have the gate oxide rupture issue, but also has the double-side carrier injection and the strong conductivity modulation in the drift region, can maintain a low forward voltage drop at high temperatures at the 10 kV to 30 kV blocking voltage level. The high voltage (10 kV-25 kV) SiC GTOs will have an important impact on the future utility applications because they can greatly reduce the number of series connected devices when compared to the silicon devices, leading to a huge reduction of the power electronic system size, weight, control complexity, cooling cost, as well as providing an improvement of the system efficiency and reliability. Therefore, 4H-SiC GTO is a very attractive device for high voltage, high power, high temperature application.

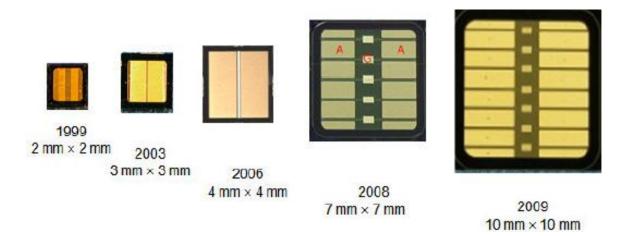

Fig. 1-4 Increase in SiC GTO chip size over the past ten years demonstrated at CREE, [26].

4H-SiC GTOs have been demonstrated by CREE, Inc., Northrop Grumman, and few universities since the late 90s for very high voltage applications in utility (for example - Fault Current Limiters) and pulse power applications [23,24,25]. The devices were made

on n-type 4H-SiC substrates resulting in an npnp structure, which is inverse of the conventional pnpn structure used in the silicon technology. This is necessary in SiC due to the high resistance of the p-type SiC substrates. The limitations on the epilayer thickness and the device footprint have generally limited these results to a few thousand volts of the blocking voltage and several amps. The small size was partially attributed to the presence of the high density of micropipes in the SiC crystal. In the last several years, the SiC technology has made tremendous strides in reducing the defect density which has enabled larger SiC GTO chip sizes as shown in Fig. 1-4 [26]. The micropipe density (MPD) has been reduced from more than 10 cm<sup>-2</sup> in 90s to less than 1 cm<sup>2</sup> in early 2005, and eventually zero MPD published in 2008 [27]. The blocking voltage of SiC GTOs is dependent upon the thickness and doping concentration of the drift layer. As the recent improvements in the growth process of the thicker epilayer, the blocking voltage has been steadily increases from 5 kV in 2003, 6 kV in 2007 to 9 kv in 2009.

#### **1.3 4H-SiC GTO Fundamentals**

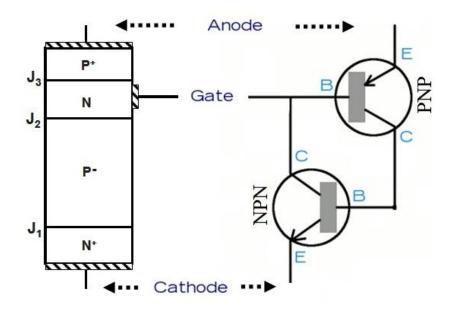

A typical device cross-section of SiC GTO is shown in Fig. 1-5. As a result, unlike silicon GTOs, SiC GTOs have anode on the top and cathode on the bottom. The gate is referenced to the anode. The anode layer is formed by epitaxial growth as in SiC BJTs since ion-implantation of p+ will cause too much damage and reduce the current gain of the PNP transistor.

To turn-on the GTO, the anode is grounded. A negative voltage is applied to the cathode and a gate current (electron current) is injected into the base resulting in the forward biasing of junction  $J_3$  and turning on the upper PNP transistor. Its collector current provides the base current for the lower NPN transistor. The injected electrons

from the cathode region diffuse across the P- drift region and get collected by junction  $J_2$  as the base current of PNP transistor. Once this happens, the two transistors are coupled, the thyristors latches and allows on-state current conduction without the gate signal.

Fig. 1-5 Cross-section of a GTO cell with circuit symbols.

In Fig. 1-5 the current amplification factor of transistor PNP is called  $a_{pnp}$ , and that of transistor NPN,  $a_{npn}$ . If reverse current  $I_{GQ}$  flows through the gate, base current  $I_B$  at transistor PNP is reduced when  $I_{GQ}$  is increased. This relationship can be expressed by the following equation:

$$I_{\rm B} = I_{\rm K} a_{\rm npn} - I_{\rm GO}$$

Eq. 1-1

where  $I_K$  is the cathode current.

On the other hand, hole current  $I_{RB}$ , which disappears due to the recombination in the PNP base layer, can be expressed as follows:

$$I_{RB} = (1 - a_{pnp})I_A \qquad Eq. 1-2$$

where  $I_A$  is the cathode current.

The relationship between GTO anode current  $I_A$  and cathode  $I_K$  current is expressed by the following equation:

$$I_A + I_{GQ} = I_K Eq. 1-3$$

To turn off the GTO,  $I_B$  must be smaller than  $I_{GQ}$ . The magnitude of the reverse-bias current can be calculated by the following equation:

$$I_{GQ} = \frac{a_{PNP} + a_{NPN} - 1}{a_{PNP}} \times I_{K}$$

Eq. 1-4

As can be seen from what has been discussed, it is possible in theory that a GTO can carry out the turn-off if an adequate magnitude of the reverse bias current is supplied to the gate. The most important parameter during the turn-off is the gate resistance since the maximum electron current extracted from the base is dependent on the reverse blocking capability of  $J_3$ . Under this condition, the electron current conducting underneath the anode layer causes a voltage drop along the base resistance which makes  $J_3$  in reverse bias. The maximum gate current is given by Eq. 1-5 [12]:

$$I_{G} = \frac{nV_{GR}}{R_{B}}$$

Eq. 1-5

where  $V_{GR}$  is the breakdown voltage of the gate-anode junction;  $R_B$  is the base resistance. n is a constant which is related to the cell design of the device.

Three important features for SiC GTOs should be noted: (i) the maximum  $I_G$  for SiC is much higher than in Si due to a higher  $V_{GR}$ ; (ii) n-GTO has a much lower maximum gate current than p-GTO due to the much higher p-type base resistance; (iii) the uniformity of the base resistance is crucial to achieving a uniform turn-off of GTO,

especially for big size devices. Since the anode finger is formed by dry etching, the etching rate uniformity will directly affect the base resistance.

#### **1.4 Edge Termination in Power Devices**

Power devices operate at high voltages in the blocking mode. Along the direction of current transport, the space-charge region drops this voltage such that the electric field decreases linearly away from the junction. Under this 1-D approximation, iso-electric field contours are parallel to the junction. But since a power device is of a finite size, edges of the device are formed by cleaving the substrate. If this irregular surface were to be exposed to high electric field, voltage would not be dropped smoothly across the epitaxial layer. So, while the back side (non-junction) contact of a discrete power device covers the entire face, the front side contacts cover a smaller area outside which the potential rises to that at the backside. Hence, the high voltage at the junction also has to be dropped across the surface of the device. If no special "edge-termination" schemes are used, this voltage drops abruptly at the edge, causing a high electric field which leads to the device breakdown well below the parallel plane breakdown limit. So, various electric field termination schemes have been developed to spread the lateral electric field at the edge of the device over a wide enough region such that the lateral breakdown voltage approaches the parallel-plane breakdown voltage [1].

SiC, with its superior properties of the high breakdown field and the high thermal conductivity, is an attractive material for high-power and high-temperature applications. To utilize the high breakdown field in a high-voltage device, an efficient junction termination is needed. Among different high-voltage junction termination techniques, the

multistep junction termination extension (MJTE) has been considered as a preferred method due to its simple design and processing technique [32]. The design and optimization of MJTE for high power SiC devices will be considered in this thesis

#### **1.5** Outline of the Dissertation

In the introduction, material properties of 4H-SiC, 4H-SiC bipolar switching devices research status, and GTO theory are reviewed. In the following chapters of this dissertation aim to further investigate these crucial issues in 4H-SiC power GTO device design and fabrication process, optimize them, and improve the overall performance of 4H-SiC GTOs.

Chapter 2 discusses the details on physics-based 2-D 3-step MJTE design and optimization by using numerical simulation and demonstrates 3-step MJTE for more than 7 kV NPN structure for high power GTOs.

Chapter 3 focuses on the design and simulation of more than 6 kV GTO. Static and dynamic characteristics will be analyzed by 2-D simulation. Then the design of GTO mask sets will be introduced after the discussion of device simulation.

Chapter 4 introduces a detailed process on GTO fabrication from the mesa etch to the metal overlay formation. Then, the dissertation presents and analyzes the static and dynamic characterization of the fabricated devices.

Chapter 5 summarizes the achievements in this research and the knowledge gained through the technology developed. A discussion on the remaining challenges and suggestions for future work are also given in this chapter.

# CHAPTER 2 DESIGN AND DEMONSTRATION OF MJTE FOR 4H-SiC GTO

The edge termination is a critical technology for power devices. An effective edge termination technique makes the electric field distribution more uniform at the edge of device, in order to approach the ideal breakdown voltage capability of the epitaxial layer used. In the past, various termination techniques, which include field plate (FP) [28], guard ring (GR) [29], multizone junction termination [30] and MJTE [31], have been employed for SiC power devices. High voltage FP techniques are constrained by the need for thick oxide layers to reduce the high oxide field, and are often limited to less than 2 kV to ensure a reliable operation. The disadvantage of GR based devices is that they need accurately optimized ring spacing. In comparison to the multizone ion implantation, which requires a multistep implantation for the edge termination, the MJTE could be advantageous since no extra implantation step is needed when utilized in SiC devices with an implanted anode structure, and the extra dry etch steps can be performed by using AlTi as the etch mask, a process that is much simpler in comparison to the process for multistep ion implantation. Among all of these edge termination structures, the MJTE has become one of preferred methods due to its simple design, processing technique, and ability to achieve close to 100% of the ideal parallel junction breakdown voltage [32]. However, fundamental studies on the edge termination structure for such high voltage devices (more than 6 kV) are still limited. The effects of reducing the electric field crowding should strongly depend on the JTE etching depth. To study the effect of different etching depths of 3-step MJTE on breakdown voltage and to optimize the design, 2-D device simulation have been carried out by using Synopsys Sentaurus [33] and

compared with experimental results. In addition, by employing the 3-step MJTE, a more than 6 kV 4H-SiC GTO is experimentally demonstrated, which will be introduced in following chapters.

#### 2.1 Junction Termination Extension (JTE)

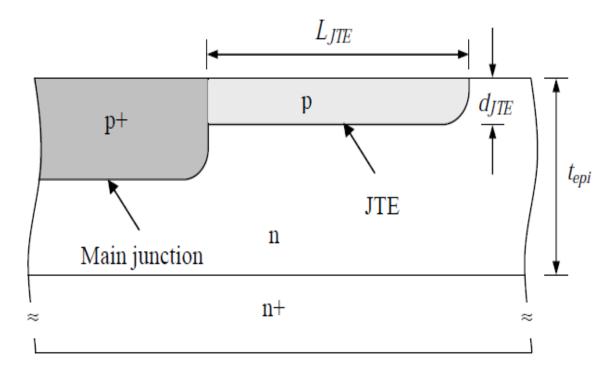

The junction termination extension (JTE) technique [34] can give almost parallel plane breakdown voltage (up to 95%). It is convenient, because no complicated photolithography steps are needed and the amount of introduced charge can be precisely controlled by ion implantation. The JTE region should be totally depleted at the required blocking voltage applied. Key parameters of The JTE are length  $L_{JTE}$ , depth  $d_{JTE}$ , and doping concentration  $N_{JTE}$ . A schematic view of a p-n junction with the JTE region is shown on Fig. 2-1.

Fig. 2-1 Schematic cross section of a p-n junction with junction termination extension.

The length of the JTE is one design aspect that has a significant effect on the breakdown voltage, and it is important effect on breakdown voltage and thus is important in maximizing the available structure area. Templet et al. [35] has investigated the required JTE length through breakdown experiments with diodes of various extension length, and they have fit their results to the following empirical formula:

$$\frac{V_{BR}}{V_{BR_{ideal}}} = 1 - \exp\left(-\frac{L_{JTE}}{t_{epi}}\right)$$

Eq. 2-1

where the factor ( $L_{JTE}/t_{epi}$ ) is the JTE length normalized to the substrate critical depletion width. Eq. 2-1 is plotted in Fig. 2-2, which indicates that in order to achieve close 100% of the parallel plane breakdown value, the JTE length must be at least four times the substrate depletion width. Our results suggest that the JTE length be extended to about five times  $t_{epi}$ .

Fig. 2-2 Dependence of the breakdown voltage on the normalized JTE length.

The length should be chosen to be larger than the epilayer thickness in order to reduce the field at the surface by supporting the same voltage with a larger depletion width. However, it should not be much larger than the epilayer thickness in order to save valuable wafer space. The implanted dose D:

$$D = N_{JTE} \times d_{JTE}$$

Eq. 2-2

is determined by the maximum electric filed and it is equal to:  $(\mathcal{E}_s \cdot E_c)/q$ . If we express it in terms of the epilayer parameters it is:

$$D = N_D \times t_{epi}$$

Eq. 2-3

where  $N_D$  and  $t_{epi}$  are the epilayer doping and thickness respectively. Once we choose the dose, we can decide about  $d_{JTE}$  and  $N_{JTE}$ . Numerical analysis shows that for a given doping level of the junction extension, the breakdown voltage increases and then decreases, going through a maximum when the depth of the junction extension increases [36,37].

One problem with the JTE structure in SiC is the uncertainty in dopants activation, which can lead to ineffectiveness of the termination. A practical approach to realize a JTE structure is to implant it and then remove as much of the implanted thickness as needed to achieve the right charge balance. This reduces the number of photomasks needed, eliminates the uncertainty in the dopant activation efficiency, as the actual JTE charge can be adjusted by etching after implantation and dopant activation. A multiple-zone JTE structure is more effective than a single-zone JTE. The different zones are formed by additional etching steps.

In the multiple-zone JTE fabrication, the key step is to achieve an accurate dose of the implanted charge that becomes completely depleted close to the surface at the desired breakdown voltage, thereby reducing the maximum electric field in the edge region. However, any implantation step is strongly dependent on the activation of implanted dopants that can differ with the annealing temperature and time. Furthermore, defect generation during implantation and surface degradation during the post-implantation annealling affect the device performance.

In this chapter, a mesa-etched 3-step MJTE with different etching depth has been designed and demonstrated by controlled etching into the epitaxially grown p-doped layer as a modification to the implanted etched JTE termination. Although this method is based on a precise etch-depth control and can be affected by variations in thickness and doping profile of the epitaxial layer, it may provide a less sensitive processing technique by introducing 3-step MJTE that can act as a controlling tool for compensation of any possible variation in the processing condition.

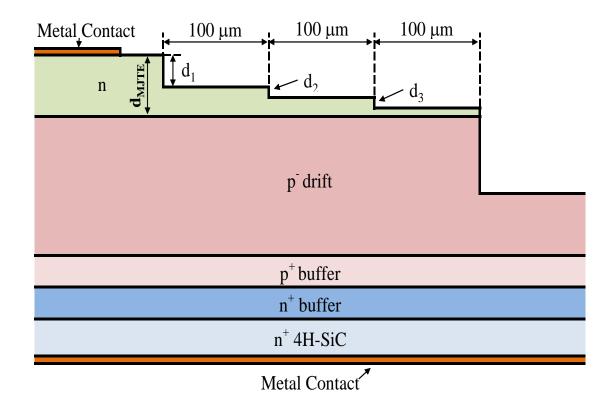

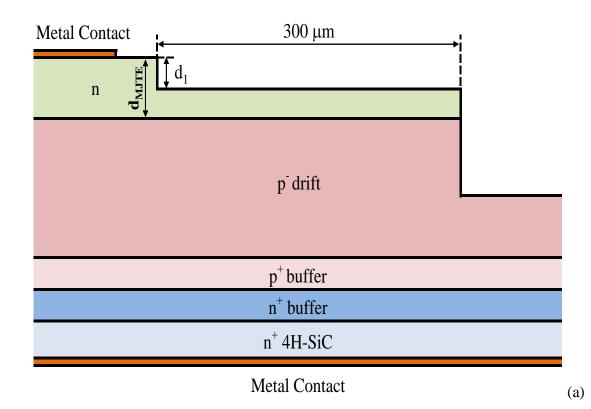

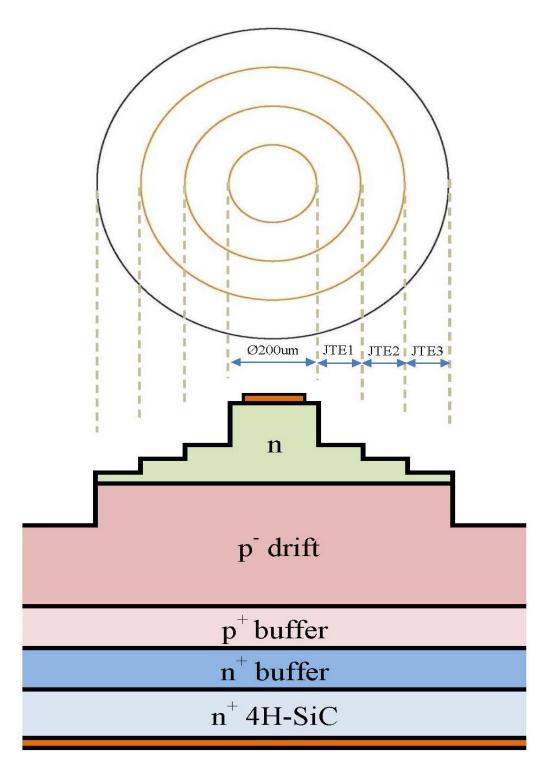

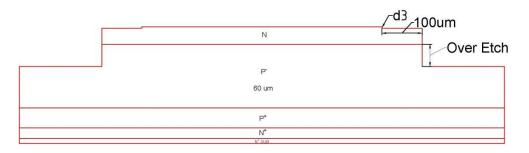

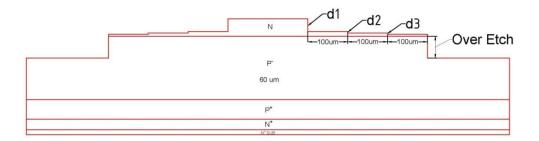

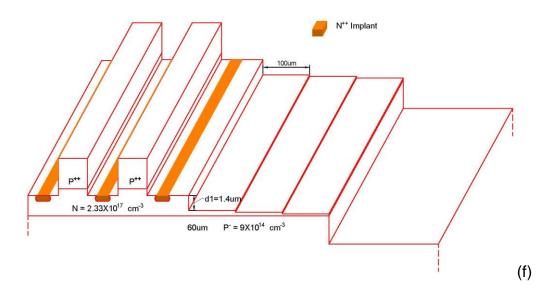

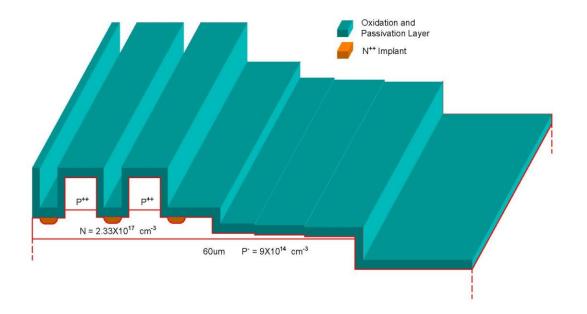

#### 2.2 Design of 3-Step MJTE

A typical device cross-section of a NPN structure with 3-step MJTE is shown in Fig. 2-3.  $d_1$ ,  $d_2$  and  $d_3$  are etching depths for JTE1, JTE2 and JTE3, respectively. Each JTE step has been designed of the same length of 100um. As shown in Fig. 2-3, the NPN structure was designed on an n<sup>+</sup> 4H-SiC substrate. The first layer on n<sup>+</sup> 4H-SiC substrate is an n<sup>+</sup> buffer. Next, a high doping p type buffer layer has been designed in order to form a punch-through structure. The above p drift layer of 60 µm thick doped to  $9x10^{14}$  cm<sup>-3</sup> is used to support the high blocking voltage. Finally, n-type layer with the thickness of  $d_{MJTE}$  is on the top of the p<sup>-</sup> drift layer. Two metal contacts were designed on top n-type layer and bottom n-type substrate, respectively.

The etching depths of MJTE prove to be the most critical, since etching depths can control the charge distribution and therefore alleviate electric field crowding at the edge of the junction. The optimum etching depths of each MJTE step need to be determined by two steps: (1) 2-D device simulation and (2) experimental verification.

Fig. 2-3 Schematic cross-section of a NPN structure with 3-step MJTE.

#### 2.3 Simulation of 3-Step MJTE

### 2.3.1 Breakdown Voltage

• 1-step JTE

The simulation was conducted from single step JTE structure, which is shown in Fig. 2-4 (a). With a single step 300µm long JTE, it is not possible to independently control

both the peak bulk field and the peak surface field because the charge in the 1-step JTE zone is too far from the point of peak curvature field to have a maximal effect. As shown in Fig. 2-4 (b), 1-step JTE NPN structure can reach the breakdown voltage of 5.7 kV, which is below 0.8 fraction of the ideal breakdown voltage of 8.4 kV, at the optimum point. Since a further reduction in the JTE charge to decrease the peak surface field would result in a significant lost in the blocking voltage for 1-step JTE structure, it is necessary to design a new structure with more than one JTE steps to allow further control of the peak field without compromising the breakdown voltage.

Fig. 2-4 1-step JTE structure cross section view and the breakdown voltage as a function of extents on etching depth  $d_1$ .

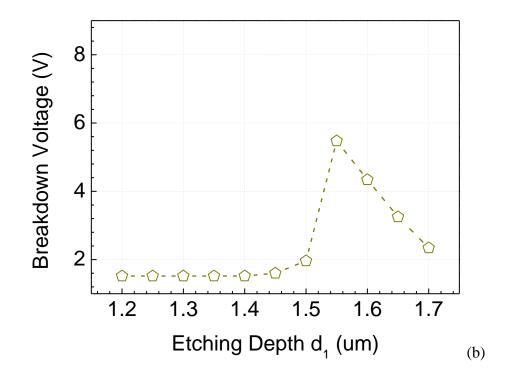

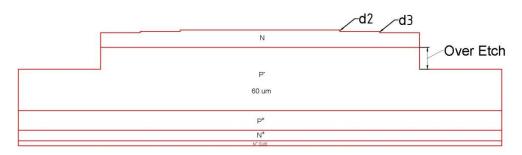

• 2-step JTEs

Single step JTE structure is not possible to independently control both the peak bulk field and the peak surface field of a high voltage device. Hence, 2-step MJTEs, as shown in Fig. 2-5 (a) has been designed to continue MJTE studying. 2-step MJTEs show over 95% ideal breakdown voltage at  $d_1 = 1.4 \ \mu m$  and  $d_2 = 0.14 \ \mu m$ , which indicates that the JTE2 has been fully depleted prior to the designed breakdown voltage, moving a second peak field to the junction of JTE1 and JTE2, thereby reducing the overall surface field.

Fig. 2-5 2-step JTE structure cross section view and the breakdown voltage as a function

of extents on etching depth  $d_1$ .

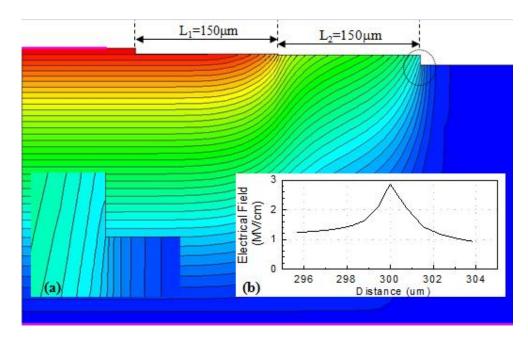

It should be pointed out that 2-step MJTE, like 1-step JTE, is sensitive with respect to d<sub>1</sub>, which plays a major role in control of the charge distribution in MJTE.  $\pm$ 5% variation of optimum etching depth d<sub>1</sub> will result in a premature breakdown either at the outmost JTE edge or at the corner of the main junction. Fig.2.6 shows the simulated equipotential lines at a reserve voltage of 7 kV on a 2-step MJTE with the optimum design and Fig. 2-6 (a) shows details at the encircled resign with the equipotential lines starting to curve at the MJTE edge. Accordingly, Fig. 2-6 (b) shows the high field of almost 3MV/cm at the edge of 2-step MJTE, which indicates there is no too much room for improvement for 2-step MJTE with high blocking capability by tuning the etching depth. However, the surface filed and leakage current, while reduced, are not particularly well controlled for 2-step MJTE with less than 0.1 µm safe window in the actual process to have over 80% ideal breakdown voltage as shown in Fig. 2-5

Fig. 2-6 Simulated equipotential lines (pitch: 200V) for 2-step MJTE with  $d_1 = 1.4 \mu m$  and  $d_2 = 0.14 \mu m$ . Insert (a) and (b) are details and field distribution at the encircled region.

3-step JTEs

The 2-step MJTE design can't offer enough room in actual fabrication. Hence, it is necessary to develop 3-step MJTE to increase process windows, especially for JTE1 etching depth  $d_1$ . Table 2-1 lists the key parameters for MJTE design:

| Step   | Length                          | Depth                        |

|--------|---------------------------------|------------------------------|

| 1-step | $L_1 = 300 \ \mu m$             | $d_1; d_2 = d_3 = 0 \ \mu m$ |

| 2-step | $L_1 = L_2 = 150 \ \mu m$       | $d_1; d_2; d_3 = 0 \ \mu m$  |

| 3-step | $L_1 = L_2 = L_3 = 100 \ \mu m$ | $d_1; d_2; d_3$              |

Table 2-1 Key parameters for MJTE design

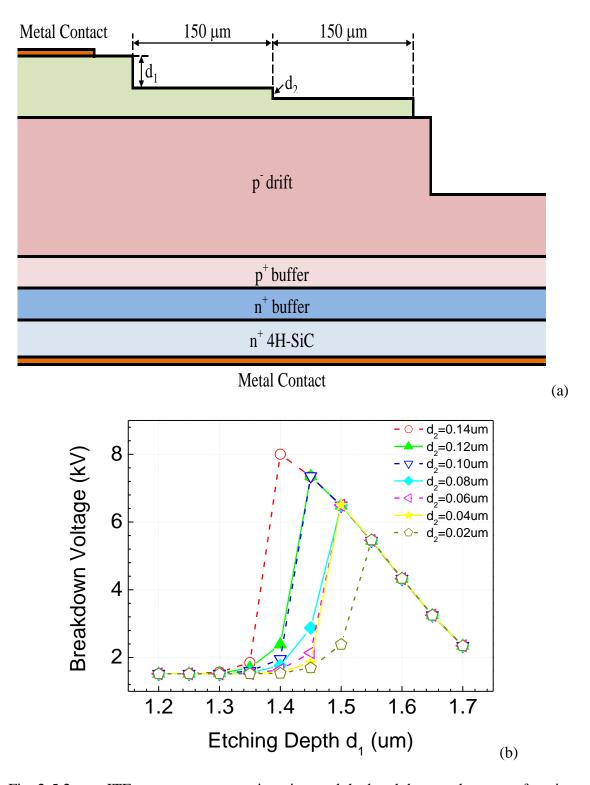

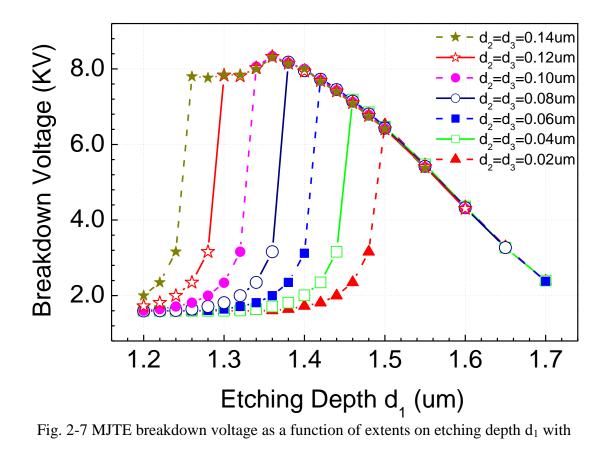

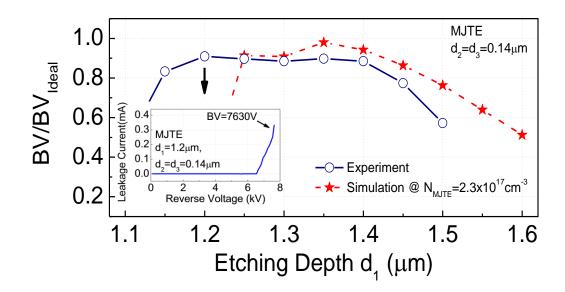

Fig. 2-7 shows the simulated breakdown voltage of the NPN structure with 3-step MJTE as the function of extents on etching depth  $d_1$  for different etching depths of  $d_2$  and  $d_3$ , and indicates that the broad MJTE etching depth  $d_1$  window can be achieved by increasing the value of  $d_2$  and  $d_3$ . For  $d_2 = d_3 = 0.08 \mu m$ , the breakdown voltage increases, and reaches the maximum value of 8.2 kV (97% of ideal value) at  $d_{JTE1} = 0.42$  um, then decreases sharply with increasing JTE1 thickness  $d_{JTE1}$  ( $d_{JTE1} = d_{MJTE} - d_1$ ). The narrow optimum MJTE depth window makes a big obstacle in the real devices fabrication, since it is difficult to shoot this peak point. Although the etching depth can be precisely controlled, the dopant profile is not totally constant through the epitaxial n-layer. In addition, the electric field distribution in the MJTE region can be perturbed by the fixed charge near the SiC surface as well as inside the passivation layer, which can vary across the wafer. This can result in a variation of the breakdown voltage across the wafer. So the more than 0.8  $\mu$ m etching depth of  $d_2$  and  $d_3$  have been simulated and the optimum

window of etching depth  $d_1$  has be extended. In the case of  $d_2 = d_3 = 0.14 \mu m$ , the range of the optimum etching depth is from 1.26  $\mu m$  to 1.46 m with the breakdown voltage of over 80% of the ideal value, as shown by full stars in Fig. 2-7.

various d<sub>2</sub> and d<sub>3</sub>.

In the MJTE design with  $d_2 = d_3 = 0.14 \ \mu\text{m}$ , the optimum range of  $d_1$  can be about 0.2  $\mu\text{m}$  with the breakdown voltage of over 80% of the ideal value, which is achievable in actual device fabrication. In order to exactly locate the range of the JTE1 etching depth,  $d_1$  was simulated from  $d_1 = 1.1 \ \mu\text{m}$  to 1.7  $\mu\text{m}$  while keeping  $d_2 = d_3 = 0.14 \ \mu\text{m}$ . It is clearly seen in Fig. 2-8 that the breakdown voltage increases, reaches a maximum, and then decreases as the JTE1 etching depth  $d_1$  is increased. The highest breakdown voltage

is 8.3 kV, which is from the design of  $d_1 = 1.36 \ \mu m$  and  $d_2 = d_3 = 0.14 \ \mu m$ . Table 2-2 lists the maximum breakdown voltage and the percent of ideal breakdown voltage of 8.4 kV for the MJTE design with  $d_1$  increasing from 1.2  $\mu m$  to 1.6  $\mu m$  and  $d_2 = d_3 = 0.14 \ \mu m$ .

Fig. 2-8 MJTE determination simulation on the NPN structure at  $d_2 = d_3 = 0.14 \ \mu m$ .

| Table 2-2 Breakdown | voltage and the | e percent of | the ideal | breakdown v | voltage for |

|---------------------|-----------------|--------------|-----------|-------------|-------------|

|---------------------|-----------------|--------------|-----------|-------------|-------------|

| MJTE d | lesign | with | $d_2 =$ | $d_3 =$ | 0.14 | μm |

|--------|--------|------|---------|---------|------|----|

|--------|--------|------|---------|---------|------|----|

| d <sub>1</sub> ( µ m) | 1.20 | 1.25 | 1.30 | 2.35 | 1.40 | 1.45 | 1.50 | 1.55 | 1.60 |

|-----------------------|------|------|------|------|------|------|------|------|------|

| BV (kV)               | 1.7  | 7.6  | 7.9  | 8.2  | 8.0  | 7.3  | 6.4  | 5.3  | 4.2  |

| % of ideal BV         | 20   | 91   | 94   | 98   | 95   | 86   | 76   | 64   | 50   |

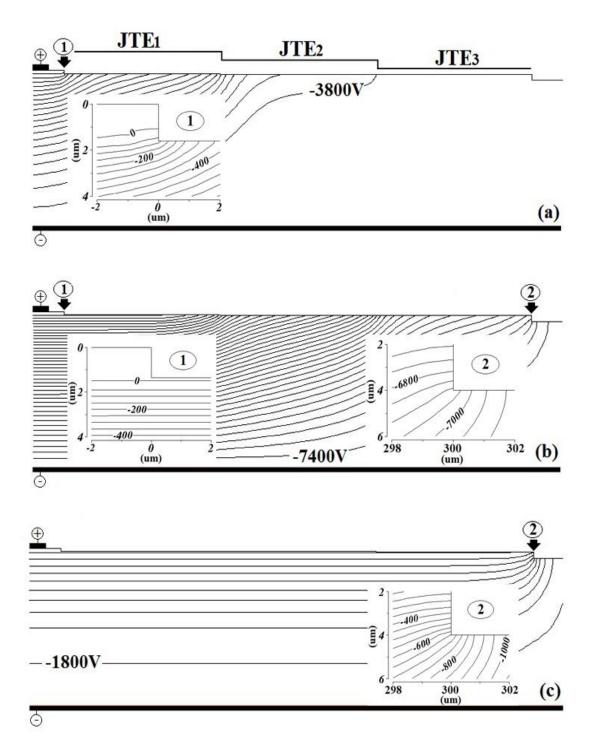

#### 2.3.2 Equipotential Lines

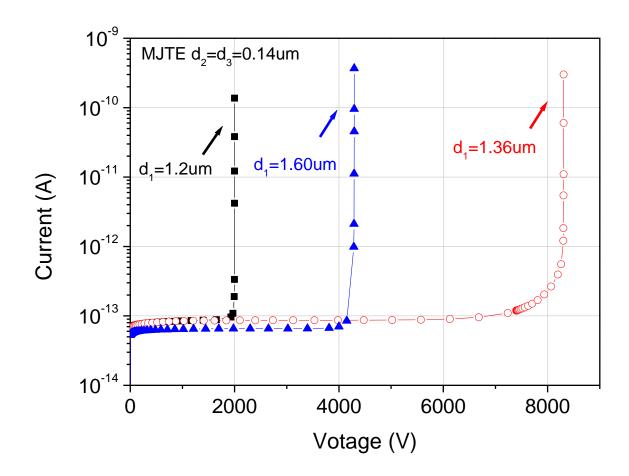

For the case of  $d_2 = d_3 = 0.14 \ \mu\text{m}$ , the breakdown voltage is less than 50% of the ideal value at  $d_1 = 1.6 \ \mu\text{m}$  with  $d_{JTE1} = 0.2 \ \mu\text{m}$ , which is a relatively thin MJTE layer compared to  $d_1 = 1.2 \ \mu\text{m}$  with  $d_{JTE1} = 0.6 \ \mu\text{m}$ . The thin MJTE region completely depletes at the low reverse voltage, and the equipotential lines severely curve at the corner of main junction at point (1) in Fig. 2-9 (a) at which the electric field crowding takes places, hence leads to a premature breakdown.

On the other hand, the thick MJTE layer makes difficult to deplete even in the outmost step of MJTE at high reverse voltages and hence the potential lines are concentrated at the outmost edge of the MJTE region for  $d_1 = 1.2 \mu m$  as shown at point (2) in Fig. 2-9 (c). The electric field crowding is at the outmost edge of the MJTE that involves the device to reach prematurely the blocking voltage, too.

For maximum effectiveness, the charge in the MJTE layer is typically designed by etching depth control so that at the desired blocking voltage, the dopants in the MJTE layer are fully depleted and act as a high resistivity layer in which support the high surface and bulk fields. In the case, the maximum breakdown voltage of 8.3 kV is revealed in the MJTE structure of  $d_1 = 1.36 \ \mu m$ ,  $d_2 = d_3 = 0.14 \ \mu m$ , approaching 100% of the ideal parallel-plane breakdown voltage. Fig. 2-9(b) indicates the high efficiency of MJTE in spreading the equipotential lines near the edge of the junction at 8.3 kV reverse bias.

| Table 2-3 Relation between $d_1$ and $d_{JTE1}$ at $d_2 = d_3 = 0.14 \ \mu m$                                |      |      |      |  |  |

|--------------------------------------------------------------------------------------------------------------|------|------|------|--|--|

| d <sub>1</sub> ( µ m)                                                                                        | 1.20 | 1.36 | 1.60 |  |  |

| $\mathbf{d}_{\mathbf{JTE1}}(\ \mathbf{\mu}\ \mathbf{m}) = \ \mathbf{d}_{\mathbf{MJTE}} \cdot \mathbf{d}_{1}$ | 0.60 | 0.44 | 0.20 |  |  |

Fig. 2-9 Simulated equipotential lines (pitch: 200V) at 90% breakdown voltage for 3-step MJTE NPN structures with  $d_2 = d_3 = 0.14 \ \mu m$  and (a)  $d_1 = 1.2 \ \mu m$ ; (b)  $d_1 = 1.36 \ \mu m$  and (c)  $d_1$

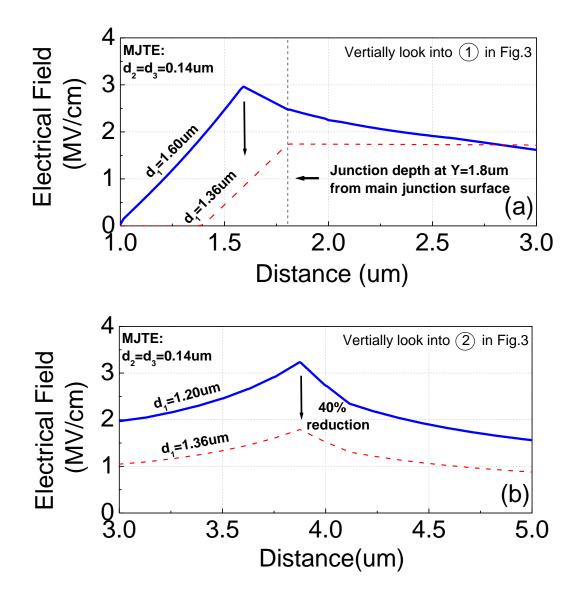

## 2.3.3 Electric Field

The successful application of the solid state technology to power control required the development of GTOs capable of operating at a high voltage. It is apparent that it is necessary to design edge terminations which promote the bulk breakdown. 3-step MJTE has been designed and simulated in the previous sections. For a non-optimum design, equipotential lines were curved at the corner of the main junction or at the outmost edge of the MJTE region, at which the electric field crowding takes place. The high surface field in high voltage 4H-SiC devices can lead to the excess leakage and a premature breakdown at the surface of the devices.

Fig. 2-10 shows the electric field distribution observed vertically from points of (1) at  $X = 0 \ \mu m$  and (2) at  $X = 300 \ \mu m$  in Fig.2.9, respectively. The optimum design with  $d_1 = 1.36 \ \mu m$  and  $d_2 = d_3 = 0.14 \ \mu m$  can independently control both the peak bulk field and the peak edge field. Compared with the  $d_1 = 1.6 \ \mu m$  design, the optimum designed 3-step MJTE effectively suppress the peak electric field at the main junction edge from 3 MV/cm to 1 MV/cm, which is about 60% of the value of the peak bulk electric field on the optimum design as shown in Fig. 2-10 (a). Hence, the breakdown voltage can be increased by about 100% from 4.3 kV at  $d_1 = 1.6 \ \mu m$  to 8.3 kV at  $d_1 = 1.6 \ \mu m$ .

In contrast to the  $d_1 = 1.2 \ \mu m$  design, as shown in Fig. 2-10 (b), the optimum design provides a balanced electric-field at both the inner and outer edges of the 3-step MJTE and significantly reduces the peak electric field at the outmost edge of MJTE by 40%, where JTE<sub>3</sub> is fully depleted prior to the designed breakdown, moving the peak field into the junction of JTE<sub>2</sub> and JTE<sub>3</sub> and then the junction of JTE<sub>1</sub> and JTE<sub>2</sub>, thereby reducing the overall peak surface field and resulting in nearly the ideal breakdown voltage.

Fig. 2-10 The electrical field is observed vertically (a) along the main junction edge at  $X = 0 \mu m$  and (b) along the outmost edge of MJTE at  $X = 300 \mu m$ .

## 2.4 Mask Layout for the NPN Structure

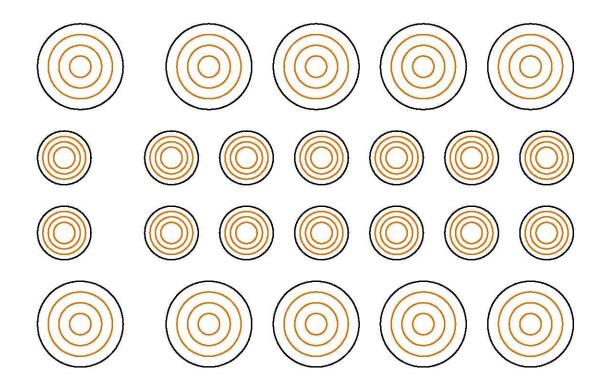

The 3-step MJTE test cells were designed as single-mesa concentric circular NPN structures. There are 4 layer masks for MJTE test cell fabrication, including ISOLATION mask, JTE1 mask, JTE2 mask and JTE3 mask. Detailed fabrication steps will be introduced in the next section.

There are two types of 3-step MJTE cells. Both type cells have the same innermost JTE diameter of 200 µm. The small cell has 50 µm JTE step length and 500 µm outer diameter; the large one has 100 µm JTE step length and 800 µm outer diameter cell. Fig. 2-11 shows one group of the circular NPN structures. Large cells are designed at the outside two rows and small ones are drawn at the central two rows. Detailed dimension for a single cell is illustrated in Fig. 2-12. Correspondingly, the cross sectional diagram of the circular structures is demonstrated at the bottom part of Fig. 2-12.

Fig. 2-11 A group of JTE testing concentric circular NPN structures. The innermost JTE diameter is 200 μm. The length of a JTE step is 50 μm for smaller cells and 100 μm for larger cells. The outmost blue rings on each cell are isolation mask layer

Fig. 2-12 Top and cross-sectional view of a circular NPN structure with MJTE. For small cell,  $JTE_1 = JTE_2 = JTE_3 = 50 \ \mu m$ ; For large cell  $JTE_1 = JTE_2 = JTE_3 = 100 \ \mu m$ .

## 2.5 Fabrication of the NPN Structure with MJTE

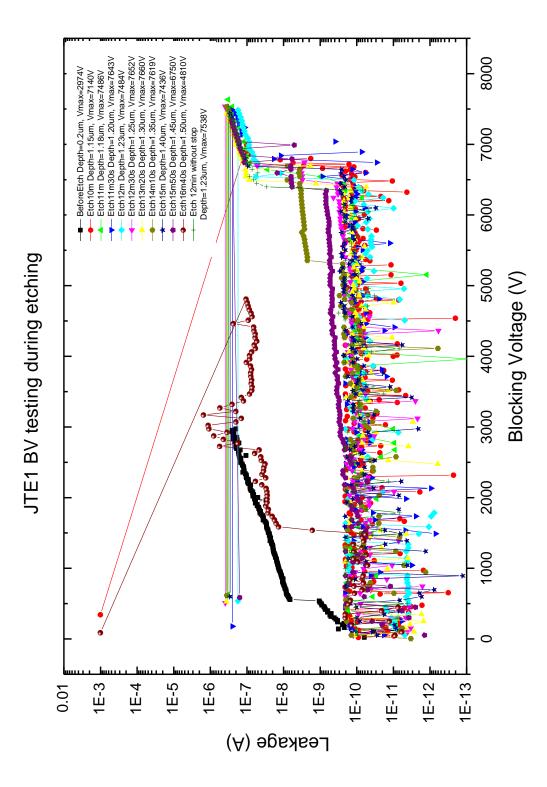

Based on the above simulation results, the mask layout for the NPN structure with 3step JTE has been designed. The total MJTE length is 300  $\mu$ m with 100  $\mu$ m or 150  $\mu$ m with 50  $\mu$ m for each step length, as shown in Fig. 2-12. All of the 4H-SiC samples used in the current experiments have been cut from the same N- type 4H-SiC substrate with 60 $\mu$ m P- drift layer of 9x1014cm-3 doping, which has been designed for GTO devices and purchased from Cree, Inc. N<sub>MJTE</sub> = 2.3 x 10<sup>17</sup> cm<sup>-3</sup> has been selected as the target of the doping concentration for the MJTE layer. The MJTE region has to be thinned down by dry etching in order to achieve the charge balance that will yield the desired field suppression at the device periphery. First, the outer two steps have been etched with d<sub>2</sub> = d<sub>3</sub> = 0.14  $\mu$ m. Next, the innermost step depth d<sub>1</sub> was gradually increased by repeated Inductively Coupled Plasma (ICP) etching in CF4+O2 plasma, while the reserve I-V characteristics have been monitored at every etching run.

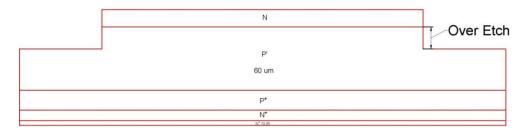

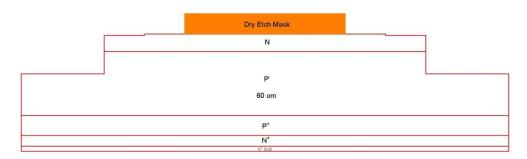

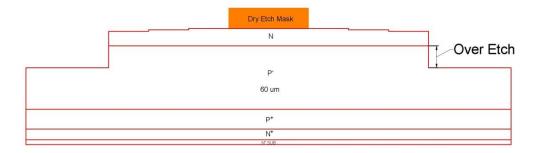

The major fabrication steps for the NPN structure with MJTE are as follows (Fig. 2-13):

- Wafer cutting and cleaning (Fig. 2-13 (a))

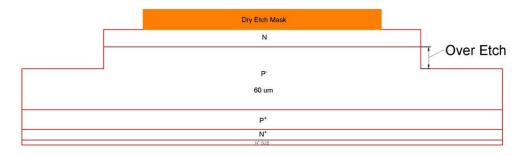

- Lithography, metal Sputtering and wet etching for isolation dry etch mask formation (Fig. 2-13 (b))

- ICP dry etch to form isolation mesa of the NPN structure (Fig. 2-13 (c))

- Lithography, metal Sputtering and wet etching for JTE3 dry etch mask formation (Fig. 2-13 (d))

- ICP dry etch to form JTE3 of the NPN structure (Fig. 2-13 (e))

- Lithography, metal Sputtering and wet etching for JTE2 dry etch mask formation (Fig. 2-13 (f))

- ICP dry etch to form JTE2 of the NPN structure (Fig. 2-13 (g))

- Lithography, metal Sputtering and wet etching for JTE1 dry etch mask formation (Fig. 2-13 (h))

- ICP dry etch to form JTE1 of the NPN structure (Fig. 2-13 (i))

| Ν           |  |

|-------------|--|

|             |  |

| P           |  |

| 60 um       |  |

|             |  |

| <br>P*      |  |

| N*<br>N*SUB |  |

(a) Wafer cutting and cleaning

|   | Dry Etch Mask       |  |

|---|---------------------|--|

|   | Ν                   |  |

|   |                     |  |

|   | P'                  |  |

|   | 60 um               |  |

|   | p <sup>+</sup>      |  |

| - | Р<br>N <sup>+</sup> |  |

|   | N* SUB              |  |

(b) Dry etch mask formation for Isolation

(c) Isolation mesa of NPN structure formation

(d) Dry etch mask formation for JTE3

(e) JTE3 of NPN structure formation

(f) Dry etch mask formation for JTE2

(g) JTE2 of NPN structure formation

(h) Dry etch mask formation for JTE1

(i) JTE1 of NPN structure formation

Fig. 2-13 (a)-(i): Fabrication steps of MJTE with the NPN structure.

# 2.6 MJTE Optimization

The MJTE structure has been optimized on a separate test samples. The MJTE structure has three stages, including JTE1, JTE2 and JTE3, each stage 100  $\mu$ m wide. The depths of outer two JTE stages were 0.14um each. The depth of the innermost step has been gradually increased by repeated ICP etching while the reversed I-V characteristics have been monitored at every etching run. The results are shown in Fig. 2-14. The optimum blocking voltage/reverse leakage corresponded to about 1.3  $\mu$ m etching depth for innermost JTE step. For MJTE steps etching were done with AlTi etching masks of 6000 Å in thickness patterned by photolithography and standard Al etchant.

Fig. 2-14 Reverse I-V characteristics of NPN structure with 3-step MJTE measured at different stages of the JTE determination process.

Fig. 2-15 represents the dependence of the experimental normalized breakdown voltage on the etching depth  $d_1$ , measured at room temperature. Open circles denote the experimental results for 3-step MJTE with  $d_2 = d_3 = 0.14 \ \mu\text{m}$ . The maximum blocking voltage of 7630 V is obtained, which approaches 90% of the breakdown voltage of the corresponding ideal parallel-plane junction. The result of experiment indicates that the depth of  $d_1$  has a broad window from 1.15  $\mu$ m to 1.45  $\mu$ m with breakdown voltage over 7 kV (more than 80% of the ideal breakdown voltage), which means the design of 3-step MJTE has enough tolerant window for actual devices fabrication.

Fig. 2-15 Simulated and experimental normalized breakdown voltage as a function of extents on etching depth d<sub>1</sub>. The ideal breakdown voltage is 8.4 kV.

The simulated results are also plotted in the same figure. The experimental results showed a good agreement with the simulated results. The difference between the simulated results and experimental results may be due to the facts that the actual doping concentration of the blocking layer is different from its specification value and the actual MJTE implantation profile is different from the doping profile used in the simulations.

# 2.7 Summary

Using 2-D numerical simulations, 3-step MJTE techniques for 4H-SiC power devices have been investigated. Compared with 1- and 2-step MJTE, the 3-step MJTE design can improve the blocking performance, balance electric-field, and decrease the sensitivity of the breakdown voltage to JTE etching depth while keeping the total JTE length constant. The simulation results were confirmed by the fabrication of 3-step JTE NPN structure with the maximum blocking voltage of 7630V, which is 90% of the ideal breakdown voltage. The design methodologies discussed in this study are believed to be useful in designing the edge terminations structures for other range of the breakdown voltage.

# CHAPTER 3 DESIGN OF 4H-SiC GTOs

High power systems require robust power switches to operate at high temperatures to meet the demand for smaller and higher power density systems. 4H–SiC has unique material properties that enable it to be far superior to silicon (Si). Benefits of 4H–SiC compared to Si include three times wider band gap (3.2 eV), ten times higher critical field ( $3.0 \times 10^6 \text{ V/cm}$ ), and three times higher thermal conductivity (4.9 W/cm K) [3,4]. Compared to other devices made on SiC, such as BJTs, JFETs, MOSFETs, and IGBTs, SiC GTOs are the favorable devices for pulsed power applications due to their ability to operate at high current and high voltage levels, which is attributed to conductivity modulation in the drift layer of the device. Furthermore, SiC GTOs offer several advantages over Si thyristors and Si GTOs such as compactness, higher current density, faster switching, and higher temperature operation.

The considerable improvement of materials quality and the refinement of fabrication process resulted in the remarkable increase in the blocking voltage of SiC GTOs from below 1 kV to over 10 kV [26, 38, 39, 40]. For a current density of 500 A/cm<sup>2</sup>, the GTO (fabricated at Rutgers University) shows a forward on-state voltage of 5.74 V at the room temperature. The GTOs have also demonstrated fast switching and high current capability. In addition to the blocking voltage, total current, and switching time, the on-state voltage drop V<sub>F</sub> and the current density that can be turned off are two of the important parameters characterizing the performance of GTOs. In this chapter, the design of more than 6 kV 4H-SiC GTOs will be presented, which includes the 4H-SiC GTO structure design, simulation of static and dynamic characteristics. The GTO mask design will be considered in the last part of this chapter.

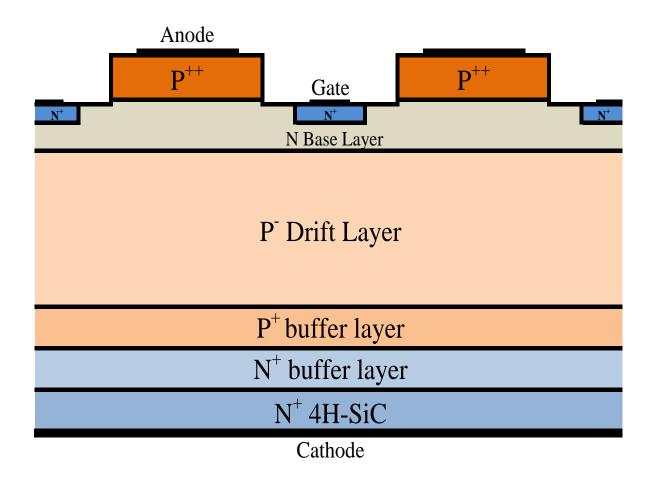

## **3.1 Design of the GTO Structure**

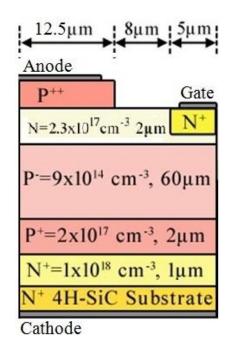

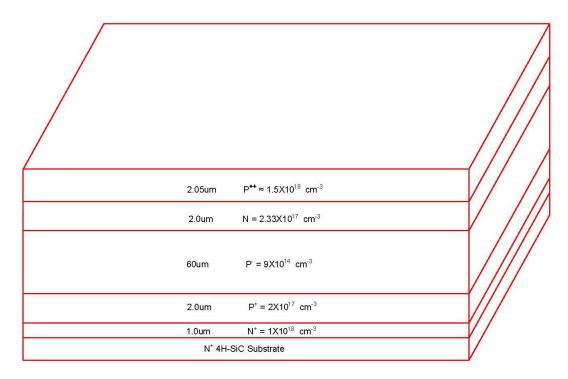

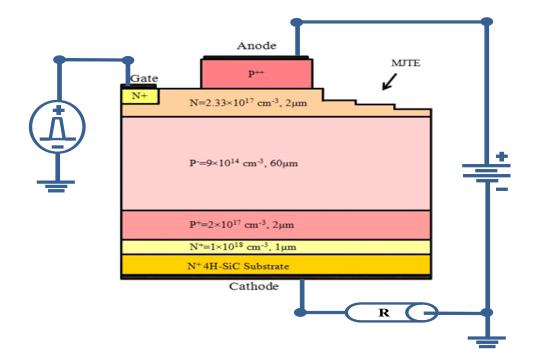

Fig. 3-1 shows the NPNP device structure grown on an n+ 4H-SiC substrate. As a result, unlike silicon GTOs, the SiC GTOs have the anode on the top and the cathode on the bottom. All the epilayers were grown in a single run and designed for a high turn-on gain. The device has an asymmetrical structure with the blocking in the forward direction only. A fine pitch design is used to facilitate high di/dt and dv/dt performances required for pulsed power applications.

Fig. 3-1 Cross-sectional view of 60 µm the 4H-SiC GTO structure

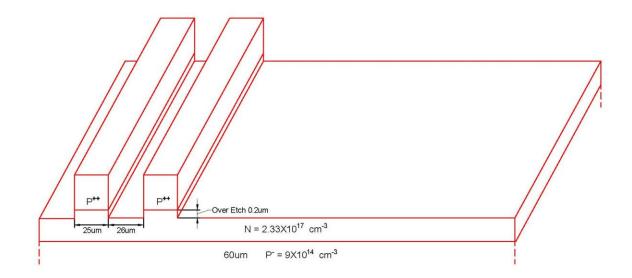

A 60  $\mu$ m thick, lightly doped (N<sub>A</sub> = 9x10<sup>14</sup> cm<sup>-3</sup>) P-base layer is used to achieve high blocking voltage (more than 6 kV). The GTOs are terminated by a three-zone, N-type junction Termination Extension (JTE). Fabrication details on MJTE have been introduced in the previous chapter. The control gate was formed on the n-based layer, and anode and cathode were formed on the p<sup>++</sup> top layer and n<sup>+</sup> substrate, respectively.

The top  $p^{++}$  layer should be doped as high as possible (>  $1x10^{19}$  cm<sup>-3</sup>), so as to increase the emitter efficiency of the pnp transistor as well as the ohmic contact quality. The thickness can't be too thin. Otherwise the contact metal might spike through to the beneath n layer and cause a problem. A 2 µm thick  $p^+$  layer is chosen here. Increasing the  $p^{++}$  layer thickness further only increases the series resistance and is not good.

The n-base layer thickness and doping concentration have to be in the right range. If the thickness is too large or the doping concentration is too high, the emitter efficiency (or current gain) is low and it might be difficult for the GTO to turn on. If the thickness is too small or the doping concentration is too low, the depletion region might punch trough to the top  $p^+$  layer when the device is working in the forward blocking state, and the GTO forward blocking capability is reduces. The thickness and doping concentration are chosen here to be 2 µm and doping concentration of  $2.3 \times 10^{17}$  cm<sup>-3</sup>, respectively. We will see in the later sections that this choice is experimentally proven to be appropriate.

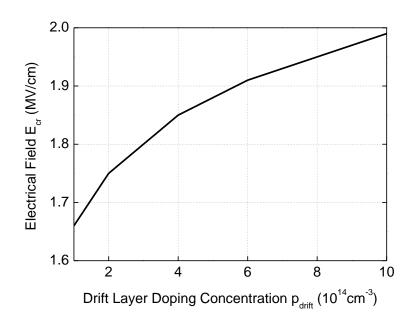

The doping and thickness of the drift layer are determined by the device blocking voltage. For 4H-SiC, the dependence of the critical field on the doping concentration can be described as Eq. 3-1 [42]. The dependence of the critical field on the doping concentration is shown in Fig. 3-2.

$$E_{\rm cr} = \frac{2.49 \times 10^6}{1 - \frac{1}{4} \log_{10}(\frac{p_{\rm drift}}{10^{16}})}$$

Eq. 3-1

Fig. 3-2 Dependence of the critical field on the drift layer doping concentration

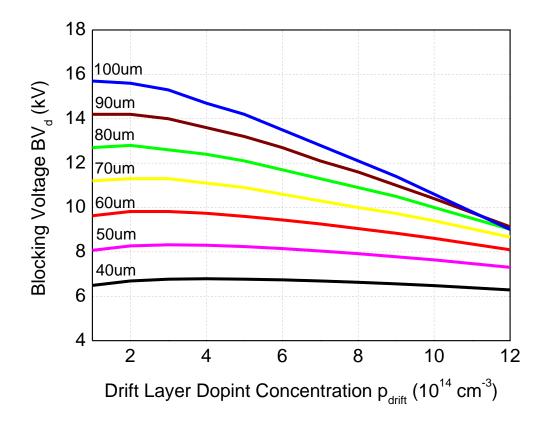

Ignoring the effect of the current spreading layer on the breakdown voltage, the breakdown voltage  $V_{PT}$  determined by the critical field and the drift layer doping concentration is obtained as in Eq. 3-2 [12]:

$$\mathbf{BV}_{\mathrm{d}} = \frac{E_{\mathrm{cr}}W_{\mathrm{d}}}{2} \left(\frac{2W_{\mathrm{cr}} - W_{\mathrm{d}}}{W_{\mathrm{cr}}}\right)$$

Eq. 3-2

where  $W_d$  is the drift layer thickness;  $W_{cr}$  is the depletion width at the critical field with uniform doping  $p_{drift}$ , which is given by

$$W_{cr} = \frac{\varepsilon_0 \varepsilon_{SiC} E_{cr}}{q p_{drift}}$$

Eq. 3-3

The dependence of the breakdown voltage on the drift layer doping concentration is obtained from Eq. 3-5 and Eq. 3-2 as shown in Fig. 3-3. It indicates that for more than 8 kV GTOs, the drift layer should be doped as low as  $p_{drift} < 1.2 \times 10^{15} \text{ cm}^{-3}$ . A 60 µm thick, lightly doped (N<sub>A</sub>=9x10<sup>14</sup> cm<sup>-3</sup>) P-base layer was selected for more than 6 kV GTOs.

Fig. 3-3 Dependence of the critical field on the drift layer doping concentration

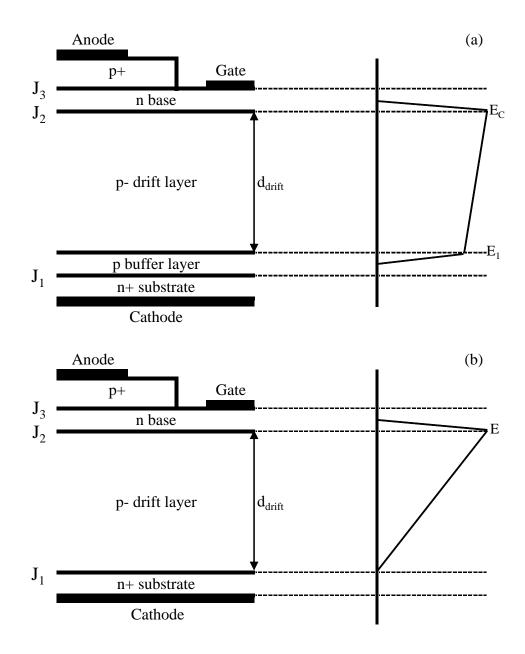

The p buffer layer used to make electric field profile in the blocking layer more uniform and the thyristor blocking voltage can be increased. The difference between GTO structures with/without a p buffer layer is shown in Fig. 3-4. For the structure shown in Fig. 3-4 (b) to have the highest blocking voltage for a given blocking layer thickness,  $d_{drift}$  the blocking layer doping concentration,  $p_{drft}$ , has to be chosen to make the electric field at the blocking junction close to the critical field  $E_{cr}$  and at the same time let the depletion region reaches the  $n^+$  substrate. The blocking voltage is then roughly equals to [41]:

$$V_{\rm B} = \frac{1}{2} \times d_{drift} \times E_{\rm C}$$

Eq. 3-4

For 4H-SiC the critical field dependence on the doping concentration is described by Eq. 3-1 [42]. For the structure shown in Fig. 3-4 (a), with the p buffer layer, the optimal design is somehow different. Here, the doping concentration of the blocking layer should be lower than that of Fig. 3-4 (b), so as to make the field distribution more uniform. The blocking voltage is given by [43]:

$$V_{\rm B} = \frac{1}{2} \times (E_{\rm C} + E_{\rm 1}) \times d_{\rm drift}$$

Eq. 3-5

$E_1$  can be close to  $E_c$ . The blocking voltage of the structure with the p buffer also makes the GTO turn-off easier and turn-on more difficult, since it decreases the gain of the npn transistor. Hence a trade-off has to be made here and the thickness and doping concentration of the buffer layer have to be also in the right range. The p buffer epilayer was designed to have a thickness of 2 µm and doping concentration of  $2x10^{17}$  cm<sup>-3</sup>.

Fig. 3-4 Comparison between two structures: (a) with a p buffer layer, (b) without a buffer layer. The structure (a) can block higher voltage than (b) for the same thickness and doping p-drift layer.

## 3.2 Simulation of GTO

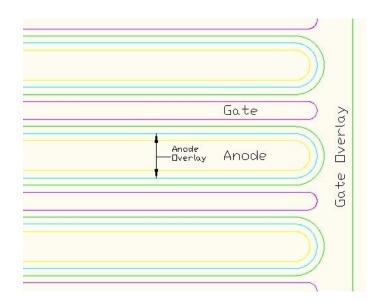

The designed GTO has been simulated by Synopsys Sentaurus [33]. The simulated structure is shown in Fig. 3-5. Each anode finger has a width of 12.5  $\mu$ m. The spacing between anode mesa edge and the gate finger is 8  $\mu$ m and each gate finger has a width of 5  $\mu$ m.

Fig. 3-5 Simulated GTO structure.

# 3.2.1 Static Characteristics

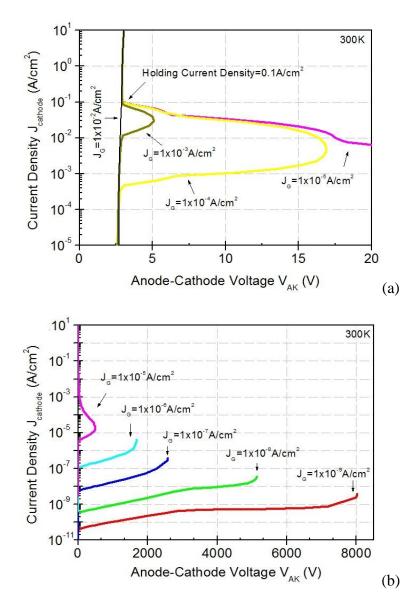

Fig. 3-6 shows the influence of the gate current at the room temperature forward I-V characteristics of 8 kV 4H-SiC GTOs with a minority carrier lifetime  $\tau_{no}$  of 1us. As expected, the forward blocking region shrinks with increase in the gate current. The GTO can block more than 8000 V when the gate current density is  $1 \times 10^{-9}$  A/cm<sup>2</sup>. When it is blocking around 500 V, a gate current density of approximately  $1 \times 10^{-5}$  A/cm<sup>2</sup> is needed to

turn on GTO device. The holding current, which is defined as the current level below which the device is unable to maintain self-sustaining current conduction, is approximately 0.1 A/cm<sup>2</sup>. The GTO latches on with no snap back at gate current density of  $1 \times 10^{-2}$  A/cm<sup>2</sup> yielding an operating current density of more than 500 A/cm<sup>2</sup> at the voltage drop of 3.5 V.

Fig. 3-6 Blocking characteristics of larger than 6 kV 4H-SiC GTO with a minority carrier lifetime  $\tau_{no}$  of 1us at room temperature.

## 3.2.2 Dynamic Characteristics

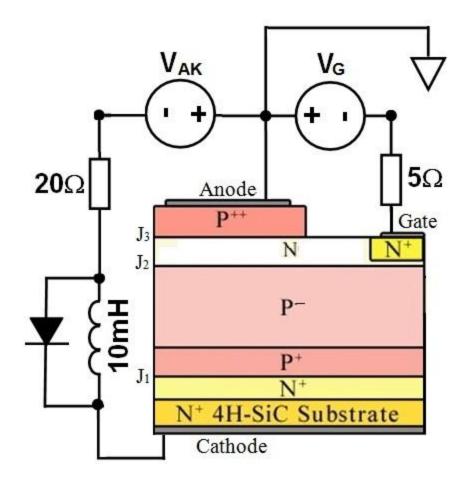

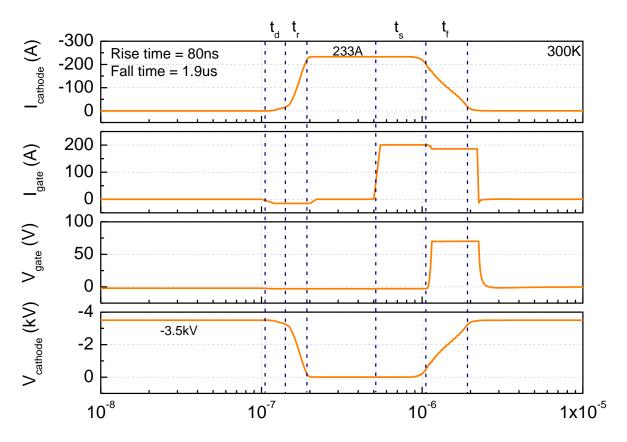

The simulated switching characteristics of the GTO were analyzed by applying the circuit in Fig. 3-7. A gate pulse generator generates series gate pluses which consist of both negative and positive voltage pulses. The negative voltage pulse with a pulse duration of 0.22  $\mu$ s is used to turn on the GTO with an anode to cathode bias of 3500 V, whereas the positive voltage pulse of 1.75  $\mu$ s in duration is used to turn off the device. The interval between these two pulses is 0.28  $\mu$ s. The inductor is used to limit the di/dt rate. The simulation is done at 300 K. The on-state current is limited by 20  $\Omega$  resistance.

Fig. 3-8 shows a set of GTO voltage and current waveforms. These waveforms show the GTO's switching characteristics, such as the turn-on/off delay, turn-on/off time, and voltage drop. These characteristics are important in determining during the actual application.

The GTO can be triggered from the forward-blocking mode to the on-state by the application of a gate drive current. The gate drive current flows from the gate terminal to anode. The voltage drop between P+ anode and N gate due to the gate current flow forward biases the  $J_3$  junction in Fig. 3-7, producing the injection of holes from P+ anode. This does not immediately produce the cathode current flow. The injected holes diffuse through the n-base region in a finite time interval referred to as the delay time  $t_d$ . Once the holes cross the N gate/P drift junction  $J_2$  initiated a current flow through the devices. Consequently, the cathode current begins to flow after a delay time interval, which is about 7 ns.

Fig. 3-7 60 µm 4H-SiC GTO switching testing circuit.

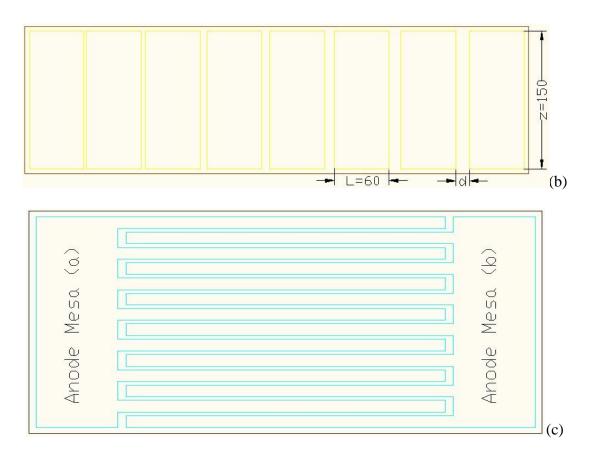

During the turn-on process, a high concentration of electrons is injected into the Pdrift region from the N+ cathode region and a high concentration of electrons is injected into the P-drift region from P+ cathode region. Those will increase the stored carriers in N-base and P-base region. The cathode current will grow exponentially (as shown in Fig. 3-8) to the on-state value after a rise time  $t_r$ , which is about 80 ns. Therefore, the turn-on time at 300 K is  $t_{on} = t_d + t_r = 87$  ns.