©2014

Yang Zhang

ALL RIGHTS RESERVED

### ZINC OXIDE-BASED RESISTIVE SWITCHING DEVICES

by

### YANG ZHANG

A dissertation submitted to the

Graduate School-New Brunswick

**Rutgers, The State University of New Jersey**

In partial fulfillment of the requirements

For the degree of

**Doctor of Philosophy**

Graduate Program in Electrical and Computer Engineering

Written under the direction of

**Yicheng Lu**

And approved by

New Brunswick, New Jersey

OCTOBER, 2014

# ABSTRACT OF THE DISSERTATION Zinc Oxide-based Resistive Switching Devices By YANG ZHANG

**Dissertation Director:**

#### **Prof. Yicheng Lu**

Recently, resistive switching (RS) memory devices have attracted increasing attentions due to their potential applications in the next-generation nonvolatile memory. Zinc Oxide (ZnO) - based RS devices possess promising features, such as well-controlled switching properties by in-situ doping and alloying, low-temperature fabrication processes, superior radiation hardness, and low cost. The goal of the research is to study the feasibility of using the transitional metal (TM) doped ZnO for making RS devices.

The Fe-doped ZnO (FeZnO) is used to make the bipolar and unipolar RS. The FeZnO is grown through MOCVD. Fe is a deep-level donor in ZnO, and Fe doping leads to better device thermal stability and larger value at the high resistance state (HRS) for switching. For the Ag/FeZnO/Pt bipolar RS structures, the ratio of the HRS over the low resistance state (LRS) of  $3.8 \times 10^2$  is achieved. The dominant conduction mechanisms are attributed to the Poole-Frenkel emission at the HRS and Ohmic behavior at the LRS, respectively. A FeZnO/MgO bi-layer (BL) is used to replace the FeZnO single layer (SL) to form an Ag/FeZnO/MgO/Pt bipolar RS structure. This BL device demonstrates a higher  $R_{HRS}/R_{LRS}$  ratio (~10<sup>6</sup>) than the SL counterpart. For the Au/FeZnO/MgO/Pt unipolar RS device, the  $R_{HRS}/R_{LRS}$  ratio of  $2.4 \times 10^6$  at 1V is achieved.

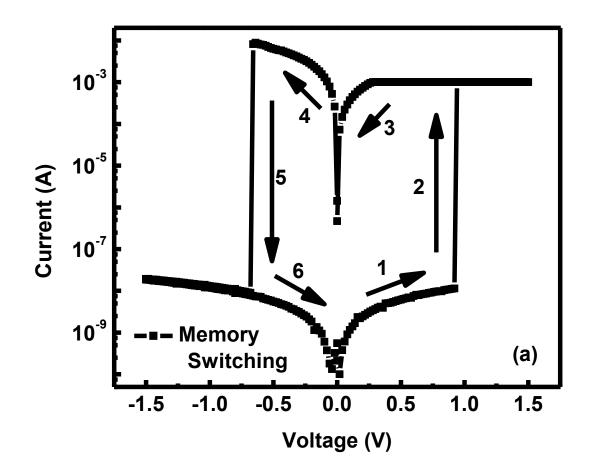

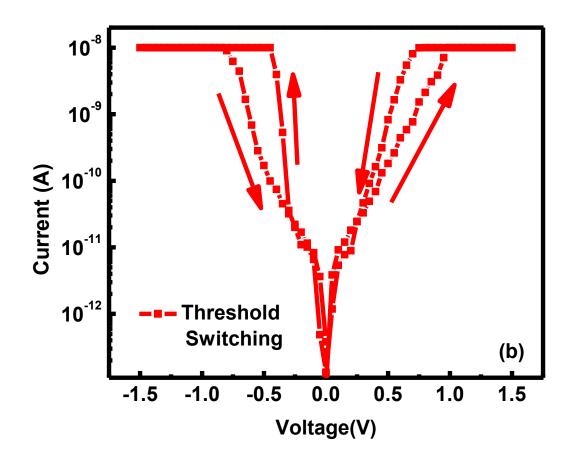

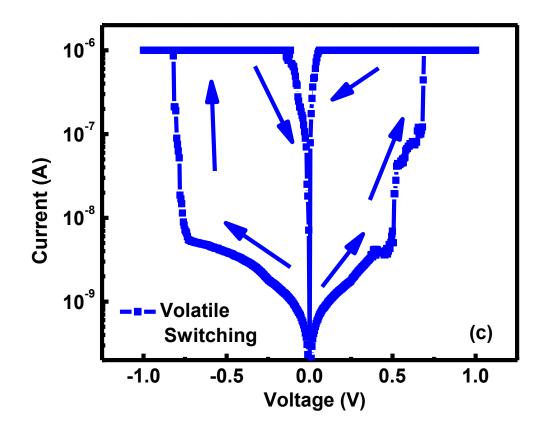

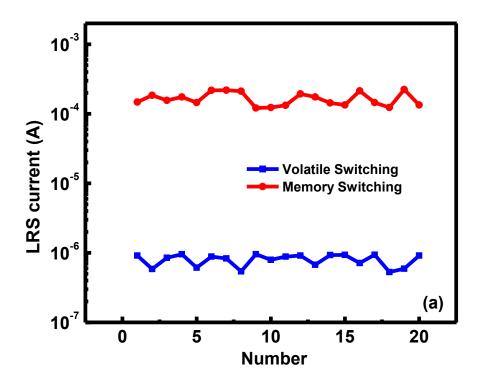

In order to reduce the processing temperature, the Ni-doped ZnO/MgO BL structure is adapted to make the RS devices using the sputtering - MOCVD hybrid deposition. The Ni doping enhances the compensation of oxygen deficiency in ZnO, resulting in larger HRS values. By controlling the compliance current during the "SET" process, three different reversible RS modes, i.e. threshold switching, volatile switching, and memory switching are obtained. Compared with the memory switching, the volatile switching possesses lower power consumption and better HRS stability. Furthermore, the different compliance currents lead to the different LRS values, which could be used for the multi-level per storage cell applications. The electrical characteristics and microstructure analysis suggest that the compliance current setting affects the formation and rupture of the metallic filaments, leading to the conversion of different switching modes.

The FeZnO switching resistor (R) is vertically integrated with a ZnO diode (D) to form the 1D1R structure, which overcomes the cross-talk in the 1R-based crossbar switching matrix. The 1D1R exhibits high  $R_{HRS}/R_{LRS}$  ratio, excellent rectifying characteristics, and robust retention. The new ZnO RS technology presents great impact on the future classes of memory devices for applications such as switching matrix, multilevel storage, and 3D non-volatile memory architecture.

### **DEDICATIONS**

To my Ph.D thesis advisor, Dr. Yicheng Lu

And my master degree advisor, Dr. Jinmin Li

To my father, Xuping Zhang And my mother, Jing Sun

#### ACKNOWLEDGEMENTS

First, I would like to express my deepest gratitude to my dissertation advisor, Professor Yicheng Lu. In the past six years he not only taught me academic knowledge, but also let me understand how to be a PhD student. The always-on light in his office likes a beacon, and it guides me to the lab, to the ECE building and to the wonderful scientific world.

I would like to thank my dissertation committee members, Prof. Jaeseok Jeon, Prof. Warren Lai, and Prof. Dunbar Birnie for taking time off their busy schedule to review and critique my dissertation.

My thanks also go to Dr. Lihua Zhang, Dr. Kim Kisslinger and Dr. Ming Lu from Brookhaven National Lab for the collaboration work.

I would like to thank my colleagues in Prof. Lu's research group and in Rutgers University, who have provided support throughout my work. Dr. Jian Zhong, Dr. Pavel Reyes, and Dr. Jeren Ku for training me in microelectronic device fabrication and characterization. Dr. Ziqing Duan for material growth and film characterizations. Mr. Rui Li, Mr. Wen-Chiang Hong and Mr. Subrata Debnath, for their help in the many facets of my work in the group. Dr. Yi Xu for helping me with material chemical characteristics. Working with you guys is such an honor.

I would like to thank my father Xuping Zhang, my mother Jing Sun. Your expectation is my motivation. Getting old let me fully realize the hardworking for the parents to raise a child. Thanks Miss Wenjia Yuan for her encouragement when I was tired and got puzzled.

This work has been supported in part by the United States Air Force Office of Scientific Research (AFOSR) under Grant No. FA9550-08-01-0452, and by the National Science Foundation (NSF) under Grant No. ECCS 1002178.

### **TABLE OF CONTENTS**

| Abstract                                                                 | ii  |

|--------------------------------------------------------------------------|-----|

| Dedication                                                               | iv  |

| Acknowledgements                                                         | v   |

| Table of Contents                                                        | vii |

| List of Table                                                            | x   |

| List of Illustrations                                                    | xi  |

| Chapter 1. Introduction                                                  | 1   |

| 1.1 Motivation                                                           | 1   |

| 1.2 Objectives and Scope of Work                                         | 4   |

| 1.3 Organization of the Dissertation                                     | 5   |

| Chapter 2. Technical Background                                          |     |

| 2.1 Basic Memories and Technical Challenges                              | 7   |

| 2.2 Resistive Switching                                                  | 10  |

| 2.3 ZnO-based Resistive Switching Devices                                | 15  |

| 2.4 Integration of Resistive Switching Devices                           | 18  |

| 2.5 Summary and Challenges of ZnO Resistive Switching Research           | 27  |

| Chapter 3. ZnO-based Bipolar and Unipolar Resistive Switching Devices    | 28  |

| 3.1 Device and Demonstration of Fe-doped ZnO Resistive Switching Devices | 28  |

| 3.1.1 FeZnO Single Layer Structure                                       | 29  |

| 3.1.2 FeZnO/MgO Bilayer Structure                                        | 29  |

| 3.2 Polarity of FeZnO Resistive Switching Device                         | 33  |

| 3.2.1 Bipolar Resistive Switching                                               | 33 |

|---------------------------------------------------------------------------------|----|

| 3.2.2 Unipolar Resistive Switching                                              | 42 |

| 3.2.3 Thickness Dependence of Switching Polarity                                | 47 |

| 3.3 Ni-doped ZnO Resistive Switching Device Fabricated at Room<br>Temperature   | 50 |

| 3.4 Summary                                                                     | 57 |

| Chapter 4. Resistive Switching Mode Conversion Controlled by Compliance Current | 59 |

| 4.1 Introduction                                                                | 60 |

| 4.2 Device Structure and Design                                                 | 62 |

| 4.3 Electrical Characteristics for Modes Conversion                             | 63 |

| 4.4 TEM Characteristics for Different Switching Modes                           | 74 |

| 4.5 Summary                                                                     | 79 |

| Chapter 5. Integration of ZnO-based Resistive Switching Devices                 |    |

| 5.1 1D1R Integration                                                            | 80 |

| 5.1.1 ZnO-based Schottky Diode                                                  | 80 |

| 5.1.2 Vertical Integration of Resistive Switching and Diode Devices             | 85 |

| 5.1.3 1D1R Testing Results                                                      | 88 |

| 5.2 Control compliance current for 1T1R integration                             | 94 |

| 5.3 Summary                                                                     | 96 |

| Chapter 6. Conclusions and Suggestions for Future Work                          |    |

|                                                                                 |    |

| 6.1 Conclusions                                                                 | 97 |

#### References

100

## LIST OF TABLE

**3.1.** Effects of thickness and electrodes on resistive switching 48 performances

### LIST OF ILLUSTRATIONS

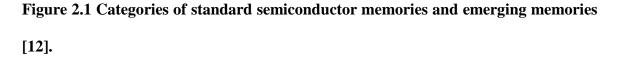

| 2.1. | Categories of standard semiconductor memories and emerging memories.                                                                                                                                                                 | 8  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

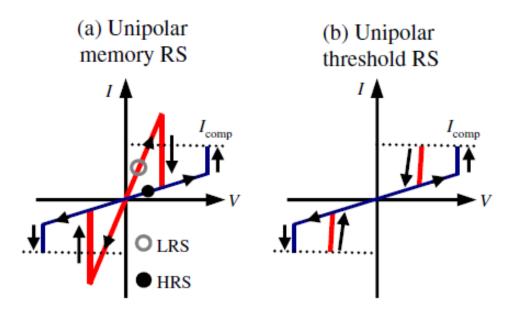

| 2.2. | Schematic diagrams of current-voltage (I-V) curves for two resistance switching (RS) phenomena: (a) unipolar memory RS and (b) unipolar threshold RS.                                                                                | 12 |

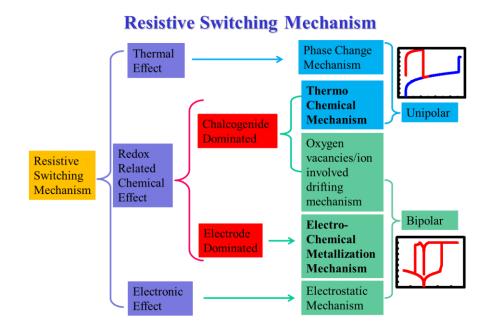

| 2.3. | The category of the resistive switching mechanisms                                                                                                                                                                                   | 13 |

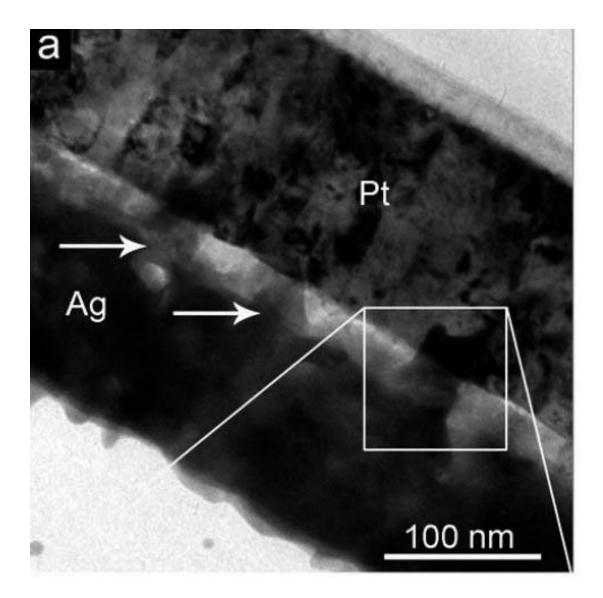

| 2.4. | Conventional TEM observation for conductive filaments in the Ag/ZnO:Mn/Pt memory cell that has been switched to LRS.                                                                                                                 | 17 |

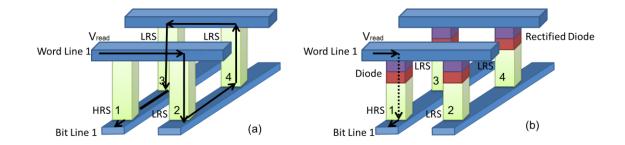

| 2.5. | (a) Reading malfunction in an array consisting of $2\times 2$ resistive switching cells without diodes. (b) Rectified reading operation in an array consisting of $2\times 2$ cells with diodes.                                     | 19 |

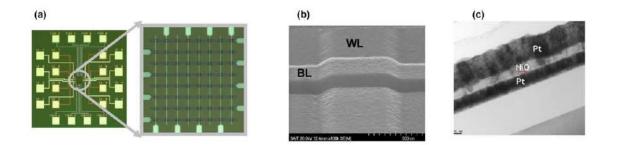

| 2.6. | (a) Optical microscopic image including pads for our test array structures and image of the 8x8 cell array. (b) SEM image of Pt word and bit line. (c) TEM image of NiO storage element.                                             | 21 |

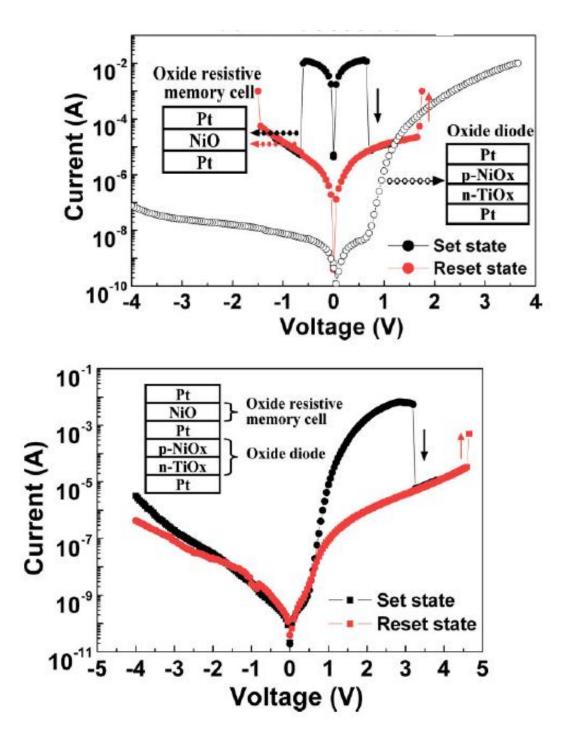

| 2.7. | The IV characteristics of the single memory cell, diode cell and the integration 1D1R structure.                                                                                                                                     | 22 |

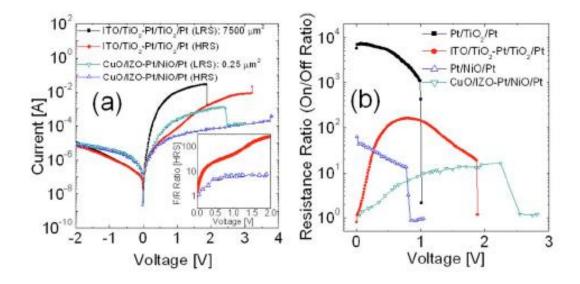

| 2.8. | The IV characteristics of ITO/TiO2-Pt/TiO2/Pt and CuO/IZO-Pt/NiO/Pt 1D1R structure.                                                                                                                                                  | 24 |

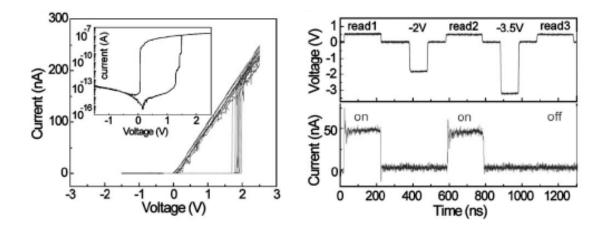

| 2.9. | The IV characteristics curve of the self-rectifying structure and the response time of the device.                                                                                                                                   | 25 |

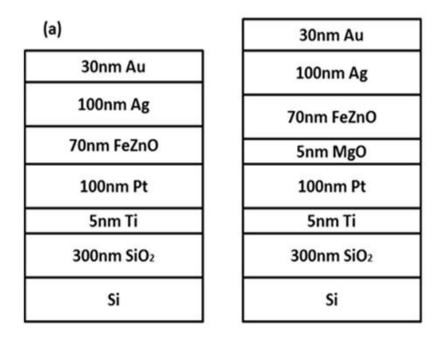

| 3.1. | (a) The schematic diagrams of the bipolar resistive switching structures: the left diagram shows an Ag/FeZnO/Pt (SL) structure, and the right diagram shows an Ag/FeZnO/MgO/Pt (BL) structure; (b) an SEM image of the BL structure. | 31 |

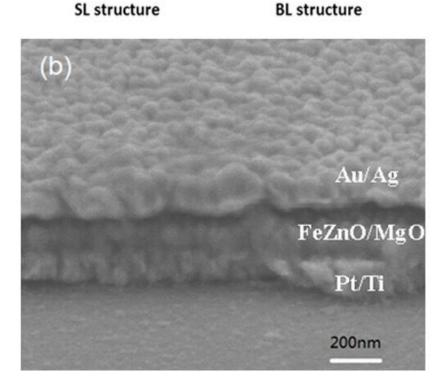

| 3.2. | XRD spectra of the FeZnO deposited (a) on the Pt/Ti/SiO2/Si, and (b) on the MgO/Pt/Ti/SiO2/Si.                                                                                                                                       | 33 |

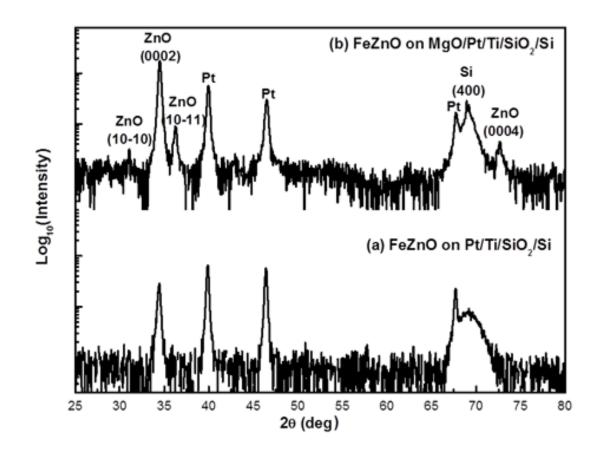

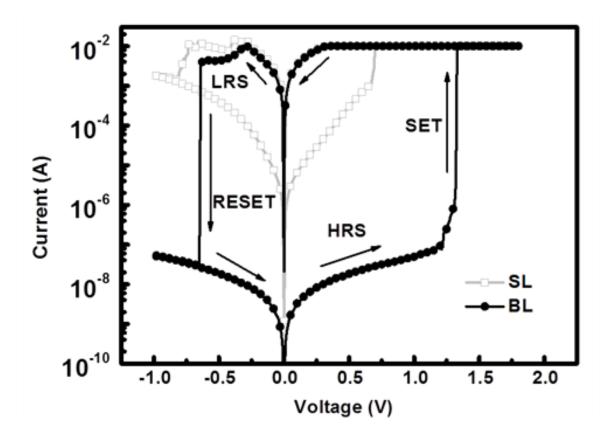

| 3.3. | The I-V characteristics of the Ag/FeZnO/Pt (SL) structure and the Ag/FeZnO/MgO/Pt (BL) structure.                                                                                                                                    | 35 |

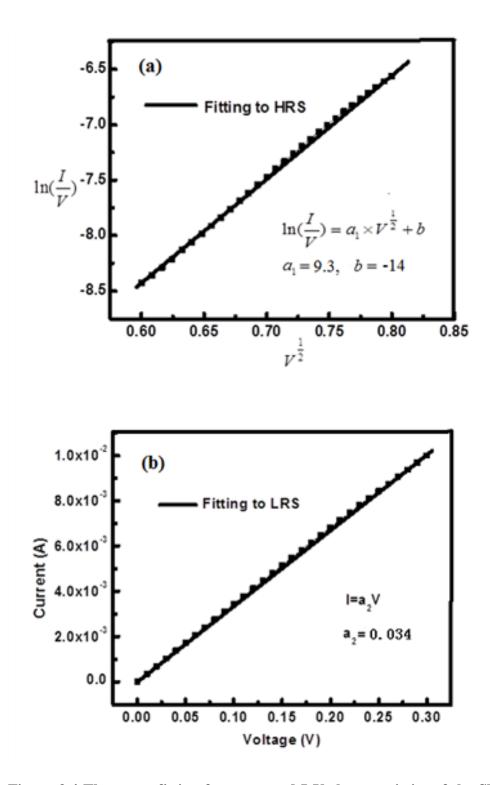

| 3.4. | The curve fitting for measured I-V characteristics of the SL structure at (a) HRS and (b) LRS. The measured data are represented by square dots, and the fitting results are represented by                                          | 37 |

straight lines.

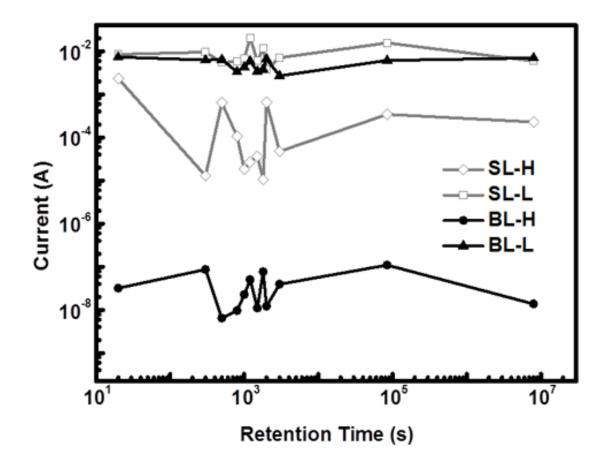

| 3.5.  | The retention time of the SL and BL structures.                                                                                                                                                                                                                                                                                                                                        | 39 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

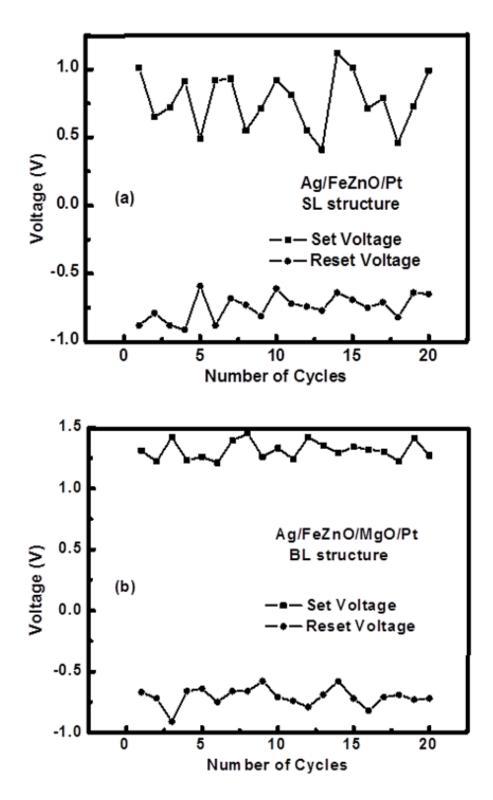

| 3.6.  | The distribution of the operation voltages of the (a) SL and (b) BL structures.                                                                                                                                                                                                                                                                                                        | 41 |

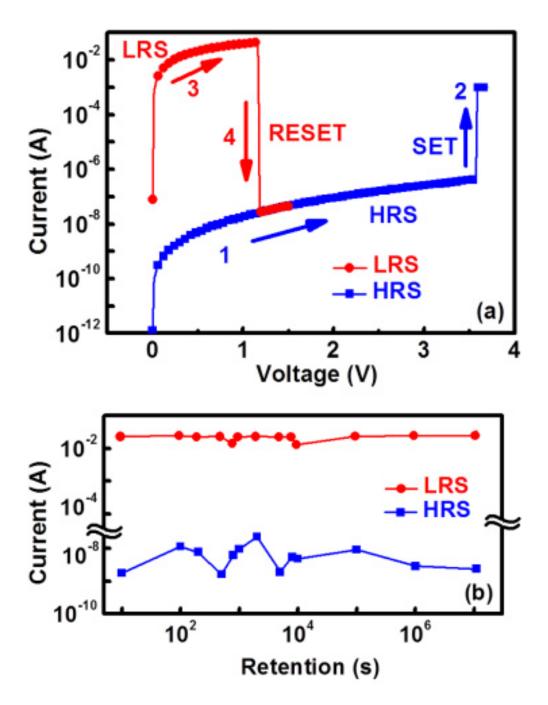

| 3.7.  | (a) The I-V characteristics and (b) retention time of the FeZnO/MgO switching resistor. The entire characterization was conducted at room temperature.                                                                                                                                                                                                                                 | 43 |

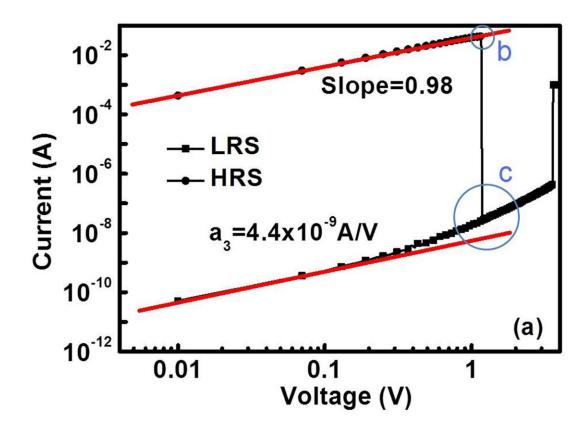

| 3.8.  | (a) A log-log plot of I-V characteristics of the FeZnO/MgO switching resistor. (b) The enlarged region b in figure (a), where a slight deviation from the initial linearity of LRS occurs when the voltage is larger than 1.1 V. (c) The enlarged region c in figure (a), where the experimental data of HRS are fitted by the Poole-Frenkel model when the voltage is larger than 1V. | 45 |

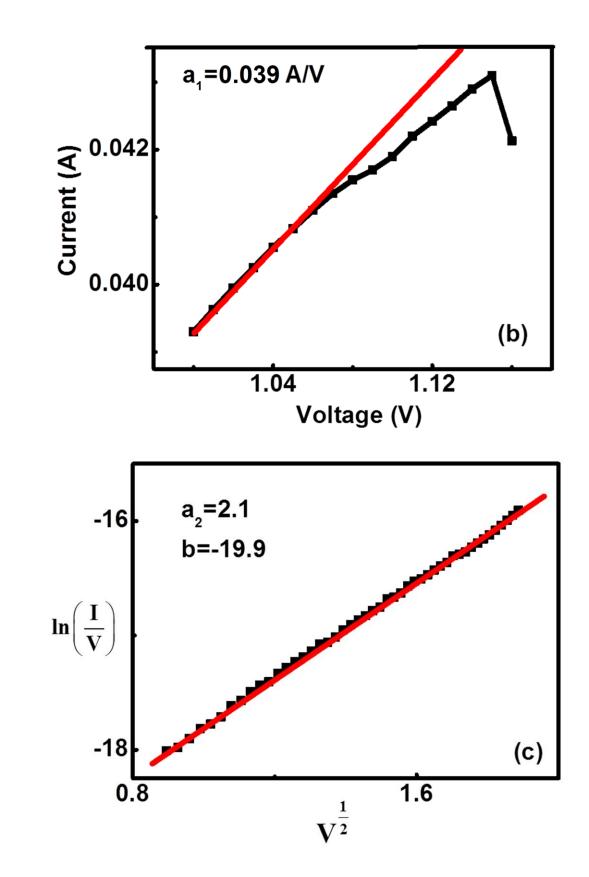

| 3.9.  | The proposed SET process and formed filament in the unipolar and bipolar resistive switching.                                                                                                                                                                                                                                                                                          | 50 |

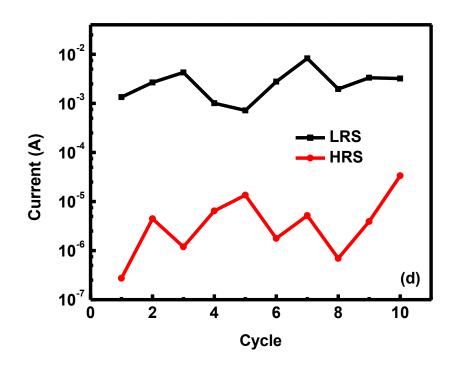

| 3.10. | The IV characteristics of ZnO based resistive switching device on SiO2/Si (a) and polymer flexible substrate (b) at RT. (c) The flexible memory fabricated with shadow mask with the dimension of 400 um. (d) The stability of the flexible resistive switching.                                                                                                                       | 54 |

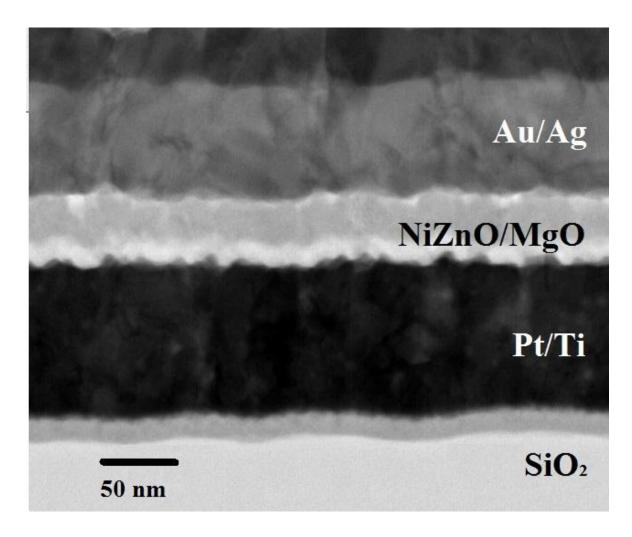

| 4.1.  | A cross-sectional TEM image of the resistive switching devices.                                                                                                                                                                                                                                                                                                                        | 63 |

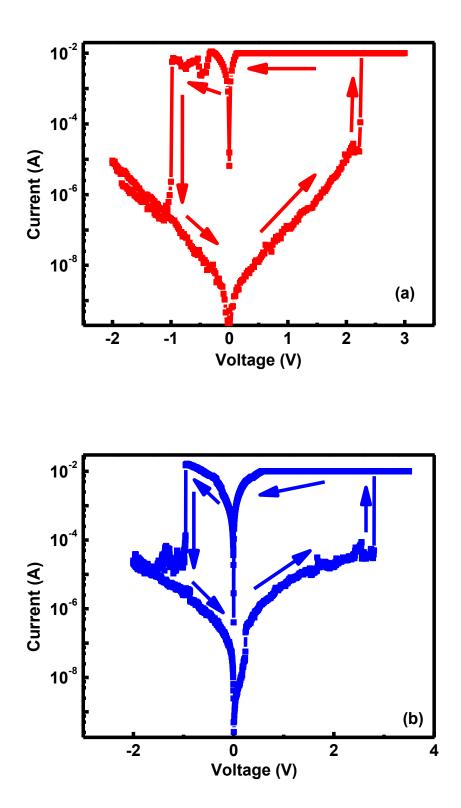

| 4.2.  | The IV characteristics of (a) memory switching, (b) threshold<br>switching, and (c) volatile switching. The switching mode can be<br>converted by changing the compliance currents.                                                                                                                                                                                                    | 65 |

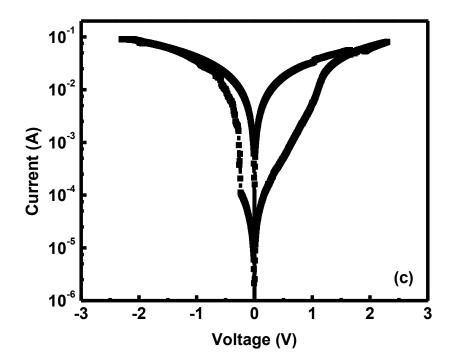

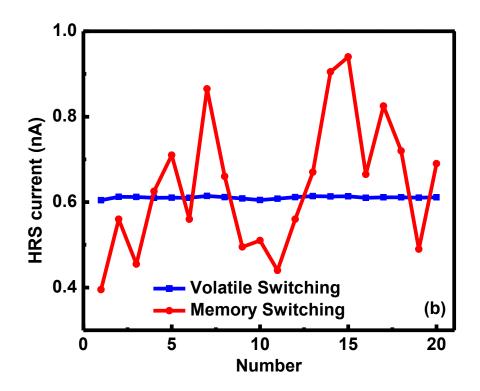

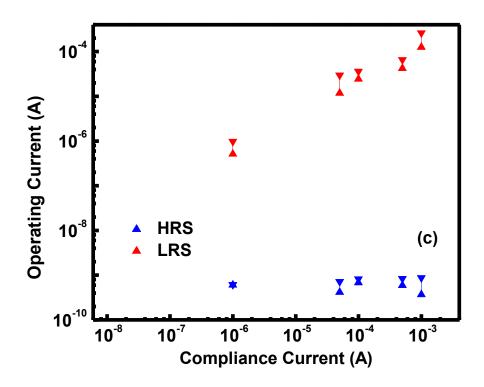

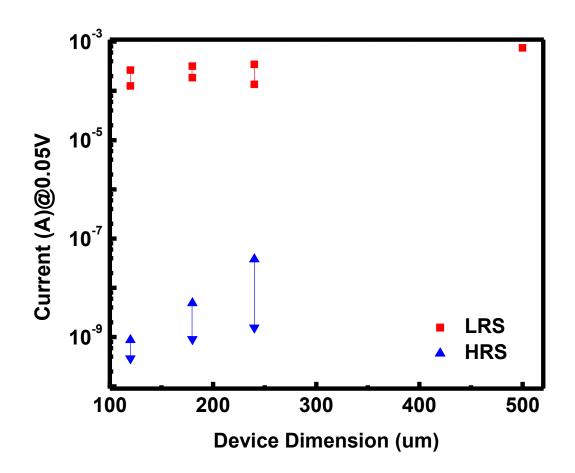

| 4.3.  | (a) LRS current, (b) HRS current comparison of the volatile switching and memory switching. (c) The different reading current at different compliance current. The reading voltage is set at 0.05 V.                                                                                                                                                                                   | 69 |

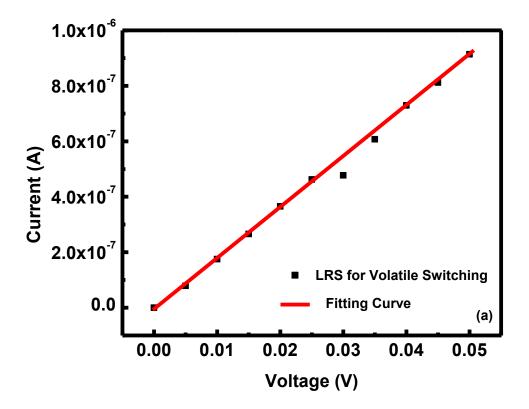

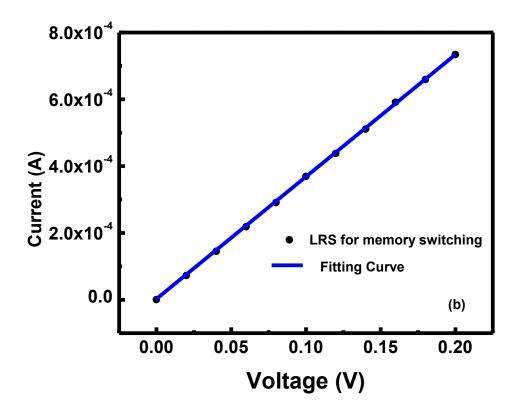

| 4.4.  | The LRS curve fitting for volatile switching (a) and memory switching (b).                                                                                                                                                                                                                                                                                                             | 71 |

| 4.5.  | The IV characteristics for memory switching with different dimension                                                                                                                                                                                                                                                                                                                   | 72 |

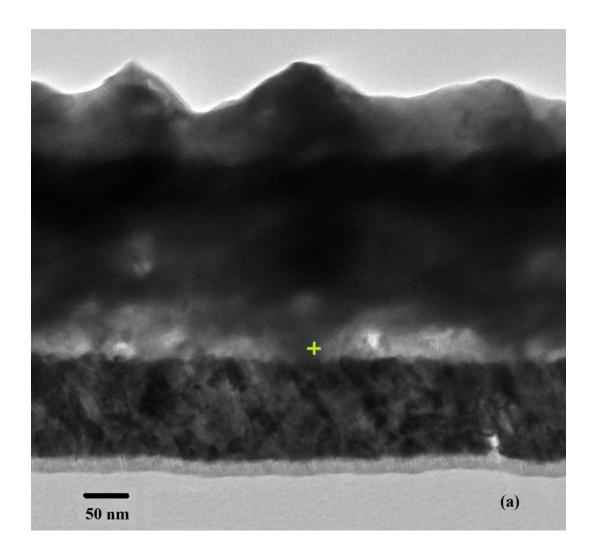

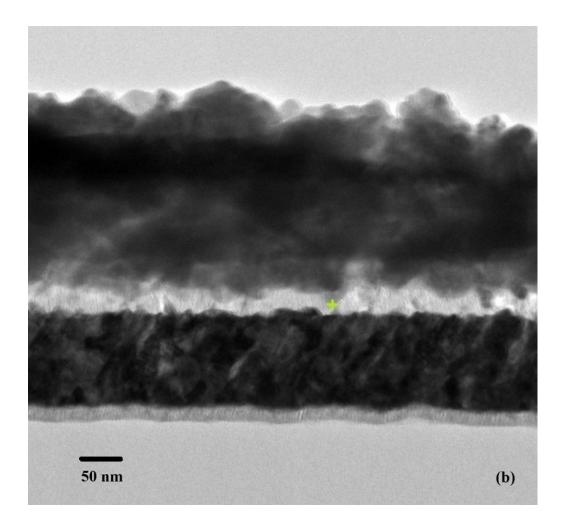

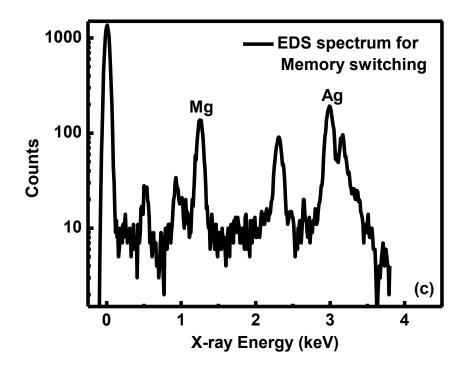

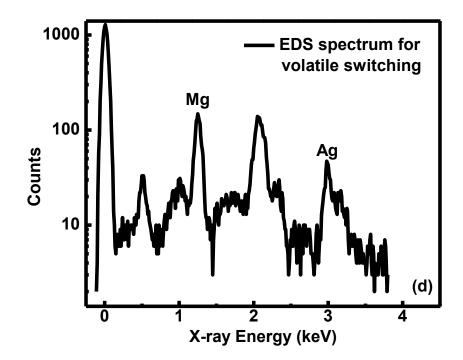

| 4.6.  | The TEM Characteristics of the memory switching (a) and volatile switching (b). The green marks indicated where the EDS data took                                                                                                                                                                                                                                                      | 76 |

for memory switching (c) and volatile switching (d).

region.

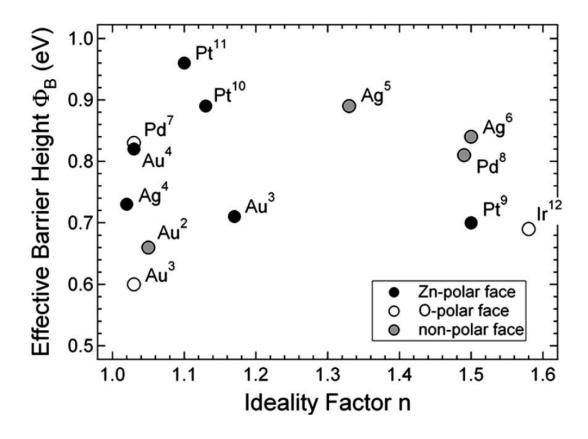

| 5.1. | Effective barrier height vs ideality factor n for the best reported<br>Schottky contacts on n-type ZnO with different metal.                                                                                                                                                                                                                                                 | 82 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

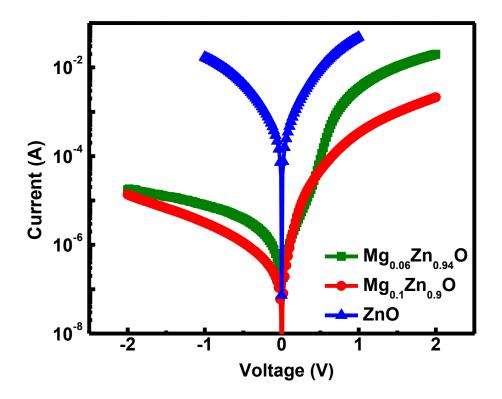

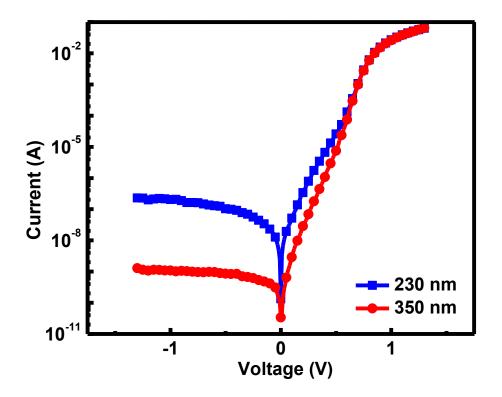

| 5.2. | The IV characteristics of the ZnO-based Schottky diode with different Mg doping.                                                                                                                                                                                                                                                                                             | 83 |

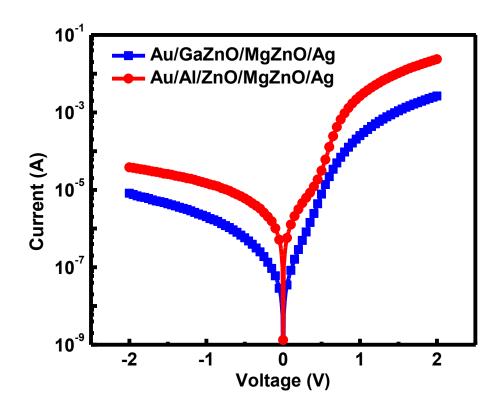

| 5.3. | The IV characteristics of the ZnO-based Schottky diode with different ohmic contact.                                                                                                                                                                                                                                                                                         | 84 |

| 5.4. | The IV characteristics of the ZnO-based Schottky diode with different MgZnO thickness.                                                                                                                                                                                                                                                                                       | 85 |

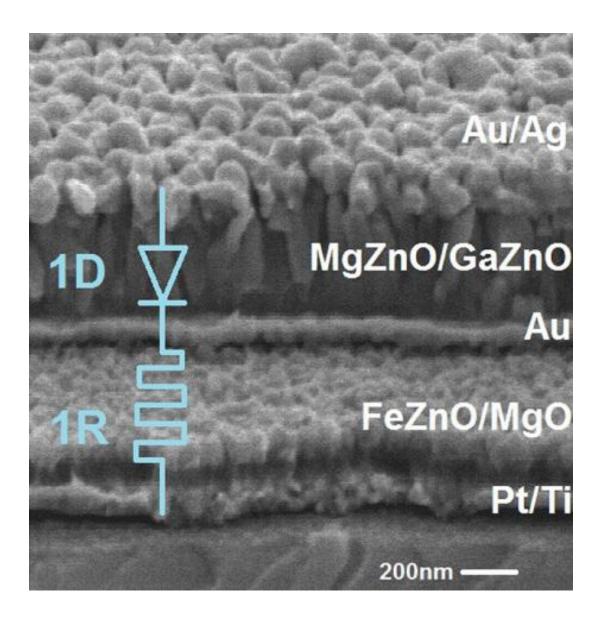

| 5.5. | A SEM image of a vertically integrated ZnO-based 1D1R structure.                                                                                                                                                                                                                                                                                                             | 87 |

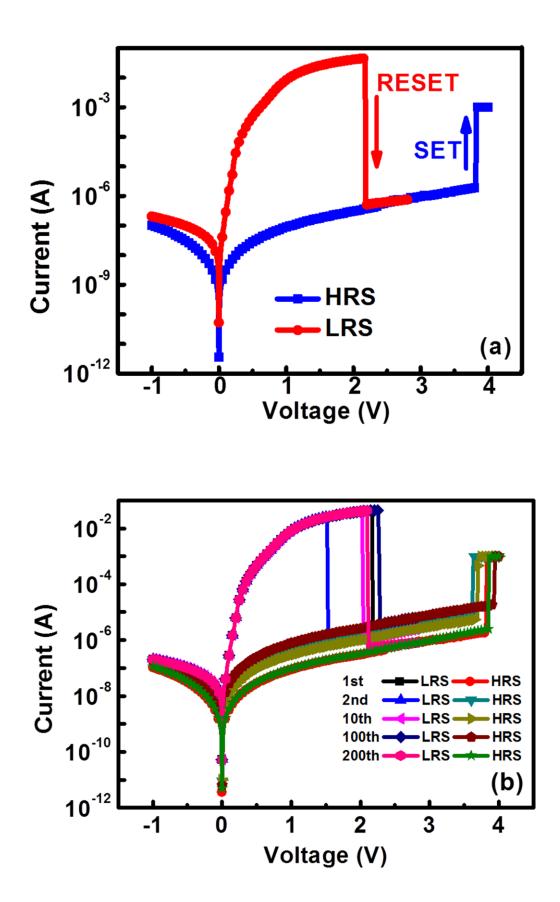

| 5.6. | I-V characteristics of (a) the vertically integrated ZnO-based 1D1R, and (b) the endurance performance of the 1D1R structure within 200 cycles.                                                                                                                                                                                                                              | 90 |

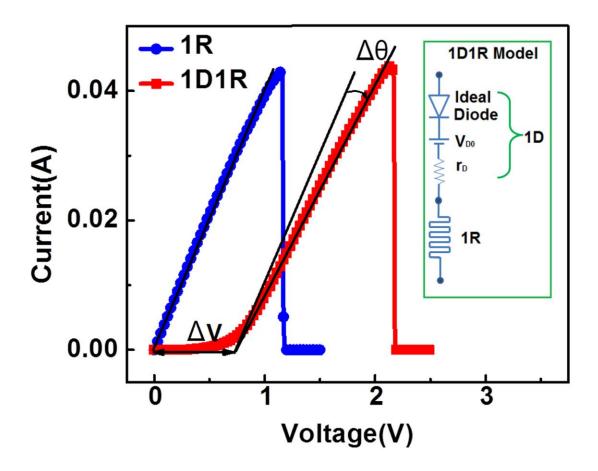

| 5.7. | I-V characteristics of the 1R-only and the 1D1R under LRS are<br>presented in the linear scale. Their I-V curves show two major<br>differences: voltage shift of $\Delta V$ and slope change of $\Delta \theta$ . The insert<br>image shows the schematic circuit model of the 1D1R where a<br>switching resistor is in series with the diode presented by the PWL<br>model. | 93 |

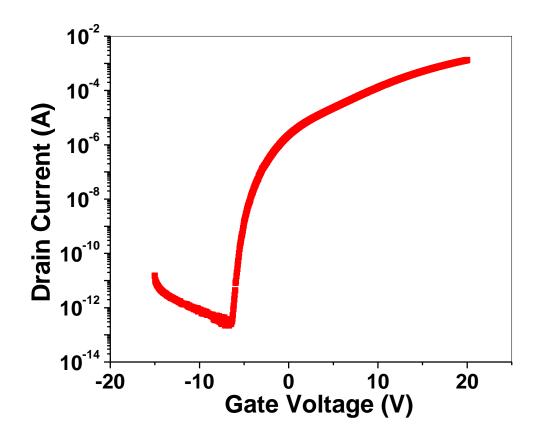

| 5.8. | $I_{DS}$ - $V_{GS}$ transfer characteristics of ZnO TFT in the saturation                                                                                                                                                                                                                                                                                                    | 95 |

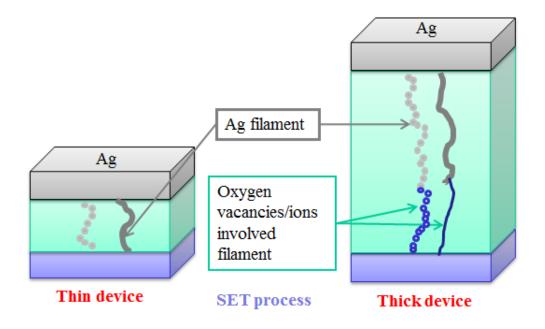

### Chapter 1

### Introduction

#### **1.1. Motivation**

In the last several decades, computer memory develops rapidly by reducing the size of the unit cell and increasing the intensity of the memories. However, conventional memory techniques are facing numerous scaling and reliability challenges when the characteristic dimension reaches to the physics limitation. To solve the problems, resistive random access memory (RRAM) is emerging as an important nonvolatile memory (NVM) technology [1]. The oxide-based resistive switching devices have inspired substantial scientific and commercial interests due to their simple structure, great scalability, fast operating speed, and low power consumption [2-4]. Among them, ZnO-based resistive switching devices possess promising features, such as well-controlled switching properties through *in-situ* doping and alloying, and low cost due to its abundant material source and relatively simple processing. Furthermore, the multifunctional properties such as semiconducting and resistive switching of ZnO can be achieved through the proper doping process, facilitating the device integration.

It has been proposed that resistive switching in oxides is attributed to the formation and rupture of the conductive filaments in the oxides, which are closely related to the oxygen vacancies and oxygen ions [2, 5], or metal ions [6]. However, the difficulty in control of the length and amount of the conductive filaments in the resistive memory fabricated using the single layer (SL) oxide structure prevents the device from achieving a high and stable  $R_{HRS}/R_{LRS}$  ratio, which could cause false programming and readout hazards. To overcome these problems, several oxide-based bilayer (BL) structures have

been reported. These BL structures have better control on the switching parameters and improve the performances of the resistive memory devices. Up to date, there has been no information on the BL structures used in ZnO-based resistive switching devices though ZnO has shown promising multifunctional properties for integrated RRAM applications. In this research, we fabricated Ag/FeZnO/Pt (SL) and Ag/FeZnO/MgO/Pt (BL) structures for resistive switching. Their current-voltage (*I–V*) characteristics are analyzed and compared. The transition metal (TM) Fe, is used to form the Fe<sub>x</sub>Zn<sub>1-x</sub>O (x~4%) films which serve as the switching layer. In the ternary Fe<sub>x</sub>Zn<sub>1-x</sub>O, most Fe atoms tend to be in a Zn substitutional site with a small displacement due to the similar ionic radius as Zn. Fe has superior thermal stability over other TM ions in the ZnO lattice [7, 8]. These properties could result in higher structural quality of the material and better endurance performance for resistance switching. Fe is a deep level donor in ZnO [9, 10], and Fe doping could increase the resistivity of the HRS for resistive switching [11].

There are several issues related to the mechanism of the resistive switching that need to be clarified. For example, different polarities of the resistive switching have specific applications; therefore understanding of the reason for the unipolar and bipolar RS and the relationship between them are critical for further development of resistive switching. In addition, the cause for the switching between the HRS and LRS is worth studying in order to optimize the RS parameters, such as the ratio of  $R_{HRS}/R_{LRS}$ , the parameter dispersion, and the endurance performance. Compared to the memory RS, the threshold RS is a volatile memory, which could serve as a good switch device to control the random access to specific memory cells. Due to the difficulty of finding the reading voltage and the relative stable LRS in threshold switching, a medium mode, which is

called the volatile switching mode, becomes more important in the practical application. Free of another reset process, low operation current, and possible faster speed turn this kind of switching into a promising complement for regular memory switching. The conversion between these three RSs will be discussed in the electrical characteristics and TEM analysis.

The crossbar array provides for both high density and easy multi-bit operation; therefore, is preferred for the applications in nonvolatile memory and reconfigurable switching matrix. However, if the crossbar array only consists of a resistive switching device (1R) between the top and bottom electrodes, during reading process on one R cell in HRS, the parasitic current can easily flow through the nearby cells in LRS, leading to reading disturbance among the neighboring cells, thus causes fake readout signals. The 1D1R cell consisting of a diode (1D) and a switching resistor (1R) is ideal for avoiding such malfunction in the crossbar configuration because the diode's rectifying behavior under the reverse bias could eliminate the cross-talk. There are two types of resistive switching devices: the unipolar one in which the resistive switching between lowresistance state (LRS) and high-resistance state (HRS) is only dependent on the magnitude of applied voltage, but independent of the polarity; and the bipolar one in which the SET (switching from HRS to LRS) and RESET (switching from LRS to HRS) processes occur under the applied voltages with different polarities. There are unique advantages of using the unipolar switching device over the bipolar counterpart in the crossbar system. First, the unipolar resistive switching only depends on the magnitude but is independent of the polarity of the applied voltage, leading to easy operation with the unipolar voltage source. Second, the different absolute values of the SET and RESET

voltages can prevent reading/writing confusions under multiple-control signals. The vertical 1D1R structure is ideal for such crossbar configuration as it can significantly save the cell area to  $4F^2$  (F is the minimum feature size), thus increase the memory density. Furthermore, the vertically integrated 1D1R is preferred for 3-dimensional (3-D) integration.

However, 1D1R crossbar structure applications also have their limitations. 1D1R array is a passive crossbar matrix, which just connect the word and bit lines at each node. For the simple digital circuits, there are only high voltage, which is recognized as the signal "1"; and low voltage, which is recognized as the signal "0". There is no simple medium voltage which could RESET the node for unipolar RS. For further complicated application the crossbar system has to be controlled by the outside circuits. Alternatively, the RS device could be organized in an active array comprising of a transistor at the node which disable the RS cell if it is not addressed. Regular voltage could SET the node and the reversed voltage could RESET for the bipolar RS. ZnO-based thin film transistor is an emerging transistor for the active 1T1R memory integration for flexible memory application.

The aim of this interdisciplinary work is to enhance the performance of the resistive switching and stimulate integration based on the resistive switching devices. 1D1R and other integration structures can serve as the basic circuit building block for reconfigurable switching matrix and nonvolatile memory (NVM).

#### **1.2.** Objectives and Scope of Work

The objectives of this research are to design, fabricate and characterize the ZnObased resistive switching devices and explore their integration with other ZnO devices. The scope of this study covers:

- (1) Design and development of the ZnO-based resistive switching devices, including the unipolar and bipolar switching devices. Study its conduction mechanism through simulation and curve fitting of the current in the HRS and LRS. Adapt the ZnO/MgO bilayer structure as the active layer in the resistive switching device to enhance the resistive ratio and the stability of the operation parameters.

- (2) Investigation on conversion of different resistive switching modes in similar structure. Through compliance current setting, we could achieve the conversion between the threshold switching, volatile switching and memory switching, but control the operation parameters. TEM characteristics are also used to prove the assumption with the electrical analysis.

- (3) Integration of the TM-doped ZnO resistive switching device with other ZnO devices to explore its applications. The unipolar switching device is vertically integrated with a diode into the 1D1R structure for switching matrix. The bipolar switching device is integrated with thin film transistor into 1T1R for non-volatile memory on flexible substrate.

#### **1.3. Organization of the Dissertation**

After establishing the motivation and the specific objectives and scope of this research in Chapter 1, a review of the related work on ZnO-based resistive switching in Chapter 2. Chapter 2 also provides a background on the technical approach employed in

designing ZnO switching devices and related integration. In Chapter 2 the review for the mechanism discussion on the resistive switching is also presented. Chapter 3 includes a discussion of the characterization of the ZnO-based bipolar and unipolar resistive switching devices. A detailed description of the experimental results is also presented on the bilayer structure study for the switching parameter optimization. Chapter 4 deals with the conversion of different switching modes. The switching modes included the threshold switching mode, volatile switching mode, and memory resistive switching mode. Chapter 5 presents the integration of resistive switching devices with diode and other devices. The optimization for the vertical Schottky diode is also discussed. Finally, Chapter 6 summarizes the results of the dissertation research and presents further work.

## **Chapter 2**

# **Technical Background**

Resistive switching device is a new fundamental circuit element, whose resistance depends on the history of applied voltage (magnitude, polarity, and duration). Compared with other charge-storage memory, the oxide resistive switching memories (OXRRAM) are emerging as nonvolatile memory technology due to their ability of scaling, high storage density, fast write time, and low power operation. ZnO RRAM devices can be built on glass and SiO<sub>2</sub>/Si substrates, offering full optical transparency, large ON/OFF ratio, fast programming speed, and long retention time. ZnO-based resistance switching device possess several advantages, including well-controlled switching properties through in-situ doping and alloying, a simple fabrication process, and radiation hardness. ZnO resistive switching device in an ultra-high-density configuration possess both the non-volatile characteristics of ROM and the high speed of DRAM and SRAM. In this chapter, the role of ZnO in the field of resistive switching research will be discussed. Various reported switching devices and related integration based on ZnO operating in different modes will also be discussed in this chapter.

#### **2.1. Basic Memories and Technical Challenges**

Semiconductor memory is a critical part of digital systems in computers for storing data and programs. As shown in Figure 2.1, there are two different types of computer memories: volatile memory and non-volatile memory. Volatile memory requires power to maintain the stored information, in other words it needs power to achieve the function of memory. Volatile memory retains the information as long as power supply is on, but when power supply is off or interrupted, the stored memory is lost. Static Random Access Memory (SRAM) and Dynamic RAM (DRAM) are two main memory devices in the volatile memory. SRAM utilize static latches as the storage cells and DRAM storage the binary data on capacitors, which could reduce the feature size of the unit cell. The operation times for SRAM and DRAM are short (0.3 ns for SRAM and 10 ns for DRAM), but the density is very low because of the large size of the unit cell ( $140F^2$  for SRAM and  $6F^2$  for DRAM, F is the minimum feature size). In addition, SRAM and DRAM could only be used for the temporary data, because when the power is off, the memorized information will disappear.

Non-volatile memory is another type of computer memory that can retain stored information even when not powered. Examples of non-volatile memory include read-only memory, flash memory, ferroelectric RAM (F-RAM), most types of magnetic computer storage devices (e.g. hard disks, floppy disks, and magnetic tape) and optical discs. Normally these kinds of memories has longer operation time (larger than 10 ns), however because of relative small unit size and non-volatile characteristics, they are the important components in the computer memory.

In order to overcome the disadvantages in both types of the well-developed memories, there are several expectations and requirements for the next generation of memory technology.

Unit cell size: Memory density is a critical aspect in the performance. Currently the common memory has the minimum unit size of  $6F^2$ . The unit cell size for the next generation memory should be in the range of  $4F^2$  to  $6F^2$ .

Writing and reading operation: The operation voltage of the memory should be less than 10 V to protect the active layer and the reading voltage cannot be less than one tenth of writing voltage.

**Resistance ratio and stability:** Normally the ratio for memory is larger than 10 to identify the signal "1" and "0", however higher resistive ratio and limited dispersion of the parameters could increase the yield of the devices.

Endurance performance and retention time: The endurance performance of the common memory should be larger than  $10^5$  testing cycles and the device should be robust for more than 5 years. [1]

Novel memory technology fulfilling with the requirements above could be a suitable candidate for the next generation of memory.

#### 2.2. Resistive Switching

Recently, a new fundamental circuit element, memory resistive switching (RS) device, is emerging as a promising resistance random access memory (RRAM) device. In a RS device, the resistance value depends on the history or polarity of an applied voltage. It exhibits switching characteristics when the threshold voltage is reached. When the power is off, the device will keep the same resistance state, therefore it is categorized into the non-volatile memory. There are two different types of RS: unipolar and bipolar. The unipolar RS between low (LRS) and high resistance state (HRS) only depends on the magnitude but independent of the polarity of the applied voltage,[13,14] while the bipolar RS depends on not only the magnitude but also the polarity.

Various materials are used to achieve the resistance switching, including metal oxide, [6, 15] chalcogenide, [16, 17] and organic molecular system, [18, 19] etc. Compared with other memory devices, the oxide-based resistive switching devices are promising due to its simple structure and fabrication process, high storage density, fast writing and reading speed, and low power operation. There are plenty of oxide materials could be used for resistive switching device, such as NiO<sub>x</sub> [15], TiO<sub>x</sub> [20], AlO<sub>x</sub> [21], CuO<sub>x</sub> [22], HfO<sub>x</sub> [23], ZnO [6] etc.

However, because the active layers of the structures listed above are only one layer, they are very difficult to control the parameters of the resistive switching. It is reported that using two-layer structure to optimize the performance. For example, a 5 nm  $ZrO_x$  layer is added on the HfO\_x layer to form a  $ZrO_x/HfO_x$  BL structure to improve the stability of switching performance, and the ratio of  $R_{HRS}/R_{LRS}$  is increased by ~100 times over the single HfO\_x-based structure [24]. It is also reported that a BL switching structure, consisting of the AlO<sub>x</sub> as a tunnel layer and TiO<sub>x</sub> as a transport layer, reduces the dispersion of the switching parameters [25].

Generally speaking, there are two different kinds of RS effects: memory RS and threshold RS [26, 27], and the characteristic I-V curves are shown in Figs. 2.2 (a) and (b), respectively. The memory RS effect has an IV curve loop and two reversible transitions. As both LRS and HRS are stable when the power is off, they can be used in nonvolatile memory devices. However, as shown in Fig. 2.2 (b), the threshold RS effect has only one stable resistance state if no external bias applied, which could be categorized into volatile memory. There are several methods to make the conversion between the two switching. Chang et al. observed two types of reversible resistance switching (RS) effects by control thermal cycling in a NiO film: memory RS at low temperature and threshold RS at high temperature. [28] They used a dynamic percolation model to explain the transition phenomena and showed that the RS effects are controlled by the thermal stability of the conduction filaments, and the conversion from the two types of resistive switching result from the competition between Joule heating and thermal dissipation. Another method is using voltage pulse to change between bistable memory switching and monostable threshold switching in Pt/NiO/Pt structure.[29] Memory RS could be changed to threshold RS by applying a positive electrical pulse with height of 2 V and width between  $10^{-2}$  and  $10^{-4}$  s. The change is reversible by applying a negative electrical pulse with the same height and width. The polarity- and width-dependence of the switching transition and compositional difference on electrical properties in  $NiO_x$  proved that the migration of oxygen ions is responsible for the switching transition in Pt/NiO/Pt structures.

Figure 2.2 Schematic diagrams of current-voltage (I-V) curves for two resistance switching (RS) phenomena: (a) unipolar memory RS and (b) unipolar threshold RS. [28]

Figure 2.3 summarizes the main mechanisms of the memory resistive switching [1]. In the redox related resistive switching effect, there are two different types: chalcogenide and electrode dominated effect. Thermal Chemical Mechanism (TCM) [2] and Oxygen Ion Drifting Mechanism (ODM) [5] could explain the chalcogenide dominated effect, and the Electro-Chemical Metallization Mechanism (MCM) [6] need the interface redox between the electrode and active layer, therefore it could explain the electrode dominated effect, and mainly for the bipolar RS. However, both of the Thermo Chemical Mechanism and the Oxygen vacancies/ion involved drifting mechanism are

involved with the oxygen vacancies or ions. The main difference between these two mechanisms is that TCM used Joule heating to explain the rupture (unipolar RS) and ODM used drifting of the oxygen vacancies or ions under the reverse voltage to explain the rupture (bipolar RS). [5]

Figure 2.3 The category of the resistive switching mechanisms, according to [1].

The detailed study for the mechanism of resistive switching is complicated and still controversial. Some research group tried to study the compliance current (CC) effect to the resistive switching and get a preliminary knowledge for the mechanism.

During the set step of resistance switching, the limited current is confined on the memory to avoid excessive current and possible avalanche breakdown, which is also called compliance current (CC). Seo *et al* [30] first mentioned that the low resistance

values of the switching are dependent on the compliance current in polycrystalline NiO films by sputtering. Rohde [21] described that if the allowed maximum current was not limited to a certain low value, the sample completely broke down, maybe due to avalanche multiplication. By setting a proper current compliance value, stable switching from off- to on-state was repetitively observed. It was considered that the sudden increase in current at SET point was due to the formation of strong filaments that switch the film to the on-state. Therefore, it can be imagined that the maximum allowed current (current compliance) influences the formation of strong filaments. A higher current compliance for switching to the on-state, therefore, results in the formation of stronger and less resistive filaments, which in turn need more energy and power for their rupture. Tsunoda et al [31] also confirmed that the on-state resistance was controlled by the magnitude of the current compliance in Pt/TiO<sub>2</sub>/Ag system. Kinoshita et al [32] pointed out that if compliance current in the Pt/NiO/Pt system is less than 1 mA, the response time for the current limiter in the semiconductor parameter analyzer may not catch up the rapid increase in the current during the set transition. Later Wan et al. proved the overshooting will exist under 1mA. [33]

Cao *et al.* [34] found out in the Pt/TiO<sub>2</sub>/Pt structure there is a kind of threshold current. If the compliance current is more than the threshold current, there will be no reset switching, and the curve fitting shows that the reset current not only have the initial ohmic region, just as other switching-achieved curve; but also have the nonlinear region. From equation, they find that the conducting mechanism of the LRS changes from Ohmic to Poole-Frenkel emission when applying a large CC. Thus, the switching behaviors disappear after the conversion of the conducting mechanism. It is suggested that a proper CC is essential to obtain a reversible resistive switching behavior. Kwon et al [35] use TEM image to indicate the bias voltage is largely reduced when the current level reaches the compliance limit, preventing further growth of other nanofilaments. Wang et al. showed that lower CCs produce conductive filaments (CFs) with simple connectivity and good controllability, resulting in a narrow distribution of switching voltages and a high ratio of high-to-low resistance states. In contrast, the stronger net-like CFs are formed at higher CCs, and their complete ruptures are difficult. Thus, the lower high-resistance states and a wide distribution of SVs appear in the reversible switching processes. [36] Lee et al. used random circuit breaker network model to simulate that if reduce the compliance current, the volume of the conducting filaments will decrease. [37] Nagashima et al. reported that varying the compliance current value resulted in the variation of LRS resistance, although the HRS resistance in each measurement was almost identical, even when the switching does not really happened. More importantly, there was a systematic relationship between the compliance current and the LRS resistance, indicating the "multistate memory effects".[38]

#### **2.3. ZnO-based Resistive Switching Devices**

Zinc oxide (ZnO) is a kind of wide band gap semiconductor material with a direct band gap of 3.34 eV at room temperature. [5] Compared with other wide band-gap semiconductors, ZnO has several advantages, such as a high free exciton binding energy of about 60 meV as compared to 25 meV for GaN, large UV photoresponse, superior radiation hardness, availability of large size single crystal substrates facilitating for homoeptaxial growth, and ease of wet chemical etching. ZnO nanostructures have become one of the most promising and useful multifunctional nanostructures. It can be grown at low temperature on various substrates, giving ZnO a unique advantage over the other wide bandgap semiconductors, such as GaN and SiC nanowires. MOCVD growth can also provide atomically sharp interface control, and possible end-facet morphology control for various device applications. Catalyst-free growth of ZnO nanotips by MOCVD leads to superior optical properties.

Among oxide RS devices, ZnO-based RS devices possess advantages. First, through in-situ doping and alloying, ZnO-based devices could control the resistive switching properties. [5] Also, the ZnO device fabrication is a simple process, and it could grow without high temperature and use solution to do the wet etching for the patterning. The ZnO materials also have the character of radiation hardness.[39] Furthermore, the multifunctional properties of ZnO and its nanostructures make it feasible for integration. There are several publications on ZnO-based unipolar RS devices. Chang *et al* reported the Pt/ZnO/Pt devices, which exhibit the bistable resistance switching behaviors. [2] They attributed the low and high resistance states to the Ohmic behavior and Poole-Frenkel emission, respectively. The transparent RS device was made using ITO as an electrode and ZnO as an active layer. [40] Yang et al reported that the Mn-doping could enhance the ratio of  $R_{HRS}/R_{LRS}$  and the response time of the Ag/Mndoped ZnO/Pt reached to 5 ns.[6] Peng et al fabricated the ZnO based RS device on different substrate and presented different switching performance.[41] A transparent switching device has also been demonstrated using GaZnO as the electrodes and ZnO as an active layer [42].

The Poole-Frenkel emission theory for oxygen vacancies related resistive switching is firstly mentioned in the reference [2] where it is believed that the conduction mechanism of HRS in high electric field is PF emission and the ZnO thin films contain non-negligible traps, i.e., oxygen vacancies most likely. This work used ZnO-based unipolar resistive switching device. However, Ag filament is also found in ZnO film by Yang *et al in* figure 2.4, and it is mentioned that the metal-involved filament forming and rupture may lead to the bipolar resistive switching.[6]

Figure 2.4 Conventional TEM observation for conductive filaments in the Ag/ZnO:Mn/Pt memory cell that has been switched to LRS.[6]

#### 2.4. Integration of Resistive Switching Devices

Information technology is experiencing increased need for reconfigurable systems-on-demand that are capable of on-the-fly task and defect adaption, in real-time, and at a lower cost. High-performance electronic systems combining state-of-the-art processing logic, memories, and sensors on a single chip is desired. The challenge in implementing an advanced reconfigurable switching matrix network that can be integrated with various functional subsystems is substantial. Furthermore, the advanced crossbar architectures are becoming more critical in high density and high-performance systems. New embedded switching schemes should deliver high performance with large variations in device parameters when these devices approach nanometer scale. To date, even the design of such crossbar array are based on different material systems and complicated fabrication processes resulting in extremely low yield and are therefore, impossible for commercial application.

There are two different kinds of crossbar array using RRAM. One is called active array, which contained one transistor and one memory (1T1R) and the RRAM at the cross-point is actively controlled by the transistor. The other is passive array, with one diode and one memory (1D1R), and the cross-point is passively controlled by the outside circuit. Because the minimum area of the 1D1R vertical structure is  $4F^2$  (F is the minimum feature size), the 1D1R integration crossbar array has good potential for scaling down.

The crossbar array structure is widely used for high-density storage and reconfigurable electronics. When the memory resistor (R) serves as the unit cell in the 1R-only crossbar array architecture, the malfunction would occur. In such a crossbar array, during reading process, the parasitic current can easily flow through the nearby R cells in LRS, thus causes the fake reading signals. For example, in a 2×2 crossbar structure shown in Fig. 2.5 (a), bit 1 is in HRS, while bit 2, 3 and 4 are all in LRS. To read bit 1, a voltage pulse is applied to world line 1 while bit line 1 is ground. In the ideal operation, no parasitic current can pass from world line 1 to reach bit line 1 and the readout signal of bit 1 is in HRS. However, a parasitic current path consisting of nearby bits in LRS exists, and current can pass through bit 2, 3 and 4 in LRS to reach bit line 1. A fake readout signal of LRS for bit 1 is therefore obtained.

Figure 2.5 (a) Reading malfunction in an array consisting of 2×2 resistive switching cells without diodes. (b) Rectified reading operation in an array consisting of 2×2 cells with diodes.

To eliminate the parasitic path, a diode has to be added to form the 1D1R unit cell in this  $2\times2$  crossbar structure, as shown in Fig. 2.5(b). When positive reading voltage is applied on the bit 1, the diode in bit 4 will be equivalently under the reverse bias, this integrated diode will block the current flowing through the nearby bits in LRS to reach bit line 1 (except the extremely small leakage current flowing through the reverselybiased diode). Thus, the reading signals will be acquired correctly. Therefore, in a crossbar matrix, it is needed to integrate a diode (1D) with a memory resistor (1R) to form the 1D1R unit cell to achieve the resistive switching without the crosstalk.

Up to now, several different kinds of 1D1R switching structures have been reported. There are four different types of diode could be used in the 1D1R crossbar array. First is Si-based diode based 1D1R integration. Golubovic *et al* first fabricated vertical polycrystalline silicon p-n diodes fabricated up to the metal-1 level using basic processing steps of a CMOS front-end-of-line for 65nm node and beyond.[43] In 2010 Cho *et al* fabricated 1D1R based on the nonvolatile organic memory device.[44] They used back Al/p-Si/Al as diode and Al/PI:PCBM/Au as memory element. In the 1D1R structure the ratio of forward current over the reverse current is 10<sup>3</sup>, and the R<sub>HRS</sub>/R<sub>LRS</sub> in the forward bias is 10<sup>2</sup>. However there are two major problems in this 1D1R structure. First this structure is based on the Silicon diode, which is lack of the compatibility of RRAM fabrication and further CMOS integration. Secondly the organic memory showed the bipolar switching characteristics, which is not suitable for passive crossbar array structure.

Second is the p-n diode based 1D1R integration. Kang *et al* presented the  $CuO_x/InZnO_x$  thin-film diodes for cross-point memory applications.[45] The vertical structure is Pt/p-CuO/n-IZO/Pt, as shown in Fig. 2.6. The forward and reverse current of the cross-point diode is  $10^3$ . Lee *et al* used NiO as a memory and p-CuO/n-IZO as a diode to form the 1D1R structure with 0.5 um×0.5 um cells, where the ratio of HRS over LRS

was about 80 after 1,000 cycles.[46] In the paper they introduced 2-stack 1D1R crosspoint structure to enlarge the memory cell density. They just shared the same bit line and used two different word lines to connect the memory and switching element. They also announced that their Pt/Ti-doped NiO/Pt storage node has the HRS/LRS ratio as large as  $10^3$ . Cell and device properties of the cross-point structure 8×8 array are reported. Lee *et al* also mentioned to use Pt/NiO/Pt as oxide resistive memory cell and Pt/p-NiO<sub>x</sub>/n-TiO<sub>x</sub>/Pt as oxide diode. All films were deposited by using DC magnetron sputtering. For the integration the total ratio of HRS/LRS is  $10^3$ , and the forward current over reverse current is  $10^5$ . However from the Fig. 2.7 we could find out that because of the large threshold voltage (1V) of the p-n diode, if the voltage is less than the 1V, the forward on current is still low, the reading voltage of the 1D1R structure should be much larger than 1V, so that the reading voltage will easily reach to the reset voltage range resulting in fake reset signal. Also the high reading voltage will lead to unnecessary power consumption, which will become worse in the crossbar array.

Figure 2.6 (a) Optical microscopic image including pads for our test array structures and image of the 8x8 cell array. (b) SEM image of Pt word and bit line. (c) TEM image of NiO storage element.[46]

Figure 2.7 The IV characteristics of the single memory cell, diode cell and the integration 1D1R structure.[46]

Third is the Schottky diode based 1D1R integration. Allen et al. announced the highly rectifying Schottky contacts on the n-type hydrothermal ZnO using silver oxide.[47] A 40~80 nm thick silver oxide film was deposited by the reactive RF sputtering of a Ag target (99.99% purity) using an Ar/O<sub>2</sub> plasma, a RF power of 50 W, and a processing pressure of  $4 \times 10^{-3}$  mbar (about  $3 \times 10^{-3}$  torr). A Pt capping layer was then deposited onto the silver oxide film by e-beam evaporation. However their structure is lateral structure and the distance between Schottky diode and Ohmic diode is 25 µm. Shima et al used Pt/TiOx/Pt for a resistive memory and a Schottky diode.[48] The trilayer with electrically asymmetrical interface is synthesized by means of the reactive sputtering technique followed by the oxygen annealing. The initial current-voltage characteristics in the Pt/TiO<sub>x</sub>/Pt tri-layer cell have rectifying behavior originated from the Schottky junction formed between  $TiO_x$  and Pt top electrode layer. In their device, the ratio of HRS over LRS was about 100 and it present 25 switching cycles and no decay is observed. Shin et al presented a Schottky-type diode switch consisting of a Pt/(In,  $Sn_2O_3/TiO_2/Pt$  stack for applications to the cross-bar type resistive –switching memory arrays.[49] Fig. 2.8 also showed the difference between p-n diode type and Schottky diode type of 1D1R resistance ratio. Just because of the confinement of the p-n diode in the low voltage, the resistance ratio cannot be larger than 10 below 1V. However the resistance ratio of the Schottky-type 1D1R structure could be as large as  $10^2$ . Tallarida *et* al also announced 1D1R structure of Ag/ZnO/Ti as Schottky diode and Au/TiO2/Au as unipolar memory cell. Their ratio of HRS over LRS is  $10^2$  and forward current over reverse current is 10<sup>5</sup>.[50] Recently, a ZnO-based 1D1R structure has been reported,

where the memory region and the diode region are separated and these two kinds of elements are interconnected horizontally using a common bottom electrode.[51]

Figure 2.8 The IV characteristics of ITO/TiO<sub>2</sub>-Pt/TiO2/Pt and CuO/IZO-Pt/NiO/Pt 1D1R structure.[49]

Recently some self-verifying diode is been used for 1D1R crossbar array. Kim *et al* presented the Ag/amorphous-Silicon/poly-Silicon can exhibit diode-like I-V characteristics at on-state with reverse bias current suppressed to below  $10^{-13}$  A and rectifying ratio is larger than  $10^6$ , just as the Fig. 2.9 shown.[52] However there might be some errors. In the ten consecutive switching IV curve it is shown that the device could be switched on at about 1.5V and with -1.5V it could be switched off. However in the response time testing the device need -3.5V to be turned off and -2V is not enough. So the two figures seem to be conflict with each other. Zuo *et al* also mentioned that n<sup>+</sup>-Si/ZrO<sub>2</sub>/Pt based memory cell also have the self-rectifying effect. The rectification ratio

is  $10^4$  and on/off ratio are  $10^6$ . However its program voltage should be as high as -12V, but need positive reading voltage [53]. In the crossbar array it is inconvenient to use positive voltage to read and use negative to set/reset, so it is common to use unipolar instead of bipolar for the 1D1R crossbar array.

Figure 2.9 The IV characteristics curve of the self-rectifying structure and the response time of the device. [52]

In summary, Schottky diode based 1D1R crossbar array has the advantage of good fabrication compatibility of diode and memory, low reading voltage and avoidance of two polarities for operation voltage, and have encouraging potential for further 1D1R cross-point array integration.

However, 1D1R structure is still a passive array and need the outside control module. To avoid outside circuits, 1-transistor 1-RS device (1T1R) RRAM cell structure is fabricated. The 1T1R structure is similar to a DRAM cell, and the capacitor is replaced by the RS device for non-volatile memory use. The data is stored as the resistance state of the RS device and the transistor is served as the access switch for reading and writing

data. The 1T1R cell used as a basic building block for a memory array could avoid the sneak current and ensure reliable operation as the R should be used as bipolar resistive switching device. Hsu *et al.* first proposed the 1T1R resistive switching memory array structure on a semiconductor substrate comprises forming an array of transistors comprising a polycide/oxide/nitride gate stack with nitride sidewalls, and the transistors comprising a source and a drain region adjacent to the gate stack. [54] Kurotsuchi et al [55] first fabricated the 1T1R structure with a Phase Change Memory (PCM, using O-GST film) as the memory and the programming current is less than 100  $\mu$ A. Later the HfO<sub>x</sub> based RRAM is connected with an external, commercial-used MOSFET and form the 1T1R structure and limit the operative current to be 20  $\mu$ A.[56] It is also calculated using a performance and energy model that the write access time is inversely proportional to minimum value of resistance and directly proportional to the square of oxide layer thickness. The read access time of the cell is only a function of the maximum value of resistance and does not change by the layer thickness. Read operation is one order of magnitude faster than write operation in the 1T1R cell. From energy perspective, the write operation is roughly three times more energy consuming than the read operation. The write energy increases quadratically for larger layer thicknesses while read energy dissipation depends only on the bit line capacitor and is not a function of the physical parameters of the device. [57] Another 1T1R structure is used to modulated the Ti/ZrO<sub>2</sub>/Pt resistive switching device to multilevel resistive switching state.[58] The dimension of HfOx-based RRAM has also been scaled down to 37 nm to meet the nanopillar transistor performance in the 1T1R structure, which also prove the prospect for

RRAM in the high-density applications. [59] To sum up, currently reducing power consumption and scaling down are two main tasks for 1T1R further memory applications.

## **2.5. Summary and Challenges of ZnO Resistive Switching Research**

In summary, we have shown that resistive switching device based on the resistive random access memory is a promising candidate for the further memory development. So far the resistive switching device could be fabricated as the unipolar switching device, bipolar switching devices, and threshold switching devices. Because of the unique advantages, ZnO and its nanostructures is a highly suitable material for resistive switching design. The discussion paves the way for developing the explanation of resistive switching mechanism. Single resistive switching device could be integrated for 1D1R and other applications.

Challenges for future memory design are also indicated from the review analysis. First, the resistive ratio for the resistive switching devices that reported so far is relatively low. The low resistive ratio will reduce the operation error tolerance and increase the risk of wrong readout signal in the memory architecture. The stability of the current resistive switching devices also needs to be optimized. Second, the mechanism of resistive switching is still not clear. The confused relationship between different switching modes blocks the way for the development of the resistive switching device. Third, the integration of the resistive switching is still facing the fabrication difficulties. Large cell size in the 1D1R blocks the development for the resistive switching in the matrix and other applications. In the next three chapters of this thesis, the solutions to the three challenges above are discussed.

## Chapter 3

# **ZnO-based Bipolar and Unipolar Resistive Switching Devices**

In the previous chapter, it is presented that transition-metal-doped ZnO is emerging as a promising material for the resistive switching device. ZnO based resistive switching devices possess advantages due to the well-controlled switching properties through *in-situ* doping and alloying, multifunctional achievement, high quality nanostructures, and low cost due to its abundant material source and relatively simple process. The unipolar resistance switching only depends on the magnitude but is independent of the polarity of the applied voltage, leading to easy operation with a unipolar voltage source. In addition, unipolar device could be used for passive matrix to save the cell area  $(4F^2)$ , and increase the density of the memory architecture. However, some digital electronics could only provide one supply voltages and one reference voltage (ground). In order to SET (forward bias) and RESET (reverse bias) the device, the resistive switching device should possess bipolar characteristics. In this chapter the different fabrication conditions has been introduced for both bipolar and unipolar resistive switching devices. Curve fitting method is presented for the conduction discussion. Parameter stability comparisons with different structures are also discussed. The thickness affects the polarity of the resistive switching, which could be used for different applications.

# 3.1. Device and Demonstration of Fe-doped ZnO Resistive Switching

Devices

## **3.1.1 FeZnO Single Layer Structure**

To make the RS device, metal-oxide-metal (MOM) structure is fabricated. Si wafers were used as substrates. A SiO<sub>2</sub> layer (300 nm thick) was formed on the Si substrate by thermal oxidization. A Pt/Ti (100 nm/5 nm) layer was deposited on  $SiO_2$  by e-beam evaporation, in which Ti was used as an adhesion layer and Pt as the bottom electrode. In the SL structure, the Fe<sub>x</sub>Zn<sub>1-x</sub>O (x~4%) layer (~70 nm) was directly grown on the Pt surface by metal-organic chemical vapor deposition (MOCVD) technique. Diethylzinc (DEZn) was chosen as Zn precursor, and ultra-high purity (UHP, >99.999%) Ar and O<sub>2</sub> gases were used as the carrier and oxidizer, respectively. Substrate temperature of  $450-500^{\circ}$ C and chamber pressure of ~50 torr was kept during the growth. The device patterns with a diameter of 80 µm were formed by photolithography and wet chemical etching using hydrochloric acid. Ag metal layer (~100 nm) was deposited by e-beam evaporation on the top of  $Fe_{0.04}Zn_{0.96}O$  film to serve as the top electrode. X-ray diffraction (XRD) ( $\theta$ -2 $\theta$  scan) measurements were carried out on the SL and BL structures using a Siemens D500 X-ray diffractometer. Hitachi (S-800) field-emission scanning electron microscopy (FESEM) was used to inspect the surface morphology and layer structures. I–V measurements were conducted using Agilent 4156C Semiconductor Parameters Analyzer.

## **3.1.2 FeZnO/MgO Bilayer Structure**

In the BL structure, a thin MgO layer (~5 nm) was grown on the Pt surface, then a  $Fe_xZn_{1-x}O$  (x~4%) layer was subsequentially grown on top of the MgO layer, both by MOCVD. For the MgO growth, bis(methylcyclopentadienyl) magnesium (MCp<sub>2</sub>Mg) and

UHP  $O_2$  were used as the Mg precursor and oxidizer, respectively. MgO was grown at a substrate temperature of 300-350 °C and the as-grown MgO layer appears to be amorphous. The Fe<sub>0.04</sub>Zn<sub>0.96</sub>O layer in the BL structure was grown under the same growth conditions as that in the SL structure.

Fig. 3.1(a) shows the schematics of the SL and BL bipolar RS structures and Fig. 3.1(b) is the SEM image of the Ag/FeZnO/MgO/Pt (BL) structure. Three obvious layers, consisting of bottom electrode, oxides and top electrode, are observed. Pt/Ti bottom electrode and Au/Ag top electrode appear to be single layers. The MgO layer is too thin to be observed in the SEM picture.

Figure 3.1 (a) The schematic diagrams of the bipolar resistive switching structures: the left diagram shows an Ag/FeZnO/Pt (SL) structure, and the right diagram shows an Ag/FeZnO/MgO/Pt (BL) structure; (b) an SEM image of the BL structure.

Figure 3.2 shows the XRD results of FeZnO SL and FeZnO/MgO BL structures grown on Pt/Ti/SiO<sub>2</sub>/Si substrates. The intensity is plotted on a log scale. All peaks in both samples can be indexed into three different phases, which are ZnO, Pt, and Si. As an adhesion layer, Ti is very thin and thus goes undetected in these XRD patterns. The asgrown MgO layer is amorphous. However, it could be re-crystallized during the subsequent Fe<sub>x</sub>Zn<sub>1-x</sub>O growth at high temperature (~  $450^{\circ}$ C). Small thickness (~5 nm) makes it still undetectable in XRD. The XRD patterns of  $Fe_xZn_{1-x}O(x\sim 4\%)$  are indexed by using diffraction data of ZnO (JCPDS ICDD PDF No. 89-0510). The FeZnO layers in both SL and BL structures show the wurtzite structure without a phase separation and they are highly textured along c-axis. However, additional peaks of (10-10) and (10-11) appear in the FeZnO layer of the BL structure (Fig. 3.2(b)) but not from the SL structure (Fig. 3.2(a)). This implies that the texturing of FeZnO layer grown on Pt is different from that grown on MgO surface. When a  $Fe_xZn_{1-x}O(x\sim4\%)$  layer is directly deposited on the Pt surface, due to a lack of epitaxial relationship, the adatoms (having high surface diffusion rate at substrate temperature) tend to arrange themselves toward the direction that has the lowest surface energy so that the FeZnO layer would grow predominantly along the c-axis direction, while growth of crystallites with other orientations is inhibited (Fig. 3.2(a)). However, when the FeZnO is grown on the MgO layer, MgO could be recrystallized and its crystalline grains provide crystallographic alignment to the FeZnO film, thus inducing growth along the other orientations besides c-axis (Fig. 3.2(b)). The growth mode will finally switch to the c-axis direction due to large surface energy anisotropy of ZnO. These phenomena are also observed on wurtzite ZnO (0001) epitaxial films grown on MgO substrates [60].

Figure 3.2 XRD spectra of the FeZnO deposited (a) on the Pt/Ti/SiO<sub>2</sub>/Si, and (b) on the MgO/Pt/Ti/SiO<sub>2</sub>/Si.

## 3.2. Polarity of FeZnO Resistive Switching Device

#### 3.2.1 Bipolar Resistive Switching

Fig. 3.3 exhibits the bipolar resistive switching characteristics of the Ag/FeZnO/Pt (SL) structure and the Ag/FeZnO/MgO/Pt (BL) structure. During the measurements, the bottom electrode is grounded and the varied voltage is applied on the top electrode. When voltage is less than the threshold switching voltage, the current is relatively small and the device is in the HRS. When the voltage reaches  $V_{SET}$ , the current increases dramatically

and the device switches to LRS. The switching device remains in LRS, until the voltage reduces to  $V_{RESET}$ , then the current decreases sharply and the device switches from LRS back to HRS. The reversible I-V curve loop indicates the memory behavior. Under the reading voltage that is usually chosen between  $V_{SET}$  and  $V_{RESET}$ , HRS and corresponding small current could be recognized as the logic "0" (OFF) while the large current in LRS represents the logic "1" (ON) in the memory circuit. Under a reading voltage of 0.2 V, the currents flow through the HRS and LRS of the SL structure are  $1.8 \times 10^{-5}$  A and  $6.8 \times 10^{-3}$  A, corresponding to the R<sub>HRS</sub> and R<sub>LRS</sub> of  $1.1 \times 10^4 \Omega$  and 29  $\Omega$ , respectively. The ratio of R<sub>HRS</sub>/R<sub>LRS</sub> is  $3.8 \times 10^2$ . The V<sub>SET</sub> is 0.70 V and the V<sub>RESET</sub> is -0.77 V, which corresponds to an electrical field of around 10 kV/cm. The electrical field is smaller than other reports for ZnO resistive switching devices in literatures, which could benefit the retention performance. Both threshold voltages are far away from the reading voltage, which can prevent the reading voltage from triggering the switching process and leading to severe problems in controlling and reading the memory switching states.

Figure 3.3 The I-V characteristics of the Ag/FeZnO/Pt (SL) structure and the Ag/FeZnO/MgO/Pt (BL) structure.

The I–V characteristics of the SL structure at HRS and LRS are also analyzed through curve fitting. The HRS curve from Fig. 3.4(a) is fitted well to the following equation:

$$\ln\left(\frac{I}{V}\right) = a_1 \times V^{\frac{1}{2}} + b \tag{1}$$

It accounts for the Poole-Frenkel emission (PFE) model,[61] which is

$$\ln\left(\frac{J}{E}\right) \propto q^{\frac{3}{2}} \left(\pi \varepsilon_r \varepsilon_0\right)^{-\frac{1}{2}} \left(rkT\right)^{-1} E^{\frac{1}{2}}$$

(2)

where J is the current density, E is the electric field, q is the electric charge,  $\varepsilon_r$  is the relative permittivity of the material,  $\varepsilon_0$  is the permittivity of free space, k is the boltzmann's constant, and T is the temperature. In the fitting of the equation (1) the value of a<sub>1</sub> and b are found to be 9.3 and -14, respectively. The well-fitted result implies that the dominant conduction mechanism in HRS is the emission of trapped electrons in the FeZnO layer. It is speculated that the resistive switching is attributed to the formation and rupture of conductive filaments that are related to the oxygen ions or metal ions. In fact, we observed that after annealing the samples under oxygen ambient, the devices were no longer able to make the complete resistive switching. At the LRS of Fig. 3.4(b), the IV curve is fitted well to the linear straight line I = a<sub>2</sub>V, where the fitting parameter value of a<sub>2</sub> is 3.4×10<sup>-2</sup>. Thus, the conduction mechanism in LRS follows the Ohmic behavior.

Figure 3.4 The curve fitting for measured I-V characteristics of the SL structure at (a) HRS and (b) LRS. The measured data are represented by square dots, and the fitting results are represented by straight lines.

Figure 3.3 also shows the *I–V* characteristics of the BL structure. Through comparison between these two structures, it can be seen that both structures have similar  $R_{LRS}$ ; however, they have significantly different  $R_{HRS}/R_{LRS}$  ratios. In the BL structure, the currents in HRS and LRS are  $6.5 \times 10^{-9}$  A and  $6.4 \times 10^{-3}$  A at 0.2 V, corresponding to the resistance values of  $3.1 \times 10^7 \Omega$  and  $31 \Omega$ , in HRS and LRS, respectively. The  $R_{HRS}$  of the BL increases by  $10^3$  over that of the SL structure. The ratio of  $R_{HRS}/R_{LRS}$  for the BL structure is  $9.9 \times 10^5$ , which is also more than three orders larger than that of the SL structure ( $3.8 \times 10^2$ ). The significantly enhanced  $R_{HRS}/R_{LRS}$  of the BL structure leads to a large difference in reading ON/OFF signal, which can minimize the confusion in reading signal of "0" and "1" when it is used for the nonvolatile memory applications.

Up to now, the measured retention times of both SL and BL structures are over  $10^7$  s (Fig. 3.5), indicating robust performance of the resistive switching devices. The high thermal stability from Fe doping in ZnO could result in better endurance performance. In comparison of the current values in the HRS of the SL and BL structures, the peak-to-valley ratios for the SL and BL curves are  $2.1 \times 10^2$  and 17, respectively. A narrower switching current distribution and a higher  $R_{HRS}/R_{LRS}$  ratio (>10<sup>5</sup>) are obtained simultaneously in the BL structure, which would lead to better and repeatable device performances. Since currents in the HRS and LRS are recognized as the OFF and ON signal in the reading step, the minimized dispersion of the currents is particularly desired for the reading process of the memory devices.

Figure 3.5 The retention time of the SL and BL structures.

Shown in Figure 3.6 are the switching voltage distributions of 20 cycles for the device with the SL and BL structure, respectively. In the SL structure, the reset voltages  $V_{RESET}$  are in the range of -0.91 V to -0.59 V, with the average voltage of -0.75 V, and a standard deviation of 0.097 V. In the BL structure, the  $V_{RESET}$  values are in the range of -0.97 V to -0.58 V, with the average voltage of -0.71 V and a standard deviation of 0.085 V. On the other hand, in the SL structure the set voltages  $V_{SET}$  are in the range of 0.46 V to 1.12 V, with the average voltage of 0.77 V, and a standard deviation of 0.21 V. In the BL structure the set voltages  $V_{SET}$  are in the range of 0.46 V to 1.12 V, with the average voltage of 0.77 V, and a standard deviation of 0.21 V. In the BL structure the set voltages are in the range of 1.21 V to 1.45 V, with the average voltage of 1.31 V and a standard deviation of 0.075 V. Both SL and BL structures have

similar value range and distribution of  $V_{RESET}$ . But the  $V_{SET}$  of the BL is larger than that of the SL structure. By comparing the standard deviation values, it is shown that the  $V_{SET}$ dispersion of the BL structure is significantly reduced in comparison with that of the SL structure. Since the  $V_{SET}$  value is directly related to the writing process of the memory, thus the narrow distribution of the  $V_{SET}$  would improve the stability of the memory devices.

Figure 3.6 The distribution of the operation voltages of the (a) SL and (b) BL structures.

## 3.3. Unipolar Resistive Switching

Figure 3.7(a) shows the I-V characteristics of the Au/Fe<sub>0.04</sub>Zn<sub>0.96</sub>O<sub>x</sub>/MgO/Pt unipolar resistive switching structure. The fabrication condition of unipolar RS structure is similar to that of bipolar RS device, the only difference is using Gold as the top electrode, At the beginning, the resistance state of the device is in HRS (step 1). When the applied voltage reaches the SET region, the device turns to LRS (step 2) and remains in LRS (step 3). When the voltage reaches the RESET voltage, the resistive state switches to HRS (step 4). When the measured voltage reaches 1V, the R<sub>HRS</sub>/R<sub>LRS</sub> ratio is  $2.4 \times 10^6$ . A retention time of  $10^7$  s has been obtained, and the results are shown in Figure 3.7(b). Higher fluctuations in HRS compared to LRS are due to the different conduction mechanisms between HRS and LRS. It is noteworthy to mention that after eight months (~2×10<sup>7</sup> s) and more than 200 testing cycles, the R<sub>HRS</sub>/R<sub>LRS</sub> ratio remained larger than  $10^5$ .

Figure 3.7 (a) The I-V characteristics and (b) retention time of the FeZnO/MgO switching resistor. The entire characterization was conducted at room temperature.

I-V characteristics of the unipolar switching device were also analyzed by curvefitting to different current transportation models. In Figure 3.8 (a), the I-V characteristics in LRS are fitted with a linear relation  $I = a_1 V$  in the log-log plot, where  $a_1 = 0.042 \text{ A/V}$ , indicating good ohmic characteristics. However, at higher bias voltages (>1.1 V), the I-V curve shows a slight deviation from the initial linearity, as indicated in Figure 3.8 (b). This deviation at higher voltages is attributed to the Joule heating effect, which could increase resistance of conducting paths before the onset of the rupture process, leading to HRS.

Fig. 3.8(c) illustrates the I-V characteristics of HRS and experimental results. The HRS curve is also fitted well to the following equation:

)

$$\ln\left(\frac{I}{V}\right) = a_2 \times V^{\frac{1}{2}} + b \tag{1}$$

where  $a_2 = 2.11$  and b = -19.9. It indicated the I-V characteristics of unipolar RS device at HRS also follow Poole-Frenkel emission (PFE) theory, as well as the bipolar RS device. At low voltages (<0.1V), it fits well with a linear relation of I =  $a_3$ V as shown in Fig. 3.9(a), where  $a_3 = 4.4 \times 10^{-9}$  A/V, which is  $\sim 10^7$  times less than  $a_1$ . This could result from the fact that the RESET process may not have totally ruptured all the conducting paths formed during the SET process, and thus there still exist a few conducting paths, which provide ohmic conduction with much higher resistance. From the curve fitting analysis, the resistive switching might result from the formation and rupture of the conducting paths composed by deep-level defects, such as oxygen vacancies (V<sub>o</sub>), which serve as the positive charges according to the PFE model. In the FeZnO/MgO bilayer memory stack, the bonding energy of MgO is higher than that of ZnO, resulting in more difficulties in forming the Vo in the MgO layer than in the FeZnO layer. By adding a MgO layer to form the FeZnO/MgO bilayer switching structure, the Vo and related

conducting filaments are suppressed, resulting in higher HRS and more uniform performance of the resistive switching.