### HIGH-THROUGHPUT FPGA QC-LDPC DECODER ARCHITECTURE FOR 5G WIRELESS

BY SWAPNIL MHASKE

A thesis submitted to the

Graduate School—New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

Master of Science

Graduate Program in Electrical and Computer Engineering

Written under the direction of

**Professor Predrag Spasojevic**

and approved by

New Brunswick, New Jersey October, 2015 © 2015 Swapnil Mhaske ALL RIGHTS RESERVED

#### ABSTRACT OF THE THESIS

### High-Throughput FPGA QC-LDPC Decoder Architecture for 5G Wireless

### by Swapnil Mhaske Thesis Director: Professor Predrag Spasojevic

Wireless data traffic is expected to increase by a 1000 fold by the year 2020 with more than 50 billion devices connected to these wireless networks with peak data rates upto 10 Gb/s. The next generation of wireless cellular technology (being collectively termed as 5G) is slated to operate in the mm-wave (30-300GHz) spectrum which comes with challenges such as, reliance on line of sight (LOS) communication, short range of communication, increased shadowing and, rapid fading in time. This will necessitate additional signal processing techniques such as large antenna arrays and beamsteering which will further reduce the processing budget available to the channel coding system.

In an effort to design and develop a channel coding solution suitable to such systems, in this thesis we propose strategies to achieve a high-throughput FPGA-based decoder architecture for a QC-LDPC code based on circulant-1 identity matrix construction. We present a novel representation of the parity-check matrix (PCM) providing a multifold throughput gain. Splitting of the node processing algorithm enables us to achieve pipelining of blocks and hence layers. By partitioning the PCM into not only layers but superlayers, we derive an upper bound on the pipelining depth with respect to the size of the superlayer for the compact representation. To validate the architecture, a decoder for the *IEEE 802.11n (2012)* QC-LDPC is implemented on the *Xilinx Kintex-7* FPGA with the help of the FPGA IP compiler available in the NI Lab  $VIEW^{TM}$  Communication System Design Suite (CSDS<sup>TM</sup>). It offers an automated and systematic compilation flow. An optimized hardware implementation from the decoder algorithm was generated in approximately 3 minutes, achieving an overall throughput of 608Mb/s (at 260MHz). With little or no modifications, the proposed decoder architecture caters to a wide range of circulant-1 identity matrix construction based QC-LDPC codes widely accepted in several communication and data storage standards.

#### Acknowledgements

I would like to thank my advisor Prof. Predrag Spasojevic for having faith in me and guiding me throughout the course of this research work, the importance of his advice cannot be overstated. Special thanks to Prof. Roy Yates and Prof. Zoran Gajic for being a part of my thesis committee.

I would also like to thank my colleagues Hojin Kee and Tai Ly in the LabVIEW FPGA R&D, National Instruments, Austin for their valuable feedback and guidance. I am especially grateful to Ahsan Aziz and the Advanced Wireless Research team in National Instruments, Austin for their support. I am thankful to Christopher Mueller-Smith for his help and contribution toward developing the BCJR decoding algorithm for the 3GPP turbo decoder during the very initial phase of this project. Many thanks go out to the Department of Electrical & Computer Engineering, Rutgers University for their continual support for this research work.

Finally, I thank my parents and my dear friends Chaitral and Manasa, without their love and encouragement this would not have been possible.

# Dedication

To Aai, Baba, Tai, Ajay & Adu

### Table of Contents

| Abstract                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| Acknowledgements                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Dedication                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| List of Tables                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |

| List of Figures                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |  |  |

| <b>1. Introduction</b>                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2. Quasi-Cyclic LDPC Codes and Decoding                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2.1. Quasi-Cyclic LDPC Codes                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2.2. Scaled Min-Sum Algorithm (MSA) for Decoding QC-LDPC Codes $\ldots$ 6                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3. Strategies to Achieve High-throughput                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3.1. Linear Complexity Node Processing                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3.2. z-fold Parallelization of NPUs $\ldots \ldots \ldots$ |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3.3. Layered Decoding                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3.4. Compact Representation of $\mathbf{H}_b$                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 4. Layer-Pipelined Decoder Architecture                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 4.1. Pipelining GNPU and LNPU Arrays                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

| <b>5.</b> Case Study                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6. Application                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 2.48Gb/s QC-LDPC Decoder on the NI USRP-2953R 29                                                                                                                           |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6.1. Multi-core Decoder                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  |

| 6.2. Results            |  |

|-------------------------|--|

| 7. Related Work         |  |

| 3GPP UMTS Turbo Decoder |  |

| 8. Conclusion           |  |

| References              |  |

### List of Tables

| 2.1. | Base matrix $\mathbf{H}_b$ for $z = 81$ specified in IEEE 802.11n (2012) standard                           |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | used in the case study. $L_1 - L_{12}$ are the layers and $B_1 - B_{24}$ are the block                      |    |

|      | columns (see Section $3.3$ ). Valid blocks (see section $3.4$ ) are highlighted.                            | 5  |

| 3.1. | Arbitrary submatrix $\mathbf{I}_s$ in $\mathbf{H}$ , $0 \leq J \leq n_b - 1$ , illustrating the opportunity |    |

|      | to parallelize $z$ NPUs                                                                                     | 11 |

| 3.2. | Illustration of Message Passing in row-layered decoding in a Section of                                     |    |

|      | the PCM $\mathbf{H}_b$                                                                                      | 14 |

| 3.3. | Block index matrix $\beta_I$ showing the valid blocks (highlighted) to be pro-                              |    |

|      | cessed                                                                                                      | 15 |

| 3.4. | Block shift matrix $\beta_S$ showing the right-shift values for the valid blocks                            |    |

|      | to be processed                                                                                             | 17 |

| 4.1. | Rearranged Block Index Matrix $oldsymbol{eta}_I'$ used for our work, showing the valid                      |    |

|      | blocks (highlighted) to be processed                                                                        | 19 |

| 5.1. | LDPC Decoder IP FPGA Resource Utilization & Throughput on the                                               |    |

|      | Xilinx Kintex-7 FPGA.                                                                                       | 27 |

| 6.1. | Performance and resource utilization comparison for the Baseline archi-                                     |    |

|      | tecture with the Pipelined architecture of the QC-LDPC decoder on the                                       |    |

|      | NI USRP-2953R containing the Xilinx Kintex7 (410t) FPGA                                                     | 33 |

| 6.2. | Performance and resource utilization comparison for versions with vary-                                     |    |

|      | ing number of cores of the QC-LDPC decoder implemented on the $N\!I$                                        |    |

|      | USRP-2953R containing the Xilinx Kintex7 (410t) FPGA                                                        | 34 |

| 7.1. | Turbo Decoder IP FPGA Resource Utilization & Throughput on the                                              |    |

|      | Xilinx Kintex-7 XC7K325T-2L-FFG900                                                                          | 37 |

# List of Figures

| 2.1. | A Tanner graph where VNs (representing the code bits) are shown as           |    |

|------|------------------------------------------------------------------------------|----|

|      | circles and CNs (representing the parity-check equations) are shown as       |    |

|      | squares. Each edge in the graph corresponds to a non-zero entry (1 for       |    |

|      | binary LDPC codes) in the PCM $\mathbf{H}.$                                  | 4  |

| 2.2. | An instance of extrinsic message computation at CN $i$ and its transfer      |    |

|      | to VN $j$ on the Tanner graph. It is important to note that the VTC          |    |

|      | message from VN $j$ is not included in the computation (indicated by a       |    |

|      | dashed line) as CN $i$ intends to send it to VN $j$ itself                   | 7  |

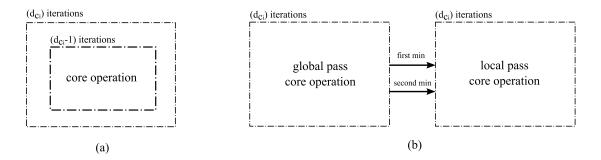

| 3.1. | For-loop view of processing complexity (a) without two pass computation      |    |

|      | (b) with two pass computation                                                | 10 |

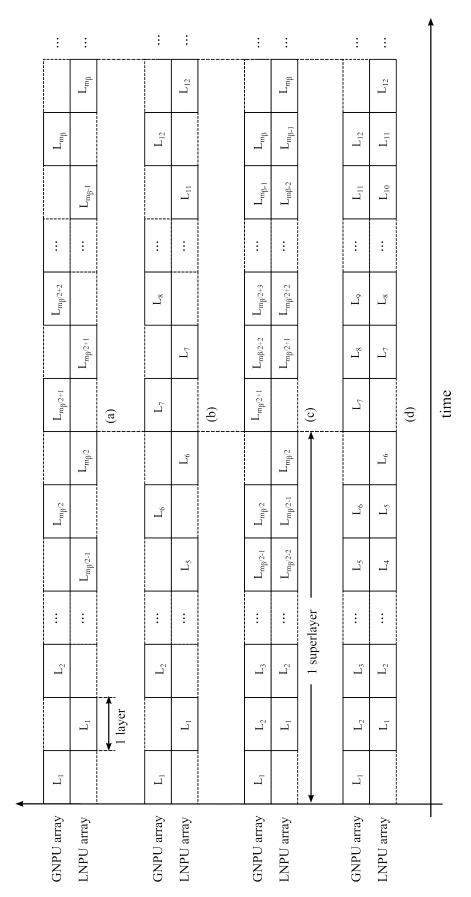

| 4.1. | Block-level view of the pipeline timing diagram. (a) General case for a      |    |

|      | circulant-1 identity submatrix construction based QC-LDPC code (see          |    |

|      | Section 2.1) without pipelining. (b) Special case of the IEEE 802.11n QC- $$ |    |

|      | LDPC code used in this work without pipelining (c) Pipelined processing      |    |

|      | of two layers for the general QC-LDPC code case in (a). (d) Pipelined        |    |

|      | processing of two layers for the IEEE802.11n QC-LDPC code case in (b).       | 22 |

| 4.2. | Layer-level view of the pipeline timing diagram. (a) General case for a      |    |

|      | circulant-1 identity submatrix construction based QC-LDPC code (see          |    |

|      | Section 2.1) without pipelining. (b) Special case of the IEEE 802.11n QC- $$ |    |

|      | LDPC code used in this work without pipelining (c) Pipelined processing      |    |

|      | of two layers for the general QC-LDPC code case in (a). (d) Pipelined        |    |

|      | processing of two layers for the IEEE802.11n QC-LDPC code case in (b).       | 23 |

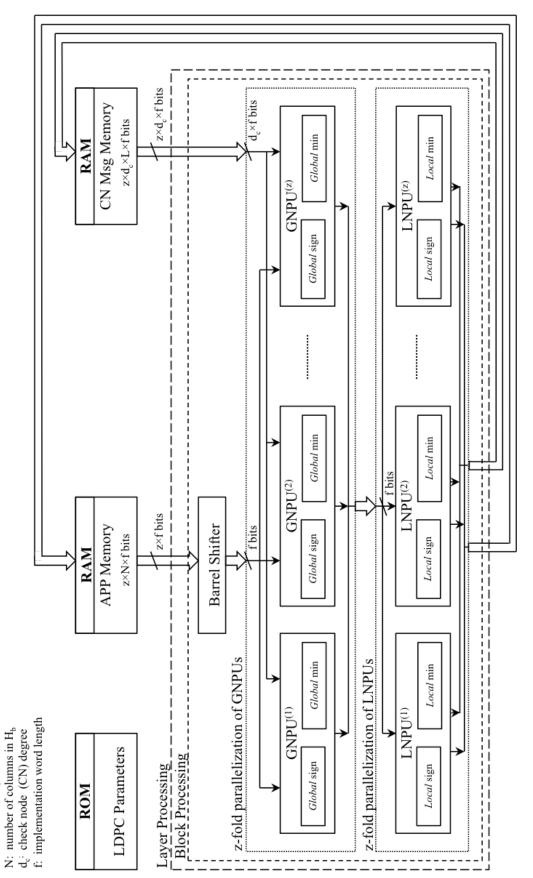

| 4.3. | High-level decoder architecture. showing the z-fold parallelization of the       |    |

|------|----------------------------------------------------------------------------------|----|

|      | NPUs with an emphasis on the splitting of the sign and the minimum               |    |

|      | computation given in equation $(2.3)$ . Note that, other computations in         |    |

|      | equations $(2.1)$ - $(2.4)$ are not shown for simplicity here. For both the      |    |

|      | pipelined and the non-pipelined versions, processing schedule for the in-        |    |

|      | ner Block Processing loop is as per Fig. 4.1 and that for the outer Layer        |    |

|      | Processing loop is as per Fig. 4.2.                                              | 25 |

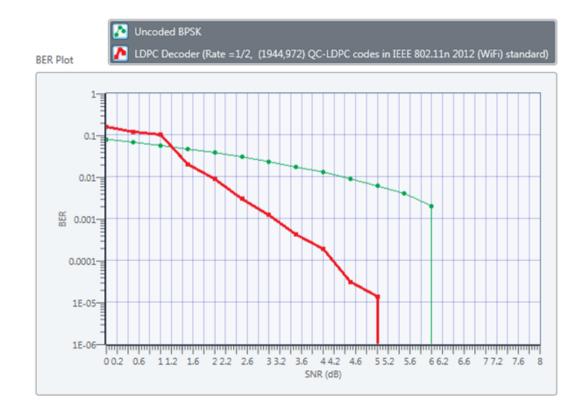

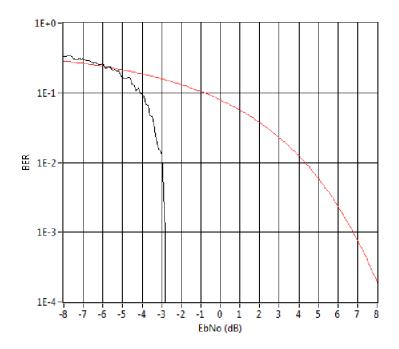

| 5.1. | Bit Error Rate (BER) performance comparison between uncoded BPSK                 |    |

|      | (rightmost), rate= $1/2$ LDPC with 4 iterations using fixed-point data           |    |

|      | representation (second from right), rate= $1/2$ LDPC with 8 iterations           |    |

|      | using fixed-point data representation (third from right), rate= $1/2$ LDPC       |    |

|      | with 8 iterations using floating-point data representation (leftmost). $\ . \ .$ | 28 |

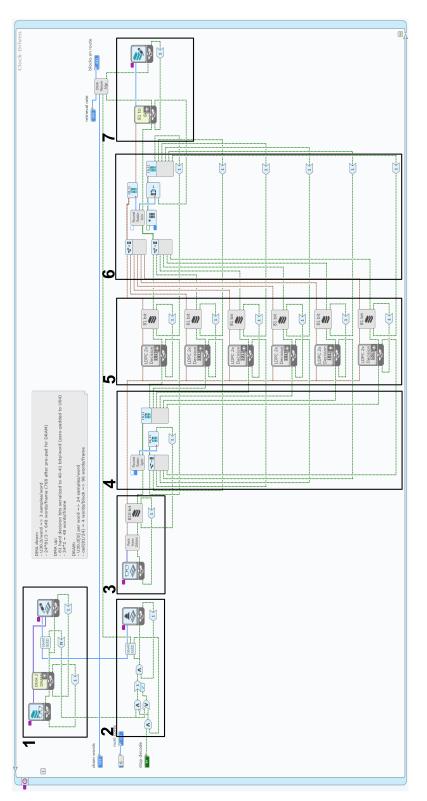

| 6.1. | Top-level VI describing the parallelization of the QC-LDPC decoder [1]           |    |

|      | on the NI USRP-2953R containing the Xilinx Kintex7 (410t) FPGA                   | 32 |

| 6.2. | Bit Error Rate (BER) performance comparison between uncoded BPSK                 |    |

|      | (green) and the 2.48<br>Gb/s, rate=1/2, QC-LDPC decoder (red) on the $N\!I$      |    |

|      | USRP-2953R containing the Xilinx Kintex7 (410t) FPGA                             | 34 |

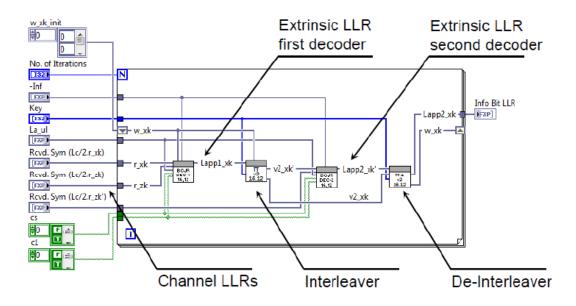

| 7.1. | Turbo Decoder Iterative Log-MAP Decoder                                          | 36 |

| 7.2. | BER performance of the aforementioned turbo decoder (curve on the left           |    |

|      | in black) versus uncoded BPSK (curve on the right in red)                        | 37 |

# Chapter 1

### Introduction

For the next generation of wireless technology collectively termed as Beyond-4G and 5G (hereafter referred to as 5G), peak data rates of up to ten Gb/s with overall latency less than 1ms [2] are envisioned. However, due to the proposed operation in the 30-300GHz range with challenges such as short range of communication, increasing shadowing and rapid fading in time, the processing complexity of the system is expected to be high. In an effort to design and develop a channel coding solution suitable to such systems, in this report, we present a high-throughput, scalable and reconfigurable FPGA decoder architecture for circulant-1 identity matrix construction based QC-LDPC codes.

It is well known that the structure offered by QC-LDPC codes [3] makes them amenable to time and space efficient decoder implementations relative to random LDPC codes. We believe that, given the primary requirements of high decoding throughput, QC-LDPC codes or their variants (such as accumulator-based codes [4]) that can be decoded using belief propagation (BP) methods are highly likely candidates for 5G systems. Thus, for the sole purpose of validating the proposed architecture, we chose a standard compliant code, with a throughput performance that well surpasses the requirement of the chosen standard. The proposed decoder architecture can be used for a wide range of circulant-1 identity construction based QC-LDPC codes many of which have been accepted in several standards such as IEEE 802.11n/ac [5], IEEE 802.16e/m [6] and DVB [7].

Insightful work on high-throughput (order of Gb/s) BP-based QC-LDPC decoders is available, however, most of such works focus on an ASIC design [8], [9] which usually requires intricate customizations at the Register Transfer Level (RTL) level and expert knowledge of VLSI design. A sizeable subset of which caters to fully-parallel [10] or code-specific [11] architectures. From the point of view of an evolving research solution this is not an attractive option, especially for rapid-prototyping. In the relatively less explored area of FPGA-based implementation, impressive results have recently been presented in works such as [12],[13] and [14]. However, these are based on fully-parallel architectures which lack flexibility (code specific) and are limited to small block sizes (primarily due to the inhibiting routing congestion) as discussed in the informative overview in [15]. Since our case study is based on fully-automated generation of the Hardware Description Language (HDL), a fair comparison is done with another state-ofthe-art implementation [16] in Chapter 5. Moreover, in this report, we provide without loss of generality, strategies to achieve a high-throughput FPGA-based architecture for a QC-LDPC code based on a circulant-1 identity matrix construction.

The main contribution of this work is a compact representation (matrix form) of the PCM of the QC-LDPC code which provides a multi-fold increase in throughput. In spite of the resulting reduction in the *degrees of freedom* for pipelined processing, we achieve efficient pipelining of two-layers and also provide without loss of generality an upper bound on the pipelining depth that can be achieved in this manner. The splitting of the node processing allows us to achieve the said degree of pipelining without utilizing additional hardware resources. The algorithmic strategies were realized in hardware for our case study by the *FPGA IP* [17] compiler in *LabVIEW<sup>TM</sup> CSDS<sup>TM</sup>* which translated the entire software-pipelined high-level language description into VH-SIC Hardware Description Language (VHDL) in approximately 3 minutes, enabling state-of-the-art rapid-prototyping. The scalability of the proposed architecture has been demonstrated in an application that achieves a throughput of 2.48Gb/s [18] on the NI USRP-2953R.

The remainder of this report is organized as follows. Chapter 2 describes the QC-LDPC codes and the decoding algorithm chosen for this implementation. The strategies for achieving high throughput are explained in Chapter 3. The details of the layered decoding technique applied in this work are given in Chapter 4. The case study for the IEEE 802.11n (2012) standard is discussed in Chapter 5, developments that contributed towards this work are presented in Chapter 7 and we conclude with Chapter 8.

#### Chapter 2

### Quasi-Cyclic LDPC Codes and Decoding

LDPC codes (due to R. Gallager [19]) are a class of linear block codes that have been shown to achieve near-capacity performance on a broad range of channels and are characterized by a low-density (sparse) PCM representation.

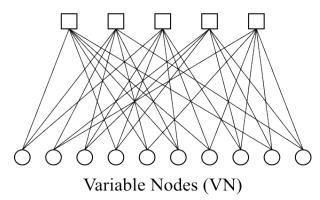

Mathematically, an LDPC code is a null-space of its  $m \times n$  PCM **H**, where m denotes the number of parity-check equations or parity-bits and n denotes the number of variable nodes or code bits [3]. In other words, for a rank m PCM **H**, m is the number of redundant bits added to the k information bits, which together form the codeword of length n = k + m. In the Tanner graph representation (due to Tanner [20]), **H** is the incidence matrix of a bipartite graph comprising of the check node (CN) set of m parity-check equations and the variable node (VN) set of n variable or bit nodes; the  $i^{th}$  CN is connected to the  $j^{th}$  VN if  $\mathbf{H}(i,j) = 1$ ,  $1 \leq i \leq m$  and  $1 \leq j \leq n$ . A toy example of a Tanner graph is shown in Fig. 2.1. The set of VNs that are connected with an edge to CN i (hereafter referred to as  $\mathcal{N}(i)$ ) is called as the neighbor set of CN i. Similarly,  $\mathcal{N}(j)$  is the neighbor set of VN j. The degree  $d_{c_i} (d_{v_j})$  of a CN i (VN j) is equal to the number of 1s along the  $i^{th}$  row  $(j^{th}$  column) of **H**. For constants  $c_c, c_v \in \mathbb{Z}_{>0}$  and  $c_c << m, c_v << n$ , if  $\forall i, j, d_{c_i} = c_c$  and  $d_{v_j} = c_v$ , then the LDPC code is called as a regular code and is called an irregular code otherwise.

#### 2.1 Quasi-Cyclic LDPC Codes

The first LDPC codes by Gallager are random i.e. the neighbors of an arbitrary CN or VN are randomly chosen, subject to constraints specified in the code construction algorithm. One such constraint is the *girth* of the Tanner graph underlying the LDPC code structure. Here girth refers to the length of the smallest cycle in the Tanner graph.

#### Check Nodes (CN)

Figure 2.1: A Tanner graph where VNs (representing the code bits) are shown as circles and CNs (representing the parity-check equations) are shown as squares. Each edge in the graph corresponds to a non-zero entry (1 for binary LDPC codes) in the PCM **H**.

Random code structures complicate the decoder implementation, mainly because a random interconnect pattern between the VNs and CNs directly translates to a complex wire routing circuit on hardware. QC-LDPC codes belong to the class of structured codes that are relatively easier to implement without significantly compromising performance.

The construction of identity matrix based QC-LDPC codes relies on an  $m_b \times n_b$  matrix  $\mathbf{H}_b$  sometimes called as the *base matrix* which comprises of cyclically right-shifted identity and zero submatrices both of size  $z \times z$  where,  $z \in \mathbb{Z}^+, 1 \leq i_b \leq m_b$  and  $1 \leq j_b \leq n_b$ , the shift value,

$$s = \mathbf{H}_b(i_b, j_b) \in \mathcal{S} = \{-1\} \cup \{0, \dots, z-1\}$$

The PCM matrix **H** is obtained by *expanding*  $\mathbf{H}_b$  using the mapping,

$$s \longrightarrow \begin{cases} \mathbf{I}_s, & s \in \mathcal{S} \setminus \{-1\} \\ \mathbf{0}, & s \in \{-1\} \end{cases}$$

where,  $\mathbf{I}_s$  is an identity matrix of size z which is cyclically right-shifted by  $s = \mathbf{H}_b(i_b, j_b)$ and  $\mathbf{0}$  is the all-zero matrix of size  $z \times z$ . As  $\mathbf{H}$  is composed of the submatrices  $\mathbf{I}_s$  and  $\mathbf{0}$ , it has  $m = m_b.z$  rows and  $n = n_b.z$  columns.  $\mathbf{H}$  for the *IEEE 802.11n (2012)* standard [5] (used for our case study) with z = 81 is shown in Table 2.1.

| ${\bf Layers} \ \downarrow$ | $\qquad \qquad $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | $B_1 \ B_2 \ B_3 \ B_4 \ B_5 \ B_6 \ B_7 \ B_8 \ B_9 \ B_{10} B_{11} B_{12} B_{13} B_{14} B_{15} B_{16} B_{17} B_{18} B_{19} B_{20} B_{21} B_{23} B_{24}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| L <sub>1</sub>              | 57 -1 -1 -1 50 -1 11 -1 50 -1 79 -1 1 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $L_2$                       | 3 -1 28 -1 0 -1 -1 -1 55 7 -1 -1 -1 0 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\mathrm{L}_3$              | 30       -1       -1       24       37       -1       -1       56       14       -1       -1       -1       0       0       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ${f L}_4$                   | 62       53       -1       -1       3       35       -1       -1       -1       -1       1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\mathrm{L}_5$              | 40 -1 -1 20 66 -1 -1 22 28 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $L_6$                       | 0 -1 -1 -1 8 -1 42 -1 50 -1 -1 8 -1 -1 -1 -1 -1 -1 -1 -1 -1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $L_7$                       | 69       79       79       -1       -1       52       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1 <td< th=""></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $L_8$                       | 65       -1       -1       -1       72       -1       27       -1       -1       -1       -1       -1       0       0       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\mathrm{L}_9$              | 64       -1       -1       1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1       -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $\mathbf{L}_{10}$           | $-1 \ \ 45 \ -1 \ \ 70 \ \ 0 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 \ \ -1 $ |

| $\mathbf{L}_{11}$           | 2 56 -1 57 35 -1 -1 -1 -1 -1 -1 12 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $L_{12}$                    | 24 -1 61 -1 60 -1 -1 27 51 -1 -1 16 1 -1 -1 16 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2.1: Base matrix  $\mathbf{H}_b$  for z = 81 specified in IEEE 802.11n (2012) standard used in the case study.  $L_1 - L_{12}$  are the layers and  $B_1 - B_{24}$  are the block columns (see Section 3.3). Valid blocks (see section 3.4) are highlighted.

5

#### 2.2 Scaled Min-Sum Algorithm (MSA) for Decoding QC-LDPC Codes

Owing to the sparsity of the PCM of an LDPC code and the computational power available today, it is practicable to decode LDPC codes using iterative message passing (MP) or belief propagation (BP) [19, 21] (name picked up from Bayesian-inference literature) on the bipartite Tanner graph. Gallager's method of BP decoding - called as the Sum-Product Algorithm (SPA) [19] is a general algorithm that provides nearoptimal performance for a wide range of channels. The MSA is a reduced complexity version of the SPA which has a small loss in performance.

As the name suggests, in MP decoding, the CNs and VNs communicate with each other, successively passing revised estimates or *messages* of the a posteriori probability (APP) log-likelihood ratios (LLR) of the associated VNs or code bits, in every decoding iteration. In this work we have employed the efficient decoding algorithm presented in [22], with pipelined processing of layers based on the row-layered decoding technique [23], detailed in Section 3.3.

**Definition 1.** For  $1 \le i \le m$  and  $1 \le j \le n$ , let  $v_j$  denote the  $j^{th}$  bit in the length n codeword and  $y_j = v_j + n_j$  denote the corresponding received value from the channel corrupted by the noise sample  $n_j$ . Let the variable-to-check (VTC) message from VN j to CN i be  $q_{ij}$  and, let the check-to-variable (CTV) message from CN i to VN j be  $r_{ij}$ . Let the a posteriori probability (APP) ratio for VN j be denoted as  $p_j$ .

The steps of the scaled-MSA [24] are given below.

1. Initialize the APP ratio and the CTV messages as,

$$p_j^{(0)} = ln \left\{ \frac{P(v_j = 0|y_j)}{P(v_j = 1|y_j)} \right\}, \quad 1 \le j \le n$$

$$r_{ij}^{(0)} = 0, \quad 1 \le i \le m, 1 \le j \le n$$

(2.1)

2. Iteratively compute at the  $t^{th}$  decoding iteration,

$$q_{ij}^{(t)} = p_j^{(t-1)} - r_{ij}^{(t-1)}$$

(2.2)

$$r_{ij}^{(t)} = a \cdot \prod_{k \in \mathcal{N}(i) \setminus \{j\}} sign\left(q_{ik}^{(t)}\right) \cdot \min_{k \in \mathcal{N}(i) \setminus \{j\}} \left\{ |q_{ik}^{(t)}| \right\}$$

(2.3)

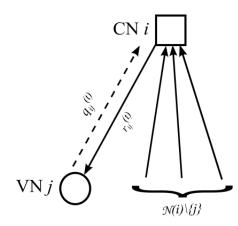

Figure 2.2: An instance of extrinsic message computation at CN i and its transfer to VN j on the Tanner graph. It is important to note that the VTC message from VN j is not included in the computation (indicated by a dashed line) as CN i intends to send it to VN j itself.

$$p_j^{(t)} = q_{ij}^{(t)} + r_{ij}^{(t)}$$

(2.4)

where,  $1 \leq i \leq m$ , and  $k \in \mathcal{N}(i) \setminus \{j\}$  represents the set of the VN neighbors of CN *i* excluding VN *j*. An instance of this message exchange is shown in Fig. 2.2. Let  $t_{max}$  be the maximum number of decoding iterations.

3. Decision on the code bit  $v_j$ ,  $1 \le j \le n$  as,

$$\hat{v}_j = \begin{cases}

1, & p_j \le 0 \\

0, & otherwise

\end{cases}$$

(2.5)

4. If  $\hat{\mathbf{v}}\mathbf{H}^T = 0$ , where  $\hat{\mathbf{v}} = (\hat{v}_1, \hat{v}_2, \dots, \hat{v}_n)$ , or  $t = t_{max}$ , declare  $\hat{\mathbf{v}}$  as the decoded codeword.

It is well known that since the MSA is an approximation of the SPA, the performance of the MSA is relatively worse than the SPA [3]. However, in [24] it has been shown that scaling the CTV messages  $r_{ij}$  can improve the performance of the MSA. Hence, we scale the CTV messages by a factor a (=0.75).

*Remark* 1. The standard MP algorithm is based on the so-called *flooding* or *two-phase* schedule where, each decoding iteration comprises of two phases. In the first phase, VTC messages for all the VNs are computed and in the second phase the CTV messages for all the CNs are computed, strictly in that order. Thus, message updates from one

side of the graph propagate to the other side only in the next decoding iteration. In the algorithm that we have used [22] however, message updates can propagate across the graph in the same decoding iteration resulting in the following advantages:

- 1. Single processing unit: Since the VTC messages  $q_{ij}$  given by equation (2.2) can be computed on the fly (i.e.  $q_{ij}$  updates are immediately consumed by the CTV  $r_{ij}$ computation) in the same decoding iteration, there is no need to have a separate VN processing unit, unlike that in the standard MP algorithm. The single node processing unit (NPU) computes both the CN and the VN messages.

- 2. Reduced memory storage: The on the fly computation of the VTC messages  $q_{ij}$  also implies that there is no need to store the VN messages separately.

- 3. Fast convergence: It has been shown in [22] that the algorithm we have employed in our work converges faster than the standard MP flooding schedule. This means that comparable performance can be achieved by the algorithm described in this Section with fewer decoding iterations, thus helping the high-throughput implementation of the decoder.

#### Chapter 3

#### Strategies to Achieve High-throughput

To understand the high-throughput requirements for LDPC decoding, let us first define the decoding throughput T of the hardware realization of an LDPC decoder based on an iterative MP decoding algorithm.

**Definition 2.** Let  $F_c$  be the clock frequency, n be the code length,  $N_i$  be the number of decoding iterations and  $N_c$  be the number of clock cycles per decoding iteration, then the throughput of the decoder is broadly given by,  $T = \frac{F_c \cdot n}{N_i \cdot N_c} b/s$ .

Even though, n and  $N_i$  are functions of the code and the decoding algorithm used,  $F_c$  and  $N_c$  are determined by the hardware architecture. Architectural optimization such as the ability to operate the decoder at higher clock rates with minimal latency between decoding iterations can help achieve higher throughput. We have employed the following techniques to increase the throughput given by Definition 2.

#### 3.1 Linear Complexity Node Processing

As noted in Section 2.2, separate processing units for CNs and VNs are not required unlike that for the flooding schedule. The hardware elements that process equations (2.2)-(2.4) are collectively referred to as the Node Processing Unit (NPU).

Careful observation reveals that, among equations (2.2)-(2.4), processing the CTV messages  $r_{ij}$ ,  $1 \leq i \leq m$  and  $1 \leq j \leq n$  is the most computationally intensive due to the calculation of the sign, and the minimum value operations. Note that, computing the CTV message  $r_{ij}$  from CN *i* to VN *j* (in equation 2.3) involves processing the metrics for VNs in the set  $\mathcal{N}(i) \setminus \{j\}$ , not  $\mathcal{N}(i)$ . Thus, the complexity of processing these values is  $\mathcal{O}(d_{c_i}^2)$ . A naive implementation of the minimum process in (2.3) could be an

Figure 3.1: For-loop view of processing complexity (a) without two pass computation (b) with two pass computation.

algorithm that traverses over all  $d_{c_i}$  branches of CN *i* and compares two values at a time translating into  $d_{c_i}$  comparator-based *min-trees* with  $(d_{c_i} - 1)$  leaf nodes each. In software, this translates to two nested for-loops, an outer loop that executes  $d_{c_i}$  times and an inner loop that executes  $(d_{c_i} - 1)$  times. This is shown in Fig. 3.1 (a).

To achieve linear complexity  $\mathcal{O}(d_{c_i})$  for the minimum value computation, we split the process into two phases or passes: the global pass where the first and the second minimum (the smallest value in the set excluding the minimum value of the set) for all the neighboring VNs of a CN are computed and the *local* pass where the first and second minimum from the global pass are used to compute the minimum value for each neighboring VN. Based on the functionality of the two passes, the NPU is divided into the Global NPU (GNPU) and the Local NPU (LNPU). The detailed steps of the algorithm are given below.

#### 1. Global Pass:

i. Initialization: Let  $\ell$  denote the discrete time-steps such that,  $\ell \in \{0\} \cup \{1, 2, \dots, |\mathcal{N}(i)|\}$  and let  $f^{(\ell)}$  and  $s^{(\ell)}$  denote the value of the first and the second minimum at time  $\ell$  respectively. The initial value at time  $\ell = 0$  is,

$$f^{(0)} = s^{(0)} = \infty. (3.1)$$

ii. Comparison: Let  $k_i(\ell) \in \mathcal{N}(i), \ell = \{1, 2, ..., |\mathcal{N}(i)|\}$ , denote the index of the  $\ell^{th}$  neighboring VN of CN *i*. Note that,  $k_i(\ell)$  depends on *i* and  $\ell$ , specifically, for a given CN *i* it is a bijective function of  $\ell$ . An increment from  $(\ell - 1)$  to

|                               | $VN_{zJ}$ |      |   | $\mathbf{VN}_{\mathbf{zJ+l}}$ |   | $\mathbf{VN}_{\mathbf{z}(\mathbf{J+1})-1}$ |   |

|-------------------------------|-----------|------|---|-------------------------------|---|--------------------------------------------|---|

| $\mathbf{NPU}_{0}$            | 0         | •••  | 0 | 1                             | 0 | •••                                        | 0 |

| $\mathrm{NPU}_1$              | 0         | •••  | 0 | 0                             | 1 | •••                                        | 0 |

| :                             | :         |      |   |                               |   |                                            | ÷ |

| $\rm NPU_{z-2}$               | 0         | •••• | 0 | 0                             | 0 | •••                                        | 0 |

| $\mathbf{NPU}_{\mathbf{z}-1}$ | 0         | •••  | 1 | 0                             | 0 | •••                                        | 0 |

Table 3.1: Arbitrary submatrix  $\mathbf{I}_s$  in  $\mathbf{H}$ ,  $0 \leq J \leq n_b - 1$ , illustrating the opportunity to parallelize z NPUs.

$\ell$  corresponds to moving from the edge CN  $i \leftrightarrow$  VN  $k_i(\ell - 1)$  to the edge CN  $i \leftrightarrow$  VN  $k_i(\ell)$ .

$$f^{(\ell)} = \begin{cases} |q_{ik_i(\ell)}|, |q_{ik_i(\ell)}| \le f^{(\ell-1)} \\ f^{(\ell-1)}, & otherwise. \end{cases}$$

(3.2)

$$s^{(\ell)} = \begin{cases} |q_{ik_i(\ell)}|, f^{(\ell-1)} < |q_{ik_i(\ell)}| < s^{(\ell-1)} \\ f^{(\ell-1)}, |q_{ik_i(\ell)}| \le f^{(\ell-1)} \\ s^{(\ell-1)}, & otherwise. \end{cases}$$

(3.3)

Thus,  $f^{(\ell_{max})}$  and  $s^{(\ell_{max})}$  are the first and second minimum values for the set of VN neighbors of CN *i*, where,  $\ell_{max} = |\mathcal{N}(i)|$ .

2. Local Pass: Let the minimum value as per equation (2.3) for VN  $k_i(\ell)$  be denoted as  $q_{ik_i(\ell)}^{min}$ ,  $\ell \in \{1, 2, \dots, |\mathcal{N}(i)|\}$  then,

$$q_{ik_i(\ell)}^{min} = \begin{cases} f^{(\ell_{max})}, & |q_{ik_i(\ell)}| \neq f^{(\ell_{max})} \\ s^{(\ell_{max})}, & otherwise. \end{cases}$$

(3.4)

In software, this translates to two consecutive for-loops, each executing  $(d_{c_i} - 1)$  times. This is shown in Fig. 3.1 (b). Consequently, this reduces the complexity from  $\mathcal{O}(d_{c_i}^2)$  to  $\mathcal{O}(d_{c_i})$ . A similar approach is also found in [25], [8]. The sign computation is processed in a similar manner. The CN message computation given by equation (2.3) is repeated *m* times in a decoding iteration i.e. once for each CN. A straightforward serial implementation of this kind is slow and undesirable. Instead, we apply a strategy based on the following understanding.

Fact 1. An arbitrary submatrix  $\mathbf{I}_s$  in the PCM  $\mathbf{H}$  corresponds to z CNs connected to z VNs on the bipartite graph, with strictly 1 edge between each CN and VN.

This implies that no CN in this set of z CNs given by  $\mathbf{I}_s$  shares a VN with another CN in the same set. Table 3.1 illustrates such an arbitrary submatrix in  $\mathbf{H}$ . This presents us with an opportunity to operate z NPUs in parallel (hereafter referred to as an *NPU array*), resulting in a z-fold increase in throughput.

#### 3.3 Layered Decoding

In Section 3.2 we saw that z CNs (and hence VNs) computations can be done in parallel by virtue of the circulant-1 identity matrix based structure of the CN-VN connections. A straightforward way of improving throughput by multiple folds is to process more than z CTV (and hence VTC) message updates i.e. to extend the parallelism beyond the boundary of a submatrix of size z. A greedy approach to maximize throughput in this manner is to process all the m CTV updates at once. This is the classical *fully parallel* implementation which in principle is a manifestation of the flooding schedule (see Remark 1) where *all* nodes on one side of the bipartite graph can be processed in parallel. Although, such a *fully parallel* implementation may seem as an attractive option for achieving high-throughput performance, it has the following drawbacks.

- 1. Firstly, it becomes quickly intractable in hardware due to the complex interconnect pattern.

- 2. Secondly, such an implementation caters to the graph of a particular code in a code ensemble. In other words, the routing interconnect determined by the code is frozen in hardware.

Nevertheless, there is still scope to achieve a degree of parallelism greater than z without sacrificing the flexibility of the implementation. This can be accomplished if the following condition is satisfied by the processing schedule.

Fact 2. From the perspective of CN processing, two or more CNs can be processed at the same time (i.e. they are independent of each other) if they do not have one or more VNs (code bits) in common.

This is central to the row-layering [23] technique used in this work. To understand this in detail let us define the following.

In terms of **H**, an arbitrary subset of rows can be processed at the same time provided that, no two or more rows have a 1 in the same column of **H**. This subset of rows is termed as a *row-layer* (hereafter referred to as a *layer*). In other words, given a set  $\mathcal{L} = \{L_1, L_2, \ldots, L_I\}$  of I layers in **H**,  $\forall u \in \{1, 2, \ldots, I\}$  and  $\forall i, i' \in L_u$ , then,  $\mathcal{N}(i) \cap \mathcal{N}(i') = \phi$ .

Observing that,  $\sum_{u=1}^{I} |L_u| = m$ , in general,  $L_u$  can be any subset of rows as long as the rows within each subset satisfy the condition in Fact 2; implying that,  $|L_u| \neq |L_{u'}|$ ,  $\forall u, u' \in \{1, 2, \ldots, I\}$  is possible. It is not hard to see that, this is more so true in the case of unstructured or random codes. In fact, if  $|L_u| \neq |L_{u'}|$  the hardware complexity increases since the processing effort changes from one layer to another. For instance, the memory allocation for each layer could be different, resulting in dynamic memoryaddress generation patterns.

Owing to the structure of QC-LDPC codes, the choice of  $|L_u|$  (and hence I) becomes much obvious. Submatrices  $\mathbf{I}_s$  in  $\mathbf{H}_b$  (with row and column weight of 1) guarantee that, for the z CNs corresponding to the rows of  $\mathbf{I}_s$ ), always satisfy the condition in Fact 2. Thus, keeping in mind the ease of implementation,  $|L_u| = |L_{u'}| = z$  is the most obvious choice.

From the VN or column perspective,  $|L_u| = z$ ,  $\forall u = \{1, 2, ..., I\}$  implies that, the columns of **H** are also divided into subsets of size z (hereafter referred to as *block columns*) given by the set  $\mathcal{B} = \{B_1, B_2, ..., B_J\}$ ,  $J = \frac{n}{z} = n_b$ . Observing that VNs belonging to a block column may participate in CN equations across several layers,

| Layers    | $\mathbf{s}\downarrow$ |              | $\operatorname{Blocks} \longrightarrow$ |                |  |  |  |  |  |  |

|-----------|------------------------|--------------|-----------------------------------------|----------------|--|--|--|--|--|--|

|           |                        | $B_2$        | $B_3$                                   | $\mathbf{B_4}$ |  |  |  |  |  |  |

| $L_1$     |                        | $\downarrow$ | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| $L_2$     |                        | $\downarrow$ | 28                                      | $\downarrow$   |  |  |  |  |  |  |

| $L_3$     | •••                    | $\downarrow$ | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| ${f L}_4$ |                        | 53           | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| $L_5$     |                        | $\downarrow$ | $\downarrow$                            | 20             |  |  |  |  |  |  |

| $L_6$     |                        | $\downarrow$ | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| $L_7$     |                        | 79           | 79                                      | $\downarrow$   |  |  |  |  |  |  |

| $L_8$     |                        | $\downarrow$ | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| $L_9$     | •••                    | $\downarrow$ | $\downarrow$                            | $\downarrow$   |  |  |  |  |  |  |

| $L_{10}$  |                        | 45           | $\downarrow$                            | 70             |  |  |  |  |  |  |

| $L_{11}$  |                        | 56           | $\downarrow$                            | 57             |  |  |  |  |  |  |

| $L_{12}$  |                        | $\downarrow$ | 61                                      | $\downarrow$   |  |  |  |  |  |  |

|           |                        | to $L_4$     | to $L_2$                                | to $L_5$       |  |  |  |  |  |  |

|           |                        |              |                                         |                |  |  |  |  |  |  |

Table 3.2: Illustration of Message Passing in row-layered decoding in a Section of the PCM  $\mathbf{H}_b$ .

we further divide the block columns into *blocks*, where a block is the intersection of a layer and a block column. One may visualize a block in the decoder architecture as a submatrix in  $\mathbf{H}_b$ , owing to the equivalence between the two. Two or more layers  $L_u, L_{u'}$ are said to be *dependent* with respect to the block column  $B_w$  if,  $\mathbf{H}_b(u, w) \neq -1$  and,  $\mathbf{H}_b(u', w) \neq -1$  and are said to be *independent* otherwise.

For example, in Table 3.2 we can see that layers  $L_4, L_7, L_{10}$  and  $L_{11}$  are dependent with respect to block column  $B_2$ . Assuming that the message update begins with layer  $L_1$  and proceeds downward, the arrows represent the directional flow of message updates from one layer to another. Thus, layer  $L_7$  cannot begin updating the VNs associated with block column  $B_2$  before layer  $L_4$  has finished updating messages for the same set of VNs and so on. It is worthwhile to reiterate that the idea of parallelizing z NPUs seen in Section 3.2 can be extended to layers, NPU arrays can process message updates for multiple independent layers. It is clear that, dependent layers limit the degree of parallelization available to achieve high-throughput. In Chapter 4, we discuss

| Layers     | $\downarrow$   | $\mathbf{Blocks} \longrightarrow$ |                |                |                |                |                |                |  |  |  |  |

|------------|----------------|-----------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|--|--|--|--|

|            | $\mathbf{b_1}$ | $\mathbf{b_2}$                    | $\mathbf{b_3}$ | $\mathbf{b_4}$ | $\mathbf{b_5}$ | $\mathbf{b_6}$ | $\mathbf{b_7}$ | $\mathbf{b_8}$ |  |  |  |  |

| $L_1$      | 0              | 4                                 | 6              | 8              | 10             | 12             | 13             | -1             |  |  |  |  |

| $L_2$      | 0              | 2                                 | 4              | 8              | 9              | 13             | 14             | -1             |  |  |  |  |

| $L_3$      | 0              | 4                                 | 5              | 8              | 9              | 14             | 15             | -1             |  |  |  |  |

| ${ m L}_4$ | 0              | 1                                 | 4              | 7              | 8              | 15             | 16             | -1             |  |  |  |  |

| $L_5$      | 0              | 3                                 | 4              | 7              | 8              | 16             | 17             | -1             |  |  |  |  |

| ${ m L}_6$ | 0              | 4                                 | 6              | 8              | 11             | 17             | 18             | -1             |  |  |  |  |

| $L_7$      | 0              | 1                                 | 2              | 6              | 8              | 12             | 18             | 19             |  |  |  |  |

| $L_8$      | 0              | 4                                 | 5              | 8              | 10             | 19             | 20             | -1             |  |  |  |  |

| $L_9$      | 0              | 4                                 | 5              | 8              | 11             | 20             | 21             | -1             |  |  |  |  |

| $L_{10}$   | 1              | 3                                 | 4              | 8              | 9              | 21             | 22             | -1             |  |  |  |  |