© 2016 Binh Quang Pham ALL RIGHTS RESERVED

## ARCHITECTURAL SUPPORT FOR EFFICIENT VIRTUAL MEMORY ON BIG-MEMORY SYSTEMS.

BY BINH QUANG PHAM

A dissertation submitted to the Graduate School—New Brunswick Rutgers, The State University of New Jersey in partial fulfillment of the requirements for the degree of Doctor of Philosophy Graduate Program in Computer Science Written under the direction of Abhishek Bhattacharjee and approved by

> New Brunswick, New Jersey January, 2016

### ABSTRACT OF THE DISSERTATION

## Architectural Support for Efficient Virtual Memory on Big-Memory Systems.

## by Binh Quang Pham Dissertation Director: Abhishek Bhattacharjee

Virtual memory is a powerful and ubiquitous abstraction for managing memory. However, virtual memory suffers a performance penalty for these benefits, namely when translating program virtual addresses to system physical addresses. This overhead had been limited to 5-15% of system runtime by using a set of sophisticated hardware solutions, but has increased to 20-50% for many scenarios, including running workloads with large memory footprints and poor access locality or using deeper software stacks.

My thesis aims to solve this problem so that the memory systems can continue to scale without being hamstrung by the virtual memory system. We observe that while operating systems (OS) and hypervisors have a rich set of components in allocating memory, the hardware address translation unit only maintains a rigid and limited view of this ecosystem. Therefore, we seek for patterns inherently present in the memory allocation mechanisms to guide us in designing a more intelligent address translation unit.

First, we realize that OS memory allocators and program faulting sequence tend to produce contiguous or nearby mappings between virtual and physical pages. We propose Coalesced TLB and Clustered TLB designs to exploit these patterns accordingly. Once detected, the related mappings are stored in a single TLB entry to increase the TLB reach. Our designs help reduce TLB misses substantially and improve performance as a result.

Second, we see that there are often tradeoffs between reducing address translation overheard and improving resource consolidation in virtualized environments. For example, large pages are often used to mitigate the high cost of two-dimensional page walks, but hypervisors usually break large pages into small pages for easier sharing guests memory. When that happens, the majority of those small pages still remain aligned. Based on this observation, we propose a speculative TLB technique to regain almost all performance loss caused by breaking large pages while running highly consolidated virtualized systems.

## Acknowledgements

Seven years ago, I was very happy when I received an admission letter to pursue a PhD degree in the US. Fresh out of college, I had little idea of what my research area would be and what doing a PhD entailed. Looking back, I find that doing a PhD is one of the most challenging yet rewarding experience of my life. As I am coming to the end of my PhD journey, I would like to take a moment and acknowledge the many people that I am thankful for in my life.

First and foremost, I wish to thank my advisor, Dr. Abhishek Bhattacharjee for his guidance in developing this thesis. I am grateful to him for teaching me how to do research, from formulating ideas, conducting experiments, to presenting the final results. We have had many discussions in the last few years working together – I always came out with a clear idea of what to do next and felt strongly motivated to go to the end of the road after each and every discussion.

I owe a very special thank you to my parents for their unconditional love and encouragement throughout my life. To my sisters, Thuy and Ha, my brother-in-laws Kien, Hieu, my nephews and niece for their love and support. To Hue for always being there for me and sharing the ups and downs of a PhD student's life. Whenever I feel tired, thinking of them gives me strength to continue and try.

I also wish to thank:

- Dr. Gabriel H. Loh for being a great mentor and collaborator during and after my internship at AMD. I am fortunate enough to work with him on a major part of my thesis, and I learn a great deal from him, whether it is understanding technical concepts, generating ideas, or getting work done in the most efficient way

- Dr. Thu Nguyen, Dr. Ricardo Bianchini, and Dr. Martha Kim for serving as my committee members and their valuable feedback while I am working on this

${\rm thesis}$

- Dr. Yasuko Eckert and Dr. Trey Cain for being amazing mentors during my internships at AMD and Qualcomm. These internship experiences help me better understand how research ideas can and should be applied to the outside world

- Members and former members of the RUARCH Lab for helping me complete the projects that lead to this thesis, for attending endless practice talks and proofreading my paper submissions as well as this thesis

- Department of Computer Science at Rutgers University for being my second home in the US.

# Dedication

To my family.

## Table of Contents

| Abstra  | ict          |                                                            | ii   |

|---------|--------------|------------------------------------------------------------|------|

| Ackno   | wledge       | ements                                                     | iv   |

| Dedica  | tion .       |                                                            | vi   |

| List of | <b>Table</b> | <b>s</b>                                                   | xii  |

| List of | Figur        | es                                                         | ciii |

| 1. Intr | roducti      | $\mathbf{ion}$                                             | 1    |

| 1.1.    | Motiva       | ation                                                      | 1    |

| 1.2.    | Our g        | oal                                                        | 4    |

| 1.3.    | Profili      | ing Address Translation Overhead                           | 4    |

| 1.4.    | Disser       | tation Structure                                           | 6    |

| 1.5.    | Contri       | ibutions                                                   | 7    |

| 2. Exp  | oloiting     | g Sequential Locality in Page Translations for Large Reach |      |

| TLBs    |              |                                                            | 9    |

| 2.1.    | Introd       | luction                                                    | 9    |

| 2.2.    | Backg        | round and Related Work                                     | 10   |

|         | 2.2.1.       | Prior TLB Enhancement Techniques                           | 10   |

|         | 2.2.2.       | Superpaging Benefits and Problems                          | 11   |

|         | 2.2.3.       | TLB Subblocking and Speculation                            | 12   |

|         | 2.2.4.       | Our Approach                                               | 14   |

| 2.3.    | Under        | standing Page Allocation Contiguity                        | 15   |

|         | 2.3.1.       |                                                            | 15   |

|         | 2.3.2.       |                                                            | 15   |

|      |        | 2.3.2.1.  | Process address space                                         | 16 |

|------|--------|-----------|---------------------------------------------------------------|----|

|      |        | 2.3.2.2.  | Buddy allocation.                                             | 17 |

|      |        | 2.3.2.3.  | Memory compaction.                                            | 18 |

|      |        | 2.3.2.4.  | Transparent hugepage support                                  | 19 |

|      |        | 2.3.2.5.  | Putting Things Together                                       | 20 |

|      |        | 2.3.2.6.  | System Load and Memory Fragmentation                          | 21 |

| 2.4. | CoLT   | Design a  | nd Implementation                                             | 21 |

|      | 2.4.1. | CoLT-S.   | A Design and Implementation                                   | 22 |

|      |        | 2.4.1.1.  | Overall operation                                             | 22 |

|      |        | 2.4.1.2.  | TLB set selection                                             | 23 |

|      |        | 2.4.1.3.  | Lookup operation                                              | 24 |

|      |        | 2.4.1.4.  | Practical coalescing restrictions.                            | 24 |

|      |        | 2.4.1.5.  | Replacement, invalidations, and attribute changes             | 25 |

|      | 2.4.2. | CoLT-F.   | A Design and Implementation                                   | 25 |

|      |        | 2.4.2.1.  | Overall operation.                                            | 26 |

|      |        | 2.4.2.2.  | Lookup operation                                              | 27 |

|      |        | 2.4.2.3.  | Replacement, invalidations, and attribute changes             | 28 |

|      | 2.4.3. | CoLT-A    | ll Design and Implementation                                  | 28 |

|      |        | 2.4.3.1.  | Overall operation                                             | 28 |

|      |        | 2.4.3.2.  | Lookup operation                                              | 29 |

|      |        | 2.4.3.3.  | Replacement, invalidation, and attribute changes. $\ . \ .$ . | 29 |

| 2.5. | Metho  | odology   |                                                               | 30 |

|      | 2.5.1. | Real-Sys  | stem Characterizations of Page Allocation Contiguity          | 30 |

|      |        | 2.5.1.1.  | Experimental platform and methodology                         | 30 |

|      |        | 2.5.1.2.  | Evaluation workloads                                          | 31 |

|      | 2.5.2. | Simulati  | ion-Based CoLT Evaluations                                    | 32 |

|      |        | 2.5.2.1.  | Simulated system                                              | 32 |

|      |        | 2.5.2.2.  | Evaluation workloads                                          | 34 |

| 2.6. | Real-S | System Cl | naracterizations of Page Allocation Contiguity                | 34 |

|        | 2.6.1.   | Superpaging, Memory Compaction                                                                               | 4 |

|--------|----------|--------------------------------------------------------------------------------------------------------------|---|

|        | 2.6.2.   | No Superpaging, Memory Compaction                                                                            | 5 |

|        |          | 2.6.2.1. No Superaging, Low Memory Compaction                                                                | 6 |

|        | 2.6.3.   | Superpaging, Memory Compaction, Memhog                                                                       | 6 |

|        | 2.6.4.   | No Superpaging, Memory Compaction, Memhog                                                                    | 8 |

|        | 2.6.5.   | Summary of results                                                                                           | 8 |

| 2.7.   | CoLT     | Evaluations                                                                                                  | 9 |

|        | 2.7.1.   | TLB Miss Rate Analysis                                                                                       | 9 |

|        |          | 2.7.1.1. CoLT TLB miss rates                                                                                 | 9 |

|        |          | 2.7.1.2. Impact of CoLT-SA's indexing scheme on TLB miss rates. 4                                            | 1 |

|        |          | 2.7.1.3. Impact of bringing missing entries into L2 TLB for CoLT-                                            |   |

|        |          | FA and CoLT-All                                                                                              | 2 |

|        |          | 2.7.1.4. Studying CoLT's effectiveness at higher associativities. 4                                          | 4 |

|        | 2.7.2.   | Performance Analysis                                                                                         | 5 |

| 2.8.   | Summ     | ary 4                                                                                                        | 6 |

| 3. Exp | oloiting | Clustered Locality in Page Translations for Large Reach                                                      |   |

| TLBs   |          |                                                                                                              | 8 |

| 3.1.   | Introd   | uction $\ldots \ldots 4$ | 8 |

| 3.2.   | Relate   | d Work and Our Approach                                                                                      | 9 |

|        | 3.2.1.   | Spatial Locality in Page Table Entries                                                                       | 9 |

|        | 3.2.2.   | Other Techniques to Exploit Page Table Spatial Locality 5                                                    | 0 |

|        | 3.2.3.   | Our Approach: Clustered TLBs                                                                                 | 1 |

| 3.3.   | Weak     | Spatial Locality in Page Tables                                                                              | 3 |

|        | 3.3.1.   | CoLT-like Contiguous Spatial Locality                                                                        | 3 |

|        | 3.3.2.   | Clustered Spatial Locality                                                                                   | 4 |

|        | 3.3.3.   | Impact of Memory System Fragmentation                                                                        | 6 |

| 3.4.   | The M    | ulti-granular TLB                                                                                            | 6 |

|        |          | 0                                                                                                            |   |

|    |      | 3.4.2.  | Multi-granular TLB Organization and Operation                                     | 0 |

|----|------|---------|-----------------------------------------------------------------------------------|---|

|    |      | 3.4.3.  | Frequent Value Locality in the Address Bits                                       | 1 |

|    |      | 3.4.4.  | Hardware Cost                                                                     | 5 |

|    |      |         | 3.4.4.1. Basic Multi-granular TLB Hardware Cost                                   | 5 |

|    |      |         | 3.4.4.2. Enhanced Multi-granular TLB Hardware Cost 6'                             | 7 |

|    | 3.5. | Experi  | imental Methodology                                                               | 8 |

|    |      | 3.5.1.  | Workloads                                                                         | 8 |

|    |      | 3.5.2.  | Simulation Infrastructure                                                         | 9 |

|    |      |         | 3.5.2.1. Functional Simulator                                                     | 9 |

|    |      |         | 3.5.2.2. Performance Evaluation                                                   | 9 |

|    | 3.6. | Multi-  | granular TLB Evaluations                                                          | 0 |

|    |      | 3.6.1.  | Understanding Changes in Hit Rates                                                | 0 |

|    |      | 3.6.2.  | Overall Performance Improvements                                                  | 1 |

|    |      | 3.6.3.  | Prefetching versus Capacity Improvements                                          | 2 |

|    | 3.7. | Sensiti | vity Studies                                                                      | 3 |

|    | 3.8. | Summ    | ary                                                                               | 6 |

| 4. | Sup  | portin  | g Large, Yet Agile Pages in Virtualized Systems                                   | 8 |

|    | _    | -       | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ |   |

|    |      |         | round                                                                             |   |

|    |      | _       | ation and Our Approach                                                            |   |

|    | 4.4. |         | s of Page Splintering                                                             |   |

|    | 4.5. |         | Microarchitecture                                                                 |   |

|    |      | 4.5.1.  | TLB Organization                                                                  |   |

|    |      | 4.5.2.  | Speculative TLB Entries                                                           |   |

|    |      | 4.5.3.  | TLB Operations                                                                    |   |

|    |      | 4.5.4.  | Speculation Details                                                               |   |

|    |      | 4.5.5.  | Mitigating Verification Costs                                                     |   |

|    |      | 4.5.6.  | Mitigating Mis-speculation Overheads                                              |   |

|    |      |         |                                                                                   |   |

|    | 4.6.  | Experi  | imental Methodology                        |

|----|-------|---------|--------------------------------------------|

|    |       | 4.6.1.  | Workloads                                  |

|    |       | 4.6.2.  | Trace Collection                           |

|    |       | 4.6.3.  | Functional simulator                       |

|    |       | 4.6.4.  | Analytical Performance Model               |

|    | 4.7.  | Experi  | imental Results                            |

|    |       | 4.7.1.  | GLUE Performance Results: Single VM 100    |

|    |       | 4.7.2.  | GLUE Performance Results: Multiple VMs 103 |

|    |       | 4.7.3.  | Characterizing Page Splintering Sources    |

|    |       | 4.7.4.  | Importance of GLUE in Future Systems       |

|    |       | 4.7.5.  | Understanding GLUE's Limitations           |

|    | 4.8.  | Relate  | d Work                                     |

|    | 4.9.  | Summ    | ary                                        |

| -  | C     | -1      | -                                          |

| 5. | Con   | ciusioi | n                                          |

| Re | efere | nces .  |                                            |

# List of Tables

| 3.1. | Comparison of Hardware Cost               | 66 |

|------|-------------------------------------------|----|

| 3.2. | Enhanced MG-TLB Hardware Cost             | 67 |

| 3.3. | Summary of benchmarks used in our studies | 69 |

# List of Figures

| 1.1.      | Ratio between last level cache capacity and last level TLB reach                    | 3               |

|-----------|-------------------------------------------------------------------------------------|-----------------|

| 1.2.      | (a) Fraction of runtime spent on page table walks; (b) Fraction of runtime          |                 |

|           | spent on looking in the second level TLB and page table walks for $4$ KB            |                 |

|           | pagesize                                                                            | 5               |

| 1.3.      | (a) Fraction of runtime spent on page table walks; (b) Fraction of runtime          |                 |

|           | spent on looking in the second level TLB and page table walks for 2MB               |                 |

|           | pagesize                                                                            | 6               |

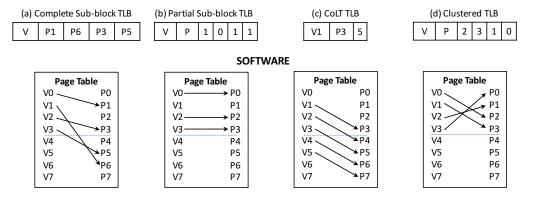

| 2.1.      | Operation of complete sub-blocking and partial sub-blocking versus CoLT             |                 |

|           | TLB. For each approach, we show the structure of a single entry and a               |                 |

|           | page table with the PTEs that can be exploited. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 12              |

| 2.2.      | Virtual memory areas in process address space                                       | 16              |

| 2.3.      | (a) Buddy allocator used for physical page allocation. Already allocated            |                 |

|           | pages are shaded, while free pages are tracked by the free lists. (b) Buddy         |                 |

|           | allocator state after an allocation for 2 pages is finished                         | 17              |

| 2.4.      | The memory compaction daemon tracks movable and free memory pages,                  |                 |

|           | exchanging them to eliminate fragmentation.                                         | 18              |

| 2.5.      | Interaction between program's fault order and memory management                     | 20              |

| 2.6.      | CoLT for set-associative L1 and L2 TLBs                                             | 22              |

| 2.7.      | CoLT for the fully-associative superpage TLB                                        | 26              |

| 2.8.      | Combined CoLT for all TLBs                                                          | 28              |

| 2.9. 2.10 | Summary of benchmarks used in our studies                                           | $\frac{31}{34}$ |

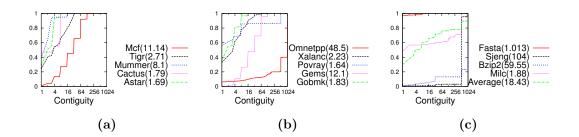

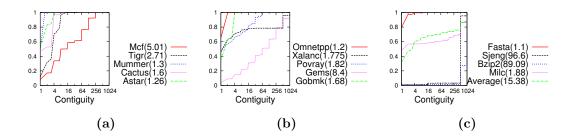

| 2.11      | . THS off, normal memory compaction contiguity CDF                                  | 35              |

| 2.12      | . THS off, low memory compaction contiguity CDF                                     | 36              |

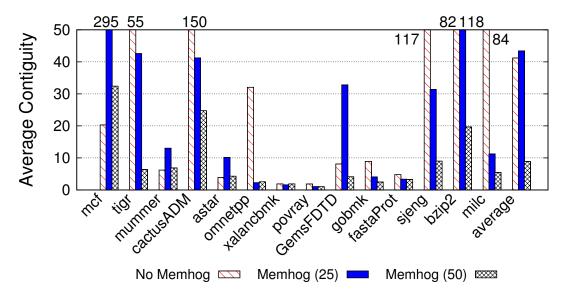

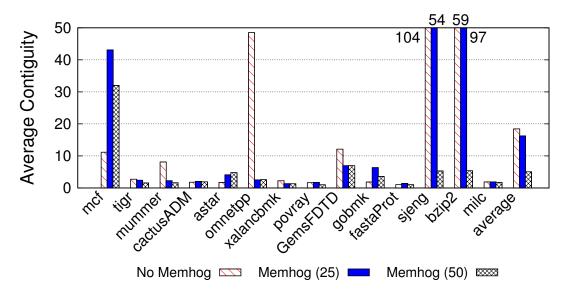

| 2.13. | Average contiguity for THS on, normal memory compaction with varying         |

|-------|------------------------------------------------------------------------------|

|       | Memhog                                                                       |

| 2.14. | Average contiguity for THS off, normal memory compaction with varying        |

|       | Memhog.                                                                      |

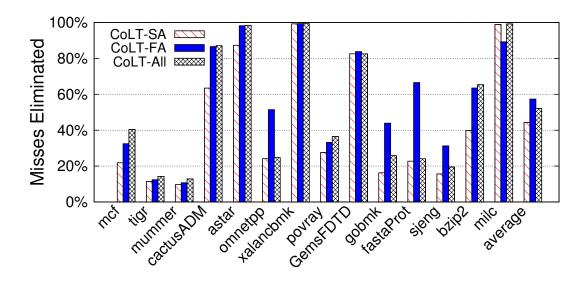

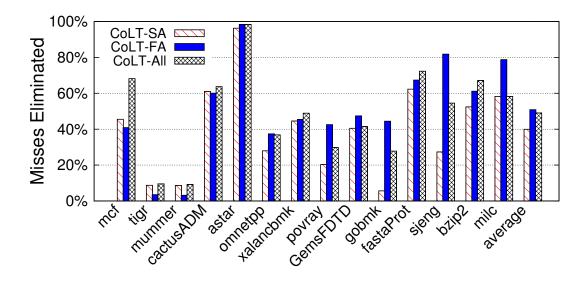

| 2.15. | Percentage of L1 TLB misses eliminated using CoLT-SA, CoLT-FA, and           |

|       | CoLT-All normalized to baseline TLB misses                                   |

| 2.16. | Percentage of L2 TLB misses eliminated using CoLT-SA, CoLT-FA, and           |

|       | CoLT-All normalized to baseline TLB misses                                   |

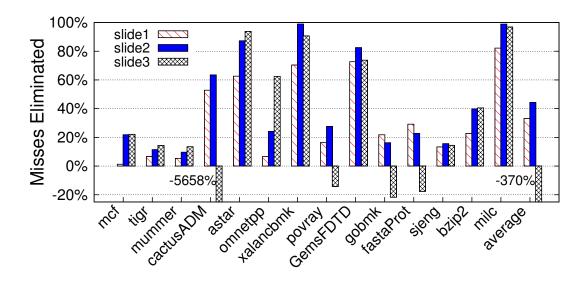

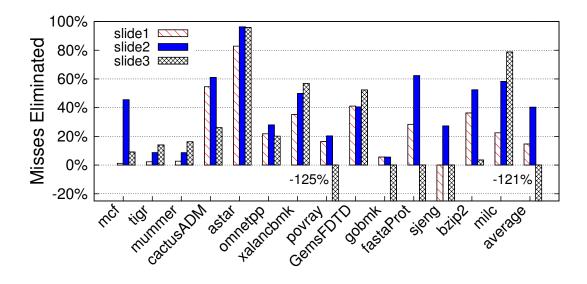

| 2.17. | Effect of left-shifting index on L1 misses                                   |

| 2.18. | Effect of left-shifting index on L2 misses                                   |

| 2.19. | Percentage of baseline misses eliminated by CoLT-SA when increasing          |

|       | associativity.                                                               |

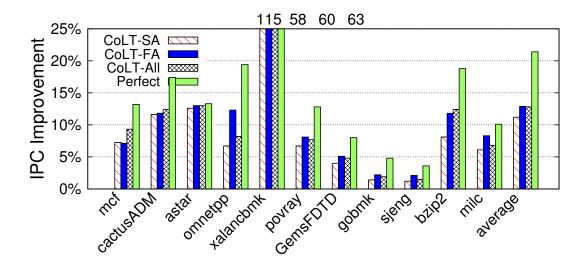

| 2.20. | CoLT-SA, CoLT-FA, and CoLT-All performance improvements compared             |

|       | to perfect TLBs with 100% hit rates                                          |

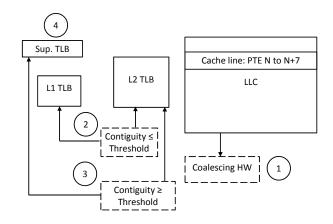

| 3.1.  | The figure on the left shows the presence of contiguous spatial locality     |

|       | (sequential groups) in a page table. The figure on the right shows that      |

|       | if clustered locality is also observed, the entire page table can be more    |

|       | efficiently covered.                                                         |

| 3.2.  | Operation complete sub-blocking, partial sub-blocking, and CoLT versus       |

|       | clustered TLB. For each approach, we show the structure of a single entry    |

|       | and a page table with the PTEs that can be exploited                         |

| 3.3.  | Interactions between program faults order and kernel's memory manage-        |

|       | ment                                                                         |

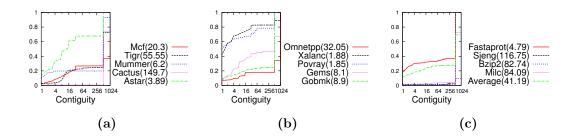

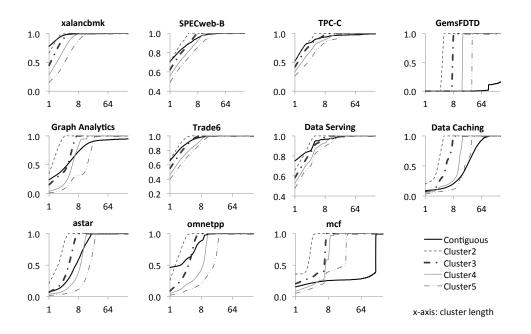

| 3.4.  | Cumulative distribution functions comparing the opportunity of CoLT-         |

|       | style contiguous spatial locality versus the clustered spatial locality that |

|       | we target. In general, clustered spatial locality covers a bigger portion    |

|       | of the page table than contiguous spatial locality                           |

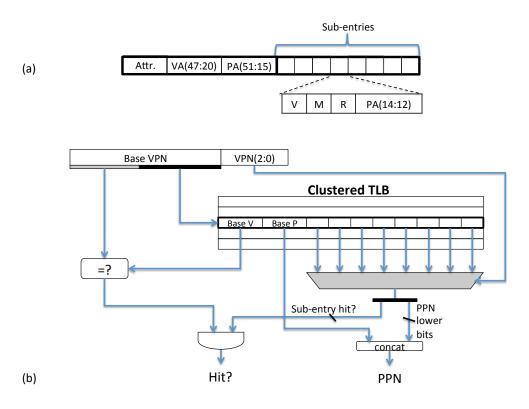

| 3.5.  | (a) Clustered TLB entry format, (b) Look-up operation                        |

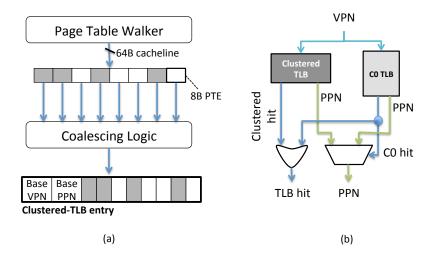

| 3.6. (a) Coalescing is performed on TLB fill, (b) Multi-granular TLB consists                |    |

|----------------------------------------------------------------------------------------------|----|

| of a clustered TLB and a small conventional TLB                                              | 59 |

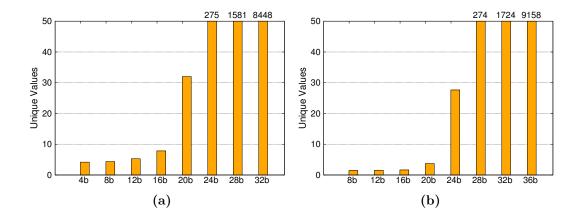

| 3.7. The number of unique values when only considering the $x$ upper-most                    |    |

| bits for the VPN (a) and PPN (b), as $x$ is varied. The upper 16 VPN                         |    |

| bits and 20 PPN bits change rarely in our experiments                                        | 62 |

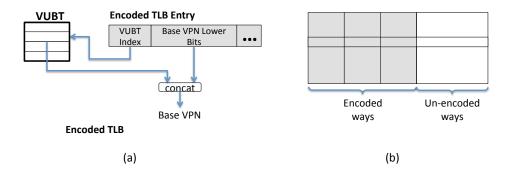

| 3.8. (a) Hardware organization for the Virtual Upper Bits Table (VUBT) and                   |    |

| an encoded TLB entry, and (b) a four-way TLB with three encoded ways                         |    |

| and one un-encoded way                                                                       | 63 |

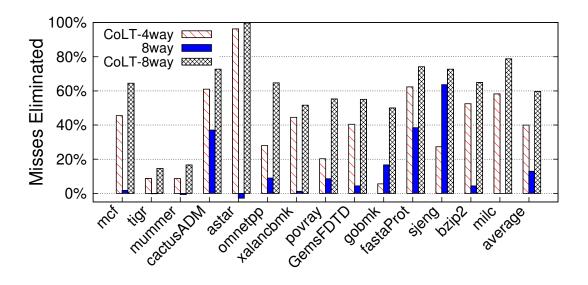

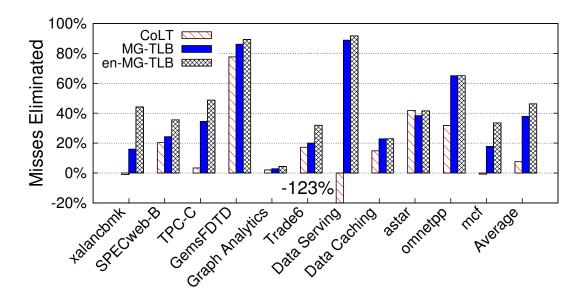

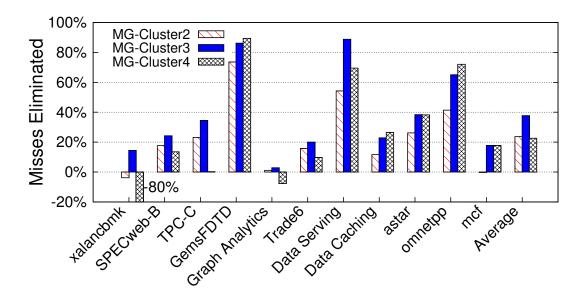

| $3.9.\ {\rm L2}\ {\rm TLB}\ {\rm misses}$ eliminated by the baseline multi-granular TLB (MG- |    |

| TLB), enhanced MG-TLBs with structures to exploit redundant most                             |    |

| significant VPN and PPN bits (en-MG-TLB) and CoLT. MG-TLB and                                |    |

| en-MG-TLB comprehensively eliminate more misses than CoLT. $\ . \ . \ .$                     | 70 |

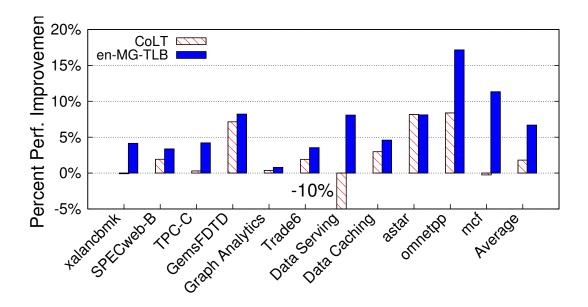

| 3.10. Performance improvements when using CoLT and en-MG-TLB. Our ap-                        |    |

| proach outperforms CoLT in every single case                                                 | 72 |

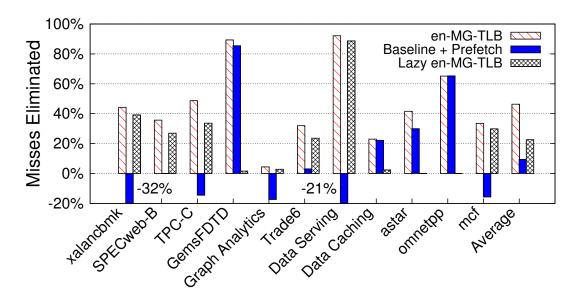

| 3.11. Separating the prefetch and capacity benefits of MG-TLBs                               | 73 |

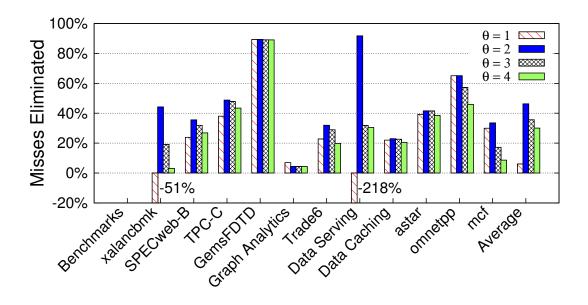

| 3.12. TLB miss-elimination rates assuming that the clustered TLB is C2, C3 $$                |    |

| (our default assumption so far), and C4 $\ldots$                                             | 74 |

| 3.13. TLB miss-elimination rates for en-MG-TLB as the cluster threshold is                   |    |

| changed for insertion into the clustered TLB                                                 | 75 |

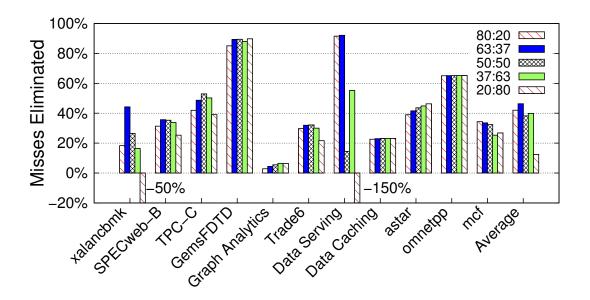

| 3.14. TLB miss eliminations for different relative sizes of the small singleton              |    |

| PTE's TLB and the clustered TLB in MG-TLB. The legend shows the                              |    |

| ratio of the MG-TLB area for the small conventional TLB to the area                          |    |

| for the clustered TLB                                                                        | 76 |

| 4.1. Percent of execution time for address translation, for applications on a                |    |

| Linux VM on VMware's ESX server, running on an x86-64 architecture.                          |    |

| Overheads are $18\%$ on average despite the fact that the OS uses both                       |    |

| 4KB and 2MB pages                                                                            | 81 |

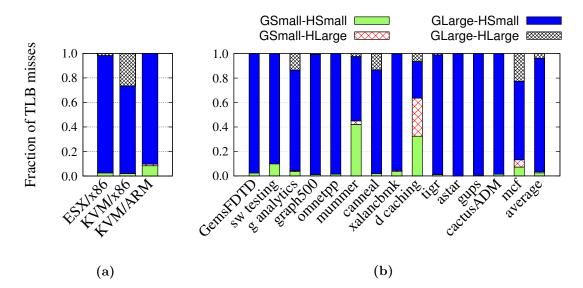

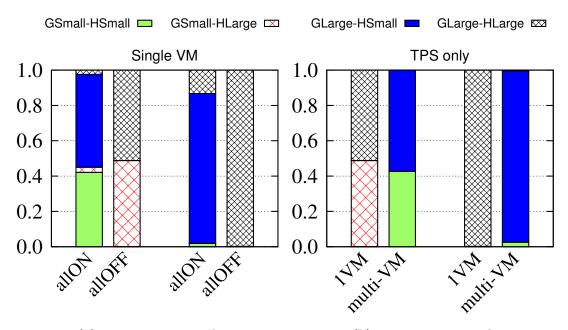

| 4.2. | Fraction of TLB misses serviced from SPPs backed by a small page in        |     |

|------|----------------------------------------------------------------------------|-----|

|      | guest and hypervisor (GSmall-HSmall), small in guest and large in hyper-   |     |

|      | visor (GSmall-HLarge), large in guest and small in hypervisor (GLarge-     |     |

|      | HSmall), and large in both (GLarge-HLarge).                                | 82  |

| 4.3. | Guest large page GVP4-7 is splintered, but SPPs are conducive to inter-    |     |

|      | polation. A speculative TLB maps the page table in two entries (using a    |     |

|      | speculative entry for GVP4-7) instead of four entries (like a conventional |     |

|      | TLB)                                                                       | 84  |

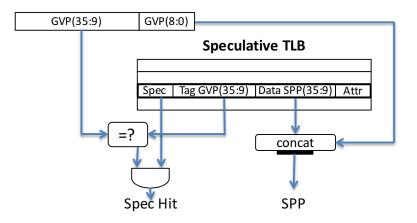

| 4.4. | Lookup operation on a speculated TLB entry. A tag match is performed       |     |

|      | on the bits corresponding to its 2MB frame. On a hit, the 2MB frame        |     |

|      | in system physical memory is concatenated with the 4KB offset within it.   | 90  |

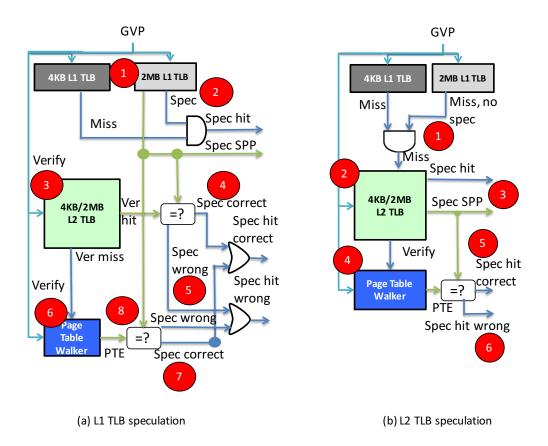

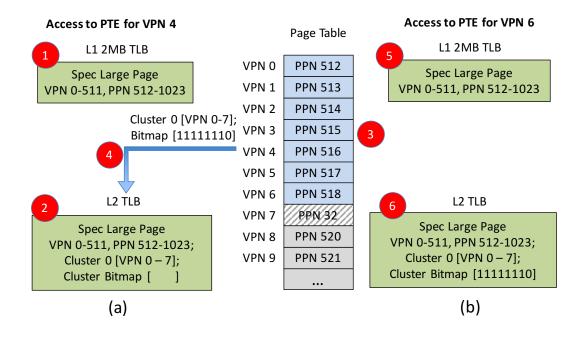

| 4.5. | The mechanics of TLB speculation. We show the case when (a) we             |     |

|      | speculate from the 2MB L1 TLB, and (b) we speculate from the L2 TLB.       | 91  |

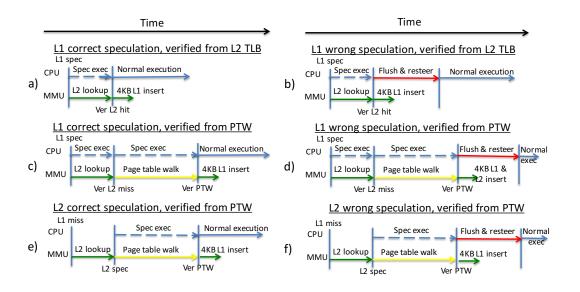

| 4.6. | Timelines for (a) speculating from the 2MB L1 TLB correctly, and ver-      |     |

|      | ifying this in the L2 TLB; (b) mis-speculating from the 2MB L1 TLB,        |     |

|      | and verifying this in the L2 TLB; (c) speculating from the 2MB L1 TLB $$   |     |

|      | correctly, and verifying with a page table walk; (d) mis-speculating from  |     |

|      | the 2MB L1 TLB, and verifying with a page table walk; (e) speculating      |     |

|      | from the L2 TLB correctly, and verifying with a page table walk; and $(f)$ |     |

|      | mis-speculating from the L2 TLB, and verifying with a page table walk.     | 92  |

| 4.7. | Storing clusters of bits (in otherwise wasted L2 TLB entry bits) to elim-  |     |

|      | inate the need for verification-induced page table walks                   | 96  |

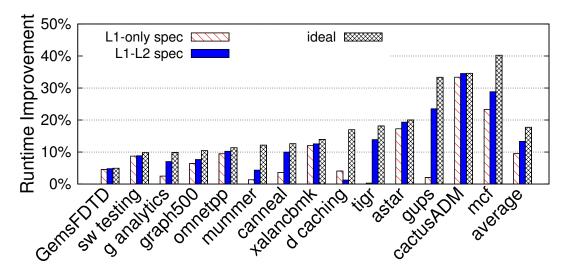

| 4.8. | Performance benefits of L1-only, L1-L2 speculation, compared to the        |     |

|      | ideal case without TLB miss overheads. Performance is normalized to        |     |

|      | the baseline single-VM.                                                    | 100 |

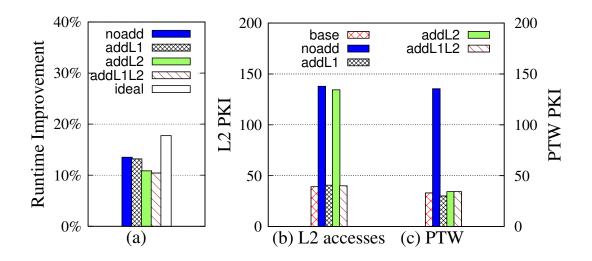

| 4.9.  | Average (a) performance improvements when inserting the non-speculative $% \left( {{{\bf{n}}_{\rm{s}}}} \right)$ |     |

|-------|------------------------------------------------------------------------------------------------------------------|-----|

|       | 4KB PTE, after correct speculation, in neither TLB (noAdd), the L1                                               |     |

|       | TLB (addL1), the L2 TLB (addL2), or both (addL1L2), compared with                                                |     |

|       | the ideal improvement; (b) number of L2 TLB accesses per kilo-instruction                                        |     |

|       | (APKI) including verification compared to a baseline with speculation;                                           |     |

|       | and (c) number of page table walks per kilo-instruction                                                          | 101 |

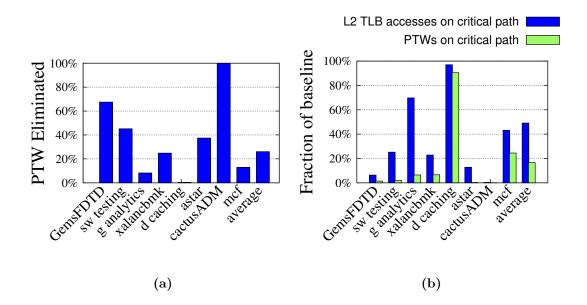

| 4.10. | (a) Fraction of page table walks eliminated using clustered bitmaps in                                           |     |

|       | speculative L2 TLB entries; and (b) fraction of the baseline L2 TLB                                              |     |

|       | accesses and page table walks remaining on the critical path of execution                                        |     |

|       | with TLB speculation.                                                                                            | 102 |

| 4.11. | Performance gains achieved by GLUE on a multi-VM configuration,                                                  |     |

|       | compared against the ideal performance improvement where all address                                             |     |

|       | translation overheads are eliminated                                                                             | 103 |

| 4.12. | (a) Effect of page sharing and memory sampling turned on (allOn) in a                                            |     |

|       | single VM versus all off (allOff) on page splintering; and (b) Effect of                                         |     |

|       | inter-VM page sharing on page splintering in multi-VM settings                                                   | 104 |

## Chapter 1

# Introduction

This dissertation shows that significant overhead is spent handling address translation, but the majority of this overhead can be eliminated by exploiting prevalent patterns present in memory allocation mechanisms.

### 1.1 Motivation

As processor vendors embrace the era of big data, fields like scientific computing, data mining, social networks, and business management depend on processing massive, multi-dimensional data sets. In this context, it is critical to re-evaluate virtual memory, ubiquitous across computer systems today since it is a powerful abstraction for allocating and managing memory with a flexible and clean programming model. Specifically, virtual memory allows programmers to fully concentrate on finding solutions to their problems as they do not have to worry about the underlying physical memory layout as well as data movement between main memory and backing storage. Virtual memory also provides isolation and protection between processes as each process operates in its own address space. Furthermore, virtual memory promotes modularity in development of complex programs, where individual modules in these programs can be compiled separately and only linked together at runtime. Virtual memory achieves these benefits by separating the virtual address space, which consists of identifiers used by programs to reference information, from the physical address space, which contains memory locations where information is actually stored. Unfortunately, virtual memory suffers from a performance tax caused by this abstraction layer, namely when translating virtual addresses to physical addresses. Therefore, it is crucial to keep this overhead as small as possible so that all of the programmability benefits provided by virtual memory remain accessible to programmers. In fact, according to Peter J. Denning, a pioneer in the field of virtual memory, address translation overhead should stay within 3% of hardware execution time in order for virtual memory systems to be widely adopted by programmers [29].

To keep this overhead as small as possible, hardware vendors have come up with a set of sophisticated solutions, including Memory Management Unit (MMU) with multilevel TLBs, MMU caches, and hardware page table walkers tightly integrated with the core pipelines and memory systems. Despite these efforts, translation overhead remains high at 5% - 14% of system runtime [19,44]. The complex and multi-step translation process attributes to this high overhead. At a high level, mappings between virtual addresses and physical addresses are stored in page tables and managed by the operating system (OS). Page tables are usually organized in a radix-tree format [1,2,5] with many levels. Therefore, translating a virtual to physical address would involve multiple memory accesses, which take several hundreds of CPU cycles to complete [44]. As fast address translation is critical to virtual memory performance, modern processors usually rely on Translation Lookaside Buffers (TLBs), which are on-chip, content-addressable caches, to keep the most recently used virtual-to-physical mappings. Hits in TLBs often return the physical address in a few clock cycles, whereas misses in TLBs default to the long latency multi-level page table look up. Therefore, avoiding TLB misses is key to virtual memory performance. Unfortunately, there are several noticeable trends in the memory systems that tend to increase TLB misses and worsen the translation overhead as discussed below.

First, application trends are aggressively pushing toward larger and larger memory requirements; to date about 2.5 quintillion bytes of data are created daily [41]. From large traditional databases to Internet-driven content, from graph analytics to bioinformatics, the need to process and analyze huge amount of information is accelerating [16,32]. However, performance challenges associated with scaling up virtual memory

to support these growing application areas may significantly slow down progress.

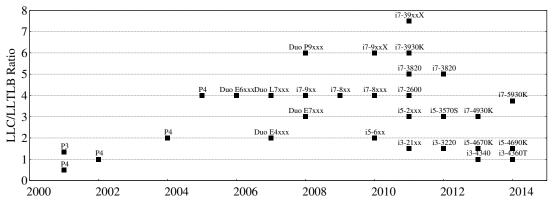

Figure 1.1: Ratio between last level cache capacity and last level TLB reach.

Second, the move toward expanding cache and physical memory size further increases pressure on virtual memory systems and in particular, TLBs. Figure 1.1 plots the ratio between the last level cache and TLB capacity in recent Intel processors. The gap between cache and TLB capacity increased steadily from 2000 to 2011, with the maximum ratio of 7x seen in core i7, 2011. Even though processor vendors have tried to mitigate this gap, it remains high, currently at 4x in core i7, 2014. Besides, the adoption of 3D stacked DRAM [40, 46, 62] and its use as a DRAM cache [47, 55, 56, 71, 81] only worsen this ratio. Similarly, we have seen enormous efforts in architecting future memory technologies [27, 43, 53, 54, 89] which make terabytes of memory possible. This in turn puts tremendous pressure on the reach of any caching structures, including TLBs, in modern processors.

Third, systems with many software layers, e.g. virtualization, are becoming more popular [3]. The main benefits of using such systems are good process isolation and resource consolidation. However, address translation overhead in these scenarios is likely to increase significantly compared to native execution [7,19,26,34]. In fact, according to a recent VMware study, TLB miss handling cost due to the hardware-assisted memory management unit is the largest contributor to the performance difference between native and virtual execution [26].

Fourth, the move toward supporting fully-shared virtual memory between CPUs

and GPUs (for example, as specified in the Heterogeneous Systems Architecture specification [52,72]) further increases the pressure on virtual memory systems and TLBs. The need to provide address translation services for potentially thousands of threads will require architects to squeeze as much benefit out of every last bit of SRAM spent on implementing TLBs.

In this new and diverse space, a good design should allow memory systems to scale without being hamstrung by the virtual memory system. This thesis describes the key designs in this space to achieve that goal.

### 1.2 Our goal

We propose intelligent TLB designs that reduce the address translation overhead significantly so that the memory systems can continue to scale in the presence of the virtual memory system. Our key observation is while operating systems (OS) and hypervisors have a rich set of components in allocating memory, the hardware address translation unit only maintains a rigid and limited view of this ecosystem. Therefore, we seek for patterns inherently present in the memory allocation mechanisms to help catch hardware with the richness of software, thus produce a more intelligent address translation unit.

### 1.3 Profiling Address Translation Overhead

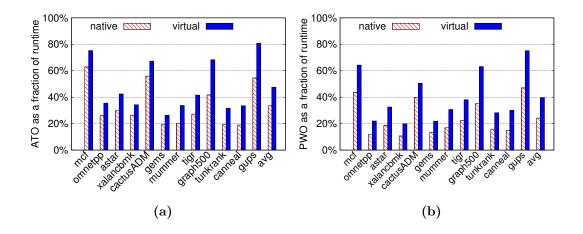

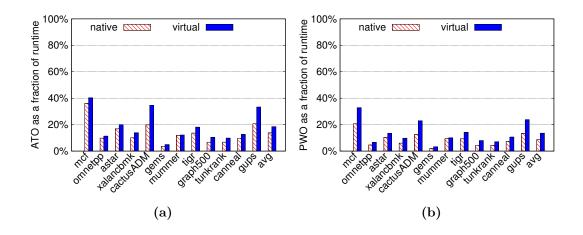

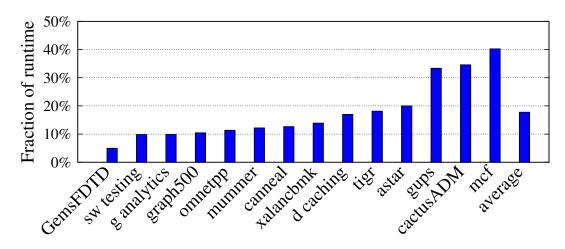

We have profiled the address translation overhead for some of the key scenarios in Section 1.1. This includes running workloads with large memory footprints on both native as well as virtualized environments. We show our initial findings in Figure 1.2.

Figure 1.2 plots the fraction of application runtime spent on address translation on native and virtualized environments. The evaluated systems use only 4KB page size, which is the most popular pagesize on x86-64. All numbers are collected from on-chip counter measurements. As multi-level TLBs are common in modern processors [1, 2, 5], we show two translation overheads in Figure 1.2, namely the fraction of runtime spent on accessing the second level TLBs after the first level TLB

Figure 1.2: (a) Fraction of runtime spent on page table walks; (b) Fraction of runtime spent on looking in the second level TLB and page table walks for 4KB pagesize

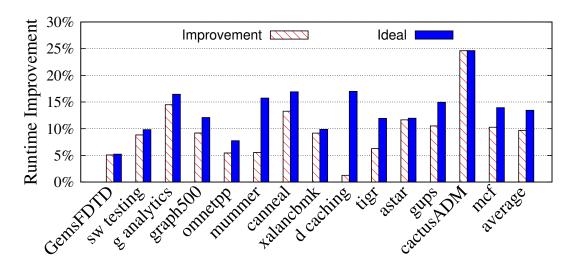

misses and walking the page tables after the second level TLB misses in Figure 1.2a, and the fraction of runtime spent on only walking the page tables in Figure 1.2b. Benchmarks from different benchmark suites have been selected, including SPECcpu<sup>®</sup> 2006 (mcf, omnetpp, astar, xalancbmk, cactusADM, GemsFDTD) [39], bioinformatics benchmarks (mummer, tigr) [8], graph processing (graph500, graph analytics) [32,63], parallel benchmarks (canneal) [24], and the RandomAccess benchmark (gups) [59]. As can be seen from Figure 1.2, all of the benchmarks have at least 20% translation overhead, and in some particular cases, e.g. mcf, cactusADM, graph500, gups, they experience up to 60% translation overhead in native environments. This overhead gets much worse, up to 80% of runtime, in virtualized environments.

One of the potential solutions to mitigate this high overhead is to use larger page sizes, e.g. 2MB in x86 architecture. In general, there are three main benefits of using large pages: lower TLB misses as a single large page is equivalent to 512 small pages, shorter page walk latency as the number of page table levels to be visited is reduced by one, and smaller page table footprint. Figure 1.3b plots the translation overhead when using 2MB page size. As expected, translation overhead is reduced significantly compared to using 4KB page size. However, there are several reasons why large pages are not the universal solution. First, in Figure 1.3b, even though the translation overhead is smaller than in Figure 1.2b, it remains high at 20% on average, and in some particular

Figure 1.3: (a) Fraction of runtime spent on page table walks; (b) Fraction of runtime spent on looking in the second level TLB and page table walks for 2MB pagesize

benchmarks (e.g. mcf, cactusADM, gups), it is close to 40% of system runtime. Second, large pages do not automatically scale with larger physical memory sizes. Third, using large pages conflicts with agile, light-weight memory management mechanisms, e.g. fine-grained protection or page sharing for consolidation. Fourth, if an application's working set is scattered over a wide address space range, large page TLB thrashing can occur [16,86]. System administrators may therefore disable the hypervisor's ability to back guest large pages [86].

#### **1.4** Dissertation Structure

This dissertation proposes and evaluates several TLB organizations that not only reduce the majority of address translation overhead, but also remain effective in the presence of big memory footprint workloads and multi-dimensional translation process. There are three main chapters:

The two chapters chapter 2 and chapter 3 are strongly related. In these works, we observe that modern operating systems often rely on many software components to manage memory, including buddy allocators, slab allocators, and memory compactors; cumulatively, they allocate as many contiguous (or least spatially-adjacent) physical pages to contiguous (or least-spatially adjacent) virtual pages as possible to reduce memory fragmentation. However, MMUs is not aware of this, hence only associates a

single virtual page to a single physical page. We proposes two novel TLB organizations that maintains an elastic representation of virtual memory. Our designs exploits patterns where many translations exhibit "sequential" or "clustered" spatial locality in which a group or cluster of contiguous or nearby virtual pages map to a similarly contiguous or clustered set of physical pages. As a result, our TLB organizations have higher effective reach than conventional TLBs, and manage to reduce 46% of the page walk overhead, which translates to 7% performance improvement.

The lessons learned from identifying the "sequential" and "clustered" spatial locality help guide us in chapter 4, where we seek for more patterns present in the virtual memory systems, with a focus on address translation in virtual machines. We observe that while large pages are often used to mitigate the high cost of two-dimensional page walks, hypervisors might choose to break them into small pages for better guests memory sharing and monitoring. The tension between large page TLB benefits and fine-grained memory management is regrettable because modern OSes work hard to create large pages. Nevertheless, even when this happens, we see that the majority of these small pages remains well aligned within the boundary of the original large page. Based on this observation, we propose a speculative TLB technique to predict the host physical address directly from the guest virtual address. Our design helps reduce more than 70% of the address translation overhead, which is caused by splintering large pages while running highly consolidated virtualized systems.

Finally, we conclude the thesis in chapter 5.

### 1.5 Contributions

This dissertation makes the following contributions:

- We have quantified address translation overhead for a range of workloads on both native and virtualized environments, and established that address translation overhead is high in many scenarios and is likely to worsen in the future.

- We have identified and characterized common, yet previously unknown patterns

in page tables that launched a body of work in scalable TLB organizations without explicit hardware-software coordination. This has in turn enabled continued progress in processing and analyzing ever larger datasets for the benefit of a large range of technically, economically, and socially important problems.

## Chapter 2

# Exploiting Sequential Locality in Page Translations for Large Reach TLBs

### 2.1 Introduction

In this chapter, we propose techniques exploiting page allocation contiguity that are orthogonal to superpaging, and require no operating system (OS) management overhead. We observe that OS memory allocation mechanisms such as buddy allocators and memory compaction daemons inadvertently allocate contiguous physical page frames to contiguous virtual pages. While these levels of *intermediate contiguity* (in the range of tens of pages) fall short of the contiguity requirements of superpages (hundreds of contiguous pages), they occur naturally and independently of superpages, even in the presence of great system load. In response, we propose Coalesced Large-Reach TLBs (CoLT), a series of hardware mechanisms that allow TLBs to coalesce multiple contiguous virtual-to-physical address translations, thereby enabling them to have greater memory reach. CoLT coalesces multiple virtual-to-physical page translations without explicit OS support or high management overhead. In systems with superpaging, CoLT exploits the vast amounts of contiguity that exist but are insufficient for superpage construction. Even in systems without superpaging, CoLT exploits naturally-occurring contiguity. Our contributions are as follows:

First, we conduct a range of real-system experiments to gauge how often consecutive virtual pages are allocated consecutive physical pages. We find that on Linux, tens of pages are usually contiguous, even in the presence of significant system load and without superpaging support. Furthermore, while superpaging does increase contiguity, most of it falls short of the level necessary to actually create large pages (a 2MB superpage needs 512 contiguous 4KB base pages, while we see tens of contiguous pages). Instead, we show that TLB coalescing is an effective way of leveraging contiguity.

Second, we propose CoLT using commercially-available two-level TLB hierarchies commonly found in processors today [9,42]. We detail mechanisms to effectively coalesce multiple contiguous virtual-to-physical page translations on set-associative L1 and L2 TLBs, exploring various microarchitectural tradeoffs in their design. Our strategies eliminate roughly 40% of L1 and L2 TLB misses, resulting in average performance improvements of 12%.

Third, we develop CoLT support for small, fully-associative TLBs commonly found in processors to cache superpage entries [9,42]. We show how to overcome the challenge of designing these small structures, achieving L1 and L2 TLB miss elimination rates of 58% on average. These translate to average performance improvements of 14%.

Finally, we explore mechanisms that combine coalescing on both the standard setassociative TLBs and smaller fully-associative TLBs traditionally reserved for superpages. By carefully selecting which structure to allocate coalesced entries in, we achieve L1 and L2 TLB miss eliminations of 55%, yielding average performance improvements of 14%.

Overall, we are the first to observe and exploit intermediate levels of allocation contiguity naturally provided by operating systems. Our techniques are highly effective, yet low overhead. Furthermore, they provide benefits even with heavy system load and regardless of the presence of superpaging.

### 2.2 Background and Related Work

### 2.2.1 Prior TLB Enhancement Techniques

Address translation, especially with virtualization and larger application working sets, is a primary source of system performance degradation [19,60]. In response, researchers have considered techniques to improve TLB structure, lookup, and placement [21,28]. More sophisticated techniques such as TLB prefetching and mechanisms to accelerate page walks have also been considered [14, 23, 48, 77]. While effective, high TLB miss rates remain problematic.

### 2.2.2 Superpaging Benefits and Problems

Large pages have been proposed to lower TLB miss rates [31, 33, 64, 74, 83, 84]. Large pages use the same address space as conventional pages but have sizes that are a power-of-two multiple of baseline pages. For example, x86 systems use 4KB baseline pages and support 2MB and 1GB large pages. Furthermore, large pages must be aligned in both virtual and physical memory (superpages of size N must begin at virtual and physical addresses that are multiples of N).

In general, there are three main benefits of using large pages: lower TLB miss rates by replacing hundreds of base page translations with a single superpage translation entry, shorter page walk latency, and smaller page table footprint. However, large pages do not automatically scale up with the larger physical memory. Besides, large pages have high management overheads [64, 83]. They require modifications to OS memory management policies and mechanisms such as support for multiple page sizes and superpage creation. In particular, the process of ensuring that sufficient contiguous physical pages are allocated to virtual pages (to create superpages) has high performance overheads [31,64]. As such, superpages increase the amount of I/O, page initialization/fault latency.

Cumulatively, these problems can easily outweigh the benefits of reduced TLB miss rates. This has a few implications. First, currently-available systems have no universal superpaging support in either the hardware or the OS. Architectures vary in the size of superpages they support (e.g. Intel supports 2MB/1GB superpages while Sparc supports 256MB superpages). Operating systems differ in how they create the contiguity necessary for superpages. For example, FreeBSD uses a reservation-based approach [15], while Linux optimistically allocates 2MB pages, later breaking them into baseline pages if the 2MB version is deemed overly-aggressive [10]. Furthermore, many operating systems do not support superpages. Even when superpaging is supported, it is used sparingly to minimize management overheads. In fact, we show that there

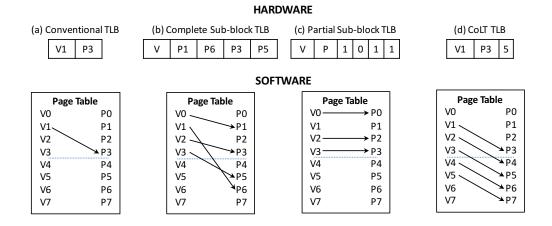

Figure 2.1: Operation of complete sub-blocking and partial sub-blocking versus CoLT TLB. For each approach, we show the structure of a single entry and a page table with the PTEs that can be exploited.

exist immense amounts of page allocation contiguity that remain unharnessed because their level of contiguity is insufficient for superpaging (in the tens of pages rather than the required hundreds of pages).

### 2.2.3 TLB Subblocking and Speculation

Two hardware-based schemes have been proposed to mitigate superpaging management overheads. Talluri and Hill [83] present *partial-subblock* and *complete-subblock* TLBs, which record ranges of physical pages per virtual page entry, in contrast with the structure of a conventional TLB entry, which only captures a single PTE (in Figure 2.1(a), virtual page V1 and physical page P3)

Complete sub-blocking: Complete sub-blocking looks for clusters of PTEs with contiguous VPNs. For a given sub-block factor N, this approach looks for *B aligned* virtual pages (i.e., all virtual address bits apart from the bottom  $\log_2(B)$  bits are the same). It then places all the PTEs corresponding to this group in one complete entry. Figure 2.1(b) shows an example of this where virtual pages 0-3 all are aligned for a sub-block factor of 4. This means that their PTEs can be stored in one entry if it maintains a field for each PPN (e.g., P1, P6, P3, and P5). Unfortunately, the ability of complete subblocking to store any set of PPNs requires expensive hardware (multiple PPN fields). Furthermore, complete sub-blocking stores a PTE count only equal to the sub-block factor.

Partial sub-blocking: Talluri and Hill proposed partial sub-blocking as a lower-overhead alternative to complete sub-blocking [83]. Figure 2.1(c) shows that partial sub-blocking searches for PTEs with an aligned group of virtual pages and an aligned group of physical pages. All PTEs that have VPNs and PPNs with the same offset from the start of the aligned package are coalescable into a single entry. In our example, PTEs for VPNs 0, 2, and 3 achieve this. This approach permits "holes" in a group of PTEs when the physical page offset within the aligned packet is different from the virtual page offset (e.g., the PTE for virtual page 1 in our example). Partial sub-blocking achieves high reach using much simpler hardware than complete sub-blocking by imposing alignment and offset restrictions on PPNs. Figure 2.1(c) shows each entry maintains only a bit vector recording the presence of the physical pages rather than the entire PPN. However, partial sub-blocking's PPN alignment and offset requirements cannot capture many instances of spatial locality. In practice, we find that most instances of spatial locality in PTEs do not fit the alignment requirements of partial sub-blocking (our measurements show that less than 10% of PTEs fit these alignment requirements naturally). While the original partial sub-blocking approach [83] addresses this problem by adding specialized OS code to generate the right alignment and offset features, our goal is to avoid explicit OS modifications.

Alternately, Barr, Cox, and Rixner [15] increase TLB hits with speculation in systems with reservation-based superpaging [64]. Here, physical pages are allocated in aligned 2MB regions of memory corresponding to their alignment within a 2MB region of virtual memory. Since this makes physical page references predictable, Barr, Cox, and Rixner propose SpecTLB, a separate structure to speculatively provide physical addresses when standard TLBs miss. While effective, SpecTLB requires reservationbased superpaging, which is not in widespread use (eg. Linux superpaging [10] does not use reservation-based superpages). SpecTLB also requires additional hardware and can suffer from incorrect speculations.

### 2.2.4 Our Approach

Our goal is to demonstrate that operating systems naturally generate intermediate levels of page allocation contiguity without explicit support like superpaging, and then to leverage this contiguity to realize large-reach TLBs. Unlike superpaging or subblocked TLBs, we therefore want to avoid OS intrusion and high management overheads. Moreover, we want to exploit *any* amount of contiguity rather than restricting ourselves to set superpage sizes or sizes accommodated by a particular sub-blocked TLB. Unlike SpecTLB, we also do not want to restrict ourselves to one type of superpaging. In fact, CoLT must be effective even *without* superpaging and under high system load. At a high level, as shown in Figure 2.1(d) a CoLT entry maps a group of contiguous, spatially-local PTEs (in our example, PTEs for virtual pages 1-5). Any arbitrary set of PTEs can be accommodated (e.g., five PTEs in Figure ??) by recording only the base PTE and the number of coalesced PTEs. On look-up, the offset between the base virtual address stored in the tag is used to calculate the offset from the base physical page. There are no alignment restrictions for this approach. Our studies are structured as follows:

We first study how often contiguity exists in real systems, and how this contiguity is affected by buddy allocators, memory compaction superpaging support, and system load. Real-system experiments are particularly crucial since we must establish that contiguity does indeed exist under a variety of scenarios and even in the presence of heavy system fragmentation. Past architectural studies [15] usually focus on simulations to study contiguity; since simulations only capture a small window of the runtime at system boot time when there is little fragmentation, real-system numbers are essential to showcase the wide applicability of our approach.

We then exploit contiguity to realize CoLT, a range of coalesced TLBs. Commercial two-level TLB hierarchies are comprised of set-associative L1 and L2 TLBs, supported by smaller fully-associative buffers to store superpages. We implement coalescing on various combinations of these structures, assessing their benefits and design challenges. In order to maintain low-overhead designs, unlike past speculation or past prefetching work [15,23,48], we do not augment the standard TLBs with separate structures for our techniques. Therefore, we adjust coalescing designs to seamlessly fit into existing TLB microarchitecture.

### 2.3 Understanding Page Allocation Contiguity

We now explore why operating systems often allocate contiguous physical page frames to contiguous virtual pages. Since CoLT relies on this behavior, we ascertain which memory allocation policies and mechanisms produce contiguity.

### 2.3.1 Defining Page Allocation Contiguity

We say that system contiguity exists when consecutive virtual pages are allocated consecutive physical page frames. For example, if virtual pages 1, 2, and 3 are allocated physical page frames 58, 59, and 60, we say that these pages are contiguous. Moreover, since this example involves three pages, we say that this is an instance of 3-page contiguity.

Our definition is distinct from superpages in two ways. First, superpages require a set amount of contiguity. For example, 2MB superpages on x86 systems require instances of *512-page* contiguity. Instead, we make no restrictions on the amount of contiguity that is useful. Second, unlike superpages, we make no assumption on alignment. Overall, our relaxations on contiguity amounts and alignment restrictions reveal huge amounts of *intermediate* contiguity.

### 2.3.2 Sources of Page Allocation Contiguity

Operating systems maintain a complex set of policies and mechanisms to perform page allocation such that page faults, initialization, and replacement are minimized. A number of these policies have a deep impact on page allocation contiguity. We elaborate on them here, focusing on Linux.

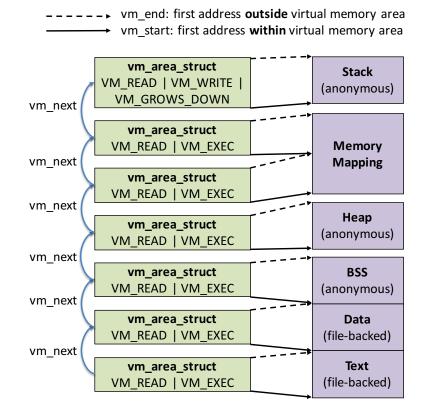

Figure 2.2: Virtual memory areas in process address space.

### 2.3.2.1 Process address space.

Figure 2.2 shows the layout of the process address space. It consists of multiple virtual memory areas (VMA), which are regions of contiguous virtual addresses, and these regions never overlap. All VMAs are linked together in the form of a red-black tree for fast search operations. Each instance of VMA has several attributes, including its start and end addresses, and access right flags. A VMA that does not map a file is annonymous. Except the memory mapping segment, each memory segment in Figure 2.2, e.g. heap, stack, corresponds to a single VMA.

A VMA is just an agreement between a program and the kernel. When a program allocates memory via a malloc or mmap call, the kernel just creates or updates the corresponding VMM. The memory request is not actually satisfied until a page fault happens to do real work [37].

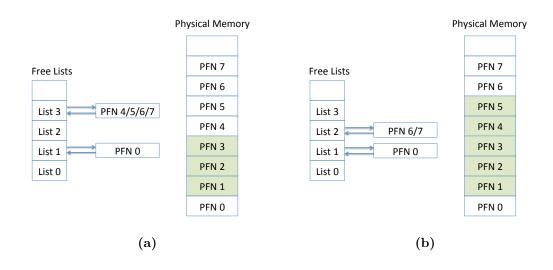

Figure 2.3: (a) Buddy allocator used for physical page allocation. Already allocated pages are shaded, while free pages are tracked by the free lists. (b) Buddy allocator state after an allocation for 2 pages is finished.

#### 2.3.2.2 Buddy allocation.

Most operating systems, including Linux, use a buddy allocator to track physical pages and assign them to virtual pages on demand. Figure 2.3a illustrates the operation of a buddy allocator, assuming that pages 1, 2, and 3 are already allocated. All free physical pages or page frames (PFs) are grouped into ten lists of blocks, which we refer to as *free lists*. Entry x in the free list tracks groups of  $2^x$  contiguous physical pages. Since physical page 0 is non-contiguous, it is listed by entry zero. On the other hand, pages 4-7 have 4-page contiguity and are hence listed by entry two.

Physical page allocations proceed as follows. Suppose an application requires an Npage data structure. The buddy allocator first searches the free list entry corresponding

to the smallest contiguous page frames bigger than N (entry  $\lceil log_2(N) \rceil$ ). If a block of

free physical pages is found in that list, allocation successfully completes. Otherwise,

the free list is progressively climbed until an entry with a block of free contiguous

physical pages is found. Once a free block is found, the buddy allocator must minimize

memory fragmentation. Therefore it iteratively halves the block, inserting these new

blocks in their appropriate free list locations, until it extracts a block of N contiguous

physical pages. As an example, Figure 2.3b shows the state of the free list after an

application level request for two physical pages to be allocated. At first, entry 1 in the

Moveable Pages Moveable Pages

# Figure 2.4: The memory compaction daemon tracks movable and free memory pages, exchanging them to eliminate fragmentation.

free list is checked; however, since this is empty, entry 2 is scanned. Here, a free block with contiguous physical pages 4, 5, 6, and 7 is found. Hence, the buddy allocator halves this block of four pages, returning pages 4 and 5 to the application and moving pages 6 and 7 to free list entry 1. Apart from allocation, the buddy allocator also updates its state when physical pages are released. At this point, the kernel attempts to merge pairs of free *buddy* blocks if both have the same size and are contiguous. This merge process is iterative, leading to large swathes of contiguity.

Therefore, though buddy allocation does not produce superpage-level contiguity, it generates large quantities of intermediate contiguity. We will show that the buddy allocator successfully produces this contiguity even in the presence of significant system load. While traditionally irrelevant for TLBs, we aim to exploit this for CoLT.

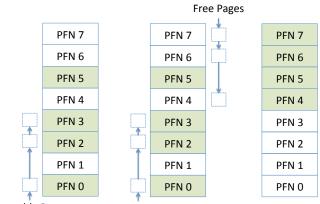

#### 2.3.2.3 Memory compaction.

While the buddy allocator does try to group together contiguous physical pages on page deallocations, this alone is insufficient to minimize memory fragmentation. Fragmentation is pronounced when multiple processes with large working sets simultaneously run on the system. Therefore, many operating systems, including Linux, boost the buddy allocator with a separate memory compaction daemon. Figure 2.4 details the Linux memory compaction daemon in three steps on a heavily-fragmented system. First, as shown in the left-most figure, memory compaction runs an algorithm that starts at the bottom of the physical memory and builds a list of allocated pages that are *movable*. While most user-level pages are movable, pinned and kernel pages usually are not. Nevertheless, user-level pages usually outnumber kernel pages, making most pages movable.

Second, the daemon concomitantly runs an algorithm that starts at the top of physical memory and builds a list of free pages. Eventually, the two algorithms meet in the middle of the physical page list. At this point, Linux invokes migration code to shift the movable pages to the free page list, yielding the unfragmented diagram at the right of Figure 2.4.

Since there is a cost associated with moving pages, the compaction daemon is only triggered when there is heavy system fragmentation. As such, its operation naturally produces contiguity, especially in tandem with the buddy allocator. In fact, we will show that this daemon successfully generates contiguity even under heavy system fragmentation.

#### 2.3.2.4 Transparent hugepage support.

Aside from buddy allocation and memory compaction, support for superpages is a primary cause of page allocation contiguity. Unlike those two schemes however, superpage management comes with overheads. As a result, Linux's Transparent Hugepage Support (THS), supported since the 2.6.38 kernel [10], uses superpages carefully. When THS is enabled, the memory allocator attempts to find a free 2MB block of memory. If this block is naturally aligned at a 2MB boundary, a superpage is constructed. In practice, the OS relies on the memory compaction daemon to construct these 2MB regions. When a superpage cannot be constructed, the system defaults to the buddy allocator. Even when the 2MB pages are allocated, increased load can eventually make them harmful. Therefore, system pressure triggers a daemon that breaks superpages into baseline 4KB pages.

We will show that in practice, THS helps create additional levels of contiguity for two reasons. First, if optimistically-allocated 2MB superpages are eventually split due to

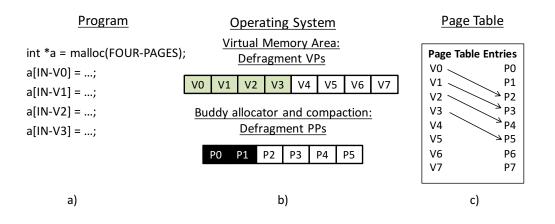

**Figure 2.5:** Interaction between program's fault order and memory management. system pressure, they retain contiguity among tens of baseline 4KB pages. Second, THS relies on the memory compaction daemon, triggering it more often and providing the buddy allocator even higher levels of contiguity. Therefore, though THS uses superpages sparingly, it constructs intermediate contiguity useful for CoLT.

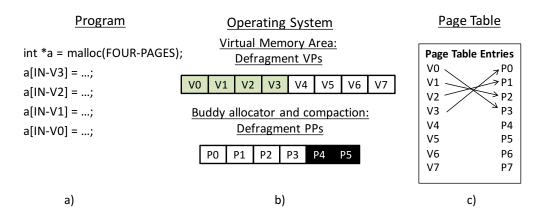

### 2.3.2.5 Putting Things Together.

In this section, let's see how everything works together to generate the intermediate contiguity between virtual pages and contiguous physical pages. Figure 2.5 shows the interaction between program faults order and kernel's memory management. In this example, a program tries to allocate four memory pages in Figure 2.5(a). As mentioned in Section 2.3.2.1, this request is not honored right away by the kernel. Instead, the kernel simply updates the heap VMA and returns – V0 to V3 region in Figure 2.5(b). No page frames are actually allocated and the new pages are not present in physical memory. Once the program actually accesses the pages, the processor page faults and invokes a page fault handler in the kernel. The handler searches for the VMA covering the faulted virtual address, when a VMA is found, the kernel creates a PTE to map the faulted virtual page to a allocated physical frame.

With the help from the buddy allocator and memory compaction, region of free contiguous physical pages have been formed, P0 to P3 in Figure 2.5(b). If program faults in order, as shown in Figure 2.5(a), physical frames will be allocated in order

from the contiguous physical pool. As a result, consecutive mappings between virtual and physical pages are established.

#### 2.3.2.6 System Load and Memory Fragmentation.

Finally, page allocation contiguity is deeply affected by the system load. If many processes run simultaneously, main memory is likelier to be fragmented. Therefore, one may initially expect that higher load degrades contiguity. Surprisingly, we will show that contiguity can actually *increase* with greater system load. This occurs because system load has a complex relationship with the memory compaction daemon, triggering it more often when there is higher load. This can, in turn, provide greater swathes of contiguous physical frames to the buddy allocator, eventually resulting in more contiguity.

#### 2.4 CoLT Design and Implementation

Having detailed contiguity sources, we now propose three variants of CoLT. Overall, they share three design principles. First, they detect instances of consecutive virtualto-physical address translations. These entries are coalesced into single TLB entries, so as to reduce miss rates. Second, CoLT coalesces only on *TLB misses*. While TLB hits could also prompt coalescing, this may increase lookup latencies. Third, coalescing is *unintrusive*, unlike speculation and prefetching [15,23,48,77] which can degrade performance. For example, incorrect speculations suffer a high penalty. Incorrect prefetches lead to the eviction of useful entries and higher bandwidth usage. Prior work mitigates these problems by TLB speculating or prefetching using separate structures [15,23,48]. In contrast, we coalesce entries directly into the TLBs but ensure that coalescing occurs only around *on-demand* translations. In the worst case, coalesced entries may be unused but are not harmful. This is crucial given that system contiguity does not necessarily imply that all contiguous translations are used in temporal proximity. We ensure coalesced entries are available if needed but do not harm TLB hit rates when they are unused.

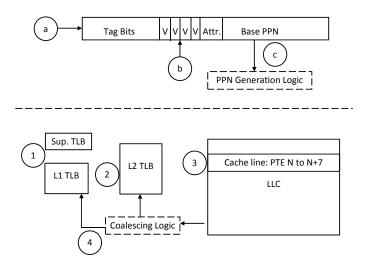

Figure 2.6: CoLT for set-associative L1 and L2 TLBs.

We propose three variants of CoLT for commercial two-level TLB hierarchies. This hierarchy contains set-associative L1 TLB and L2 TLBs, used to cache baseline 4KB pages [9,42]. Superpages are cached in separate small, fully-associative TLBs that are accessed in parallel with the L1 TLB. Note that the L2 TLB is inclusive of just the set-associative L1 TLB and not the superpage TLB.

There are three natural coalescing mechanisms for this hierarchy. First, we coalesce in just the set-associative L1 and L2 TLBs. Second, we coalesce in the superpage TLB only. Third, we use a combined approach that routes some coalesced entries to the set-associative TLBs and others to the superpage TLBs. We now describe each of these schemes.

#### 2.4.1 CoLT-SA Design and Implementation

CoLT-Set Associative (CoLT-SA) coalesces multiple virtual-to-physical page translations in the set-associative L1 and L2 TLBs. We first detail its high-level operation and then focus on specific design challenges.

#### 2.4.1.1 Overall operation.

The bottom half of Figure 2.6 shows a high-level view of CoLT-SA. In step 1, the setassociative L1 TLB and superpage TLB are looked up in parallel. Assuming L1 and L2 TLB misses (step 2), a page table walk brings in the desired translation entry into the LLC (step 3). At this point, two parallel events occur. First, the requested translation is returned to the processor pipeline. In parallel, the *Coalescing Logic* studies the translations around the requested entry for contiguity. It coalesces as many of these translations as possible, as long as map to the same set. This entry is inserted into the L1 and L2 TLBs (step 4). As we will detail, conventional set-associative TLBs map consecutive virtual addresses (and hence contiguous translations) to consecutive sets, precluding coalescing. We therefore modify the virtual page bits used for set-selection so that translations for groups of consecutive virtual page numbers do map to the same set, allowing for potential coalescing. Furthermore, since we provide the requested translation to the pipeline in parallel with the *Coalescing Logic's* operation, the latter is off the critical path and does not affect TLB miss handling times.

#### 2.4.1.2 TLB set selection.

Conventional set-associative TLBs place translations of successive virtual page numbers into successive sets, preventing coalescing. In response, we modify TLB set selection. For example, a TLB with 8 sets uses bits 2 to 0 of the virtual page number for set selection (VPN[2-0]). Instead, we left-shift the index bits by  $log_2(N)$  bits if we want to place N consecutive translations in the same set (permitting us to coalesce a maximum of N translations per entry). In our example, to ensure that translations with four consecutive virtual pages map to the same set, we use VPN[4-2] as the new indexing bits.

To coalesce more entries, the indexing bits are further left-shifted (for example, to coalesce up to eight entries, VPN[5-3] must be used). However, using higher order bits for set indexing increases conflict misses since more consecutive entries are mapped to the same set. This is a fundamental tradeoff for CoLT-SA designs – in choosing the correct index bits, we must balance opportunities for coalescing with potentially higher conflict misses. We find that allowing for coalescing of four contiguous translations generally performs best.

#### 2.4.1.3 Lookup operation.

The top half of Figure 2.6 illustrates CoLT-SA lookups. Each coalesced TLB entry maintains tag bits, the higher order bits left of the index bits used for set selection. For example, if up to four contiguous translations can be coalesced in a TLB with eight sets, VPN[4-2] is used for set selection and VPN[63-5] is the tag. In step (a), this tag is checked against the requested virtual page number. In step (b), the non-index lower-order virtual page bits (VPN[1-0] in our example) are used to select among multiple valid bits. There is one valid bit for every possible translation in a coalesced entry. These valid bits indicate the presence of a translation in the coalesced entry. If on step (b), a valid bit is set, there is a TLB hit. At this point, extra logic calculates the physical page number. CoLT entries store the base physical page number for each coalesced entry. This number corresponds to the virtual page represented by the first set valid bit. Therefore to reconstruct the physical page number, combinational logic (*PPN Generation Logic*) calculates the number of valid bits away this entry is from the first set valid bit. This number is then added to the stored base physical page number to yield the desired physical page.

We believe this lookup operation remains low-overhead and will not impact TLB access cycle times. First, the initial tag match and check of valid bits is simple. The PPN generation logic addition is also low-overhead as the amount of coalescing is bounded (in our example, at best, an addition of four will be required). As such, readily-implementable combinational logic, similar to logic used to calculate prefetching strides and addresses or update branch predictor state, can calculate the physical page number. This is substantially lower-overhead than prior prefetching schemes requiring dedicated adders [48]. This combinational logic will not affect TLB access cycles, adding just a few gate delays at best.

#### 2.4.1.4 Practical coalescing restrictions.

Ideally, after the page table is walked to handle a TLB miss, coalescing logic finds as many contiguous translations around the requested translation as possible. Practically, however, coalescing is restricted by two constraints. First, as we have already discussed, the choice of index bits for set selection places a limit on coalescing opportunity. A second limit arises from our desire to minimize the overhead associated with searching for contiguous translations. On a TLB miss, a page table walk finds the desired translation. We aim to prevent any additional page walks when checking for contiguous entries adjacent to the requested translation. Since the page table walk accesses the last-level cache (LLC) and brings data in 64-byte cache line sizes, seven additional translations are fetched. These translations are brought without additional memory references; thus we check just them for contiguity. In practice, this approach restricts coalescing to a maximum of eight translations. Despite this restriction, CoLT eliminates a high number of TLB misses.

#### 2.4.1.5 Replacement, invalidations, and attribute changes.

CoLT-SA assumes standard LRU replacement policies. While there may be benefits in prioritizing entries with different coalescing amounts differently, we leave this for future work. We also assume a single set of attribute bits for all the coalesced entries. This restricts the amount of contiguity that we can exploit; more sophisticated schemes supporting separate attribute bits per translation in a coalesced entry will improve our results. Furthermore on TLB invalidations, we flush out entire coalesced entries, losing information for pages that would be unaffected in standard TLBs. Gracefully uncoalescing TLB entries and only invalidating victim translations will perform even better. This too is the subject of future work.

#### 2.4.2 CoLT-FA Design and Implementation

Rather than supporting coalescing in set-associative TLBs and changing their indexing scheme, we can instead coalesce into just the fully-associative TLB. This structure is usually used exclusively for superpages. However, superpages are often used sparingly. Hence, allocating coalesced entries into this structure in addition to superpages entries may be beneficial. We refer to this as CoLT-Fully Associative (CoLT-FA).

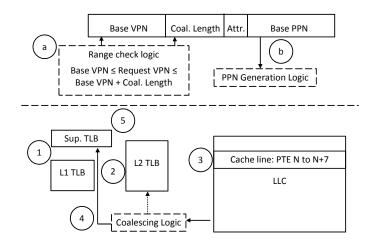

Figure 2.7: CoLT for the fully-associative superpage TLB.

#### 2.4.2.1 Overall operation.

The bottom half of Figure 2.7 delineates CoLT-FA operation. Assuming misses in all the TLBs (steps 1 and 2), a page walk is conducted in step 3. At this point, a cache line provides up to eight translations that can be checked for contiguity. Up to eight translations are now coalesced in step 4. If coalescable, the entry is loaded into the fully-associative TLB. If no coalescing is possible, it is loaded into the set-associative L1 and L2 TLBs.