©2017

WEN-CHIANG HONG

ALL RIGHTS RESERVED

### Magnesium Zinc Oxide High Voltage Thin Film Transistors

By

### **WEN-CHIANG HONG**

A dissertation submitted to the

**Graduate School-New Brunswick**

Rutgers, The State University of New Jersey

In partial fulfillment of the requirements

For the degree of

**Doctor of Philosophy**

**Graduate Program in Electrical and Computer Engineering**

Written under the direction of

**Professor Yicheng Lu**

And approved by

New Brunswick, New Jersey

May, 2017

### ABSTRACT OF THE DISSERTATION

# Magnesium Zinc Oxide High Voltage Thin Film Transistors By WEN-CHIANG HONG

Dissertation Director: Prof. Yicheng Lu

Energy is one of the most important topics in the 21<sup>st</sup> century, and solar energy has been a leading technology in the search to replace fossil-fuel energy as a sustainable and clean energy source. In order to provide an energy-efficient, less expensive, and reliable energy source, the PV system on glass (PV SOG) is emerging as an attractive concept. It integrates solar cells, solar inverters, and controller circuits on a single glass substrate.

This dissertation focuses on development of the novel oxide-based high voltage thin film transistor (HVTFT) on glass technology, which is one of the core devices for solar inverter of the PV-SOG. Currently, the inverter counts for more than 10% of the total cost of an entire PV system. The solar inverter will be the major challenge of PV-SOG because the conventional solar inverters are bulky and could not be directly built on glass substrates. In particular, its key device, high voltage transistor, is not only pricy but also requires high process temperature which is incompatible with glass substrates.

In comparison of several semiconductor materials, such as polycrystalline silicon, amorphous silicon, SiC and GaN, ZnO based materials have several

promising features suitable for HVTFT on glass technology, including wide bandgap, high thermal conductivity, high mobility, and low deposition temperature. However, the thin film transistor (TFT) made up of the pure ZnO generally suffers from poor stability and reliability due to high defect density in the material. Because energy source is a basic unit of the infrastructure, it's critical for a solar energy system to have a long lifespan. The first important issue of this dissertation research was to improve the TFT stability by adding a small amount of Mg into ZnO to form the ternary oxide, MgxZn1-xO (MZO, X<0.03) as the TFT channel. The density of oxygen vacancies in MZO was reduced so that after negative bias stress (NBS) the threshold voltage shift of MZO TFT was 30% smaller in comparison with the shift of ZnO TFT counterpart.

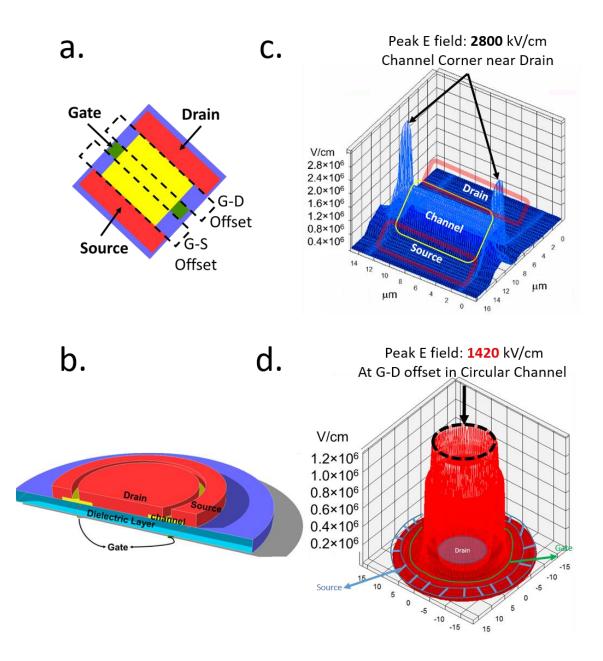

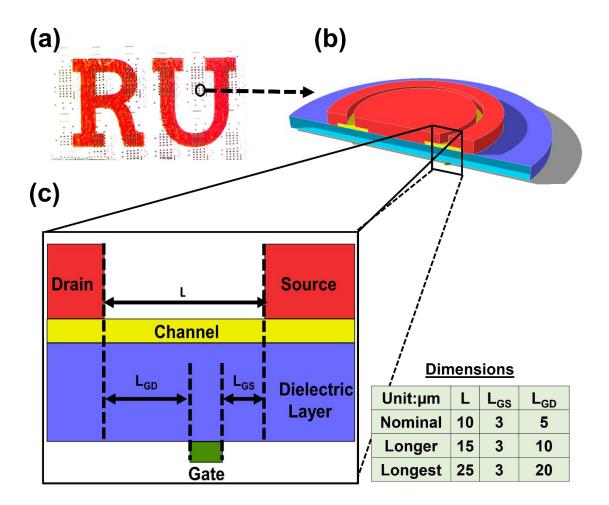

Based on the solid foundation of stable MZO TFTs, MZO high voltage TFT (MZO HVTFT) on glass technology was designed and developed. To eliminate the electrical field crowding around the corners of the conventional TFT with a rectangular channel, a symmetric circular-shape transistor was adapted. From the simulation result, the peak electrical field is reduced by 50% in the symmetric circular structure than in the conventional rectangular structure. However, the MZO HVTFT with the circular configuration only showed a blocking voltage of 92V. To further enhance the device performances, especially the blocking voltage, we developed a modified MZO (m-MZO) HVTFT, which had an ultrathin MZO transition layer (MZO-TL) using the in-situ modulation doping in the channeldielectric interface. The comprehensive characterizations using X-ray photoelectron spectroscopy (XPS) and energy-dispersive X-ray spectroscopy

iii

(EDS) were conducted to study depth profiles of elements across the channel-gate dielectric interface. It was proved that this interface engineering effectively suppressed the interdiffusion of Zn and Si between the channel and dielectric layers, resulted in the reduction of the interface states and the oxide trapped charges. The combination of the interface engineering with the symmetric device design significantly increased the blocking voltage of the m-MZO HVTFT on glass. As a result, the regular m-MZO HVTFT (channel length=10 $\mu$ m) has on/off ratio of 3.5×10<sup>10</sup> and blocking voltage of 305V, which is suitable for the regular AC 110V power system. The m-MZO HVTFT with a channel length=25 $\mu$ m has on/off ratio of 3.3×10<sup>9</sup> and blocking voltage of 609V which is suitable for the regular AC 220V power system.

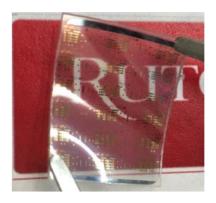

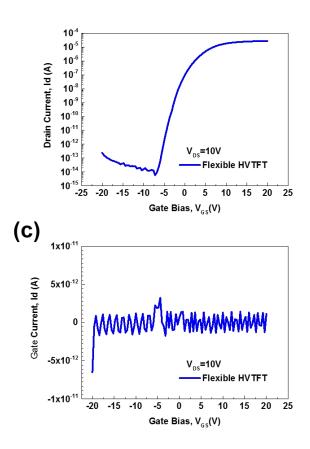

Finally, in order to expand the HVTFT technology from glass to the flexible substrate, the ZnO-based HVTFTs on plastic substrate were explored. By adopting low temperature even room temperature process, such as sputtering and atomic layer deposition, the flexible HVTFT consisting of the ZnO based channel with Al<sub>2</sub>O<sub>3</sub> dielectric layer showed an on/off current ratio of 10<sup>9</sup> and blocking voltage of 92V.

The MZO HVTFT technology opens opportunities for cost-effective and highly efficient power management systems for many applications. The HVTFTs on glass will serve for the inverter in novel Building-integrated photovoltaics (BIPV) and smart glass while the flexible HVTFT is promising for the emerging selfpowered wearable systems.

iv

## Dedication

### To my family and mentor

Chien-Yu Lin, who always loves me unconditionally, takes care of me and gives me strength.

Professor Yicheng Lu, who teaches me the true importance of life and research.

Chin-Kuo Hong and Hsiu-Chen Chen, who raised me and support the pursuit of

my dream.

Yi-Ting Wu and Shih-Kuei Lin, who give my family unreserved support and love.

Zachery Hong and Katherine Hong, who are my angels.

#### Acknowledgement

I would like to show my deepest gratitude to my dissertation advisor, Professor Yicheng Lu, for his limitless support in both my Ph.D. work and my daily life. His novel and insightful ideas inspired my creativity, and his precise and logical critiques polished my skills of logic. His patience and open-mindedness gave me great freedom to explore my passion. Having him as my advisor is my most fortunate opportunity in life.

I also would like to thank my dissertation committee members, Prof. Jaeseok Jeon, Prof. Mehdi Javanmard, and Prof. Ming Lu for spending their valuable time to review my dissertation. Their profound questions and suggestions improved my understanding of the topics and helped to promote the improvement of my dissertation.

It's my honor to have had the chance to work with colleagues in Prof. Lu's research group, who have provided indispensable help to further my work. Dr. Chieh-Jen Ku gave me comprehensive training in device fabrication and set a solid foundation for my dissertation. Dr. Pavel Reyes guided me through writing papers, making proposals, and reviewing scientific articles. Dr. Rui Li gave professional and limitless support of material growth and analysis. My thanks also go to all other members: Dr. Ziqing Duan, Dr. Yang Zhang, Mr. Tengfei Xu, Mr. Tanvir Mohsin, Mr. Keyang Yang, Ms. Szu-Ying Wang, Ms. Ke Tang, Mr. Guangyuan Li, Mr. Yuxuan Li, Mr. Hongfei Ye, Ms. Navila Alim, and other visiting scholars and students. Their great assistance in the research as well as their friendship gave

vi

me the momentum and courage to solve difficulties in both scientific work and daily life. A special thank has to be given to Mr. Robert Lorber, our guardian of the cleanroom. Your talented mechanical skills keep our tools running. It has been an unforgettable experience to work with you and Dr. Pavel Reyes to manage the laboratory.

My friends have given me great backing in my life. Ms. Carol Blumenthal, Dr. Jeremy Sykes, and Mrs. Tari Lee Sykes have always been there for my family and me. Your support helped us to stand on our own feet in the United States, and your wise advice guided us through the seemingly hopeless days. I really appreciate your great care and generous support.

Above all, I would like to thank my family. My wife, Chien-Yu Lin, always supports me unconditionally, encourages me consistently, and loves me unreservedly. My parents, Chin-Kuo Hong and Hsiu-Chen Chen, always give me great freedom and support in my path to explore my passion. My parents-in-law, Yi-Ting Wu and Shih-Kuei Lin, always gives my wife, my children, and me the greatest love and care.

This work has been supported by the National Science Foundation under Grant No. CBET-1264508. Research carried out (in part) at the Center for Functional Nanomaterials, Brookhaven National Laboratory, which is supported by the U.S. Department of Energy, Office of Basic Energy Sciences, under Contract No DE-SC0012704.

## **Table of Contents**

| ABSTRACT      | F OF THE DISSERTATIONii                     |

|---------------|---------------------------------------------|

| Dedication    | V                                           |

| Acknowled     | lgementvi                                   |

| Table of Co   | ontentsviii                                 |

| Lists of Tal  | blesxiii                                    |

| List of Illus | trationsxiv                                 |

| Chapter 1     | Introduction1                               |

| 1.1. Mo       | otivation1                                  |

| 1.2. Ob       | jectives and Scope of Work3                 |

| 1.3. Or       | ganization of the Dissertation4             |

| Chapter 2     | Technical Background5                       |

| 2.1. Ph       | otovoltaics System on Glass (PV-SOG)5       |

| 2.1.1.        | Components in solar inverters6              |

| 2.1.2.        | System design (Inverter Topology)8          |

| 2.1.3.        | Advantages of PV-SOG12                      |

| 2.1.4.        | Design of PV-SOG13                          |

| 2.2. Hi       | gh Voltage Thin Film Transistors (HVTFTs)18 |

| 2.2.1.        | Channel Materials for HVTFTs18              |

|     | 2.2.2.  | Device Structures for HVTFTs                                          | 26 |

|-----|---------|-----------------------------------------------------------------------|----|

| 2.  | .3. Ad  | dvantages of ZnO for HVTFTs                                           | 34 |

|     | 2.3.1.  | Wide Bandgap Materials                                                | 34 |

|     | 2.3.2.  | High Thermal Conductivity                                             | 35 |

|     | 2.3.3.  | Transparency                                                          | 35 |

|     | 2.3.4.  | High Quality Channel Layer at Low Process Temperature                 | 35 |

| 2.  | .4. Re  | eliability issues of ZnO TFTs                                         | 37 |

| 2.  | .5. Su  | ummary                                                                | 39 |

| Cha | apter 3 | Improvement of Stability of ZnO TFTs                                  | 41 |

| 3.  | .1. Ba  | ackground                                                             | 41 |

| 3.  | .2. Fa  | abrication Process and Setup of Electrical Test of Regular TFTs       | 42 |

| 3.  | .3. Th  | ne Effect of Mg-doping on the Electrical and Material Characteristics | 45 |

| 3.  | .4. Ne  | egative Bias Stress (NBS) Stability Result                            | 49 |

| 3.  | .5. Dis | scussion                                                              | 53 |

| 3.  | .6. Su  | ummary                                                                | 56 |

| Cha | apter 4 | MZO HVTFTs on Glass                                                   | 57 |

| 4.  | .1. Ba  | ackground                                                             | 57 |

| 4.  | .2. De  | esign of HVTFTs on Glass                                              | 57 |

|     | 4.2.1.  | Overall design of HVTFTs on glass                                     | 57 |

|     | 4.2.2.  | Symmetric Structure                                                   | 58 |

|     |         |                                                                       |    |

| 4.2.3.    | Fabrication Process of HVTFTs                                  | .62 |

|-----------|----------------------------------------------------------------|-----|

| 4.3. Te   | esting of HVTFTs                                               | .66 |

| 4.3.1.    | Testing Setup                                                  | .66 |

| 4.3.2.    | Definitions of Electrical Parameters                           | .66 |

| 4.4. Ex   | xperimental Results                                            | .67 |

| 4.4.1.    | Transfer Characteristics and Thermal Stability                 | .67 |

| 4.4.2.    | High voltage blocking capability                               | .72 |

| 4.4.3.    | Statistical Data of Electrical Performance                     | .77 |

| 4.5. Di   | iscussion                                                      | .79 |

| 4.5.1.    | The effect of interface engineering on electrical performance  | .79 |

| 4.5.2.    | Effect of interface engineering on blocking voltage            | .80 |

| 4.5.3.    | Analysis of localized electrical field in gate connection area | .83 |

| 4.6. Su   | ummary                                                         | .87 |

| Chapter 5 | Interface Engineering in MZO TFTs                              | .88 |

| 5.1. Ba   | ackground                                                      | .88 |

| 5.2. In   | terface Design and Engineering                                 | .88 |

| 5.3. M    | aterials Characterization                                      | .89 |

| 5.3.1.    | XPS Characterization                                           | .90 |

| 5.3.2.    | TEM/EDS characterization                                       | .90 |

| 5.4. El   | ectrical Characterization                                      | .94 |

| 5.4.1   | . The effect of continuous growth of (MZO-TL) and MZO channel97      |

|---------|----------------------------------------------------------------------|

| 5.4.2   | . Modulation doping of transition layer99                            |

| 5.4.3   | . Effect of MZO-TL Thickness102                                      |

| 5.4.4   | . Gate Leakage Current104                                            |

| 5.5.    | Summary107                                                           |

| Chapter | 6 ZnO Based HVTFTs on Flexible Substrate                             |

| 6.1.    | Introduction109                                                      |

| 6.2.    | Background110                                                        |

| 6.2.1   | . Self-powered wearable electronics110                               |

| 6.2.2   | . Analysis on Flexible Transistors for High Voltage Applications 111 |

| 6.3.    | Fabrication Process of HVTFTs on Flexible Substrates112              |

| 6.3.1   | . Selection of Flexible Substrate                                    |

| 6.3.2   | . Development of Channel Materials113                                |

| 6.3.3   | . Evaluation of Dielectric Layer116                                  |

| 6.4.    | Experimental Results118                                              |

| 6.4.1   | . Fabrication of flexible HVTFT118                                   |

| 6.4.2   | . Electrical Performance and Blocking Voltage119                     |

| 6.4.3   | . Bending Effects on Electrical Performance                          |

| 6.4.4   | . Dynamic Stress Testing on Electrical Characteristics               |

| 6.4.5   | Static Stress Testing on Electrical Characteristics                  |

|         |                                                                      |

| 6.5.      | Summary132                                   | 2 |

|-----------|----------------------------------------------|---|

| Chapter 7 | 7 Conclusion and Suggestions for Future Work | 3 |

| 7.1. (    | Conclusion133                                | 3 |

| 7.2. \$   | Suggestions for Future Work130               | 6 |

| 7.2.1.    | Optimization of HVTFTs on glass136           | 6 |

| 7.2.2.    | Improvement of flexible HVTFTs13             | 7 |

| 7.2.3.    | Development of fully transparent HVTFT13     | 9 |

| 7.2.4.    | Integration of HVTFT towards PV-SOG140       | 0 |

| Referenc  | es142                                        | 2 |

| Major Pu  | blications and Patent Applications14         | 8 |

## Lists of Tables

| Table 4-1 Electrical characteristics of ZnO, MZO, and m-MZO HVTFTs w               | with the |

|------------------------------------------------------------------------------------|----------|

| equivalent channel length L=10µm                                                   | 71       |

| Table 4-2 Voltage-blocking capabilities and output characteristics of              | m-MZO    |

| HVTFTs with three different channel lengths (L=10 $\mu$ m, 15 $\mu$ m, 25 $\mu$ m) | 76       |

| Table 6-1 Corresponding Strain to different radius of the rods                     | 126      |

## List of Illustrations

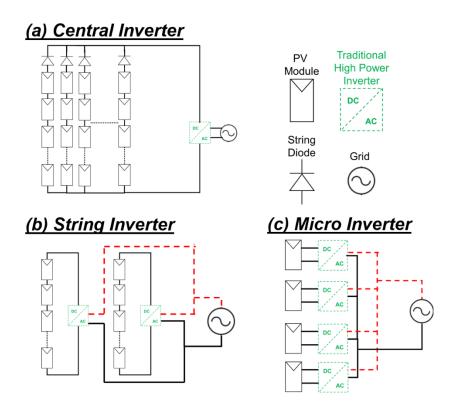

| Figure 2.1. The topologies of current inverters: (a) Central Inverter, (b) String            |

|----------------------------------------------------------------------------------------------|

| Inverter, and (c) Micro Inverter11                                                           |

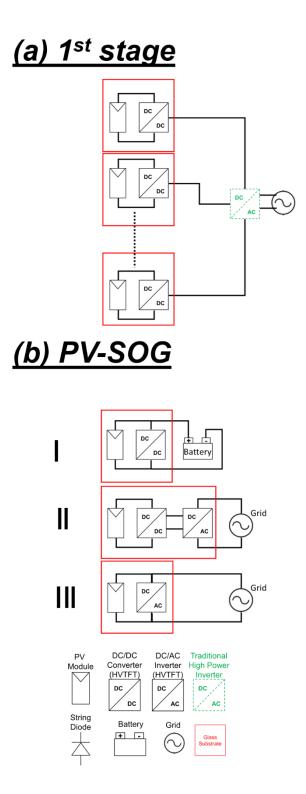

| Figure 2.2 Topology and design of (a) first stage of integration, and (b) PV-SOG             |

| 14                                                                                           |

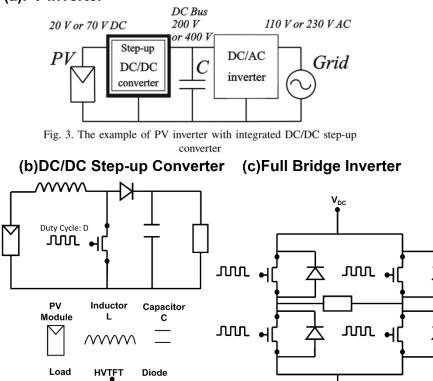

| Figure 2.3 (a) A schematic of a PV system, including a PV cell, a converter, an              |

| inverter, and a grid (b) A circuit of a transformer-less DC/DC converter. (c) A circuit      |

| of a full bridge inverter                                                                    |

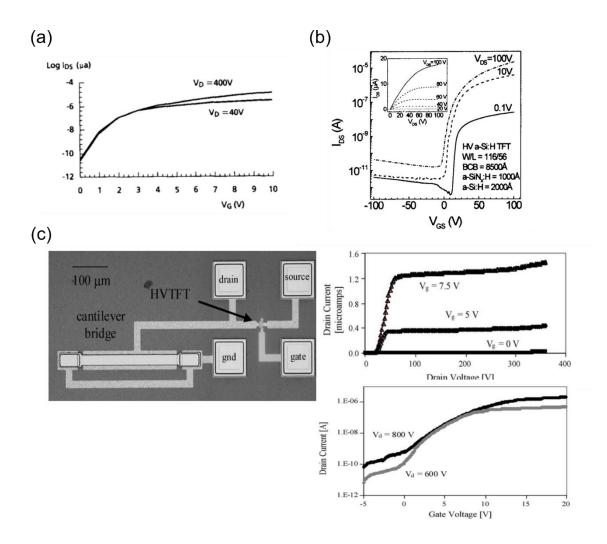

| Figure 2.4 (a) The transfer characteristics of an $\alpha$ -Si HVTFT in early period. (b)    |

| The transfer and output characteristics of $\alpha$ -Si:H HVTFT with a thick double layer    |

| gate insulator. (c) The top-view pictures, transfer and output characteristics of $\alpha$ - |

| Si:H HVTFT which was integrated with MEMS20                                                  |

| Figure 2.5 Electrical Performance of poly-Si HVTFTs. (a) The top-view, transfer              |

| characteristics and leakage current of High-voltage poly-Si TFTs with multichannel           |

| structure. (b) The transfer characteristics and effect of field plate bias on the drain      |

| current of poly-Si HVTFTs with metal field plate21                                           |

| Figure 2.6 Electrical Performance of poly-Si HVTFTs. (a) The transfer and output             |

| characteristics of a dual gate HVTFT with variable doping slot. (b) The transfer and         |

| output characteristics of a poly-Si lateral double diffused metal oxide semi-                |

| conductor (LDMOS) which is fabricated by excimer laser crystallization (ELC).                |

|                                                                                              |

Figure 2.9 (a) Cross-section of symmetric offset gate HVTFT, (b) The relationship between the blocking voltage and offset length in the conventional and implantthrough-contact (ITC) offset gate HVTFT, and (c) The relationship between the ON-current and offset length in the conventional and ITC offset gate HVTFT....

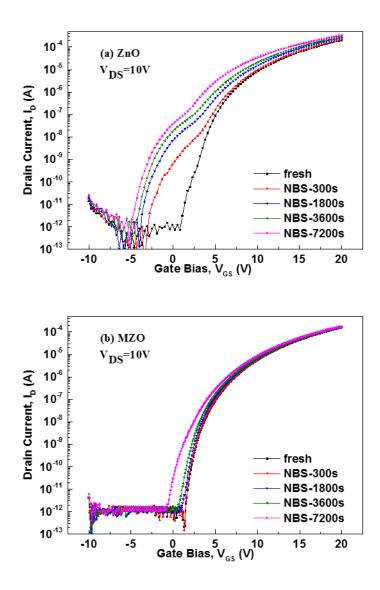

| Figure 3.2 $I_{\text{DS}}\text{-}V_{\text{GS}}$ transfer characteristics of ZnO and MZO TFTs (a) at high drain                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bias condition (V <sub>DS</sub> =10V), (b) at low drain bias (V <sub>DS</sub> =0.1V)47                                                                                         |

| Figure 3.3 (a) XPS spectra (b) TEM pictures, and (c) AFM pictures of pure ZnO                                                                                                  |

| and MZO channel layers48                                                                                                                                                       |

| Figure 3.4. $I_{\text{DS}}\text{-}V_{\text{GS}}$ transfer characteristics of ZnO and MZO TFTs (a) in the                                                                       |

| saturation region ( $V_{DS}$ =10V), (b) in the linear region ( $V_{DS}$ =0.1V)50                                                                                               |

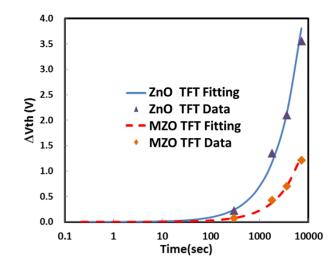

| Figure 3.5. The threshold voltage shift $\Delta V_{TH}$ versus the stress time. The testing                                                                                    |

| results are fitted based on the stretched exponential equation52                                                                                                               |

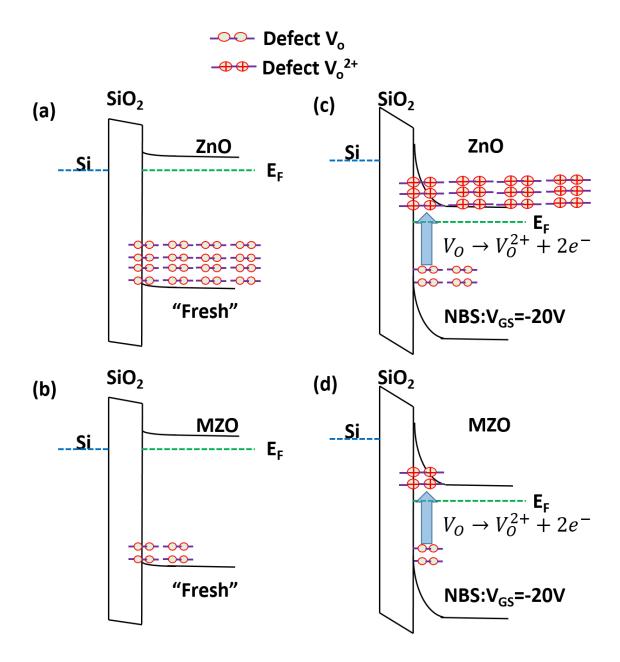

| Figure 3.6. The schematic energy band diagrams of a ZnO TFT (a) at fresh state,                                                                                                |

| (b) under NBS; and of an MZO TFT (c) at fresh state, and (d) under NBS. The                                                                                                    |

| neutral oxygen vacancies are ionized and migrate to the channel/dielectric                                                                                                     |

|                                                                                                                                                                                |

| interface during NBS55                                                                                                                                                         |

| interface during NBS                                                                                                                                                           |

|                                                                                                                                                                                |

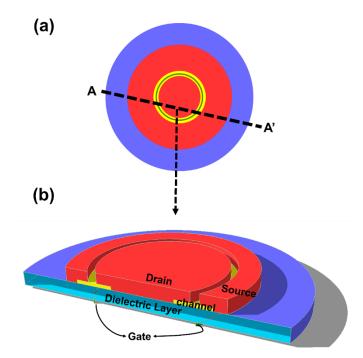

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are                                                                                                   |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure                   |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure along A-A' in (a) |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure along A-A' in (a) |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure along A-A' in (a) |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure along A-A' in (a) |

| Figure 4.1. Schematic diagrams of an MZO HVTFT with a circular structure are shown: (a) the top view and (b) the three-dimensional cross-sectional structure along A-A' in (a) |

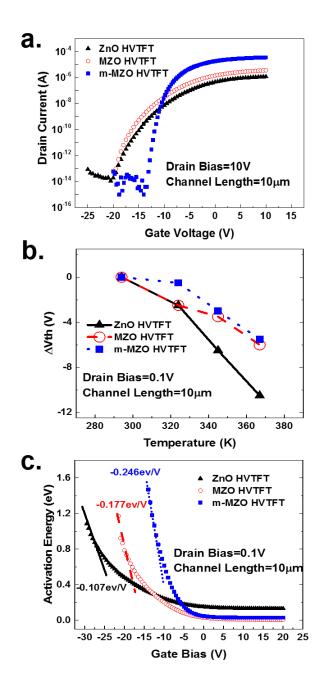

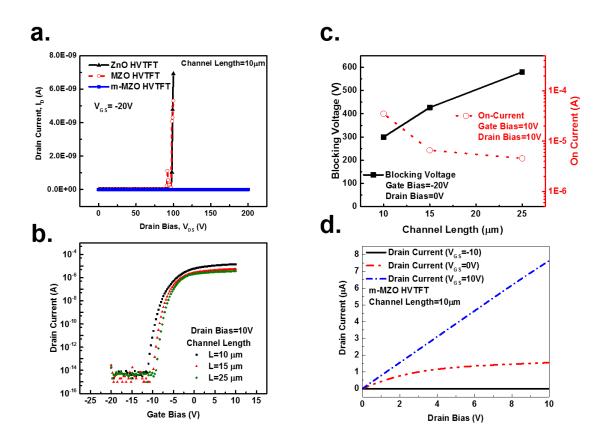

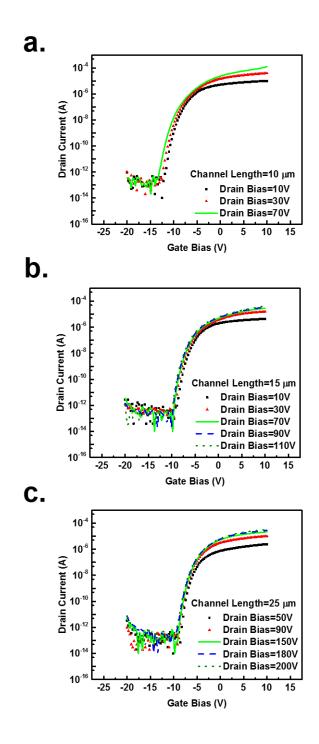

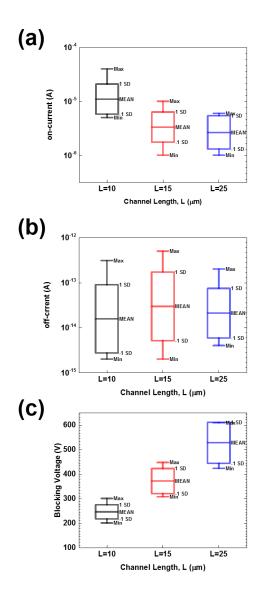

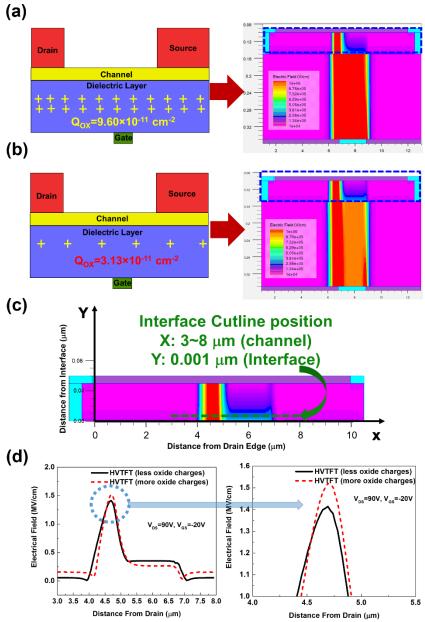

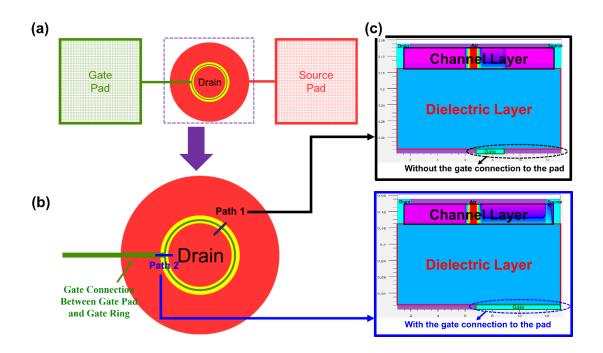

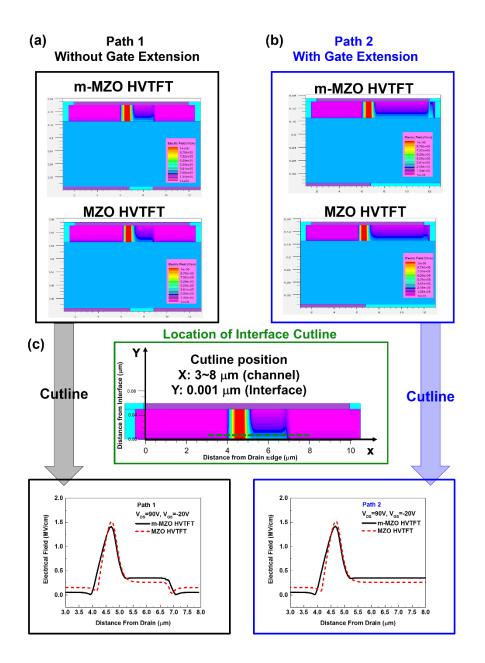

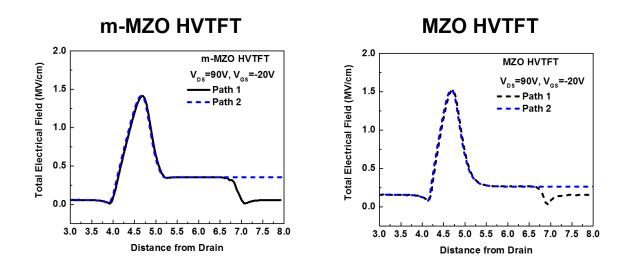

Figure 4.5. The electrical performances of HVTFTs. (a) Transfer characteristics of ZnO, MZO and m-MZO HVTFTs with  $V_{DS}$ =10V. (b) The shift of threshold voltage of HVTFTs at different temperatures. (c) The extracted activation energy of drain current as a function of gate bias in HVTFTs.....70 Figure 4.6. The electrical performances at high bias conditions and the blocking capabilities of HVTFTs: (a) drain leakage current of off state in ZnO, MZO and m-MZO HVTFTs; (b) transfer characteristics of m-MZO HVTFTs with different channel lengths, (c) the channel length dependence of blocking voltage and On current, and (d) the output characteristics of m-MZO HVTFT with a channel length Figure 4.7. The transfer characteristics at high bias conditions of m-MZO HVTFTs Figure 4.8. The statistic data of (a) on-current, (b) off-current, and (c) blocking voltage of the m-MZO HVTFTs with three different channel lengths (L = 10, 15, 15) and 25  $\mu$ m). The error bar provides mean , maximum (Max), minimum (Min), plus one standard deviation (1SD) and minus one standard deviation (-1SD) values. The numbers of data points are taken from 25, 25, and 15 devices with the channel Figure 4.9. Schematic diagrams of different interface designs and layer structures of (a) MZO and (b) m-MZO HVTFT, respectively. (c) The location of cutlines is near the interface of channel/gate dielectric and above the gate edge where the maximum electrical field locates. (d) A comparison of the electrical field of MZO

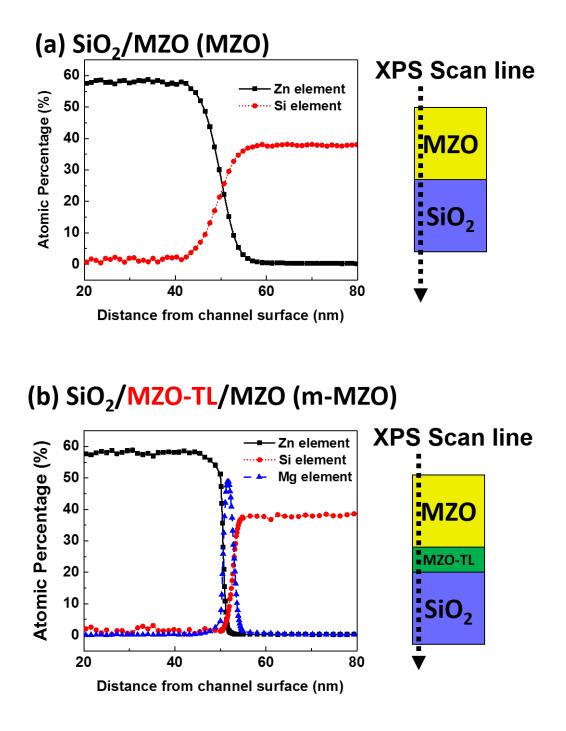

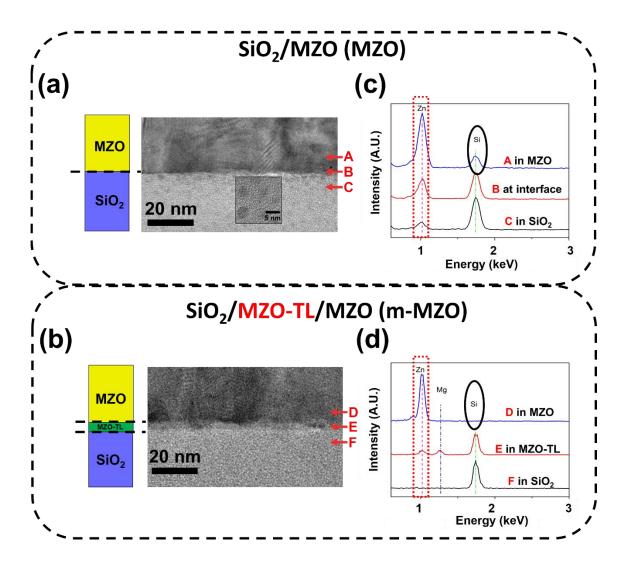

Figure 4.10 The schematics of 2D simulation areas of a HVTFT with and without the gate connection: (a) top-view of the whole device, (b) two simulation paths, Figure 4.11. The simulation results of the electrical field distributions in the channel layers. The comparisons of electrical field distribution between MZO and m-MZO HVTFTs are presented for the configuration: (a) without the gate connection and (b) with the gate connection. (c) The location of 1D cutline. The comparison Figure 4.12 The influence of the gate connection (Path 1: without the gate connection; Path 2: with the gate connection) to the electrical field distribution at Figure 5.1. Depth profiles of atomic percentage of Si, Zn, and Mg from XPS measurements of (a) MZO and (b) m-MZO samples along the scan lines shown in the TEM pictures. The oxygen profile is not included......92 Figure 5.2 TEM images of the interfaces between the channel layer and the SiO<sub>2</sub> dielectric layer (a) without a transition layer (for MZO HVTFT) and (b) with a modulation doped transition layer (for m-MZO HVTFT). The inset of Figure 5.3(a) features the gray dots found in the SiO<sub>2</sub> layer in the MZO sample. EDS spectra of Zn, Mg and Si elements at the different locations (marked in the TEM images) across the channel – gate dielectric interface for (c) MZO and (d) m-MZO samples.

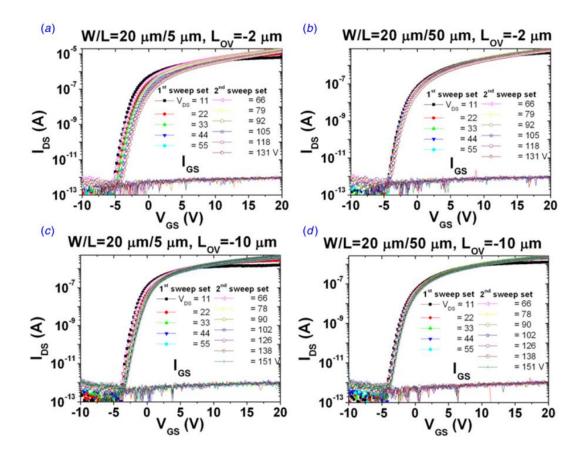

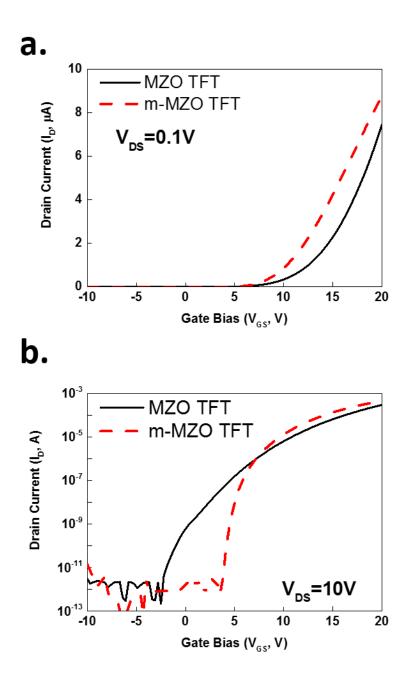

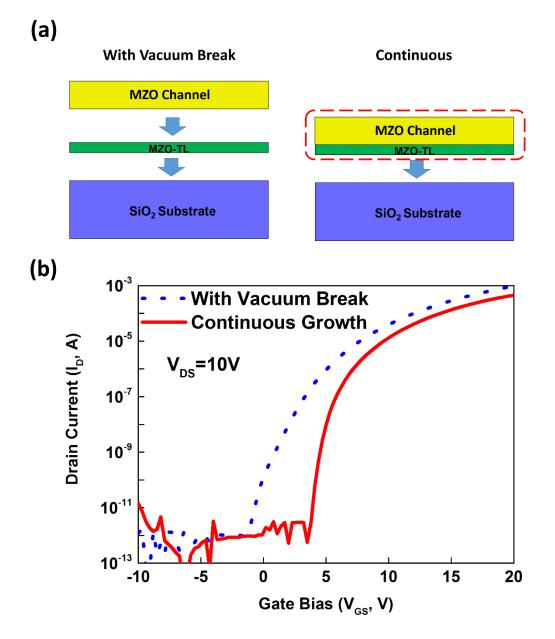

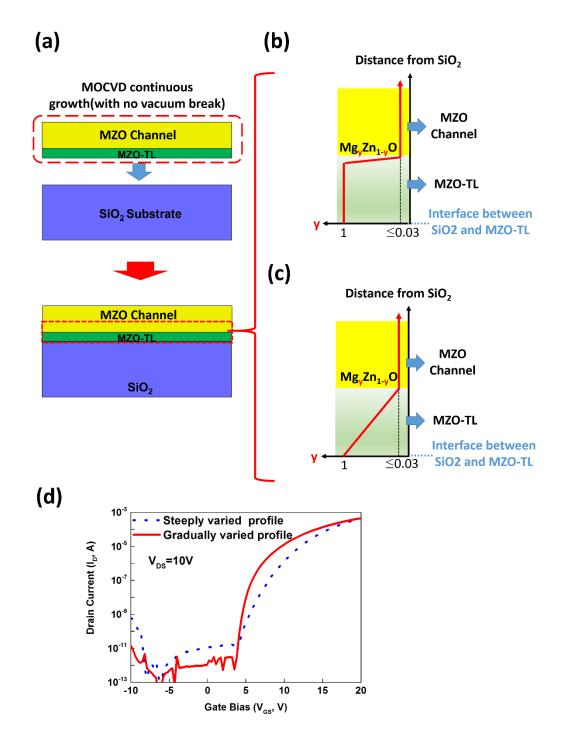

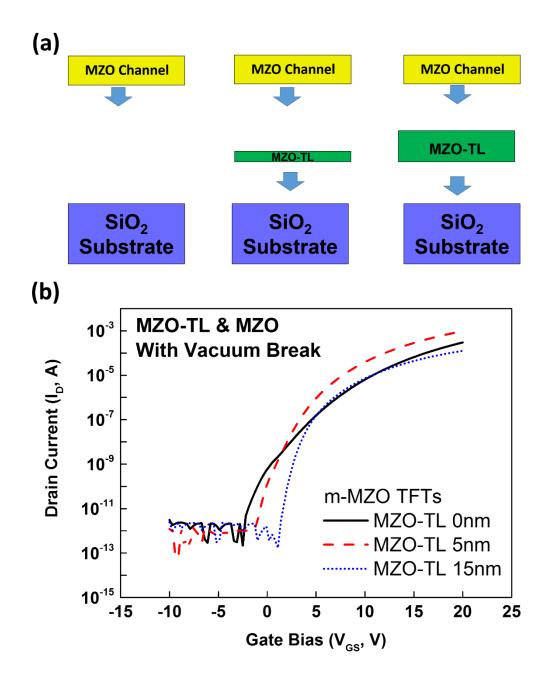

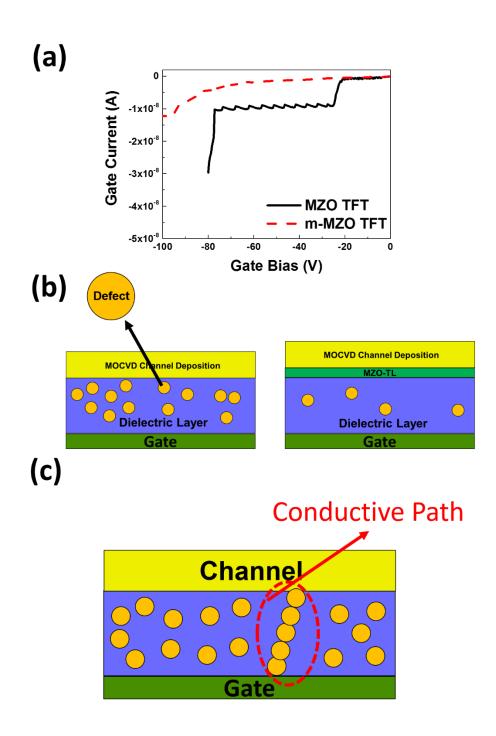

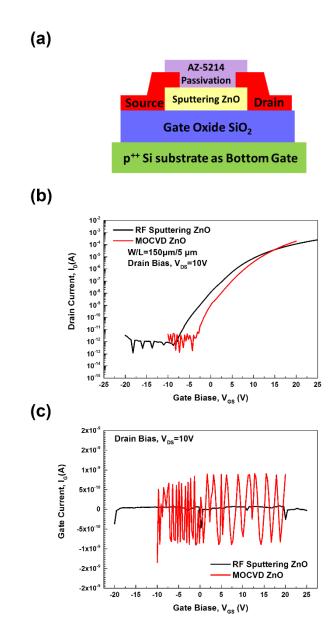

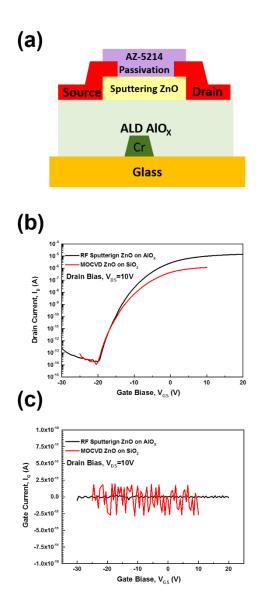

Figure 5.3 Comparisons between the regular MZO TFT and the m-MZO TFT with interface modification: (a) TFT I-V characteristics; (b) the effect of MgO thickness

Figure 5.5 (a) The schematics of adding a transition layer. The schematics of (b) with abrupt Mg profile and (c) with gradually varied Mg doping profile. (e)The Figure 5.6 (a) The schematics of MOCVD growth of different MgO thickness for transition layer. (b) The transfer characteristics of m-MZO TFTs of different Figure 5.7 (a) The comparison of the gate leakage current of MZO and m-MZO TFTs. (b) The schematics of defects distribution in MZO and m-MZO TFTs. (c) The Figure 6.1 (a) The cross-sectional of regular sputtering ZnO TFT. (b)Transfer characteristics of RF sputtering ZnO and MOCVD ZnO TFTs. (c) Gate leakage current of RF sputtering ZnO and MOCVD ZnO TFTs......115 Figure 6.2 (a) a film stack of sputtering ZnO on ALD Al<sub>2</sub>O<sub>3</sub> HVTFT. (b) The transfer characteristics and (c) gate leakage current of MOCVD ZnO/ PECVD SiO<sub>2</sub> and RF sputtering ZnO/ALD Al<sub>2</sub>O<sub>3</sub> HVTFTs. .....118 Figure 6.3 (a) The photo of (b) The transfer characteristics of, and (c) the gate leakage current of the flexible HVTFT on PEN substrate......122

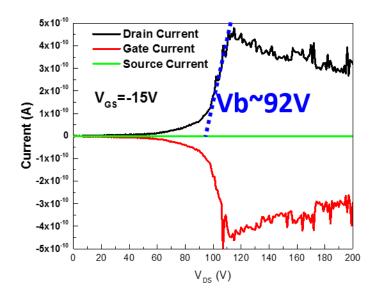

Figure 6.4 The blocking voltage measurement. The drain, gate, and source current are shown at the conditions of drain bias from 0 to 200V and gate bias of -15V.

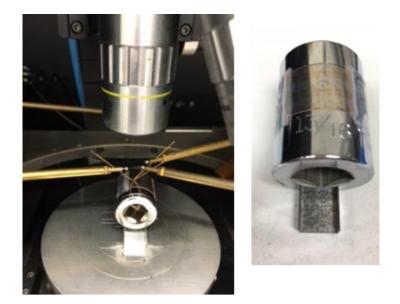

| Figure 6.5 The setup of bending test of flexible HVTFT125                         |

|-----------------------------------------------------------------------------------|

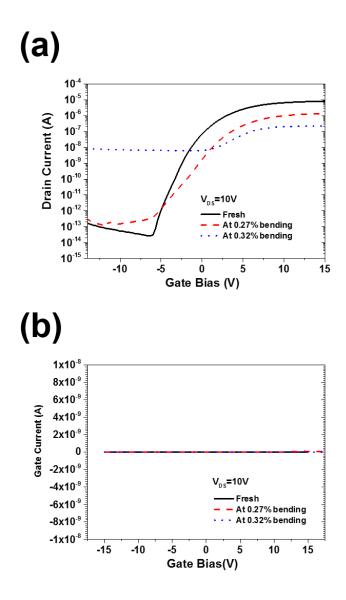

| Figure 6.6 (a) Transfer characteristics and (b) gate leakage current of flexible  |

| HVTFT at different bending status128                                              |

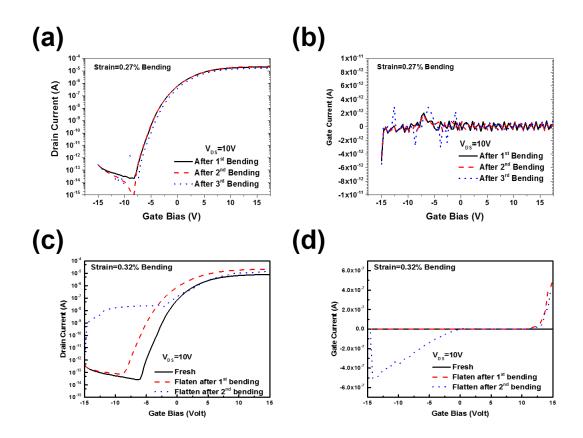

| Figure 6.7 (a) The transfer characteristics and (b) gate leakage current of ZnO   |

| flexible HVTFT at flat status after bending strain of 0.27%. (c) The transfer     |

| characteristics and (d) gate leakage current of ZnO flexible HVTFT at flat status |

| after bending strain of 0.32%130                                                  |

### Chapter 1 Introduction

#### 1.1. Motivation

For decades, solar energy has been a leading technology in searching to replace fossil-fuel energy as a sustainable and clean energy source. However, cost and efficiency remain as major concerns.<sup>1</sup> As the price of photovoltaics (PV) modules has been dropping, the inverters for energy converters now count for more than 10% of the total cost of an entire PV system<sup>2</sup>. Additionally, in a conventional PV system all PV modules link to a central inverter; therefore, the overall system performance can be brought down by an underperforming module in the array or individual solar cells blocked from sunlight.

To solve these problems, and to optimize each individual solar module, the micro inverter technology<sup>3</sup> has been proposed to embed inverters into each photovoltaic module. However, at the present time, the cost of micro inverters is still higher than that of centralized inverters in small systems ( $\leq$ 10 kW)<sup>4</sup>. Another major factor hindering the wide adoption of solar energy is a conflict between aesthetics and energy saving. Many consumers find the placement of solar arrays on buildings to be unsightly. Consequently, the technologies of integrating photovoltaics into buildings, i.e. Building Integrated Photovoltaics (BIPV) have been proposed<sup>5,6</sup>. BIPVs serve as building elements so that the appearance of houses won't be compromised due to the post-installation of solar panels.

To address these three major issues, i.e. efficiency, cost and appearance, we have explored a new type of solar inverter which can be integrated with PV modules to form a solar PV system on glass (PV-SOG). PV-SOG has three major advantages: suitable for mass production of an integrated system, occupying a small unit size, and enabling optimization of a single PV module; therefore, PV-SOG will be promising for many applications, including BIPV and self-powered smart glasses.

For solar inverters, high voltage transistors are essential to multiple functions, including DC/DC converters and DC/AC inverters. Currently, state-of-the-art high voltage and high power devices for the solar inverters use the popular SiC and GaN transistors. However, both of those wide bandgap semiconductors require epitaxial growth at high temperature on the strictly selected single-crystal substrates, which excludes their adoption in SOG. In contrast, TFT technology, which offer the low temperature process, and low material and fabrication cost is particularly beneficial to SOGs. As a result this dissertation research focuses on studies and development of oxide-based high voltage TFT (HVTFT) on glass substrate. The novel MgxZn1-xO (MZO) is used with the interface engineering to serve as the core HVTFT material. The device adopts the unique symmetric design to enable the high blocking voltage. The comprehensive characteristics with computer simulation provide the insight of electrical characteristics.

In addition to HVTFT on glass technology, we have also conducted the feasibility study to expand HVTFT on flexible substrates. As one of the central technologies of Internet of Things (IoT), wearable electronics have attracted increasing interests and broaden applications. It is critical to have more efficient and convenient wearable power components for the wearable electronic systems.

Up to date, in contrast to the well-studied energy harvest technologies, the related power management systems haven't been well established. The research on flexible HVTFT aims to explore its applications in the self-powered wearable electronics.

#### **1.2.** Objectives and Scope of Work

The objectives of this work are to design, fabricate and analyze the prototypes of ZnO-based thin film transistors for high voltage applications. The scope of this dissertation includes:

- Understand and improve the stability, especially Negative Bias Stress(NBS)

Stability of ZnO based TFT through development of a ternary Mg<sub>x</sub>Zn<sub>1-x</sub>O (MZO) to replace the pure ZnO as the channel layer

- Develop the prototype of MZO HVTFT on glass through unique design of the symmetric structure to resolve electric field crowding therefore increase the high voltage operation.

- Develop Interface engineering to resolve the Zn-diffusion introduced degradation of the TFT devices, thus enhance the IV characteristics and blocking voltage of the MZO HVTFT on glass.

- Conduct comprehensive characterizations with the computer simulation to understand the device physics, especially the interface phenomena to improve the design of the MZO HVTFT.

- Explore the flexible HVTFT by development of low temperature fabrication process of HVTFT on the plastic substrate.

#### 1.3. Organization of the Dissertation

After presenting the motivation, scope, and organization of the dissertation in Chapter 1, the basic knowledge and technical information are covered in Chapter The introduction includes background of PV-SOG, current HVTFTs technologies, and materials advantages of ZnO for HVTFT. In Chapter 3, the development of a stable MZO TFTs through material engineering is addressed. After the development of a reliable channel material, the design, fabrication, and characterization of a MZO based HVTFTs on glass through the design of device structures and interface engineering are discussed in Chapter 4. To have better ideas of the critical interface engineering and its related benefits for certain applications, Chapter 5 analyzes the MZO transition layer as a diffusion barrier in detail by utilizing different characterization methods, including XPS, FIB/TEM/EDS, electrical measurement, and oxide electrical breakdown test. To broaden the application of ZnO based high voltage TFT, the HVTFT on flexible substrate using low temperature process is covered in Chapter 6. In Chapter 7, a summary and suggested future work are given.

#### Chapter 2 Technical Background

Energy is one of the most important topics in the 21<sup>st</sup> century, and solar energy has been a leading technology in the search to replace fossil-fuel energy as a sustainable and clean energy source. However, the adoption rate of solar energy is not as high as expected. The cost and efficiency remain as major concerns, and the aesthetic is another important factor affecting popularity of the solar energy technology. In order to provide an energy-efficient, less expensive, and reliable energy source, we present a new concept of photovoltaics on glass (PV-SOG) technology. In this chapter, the introduction of PV-SOG, especially in the solar inverter, is introduced. The advantages and design of PV-SOG are discussed, so are the comparison among potential high voltage device technologies for solar inverter. At the end of the chapter, the advantages and issues of ZnO for high voltage applications are described.

### 2.1. Photovoltaics System on Glass (PV-SOG)

PV-SOG integrates solar cells, solar inverters, and controller circuits on a single glass substrate. This system not only provides optimization of single solar module for high energy efficiency but also enables the easy-integration for implementing building integrated photovoltaics (BIPV). BIPV provides better appearance by integrating photovoltaics technologies with the building, and it even makes photovoltaics become parts of the building fabrics, such as ceiling tile, windows. Moreover, the cost can be significantly reduced through a single fabrication process of system-on-glass. Overall, it addresses three major topics of

solar technology: efficiency, cost, and aesthetical appearance. Because the high voltage devices are only required in the inverter circuits, following introduction focuses on the components in solar inverters.

#### 2.1.1. Components in solar inverters

There are two major tasks of solar inverter circuits: generation of largest power output and provide proper current form into grid and/or energy storage equipment, such as batteries, capacitors. The important components in the solar inverters include maximum power point tracking (MPPT), DC/DC converter, DC/AC inverter, and controller circuits.

Maximum Power Point Tracking (MPPT): MPPT is responsible for tuning the load to maximize the power output of solar modules. The power of a PV module varies due to many reasons, such as the degradation of solar cells, the intensity of sunlight. Through the feedback signal from the PV module like the open circuit voltage, MPPT can vary the operating point of the PV module by adjusting the load to reach the maximum power output. While the PV modules are connected to the batteries in the off-grid system, it is integrated in the DC/DC converter to adjust the output of PV power, so the batteries can be charged efficiently. To improve the efficiency of PV module, MPPT can also be used in conjunction with a mechanical tracking system. By optimizing the face angle the operating point of PV module, the output power of PV system can be maximized.

- DC/DC converter: DC/DC converter can be used to increase or decrease the voltage from the PV modules. Generally, the voltage from PV modules varies from 12 VDC to 70 VDC, and it should be boosted up to the system DC Bus voltage of around 200 VDC or 400 VDC for the grid application of 110VAC or 230VAC<sup>7</sup>. The DC/DC converter also plays an important role to make the PV system robust. While the PV module underperforms, the DC/DC converter can boost up the voltage output, so the following DC/AC inverter can function correctly. For the direct connection between appliances and solar energy, DC/DC converters transform solar energy to applicable DC voltage which can be used directly to drive the appliance, including charging the batteries.

- DC/AC inverter: In order to be connected to the grid, DC/AC inverters are essential to invert DC power from solar cells to AC power for the grid. DC/AC inverter can also be used to amplify the voltage output. There are three popular types of DC/AC inverter circuits: a) With 50/60 Hz transformer(Low Frequency with Transformer, LF-T), b) With HF-transformer (High Frequency with Transformer, HF-T), and c) Transformer-Less (TL).<sup>8</sup> In comparison with the inverters with transformers, TL inverters have following advantages:

- 1. Fewer components, small size, and light weight

- 2. Cost effective and reliable.

- 3. The efficiency is higher (96~98%).

The minimum input voltage of TL inverter has to be larger than 350 VDC. The addition of DC/DC converter (boost-convert) increases the input range; however, the original advantages are slightly sacrificed, such as slightly lower 94% efficiency, slightly heavier weight.<sup>8</sup>

#### 2.1.2. System design (Inverter Topology)

The configuration of PV system affects the overall efficiency and cost tremendously, and the performance varies depending on the circumstance. There are three main categories of inverter topologies: the central inverter, the string inverter, and the micro inverter.

Central Inverter: The central Inverter as shown in the Figure 2.1(a) is the conventional technology that one inverters connects to multiple parallel PV strings. Each string of PV modules generates a sufficient high voltage, so there is no need to use DC/DC converter. It is commonly used in the large systems, such as utility-scale PV power plants, which produce large power (>30kW, up to 1MW). The configuration is simple and provides a great efficiency when every module function correctly. However, the output power may degrade seriously due to the failure or underperformance of one or several PV modules, and it may result from many reasons, such as partial shading, module degradation, dust, bird droppings. The efficiency of whole system will drag down due to the mismatch between PV modules. Moreover, energy loss is introduced by the centralized MPPT which is not optimized for each PV module, extra energy consumption from the addition of string diodes, etc.<sup>9</sup> The requirement of high voltage DC cables is also a

safety concern. Furthermore, the system is bulky, so it lacks of the flexibility to be mounted on different subjects. Furthermore, the large size of PV system can dramatically change the appearance of the mounted subjects, such as houses, and lots of people don't consider that bulky solar panels are aesthetic. The individual design for each installation make the benefits of mass-production cannot be reached. It could be a great bottleneck for the popularization of solar technology.

- String Inverters: A modified topology of inverters aims at improving energy efficiency by introducing separate MPPT for each string, eliminate the loss from string diode. The topology as shown in the Figure 2.1 (b) is that one inverter only connects to a string of PV modules. Since only a string of PV modules share one inverter, the whole system is more robust against the underperformance of individual PV module. However, the inverter still is connected to several PV modules, so the output condition cannot be optimized specifically for each PV module.

- Micro Inverters: This topology addresses the low efficiency issues in central and string inverters. A micro Inverter connects to only one PV module as shown in the Figure 2.1 (c), so a MPPT can be dedicated to each PV. Also, the solar tracker can be more effective because it only need to consider a single PV module. Overall, the topology of micro inverters can help each PV module to generate maximum power output. Moreover, this topology can make the unit size of PV system smaller, so it provides the flexibility to be utilized on many different applications, such portable devices<sup>10–12</sup>, self-

power smart window<sup>13</sup>. Although the customized MPPT for each module produce maximum power output, micro inverter may still suffer from high cost per watt. Because a single PV module cannot provide high output voltage for grid connection, the micro inverters are needed for the high voltage amplification. The high voltage amplification usually is a low efficiency conversion<sup>7</sup>. As a result, the cost of micro inverters is still higher than the cost of centralized inverters in small systems ( $\leq 10$  kW)<sup>4</sup>.

**Figure 2.1.** The topologies of current inverters: (a) Central Inverter, (b) String Inverter, and (c) Micro Inverter.

#### 2.1.3. Advantages of PV-SOG

In respect of manufacture cost, the configuration of SOG can help to reduce the overall cost. In addition to inverters, all other components including solar cells and controller circuits are designed using the same process, so the mass production of all components on the same product line can be achieved. This integration process also makes unit size of PV-SOG smaller, and it gives the installation of PV system more flexibility. As a result, it has better opportunities to conquer the limitation of space for absorbing solar energy. In respect of energy efficiency, the MPPT is dedicated to one PV module In a PV-SOG, so the output power can be maximum. The reduction of the external connection can cut down the energy loss from the power dissipation of power lines. Overall, PV-SOG can absorb more solar energy and deliver more electric energy than traditional topologies of inverters.

In terms of maintenance and lifetime, since every PV module is integrated with an individual inverter, it is easier to monitor and maintain every PV-SOG. Although the lifetime of individual PV module is the same, the lifetime of overall PV system can extended because of the easiness of repair or replacement of the individual broken PV-SOG.

Last but not least, the glass substrate makes PV-SOG more transparent than conventional system with bulky inverters. Because of the transparency and the small unit size, PV-SOG makes minor changes the effect on the appearance of mounting substrate minimized. Therefore, it is suitable for the application to BIPVs.

#### 2.1.4. Design of PV-SOG

The design of PV-SOG is shown in the Figure 2.2(a), and the development will be divided into two phases. At the first stage as shown in the Figure 2.2 (a). we will would like to use HVTFT in the DC/DC converters. By integrate DC/DC converters directly with PV modules, each system on glass can provides high and stable voltage output for the following centralized DC/AC inverters. Through this integration, the output efficiency of each solar pane can be optimized. Later, we can further apply HVTFT in the DC/AC inverters to form a real PV-SOG as shown in the Figure 2.2 (b). It requires a high frequency operation to produce a better pseudo-sinusoidal output; therefore, the deeper understanding and improvement the AC performance of HVTFT are necessary. By integrating all components of solar inverters, the benefits of PV-SOG mentioned in previous section can be fulfilled. For different applications, such as different amount of sunlight exposure, the configuration of PV-SOG can be modified. If the system is for charging batteries, it only requires an integrated DC/DC converter. If the PV module can provide high DC output, the system only requires a DC/AC inverter for the connection to the grid. On the other hand, if the PV module can only provide low DC output, both a DC/DC converter and a DC/AC inverter are necessary for PV-SOG.

Figure 2.2 Topology and design of (a) first stage of integration, and (b) PV-SOG

As shown in the Figure 2.3(a), the output voltages of DC/DC converters are 200 VDC and 400 VDC for the grids of 110 VAC and 230 VAC, respectively<sup>7</sup>. In order to be utilized in the inverters, our target of blocking voltage of 300V and 600V for the system of 110V and 230V AC system, respectively. One of the major goal of this proposal is to apply PV system on glass to the mobile applications. For these application, low stand-by power consumption is critical; therefore, we seek to lower the off leakage current. On the other hand, in order to be operated at higher frequency, a better on-state performance is also important. Therefore, a large ON/OFF current ratio is the main goal.

For the design of DC/DC converter, in order to be integrated on a substrate glass substrate, a bulky transformer is unwanted. Therefore, we would like to adopt transformer-less boost-up circuit as shown in the Figure 2.3(b) for the PV-SOG where HVTFTs are used as the switch. The transformer-less converter use inductors and/or conductors without using bulky transformer to generate voltage gain, and the gain only depends on the duty cycle in continuous boost-up circuit. The ideal gain of boost-up circuit is based on the equation (2.1):

$$Gain = \frac{V_O}{V_i} = \frac{1}{1 - D}$$

(2.1)

By changing the input signal to the HVTFT, the gain changes. However, when the amount of energy stored in the inductor cannot provide continuous current during the OFF period, the circuit operates in the discontinuous mode. Unlike in the continuous mode, the gain in the discontinuous mode is lower and affected by the inductor value, the input voltage, the commutation period, and the output current. For the design of the DC/AC inverter, a circuit of the full bridge (H bridge) inverter as shown in the Figure 2.3(c). By using pulse width modulation, it can transform the DC signal into AC sinusoidal signal. While the frequency is 1 kHz, the output signal is still choppy. If the frequency reaches 16 kHz, the wave form will be very close to sinusoidal wave<sup>8</sup>. HVTFTs will be used as the 4 switches indicated in the figure. As a result, the DC/AC inverter requires the switches have great performance at higher frequency.

## (a)PV inverter

•[

夲

**Figure 2.3** (a) A schematic of a PV system, including a PV cell, a converter, an inverter, and a grid<sup>7</sup> (b) A circuit of a transformer-less DC/DC converter. (c) A circuit of a full bridge inverter.

#### 2.2. High Voltage Thin Film Transistors (HVTFTs)

For the solar inverters, high voltage transistors are essential to several applications, including DC/DC converters, DC/AC inverters. As mentioned in previous chapter, state-of-the-art high voltage and high power devices, such as SiC, GaN transistors for the solar inverters are not compatible with PV-SOG because these devices require epitaxial growth at high temperature on strictly selected single-crystal substrates. As a result, TFT technology, which has low process temperature and fabrication cost, is compatible and beneficial for SOGs. As a result, here we only focus on the high voltage TFTs.

#### 2.2.1. Channel Materials for HVTFTs

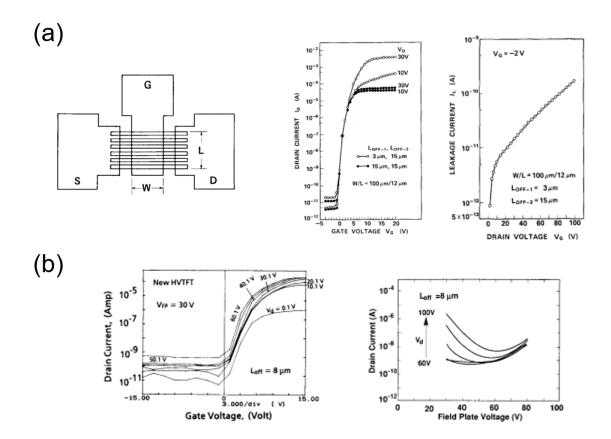

Several semiconductor materials have been tried out to make HVTFT devices. Amorphous Si<sup>14</sup> and poly-Si<sup>15</sup> HVTFTs have been studied since the 1980s<sup>16–18</sup>. For the part of amorphous Si HVTFT, in early period (1993), Martin et al.<sup>19</sup> already demonstrated an amorphous Si TFT as shown in Figure 2.4(a) can sustain operating voltage of 400 V with drain offset structure. However, the on/off ratio was only around 5 orders. In 1999, Nahm et al.<sup>20</sup> demonstrated a  $\alpha$ -Si: H HVTFT with thick double layer gate insulator for reflective active-matrix cholesteric liquid crystal displays. The on/off ratio reached 6 orders and ON-current reaches 10  $\mu$ A at V<sub>DS</sub>=100V as shown in Figure 2.4(b); however, the operating voltage only reached 100V. Chow et al. demonstrated an amorphous Si TFT could provide high blocking voltage up to 800 V<sup>21</sup> using input voltage 0~20V, and it was integrated with MEMS-- a cantilever bridge in Figure 2.4(c). Although the fabrication of amorphous Si TFTs could be at low temperature (<400°C), its poor performance

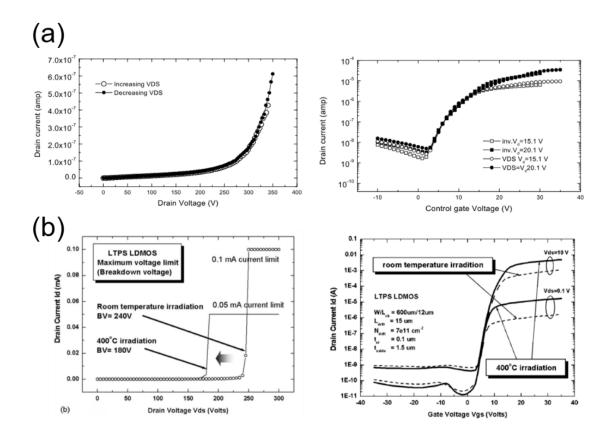

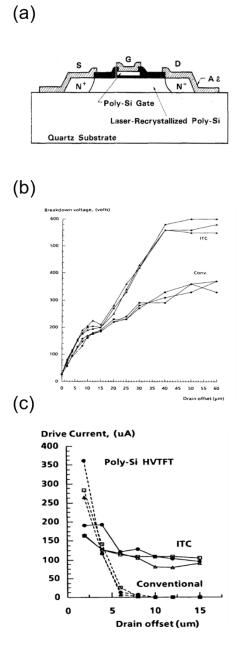

(on/off ration~10<sup>4</sup>) limited its application. For the part of Poly-Si HVTFTs, in 1988 Unagami<sup>22</sup> demonstrated High-voltage poly-Si TFTs with multichannel structure in Figure 2.5(a). The devices had high on/off ratio of 7 orders. However, the blocking voltage was only around 130V, and the fabrication temperature of 670°C could be risky for some regular glass substrates, not to mention flexible substrates. In 1990, Huang et al.<sup>23</sup> designed poly-Si HVTFTs with metal field plate in Figure 2.5(b), and the current-pinching effects result from offset region was alleviated, but the blocking voltage was still around 100V. In 2002, Krishnan et al.<sup>16</sup> demonstrated a dual gate HVTFT with variable doping slot in Figure 2.6(a) which has a blocking voltage in excess of 300V. However, the on/off ratio was limited around 4~5 orders, and the fabrication process could be complicated due to control of doping profile. Furthermore, the process temperature reached 600°C which could be a concern for regular glass substrate. In 2004, Cheng et al.<sup>24</sup> utilized excimer laser crystallization (ELC) to fabricate poly-Si lateral double diffused metal oxide semiconductor (LDMOS). As shown in Figure 2.6(b), the blocking voltage reached 240V, and on/off ratio was 1.23×10<sup>6</sup>. However, the process temperature kept as high as 600°C, and the expansive laser annealing made TFTs have poor uniformity especially in the large area applications. Overall, poly-Si HVTFTs show better driving capability, but their low blocking voltage and non-uniformity from grain boundaries make them inadequate to meet the requirements of PV-SOG. In addition, all Si-based TFT technology suffers from the absorption of visible light, restricting its application for transparent electronics.

**Figure 2.4** (a) The transfer characteristics of an  $\alpha$ -Si HVTFT in early period<sup>19</sup>. (b) The transfer and output characteristics of  $\alpha$ -Si:H HVTFT with a thick double layer gate insulator<sup>20</sup>. (c) The top-view pictures, transfer and output characteristics of  $\alpha$ -Si:H HVTFT which was integrated with MEMS <sup>21</sup>.

**Figure 2.5** Electrical Performance of poly-Si HVTFTs. (a) The top-view, transfer characteristics and leakage current of High-voltage poly-Si TFTs with multichannel structure<sup>22</sup>. (b) The transfer characteristics and effect of field plate bias on the drain current of poly-Si HVTFTs with metal field plate<sup>23</sup>.

**Figure 2.6** Electrical Performance of poly-Si HVTFTs. (a) The transfer and output characteristics of a dual gate HVTFT with variable doping slot<sup>16</sup>. (b) The transfer and output characteristics of a poly-Si lateral double diffused metal oxide semi-conductor (LDMOS) which is fabricated by excimer laser crystallization (ELC)<sup>24</sup>.

Due to the restriction of Si-based TFT, people started working on new semiconductor materials for high voltage TFT. Organic materials and oxide semiconductor are the most popular candidates. Organic TFTs which offer low cost and low process temperature have been used in display and RFID technologies. Recently, Smith et al.<sup>25</sup> reported a high-voltage organic thin-film transistor (HVOTFT), which showed switch drain-to-source voltages higher than 300 V with a controlling voltage range from 0 to 20 V in Figure 2.7. However, its low mobility, poor long-term stability basically excluded its application in PV-SOGs, which operate under sunlight radiation, and its lifetime, like the regular residential solar cells, is expected to be more than 25 years<sup>5</sup>.

Since Nomura et al<sup>26</sup> demonstrated Indium Gallium Zinc Oxide (IGZO) TFTs with high electrical performance at low process temperature, oxide semiconductor TFTs have emerged in many applications, especially in displays, and transparent electronics. In the area of HVTFT, Jeong et al.<sup>27</sup> reported an IGZO HVTFT in Figure 2.8 which operated at above 100 V with an ON/OFF current ratio of 10<sup>7</sup>. Although this is beyond the regular operating voltage in regular TFTs, it is still not sufficient to be used in inverters for a solar PV system. Furthermore, it is desired to use indium-free materials due to the high cost of indium, especially in the case of large-area electronic systems such as solar cells. In addition, the toxicity of IGZO due to its high indium concentration is of considerable environmental concern.

**Figure 2.7** (a) The output characteristics of a single HVOTFT. (b) Output current of a inverter circuit built by HVOTFT.<sup>25</sup>

**Figure 2.8** The transfer characteristics of an IGZO HVTFT of different dimensions<sup>27</sup>.

#### 2.2.2. Device Structures for HVTFTs

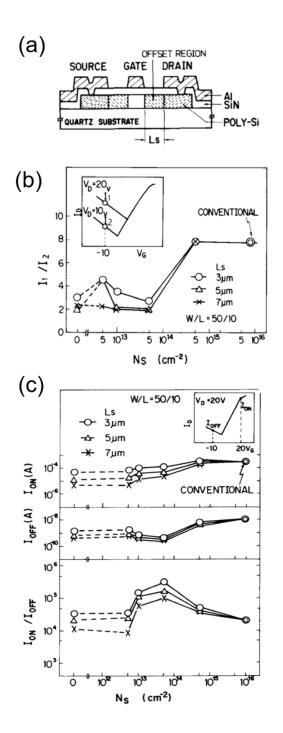

In 1982, Unagami et al.<sup>15</sup> demonstrated the symmetric offset region as shown in Figure 2.9(a) to prevent large potential (drain bias) across the gate dielectric and gate-induced junction breakdown. These offset regions could smooth the distribution of electrical field, so the peak of electrical field would be reduced. As a result, the devices could operate in the condition of the higher bias. As shown in Figure 2.9(b), devices with a longer offset showed higher blocking voltage, no matter what the methods of fabricating the offset structure were used. However, these offset regions were high-resistive regions, so the driving capability of device was impaired as shown in Figure 2.9(c). Also, the high resistive offset area resulted in current crowding.

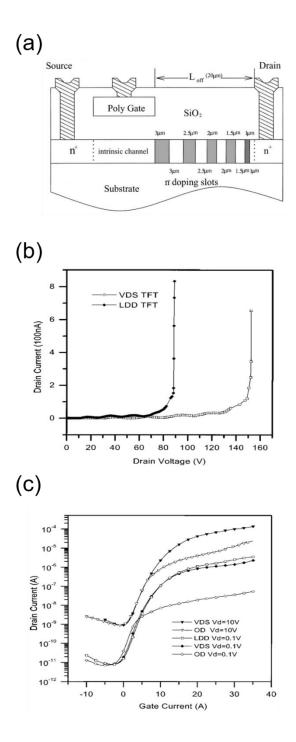

In 1988, Tanaka et al.<sup>28</sup> used lightly doped drain (LDD) ion implantation to increase the conductivity of offset regions as shown in Figure 2.10(a). By adjusting the dopant concentration, the on/off ratio improved more than an order. However, this LDD also weakened the blocking capability of HVTFT, and the control of low doping profile was hard due to the "dopant segregation" effect<sup>17</sup>. Also, the devices with LDD suffered a severe current pinching phenomenon and reproducibility problems. The relationship between blocking capability and performance of ON state was still a trade-off.

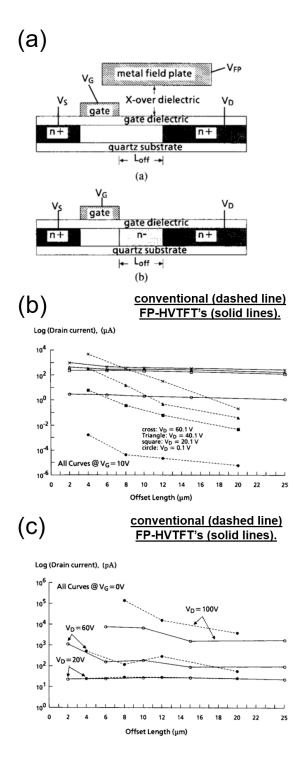

To break this trade-off between blocking capability and ON-current, Martin et al.<sup>29</sup> and Huang et al.<sup>23,30</sup> added an independently biased metal field plate (MFP) overlapping partially or entirely the offset area as shown in Figure 2.11(a). When HVTFT was in the ON-state, the MFP bias (V<sub>FP</sub>) could increase the conductivity of

the offset area, so the effect of increases of offset length on the ON-current was minimized as shown in Figure 2.11(b). Under OFF-state (blocking voltage), MFP bias (V<sub>FP</sub>) could suppress the leakage current as shown in Figure 2.11(c). Therefore, the on/off ratio improved. Moreover, MFP technology also lowered the dependence of ON-current and leakage current on the offset length, so it made devices more immune to misalignment error. Although MFP made a better balance between blocking capability and ON-current, it required an extra electrode and twosteps dielectric deposition. Moreover, the operating points of MFP bias required optimization based different drain bias. As a result, it increases not only the cost but also the complexity of the circuit design, and it is not compatible with regular device processing.

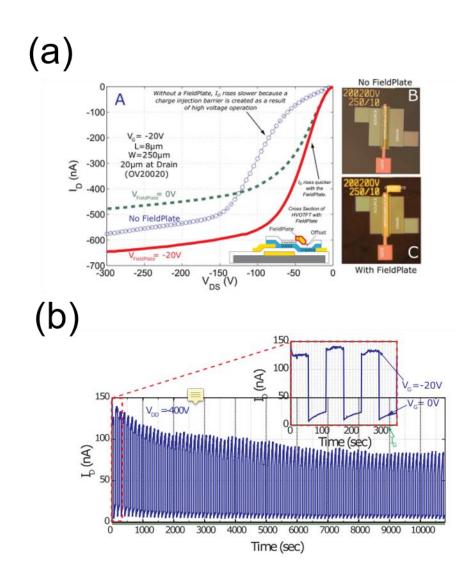

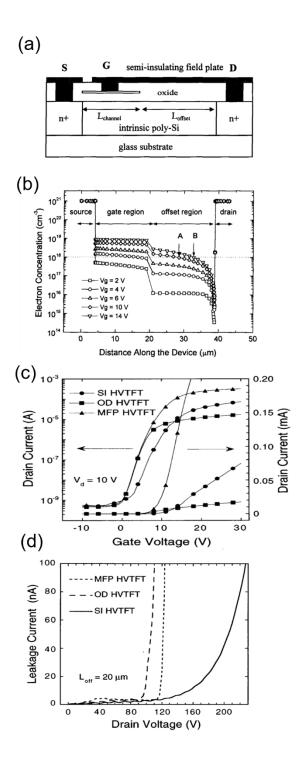

In 1996, Chen et al.<sup>31–33</sup> invented a Semi-Insulating (SI) field plated High Voltage TFT as shown in Figure 2.12(a). The SI field plate connected from the gate to the drain reduced the effective offset in the ON-state, and in the OFF-state it still kept the function of offset region as shown in the Figure 2.12(b). Therefore, the SI HVTFT had better performance in both blocking capability and on-state performance of HVTFT as shown in the Figure 2.12 (c) and (d) respectively. Although higher conductivity of SI field plate could improve the switching speed in the ON-state, it was limited to restrict the leakage from SI field plate at low level in the OFF state.

In 2002, Xu et al.<sup>17</sup> proposed a new method: variable doping slots (VDS) as shown in the Figure 2.13(a) in the offset region to improve the performance. As shown in Figure 2.13(b) and(c), VDS devices showed better transfer

characteristics and blocking voltage than LDD device and offset-drain device. However, VDS still required precise control of doping profile to avoid electrical field crowding, and the extra implantation was costly.

**Figure 2.9** (a) Cross-section of symmetric offset gate HVTFT<sup>15</sup>, (b) The relationship between the blocking voltage and offset length in the conventional and implant-through-contact (ITC) offset gate HVTFT<sup>34</sup>, and (c) The relationship between the ON-current and offset length in the conventional and ITC offset gate HVTFT. <sup>35</sup>

**Figure 2.10** (a) cross-section of LDD dopant offset TFT, (b) the effect of doping concentration on the leakage current increasing rate with drain bias, and (c) the effect of doping concentration on on/off ratio <sup>28</sup>

**Figure 2.11** (a) Cross section of FMP HVTFT in comparison with the regular gate offset HVTFT, the effect of the bias of metal field plate on the (b) ON-current, and (c) the OFF-current with different offset lengthes. <sup>30</sup>

**Figure 2.12** (a) Cross section of SI HVTFT in comparison, (b) the effect of the gate bias on the effective offset lengthes, the comparison of (c) On-state performance , and (d) the blocking voltage between SI, OD, and MFP HVTFTs. <sup>31</sup>

**Figure 2.13** (a) Cross section of VDS HVTFT in comparison, (b) the comparison of blocking voltage ce between VDS and LDD HVTFTs, and (c) the comparison of On-state performance between VDS and LDD HVTFTs.<sup>17</sup>

#### 2.3. Advantages of ZnO for HVTFTs

In last decades, ZnO has been widely studied as an electrical, optoelectric, piezoelectric materials, and people has applied it to different kinds of devices, such as varistors, thin film transistors, memory. Therefore, the fabrication process of ZnO based devices are developed and optimized well, and some technologies, such as IGZO TFTs are even commercialized to mass production. These well-developed technologies can speed up the development of ZnO based HVTFT. Moreover, ZnO material possesses following important features which are critical to the application of high voltage active devices.

#### 2.3.1. Wide Bandgap Materials

Although the maximum breakdown field measured in the experiment is affected by the defects, composition mismatch and measurement erros<sup>36</sup>, the theoretical breakdown field of a material is strongly related to the intrinsic energy bandgap. ZnO, a wide energy bandgap materials, has high electrical breakdown field. For the junction breakdown, several literatures indicated the direct relationship between energy bandgap and blocking voltage.<sup>36,37</sup> Ideally, ZnO has breakdown electrical field of  $2 \times 10^6$  V/m which is almost ten times larger than Si (0.3×10<sup>6</sup> V/m) <sup>38</sup>. For transverse electric field, ZnO materials can sustain high electric field, So it is the major materials used in the varistors for surge protection. For longitudinal electric field, Zhang et al. reported that the single crystalline ZnO nanowires can sustain electrical field of level of  $10^6$  V/m<sup>38</sup>.

#### 2.3.2. High Thermal Conductivity

For a high voltage or high power device, it's very critical to dissipate heat from the devices. Using materials of high thermal conductivity can prevent the accumulation of heat, so the related failure, such as joule heating can be alleviate. The thermal conductivity of ZnO is 1~1.4 (W/cm-K) which is as high as Si (1.5 W/cm-K)<sup>39</sup>. Although it cannot compared with the supreme thermal conductivity of SiC (5 W/cm-K), it is at the same level as GaN (1.3 W/cm-K)<sup>40</sup>.

#### 2.3.3. Transparency

As a wide bandgap material, ZnO is a transparent materials which does not affect the appearance of the substrate. By building ZnO on transparent substrates, it is easier to develop the transparent electronic devices. As mentioned in the previous paragraph, the aesthetic appearance plays an important role on the adoption rate of solar technology. If the PV system can be transparent, it won't affect the appearance of mounting surface. As a result, transparent PV system will be very suitable for the application of BIPV.

#### 2.3.4. High Quality Channel Layer at Low Process Temperature

Currently, the state-of-the-art high voltage and high power devices use the popular SiC and GaN transistors. However, both of these wide bandgap semiconductors require epitaxial growth at high temperature on strictly selected single-crystal substrates, which excludes their application in SOGs. In contrast, TFT technology made at low temperature is a more suitable candidate for PV-SOGs. In order to fabricate devices on large area substrate, the fabrication process has to be compatible with large and low-cost substrates, such as regular glass

which cannot sustain higher temperature. Si based materials are most popular in the TFT technologies. Poly-Si TFTs show its advantages over  $\alpha$ -Si: H TFTs in mobility (~100 cm<sup>2</sup>/V-s) because of large crystal size in poly crystalline film. However, the unpredictable distribution of grain boundaries of poly crystalline form result in poor uniformity of device performance. Therefore, in the case of covalent semiconductors, such as Si, the uniformity and performance are the trade-offs.

To solve issues in Si based TFT, many alternative materials for the channel in TFT are studied, and it can be divided into two major directions: low cost and higher performance. In the area of pursuing low cost TFTs, the organic TFTs (OTFTs) are proposed to replace  $\alpha$ -Si: H TFTs because of the low cost growth methods such as spin-coated, printed, or casted on the substrate at room temperature without using vacuum equipment. However, the stability will be the major concern for OTFT.<sup>41</sup> In the area of the high performance TFT, ionic oxide TFTs attract lots of attention in recent years. In the conventional Si-based semiconductor materials, the carrier transport paths by "sp3" orbital are strongly directive, so the disorder in the crystalline structure will degrade the mobility seriously. However, in the ionic oxide semiconductors, such as ZnO have the carrier transport paths through less-directive "s" orbital contributed by posttransition metal cations, so the disorder effect on the carrier transportation is minimized. As a result, ionic oxide semiconductors have higher carrier mobility in less-crystalline structure than covalent semiconductors do.<sup>26</sup> Since ionic oxide semiconductors have the mobility (10~100 cm<sup>2</sup>/V-s) in less-crystalline structure, it can have the high mobility without sacrificing the uniformity in the amorphous form

36

or nano-crystalline form. As a result, oxide TFT make a good balance between better uniformity (amorphous Si TFT) and higher mobility (poly-Si TFT).

Meanwhile, the low order crystalline of the film can be achieved at a lower growth temperature, so the high performance oxide semiconductor transistors can be built at a lower process temperature. This opens the possibility of building the high performance transistors on the low-temperature substrates, such as normal glasses, polymer substrates, and flexible substrates. It is very critical to the novel TFTs applications, such as portable electronics, flexible electronics, and wearable electronics.

In application of PV-SOG, the HVTFTs is built on a glass substrates, and the deformation of regular glasses is around 650°C. If the high temperature process is used, the expensive quartz substrates are required. As mentioned in previous sections, we are targeting the reduction of cost for the large application. As a result, the process temperature should be controlled below 600°C.<sup>42</sup> In fact, in this study, our highest process temperature was only 400°C.

#### 2.4. Reliability issues of ZnO TFTs

The stability of TFTs plays an important role in the practical application. As an infrastructure, solar technology has a strict standard of 25-year life time. As core components in solar energy system, solar inverters also have a high request on the devices.

The reliability issues in ZnO TFTs are more complicated than Si-based TFTs because ZnO consists of more types of defects from two elements: Zn and O. The most abundant native defects to be Zn or O vacancies depends on the growth

condition, and different growth conditions result in differences in chemical stoichiometry.<sup>43</sup> In the study of ZnO based TFTs, it is believed that the native defects in the ZnO based channel layer have a great impact on the device characteristics, including field effect mobility, on-off ratio, subthreshold swing, and bias stress stability<sup>44</sup>. Based on the first principles calculation, the oxygen vacancy in ZnO has the lowest formation energy<sup>45</sup> among the donor like defects. Because oxygen vacancy is a deep state in the n-type ZnO, it is generally in the neutral state. (Vo). However, in the several circumstances, it still strongly affect the conductivity of the channel.

First, under negative gate voltage, a depletion region is created in the TFT channel. In the depletion region, the fermi level approaches toward valence band minimum, the electrons in the deep state (V<sub>0</sub>) can be excited and released into the conduction band. Because V<sub>0</sub><sup>+</sup> is thermodynamically unstable, V<sub>0</sub><sup>2+</sup> is the preferable state. These electrons released from oxygen vacancies would increase the conductivity of channel and affect the stability of ZnO TFTs. Second, this instability will be worse at a higher temperature while the thermally excited oxygen atoms release from original sites and create vacancies. <sup>46</sup>

The inverters block the voltage at OFF status, and it requires negative gate bias to deplete the ZnO channel. Therefore, the HVTFT will majorly operate under negative gate bias. Meanwhile, due to the heat induced by long time exposure to sun light, the operating temperature of solar technology is usually higher. This high temperature will be a great challenge to ZnO HVTFT.

#### 2.5. Summary

In the chapter, we presented the technical background of the high voltage transistors for solar inverters. The basic introduction of solar energy system is described, including the importance of solar inverters, topologies, and components in the solar inverters. To promote the popularity of solar technologies, several solar applications have emerged, such as BIPV, smart glass. We proposed a concept of PV-SOG suitable for these applications and defined the requirement of HVTFT for PV-SOG.

The previous works of HVTFTs were reviewed. Up to date, most studies have focused on devices using Si materials, including amorphous Si and polycrystalline Si. In order to optimize the trade-off between the ON-current and blocking capability, several device structures and process methods were developed, including symmetric offset gate, LDD dopant offset, FMP, SI, and VDS. However, existing Si based HVTFT technologies are not suitable for PV-SOG due to the intrinsic limitation of Si, such as small bandgap, and poor electrical performance at low crystalline form.

To solve these issues, we studied a wide bandgap oxide semiconductor ZnO as the candidate for HVTFTs in PV-SOG. ZnO has intrinsic advantages, such as large bandgap and good thermal conductivity, promising for high voltage operation. In particular, ZnO keeps relatively high electrical performance even at low crystalline form. Moreover, the Indium-free feature makes ZnO price competitive in comparison with other oxide materials, such as In-Ga-Zn-O (IGZO). However,

ZnO has some intrinsic issues of negative bias and thermal stability. The majorly related defects- oxygen vacancies introduce instability of threshold voltage in ZnO TFT. Therefore, in the dissertation we would add a small amount of Mg into ZnO to form a ternary oxide, MgxZn<sub>1-x</sub>O (MZO, X<0.03) as the TFT channel. This was an effective and cost efficient way to improve the stability which made MZO a great candidate for HVTFTs in PV-SOG.

The development of MZO HVTFTs will open the opportunity to incorporate high voltage transistors in the system integration; therefore, it will build the foundation of PV-SOG which can provide people less expensive, more aesthetics, and more efficient solar energy system. In addition to solar inverters for PV-SOG, HVTFTs may be utilized in other integrated system, such as self-powered smart glasses, flat-panel x-ray imaging systems for medical radiology, and space engineering.

#### Chapter 3 Improvement of Stability of ZnO TFTs

#### 3.1. Background

Currently, majorities of manufacturers offer the 25-year standard solar panel warranty, which means that power output should not be less than 80% of rated power after 25 years. Inverters in PV system should have similar long life span, so it is critical for high voltage devices in solar inverters to have robust and stable electrical performance. Pure ZnO TFTs have a critical concern of the stability issues that turn-on voltage of ZnO TFTs shifts. This instability of turn-on voltage is more serious at higher temperature and at high negative gate bias. Unfortunately, solar panel often operates at higher temperature due to the long exposure to the sunlight. Moreover, the HVTFT works at negative gate bias to block the high voltage. These high temperature and negative gate bias are big challenges to pure ZnO devices.

Several reports indicated that donor like defects associated with oxygen vacancies could result in electrical instability in ZnO based TFTs<sup>43,47</sup>. To overcome shortcomings of ZnO TFTs, the IGZO TFTs emerged as a promising enabling technology which is now quickly commercialized to mass production. However, as mentioned in the previous chapter, with an increase in the cost of Indium metal and environmental concerns, it is also desired to develop an Indium-free TFT technology, especially for low cost applications.

To address this issue, we developed a ternary MZO film as the channel layer. A small amount of Mg is introduced into ZnO to form the Mg<sub>x</sub>Zn<sub>1-x</sub>O (x=0.03) channel layer, where the Mg-O has a stronger bonding energy (393.7 kJ/mole) than that of Zn-O (284.1 kJ/mol). Thus, it requires more energy to form an oxygen vacancy in the ternary Mg<sub>x</sub>Zn<sub>1-x</sub>O alloy<sup>48</sup>. The amount of Mg incorporation in Mg<sub>x</sub>Zn<sub>1-x</sub>O is kept low to avoid the degradation of TFT electrical characteristics from the alloying induced scattering and disorder. Our previous work already demonstrated that a small amount of Mg doping into ZnO improved in the thermal stability<sup>49</sup>. This chapter would focus on the stability at negative gate bias.

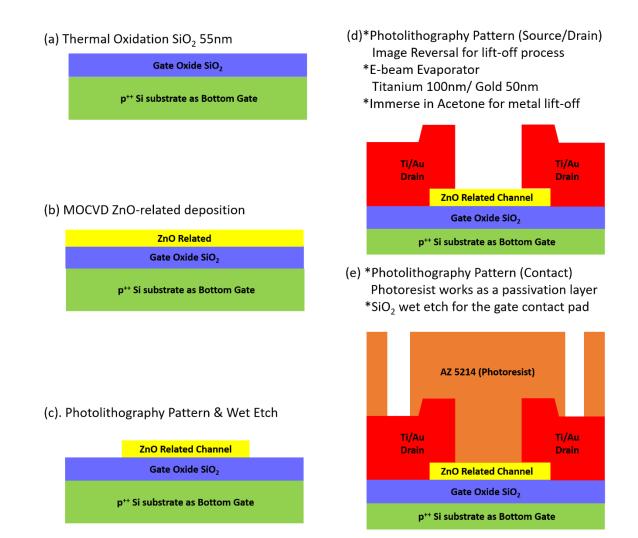

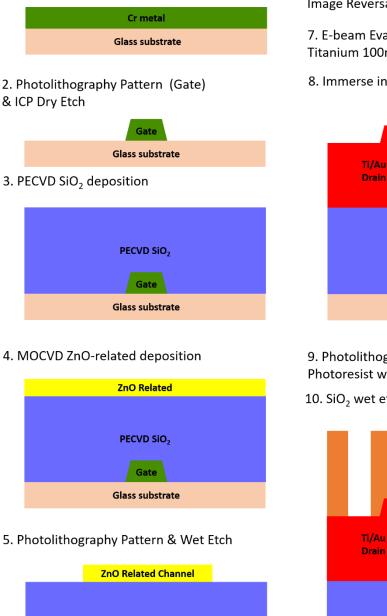

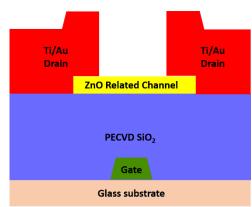

# 3.2. Fabrication Process and Setup of Electrical Test of Regular TFTs

To simplify the problems and speed up the process, in this study of the negative bias stress we utilized the regular common bottom gate TFT, instead of high voltage structure. The fabrication process is illustrated in Figure 3.1. Bottom gate Mg<sub>x</sub>Zn<sub>1-x</sub>O (x=0, 0.03) TFTs were fabricated on heavily-doped p-type Si wafers with a 50 nm thermally grown SiO<sub>2</sub> as a gate dielectric. Two types of 50 nm channel layers: ZnO and Mg0.03Zn0.97O (MZO) were grown by MOCVD at 400°C. DEZn (diethyl zinc) and MCp2Mg (bis (methylcyclopentadienyl) magnesium) were the precursors for Zn and Mg, respectively. The concentration of Mg in MZO film was characterized by using the optical bandgap in the transmission spectrum. The channel layers were patterned by the wet etch process, and two-steps procedure was used to prevent the undercut profile. The first step was done by diluted hydrochloric acid (1:2000) 5 seconds, and the diluted acetic acid (1:2000) 35 seconds was the second step. The source and drain metallization were formed with 100 nm Ti/ 50 nm Au by a lift-off process. The channel layer dimension is fixed at a width/length (W/L) ratio of 150  $\mu$ m / 5  $\mu$ m. An AZ-5214 photoresist layer was coated on top of the TFT channel, serving as a passivation layer to prevent ambient absorption/desorption during the electrical testing. All the electrical/NBS stability tests were conducted in a light-tight probe station using an HP-4156C electrical testing system.

**Figure 3.1** (a)  $\sim$  (e) The schematic diagram of fabrication process and (e) crosssectional view of the regular TFT

# 3.3. The Effect of Mg-doping on the Electrical and Material Characteristics

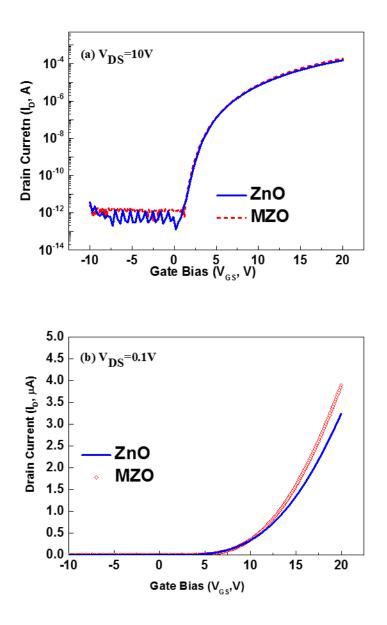

The transfer characteristics of ZnO and MZO TFTs with  $V_{DS}$ =10Vand  $V_{DS}$ =0.1V are shown in Figure 3.2 (a) and (b) respectively. The threshold voltage ( $V_{TH}$ ) is defined as the gate voltage value when a drain current ( $I_{DS}$ ) reaches 10<sup>-8</sup> A. The field effect mobility ( $\mu_{FE}$ ) is extracted from the linear region ( $V_{DS}$ =0.1V). The subthreshold swing (S.S.) is extracted from a 3-decades range in the subthreshold region of the log10 ( $I_{DS}$ ) vs  $V_G$  curve with  $V_{DS}$ =10V as in the equation (3-1)

$$S.S. = \left[\frac{\partial \log_{10} I_{DS}}{\partial V_G}\right]^{-1}$$

(3-1)

Both ZnO and MZO TFTs have the same threshold voltage of 3.5 V. The MZO TFT exhibits higher  $\mu_{FE}$  of 30 cm<sup>2</sup>/V-s and smaller *S.S.* value of 0.57 V/decade while the ZnO TFT shows  $\mu_{FE}$  of 25 cm<sup>2</sup>/V-s and S.S. of 0.79 V/decade. Since all TFTs were built on the same common Si bottom gate and dielectric layers, it could be assumed that the differences of  $\mu_{FE}$  and *S.S.* values between the two different TFT mainly resulted from the different bulk trap densities. If we assume bulk defects is much more than interface defects, the maximum bulk trap density ( $N_{BS}$ ) of the channel can be extracted from the *S.S*<sup>50</sup> as in the equation (3-2):

$$S.S. = \ln 10 \times \frac{kT}{q} \left[ 1 + q \frac{tN_{BS}}{C_{ins}} \right]$$

(3-2)

where k is the Boltzmann constant, *T* is the temperature, q is the elementary charge, *t* is the thickness of the channel, and *C*<sub>ins</sub> is the capacitance of the insulator.  $N_{BS}$  of ZnO TFT is 4.81 x 10<sup>17</sup> cm<sup>-3</sup> which is higher than 3.36 x 10<sup>17</sup> cm<sup>-3</sup> MZO TFT.

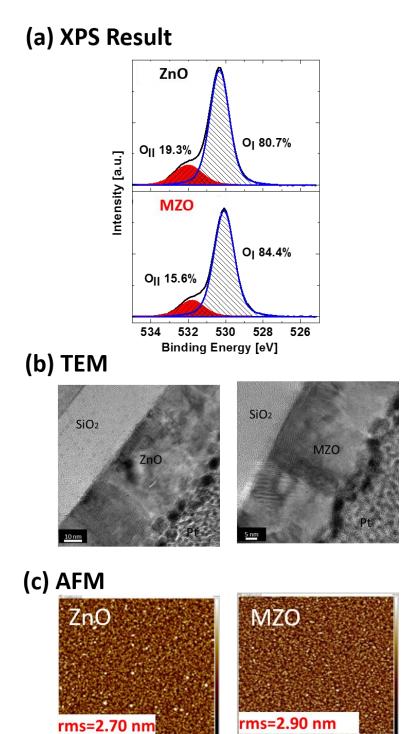

Several material characterizations were conducted to analysis the impact of a small amount of Mg in the ZnO. First, the XPS was utilized to analyze the concentration of oxygen vacancies in the films. In Figure 3.3 (a), it shows that  $O_{1s}$ peaks in XPS spectra of ZnO and MZO thin films. Gaussian fitting is used in the deconvolution of these  $O_{1s}$  peaks. The peak at the lower binding energy ~530 eV ( $O_{1}$ ) is attributed to  $O^{2-}$  ions located in a stoichiometric wurtzite ZnO structure. The other peak at the higher binding energy ~532 eV ( $O_{11}$ ) is related to  $O^{2-}$  ions in "oxygen deficient" ZnO which could be the oxygen vacancies. The ratio of two areas ( $O_{11}/O_{tot}$ ) indicates the relative quantity of this oxygen-related defect. By alloying 3% Mg into the ZnO thin film, MZO showed smaller quantity of oxygenrelated defects (15.6%) in comparison with ZnO (19.3%).