©2017

YANBIAO PAN

ALL RIGHTS RESERVED

# ORGANIC MICROELECTROMECHANICAL RELAY TECHNOLOGY FOR ULTRALOW-POWER FLEXIBLE TRANSPARENT LARGE-AREA

### ELECTRONICS

by

## YANBIAO PAN

A dissertation submitted to the

Graduate School-New Brunswick

Rutgers, The State University of New Jersey

In partial fulfillment of the requirements

For the degree of

Doctor of Philosophy

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Professor Jaeseok Jeon

And approved by

New Brunswick, New Jersey

May 2017

### **ABSTRACT OF THE DISSERTATION**

## Organic Microelectromechanical Relay Technology for Ultralow-Power Flexible Transparent Large-Area Electronics

By YANBIAO PAN

**Dissertation Director:**

Professor Jaeseok Jeon

Much research to date has focused on synthesizing new polymers or improving existing polymers, in order to overcome the limits of the conventional organic thin-film transistor (OTFT): (1) A rather low channel carrier mobility (< 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> typically) requires a power supply voltage well above 2 V for a reasonable on-/off-current ratio (>  $10^5$ ); (2) The formation of a relatively poor-quality interface between the polymeric channel and gate insulator induces large off-state leakage current well above  $10^{-13}$  A; (3) Asymmetric pairs of *n*- and *p*-type OTFTs result in noncomplementary switching. All these would affect the overall power consumption at the transistor, circuit, and system levels. This doctoral dissertation radically-different, proposes and demonstrates organic microelectromechanical (MEM) relays, in order to overcome such limits and hence enable efficient implementation of portable and/or wearable large-area electronics for the internet of things requiring ultralow-power operation, structural flexibility, visual transparency, and low-cost/-temperature processing. Firstly, a polymer-based lowthermal-budget surface-micromachining process is developed to implement organic relay prototypes (comprising multiple or single input/output terminals). Fabricated relays exhibit unique *I-V* characteristics including immeasurably-low off-state leakage current, abrupt transitions to the on-/off-state with an input voltage swing less than 60 mV for a decade change in output current, a relatively high on/off current ratio well above  $10^5$ , and complementary switching behavior and can endure a finite number of hot- and coldswitching cycles. Secondly, the effects of humidity, temperature, and low-surface-energy contacting electrodes materials on switching characteristics (such as hysteresis voltages and on-state resistance) are investigated. Thirdly, basic Boolean operations including AND, OR, and XOR and logic functions (*e.g.*, carry bit generation for four inputs) are demonstrated using a multi-input/-output relay.

#### ACKNOWLEDGEMENT

First, I would like to express my sincere, cordial, and deepest appreciation to my Ph.D. advisor Prof. Jaeseok Jeon for his unbounded enthusiasm, encouragement, patience, support, and guidance in my research towards completing my Ph.D. study at Rutgers. This is an enjoyable, inspiring and unforgettable memory in my life. My special thanks go to my dissertation committee members, Prof. Leonard Feldman, Prof. Yicheng Lu and Prof. Zhixiong (James) Guo for their enthusiastic serving on my dissertation committee and their evaluations and suggestions on my research work.

It is my pleasure to work with selfless and professional people in this project. I would like to thank Fangzhou Yu and Sourav Sagar for helping me with design and fabrication. Their insightful visions and suggestions make this project come true. I would like to thank Zhengyu Yang and Nabeela Khan for their assistance in simulation. I would also like to thank Wen-Chiang Hong and Siamak Abaslou for their suggestions in device testing.

The fabrication experiments were done in both Microelectronics Research Laboratory (MERL) of Rutgers University and Center for Functional Nanomaterials (CFN) of Brookhaven National Laboratory. I would like to thank all the staffs and co-workers in these two places, special thanks to Dr. Ming Lu, Dr. Aaron Stein, Dr. Chang-Yong Nam, Dr. Fernando Camino, Dr. Pavel Reyes, Dr. Yi Xu, Dr. Luozhou Li, Dr. Spencer Porter, Robert Lorber, Rui Li, Jiabao Zheng, Gwen Wright for their training and valuable advice on my project.

Last but not least, I am tremendously grateful to my parents and my wife for their support and encouragement. There are many difficult times during the Ph.D. study that make me start to double my abilities and decision. However, their enormous support helps me to strive for and fight through. I am truly blessed to be accompanied with my families.

## **Table of Contents**

| ABSTRACT OF THE DISSERTATION                                         | ii   |

|----------------------------------------------------------------------|------|

| ACKNOWLEDGEMENT                                                      | iv   |

| Table of Contents                                                    | vi   |

| List of Tables                                                       | viii |

| List of Illustrations                                                | ix   |

| 1. Introduction                                                      | 1    |

| 1.1. Status Quo: Organic Thin-Film Transistor Technology             | 4    |

| 1.2. New Insight: Organic Microelectromechanical Relay Technology    | 9    |

| 1.3. Organization of the Dissertation                                | 12   |

| 2. Organical Relay Design and Simulation                             | 14   |

| 2.1. Microelectromechanical Relay Structures and Operation Principle | 14   |

| 2.2. Prototype Organic Relay                                         | 21   |

| 2.2.1. Electrode Engineering                                         | 25   |

| 2.2.2. Air Gap Engineering                                           | 28   |

| 2.2.3. Gate Stack Engineering                                        | 30   |

| 2.3. Multiple-Input/-Output Relays                                   | 34   |

| 2.3.1. Single-Gate Dual-Body Relay                                   | 34   |

| 2.3.2. Dual-Gate Dual-Body Relay                                     |      |

| 3. Organic Relay Fabrication Process                                 | 44   |

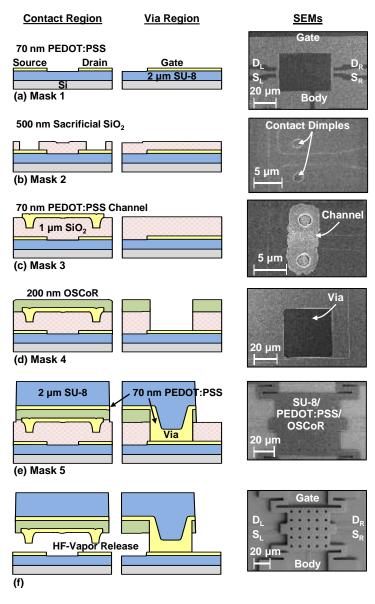

| 3.1. Substrate Preparation                                           | 46   |

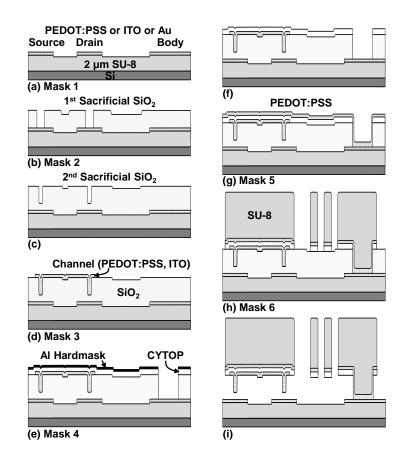

| 3.2. Mask 1: Electrode Definition                                    | 47   |

| 3.3. Mask 2: Contact Opening                                         | 51   |

| 3.4. Mask 3: Channel Formation                                       | 54   |

| 3.5. Mask 4: Via Formation                                           | 54   |

| 3.6. Mask 5: Movable Structure Formation                             | 56   |

| 3.7. Process Improvements                                              |     |

|------------------------------------------------------------------------|-----|

| 4. Relay Characterizations                                             | 68  |

| 4.1. Current-Voltage (I-V) Characteristics                             |     |

| 4.1.1. <i>I</i> ds- <i>V</i> gb Curves                                 |     |

| 4.1.2. <i>I</i> ds- <i>V</i> ds Curves                                 |     |

| 4.1.3. Body Biasing Effect                                             |     |

| 4.1.4. Complementary Switching Behavior                                |     |

| 4.1.5. Hysteric Switching Behavior                                     |     |

| 4.2. Switching Delay                                                   |     |

| 4.3. Switching Endurance                                               |     |

| 4.4. Effects of Temperature and Humidity on <i>I-V</i> Characteristics |     |

| 4.5. Relay for Logic-Gate and Carry-Generate Functions                 |     |

| 5. Conclusions                                                         | 100 |

| References                                                             | 102 |

## List of Tables

| Table 2.1 Design parameters and values of the prototype relay.                                           | .32 |

|----------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 Design parameters and values of the single-gate dual-body relay                                | .36 |

| Table 2.3 The overlap area and parallel-plate capacitance of the single-gate dual-body and the prototype |     |

| relay                                                                                                    | .40 |

| Table 2.4 Design parameters and values of the dual-gate dual-body relay                                  | .43 |

| Table 3.1 Fabrication process of SU-8 substrate.                                                         | .46 |

| Table 3.2 Young's modulus of common materials used in MEMS [48, 67, 68, 89, 90].                         | .60 |

| Table 3.3 RIE O <sub>2</sub> plasma etch rates for organic materials used in the MEM relay process       | .61 |

| Table 4.1 Hamaker constants of various materials in vacuum [107-109]                                     | .82 |

### **List of Illustrations**

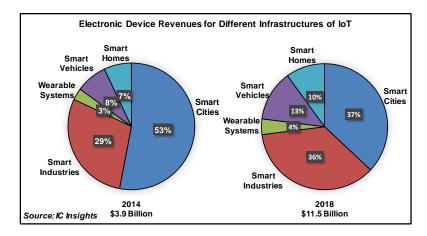

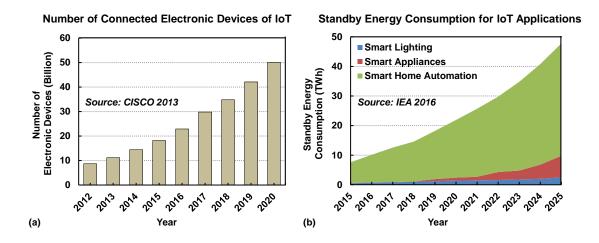

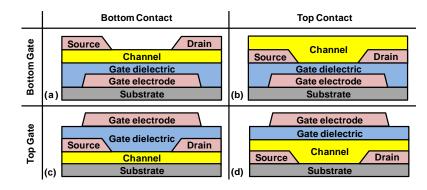

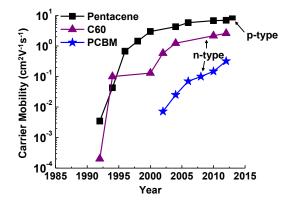

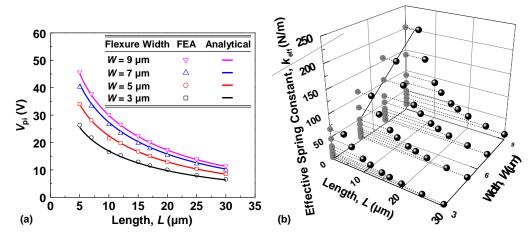

Figure 1.1 Adapted from [2]: The worldwide revenues of electronic devices used in different infrastructures of The Internet of Things (IoT). Smart cities, smart industries, smart vehicles, smart homes, and wearable systems are the main infrastructures of IoT. The revenue of electronic devices required in these infrastructures is 3.9 billion in the year of 2014. It is estimated to increase 195 % and reach 11.5 billion in Figure 1.2 (a) Adapted from [3]: The growth forecast of connected electronic devices of IoT. The number of connected electronic devices is 23 billion in the year of 2016, but it is estimated to reach 50 billion by 2020. (b) Adapted from [4]: The standby energy consumption of electronic devices used in different main IoT applications. It is predicted that the standby power consumption of main IoT electronic devices reach Figure 1.3 Schematic cross-section views of (a) Bottom gate bottom contact (BGBC) (b) Bottom gate top Figure 1.4 The development of the field-effect carrier mobility ( $\mu$ ) in some common p- and n-type Figure 1.6 (a) Schematic illustration of a simplified 3-terminal (3-T) MEM relay. In the off-state ( $V_g < V_r$ ),  $V_{\rm rl}$  is called the release voltage of the relay. The presence of air gap between source and drain electrodes prevents current flow  $I_{ds}$ , which results in zero off-state leakage. Actuation gap  $(g_0)$  is the air gap thickness between the source and gate. Dimple gap  $(g_d)$  is the air gap thickness between source to drain. In the onstate ( $V_g > V_{pi}$ ),  $V_{pi}$  is called the pull-in voltage of the relay. The electrostatic actuation force ( $F_e$ ) induced by the gate and source electrodes attracts the source to move downward so that the electrical contact between the source and drain is made, current flow  $I_{ds}$  is therefore formed, which leads to abrupt on-state transition. (b) The conceptual  $I_{ds}$ - $V_g$  characteristic of MEM relay showing the relay has zero off-state leakage, it can turn on and off abruptly by a small gate-voltage swing with  $SS \approx 0$ . The hysteretic switching behavior  $(V_{pi}-V_{rl})$  is due to pull-in mode operation and surface adhesion force  $(F_a)$  [39]. .....10 Figure 2.1 (a) Top-view, (b) Isometric-view, and (c) Circuit symbol of a 3-Terminal (3-T) relay. The 3-T relay comprises three terminals: a movable source, a gate, and a drain. The source electrode has one protruding region, referred to as dimple. The dimple restricts the motion of the movable source when it contacts the drain. (d) Top-view, (e) Isometric-view, and (f) Circuit symbol of a 4-Terminal (4-T) relay. The 4-T relay comprises four terminals: a movable gate, a body, a source, and a drain. The channel beneath the gate insulator has two protruding regions, referred to as dimples. The dimples restrict the motion of the Figure 2.2 Spring model of the electrostatically actuated 4-T MEM relay. The air gap thickness between gate and body is called the actuation gap  $(g_0)$ . The air gap thickness between the dimples and corresponding source and drain is referred to as the dimple gap thickness  $(g_d)$ . The width and length of the body electrode are  $W_a$  and  $L_a$ , respectively. When  $V_{gb}$  is applied, the electrostatic actuation force ( $F_e$ ) induced by the body and gate electrodes moves the suspended gate electrode together with the channel and gate insulator downward. The balancing force is the spring restoring force  $(F_{sp})$  of the movable gate. If  $F_e > F_{sp}$ , the movable gate brings the channel into contact with the source and drain to conduct current, which leads to abrupt on-state transition. The channel beneath the gate insulator has two protruding regions, referred to as dimples. The dimples restrict the motion of the movable gate when they contact the corresponding source

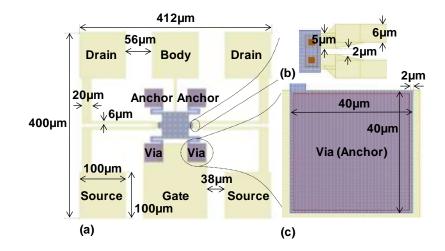

Figure 2.4 (a) Layout of the prototype relay. The minimum size of electrode pad is  $100 \times 100 \ \mu\text{m}^2$ , that is conservative large to place probe tip for relay electrical characterizations. The minimum space between electrode pads is 38  $\mu$ m, that is set in order to conservatively place separate probe tips on two adjacent electrode pads. The relay is anchored by four anchors on PEDOT:PSS substrate. Two vias enable connection from the conductive layer (PEDOT:PSS) in the gate stack to the gate electrode. (b) Zoomed-in view showing channel and dimple region, the spacing between the source and drain electrodes is set to 2  $\mu$ m to prevent surface leakage. (c) Zoomed-in view showing relay is anchored on PEDOT:PSS substrate. The size of the anchor is  $40 \times 40 \ \mu\text{m}^2$ , that is conservative large to provide enough reliability. The size of via is  $38 \times 38 \ \mu\text{m}^2$ . The gate electrode is connected to the conductive layer in the gate stack through two vias.

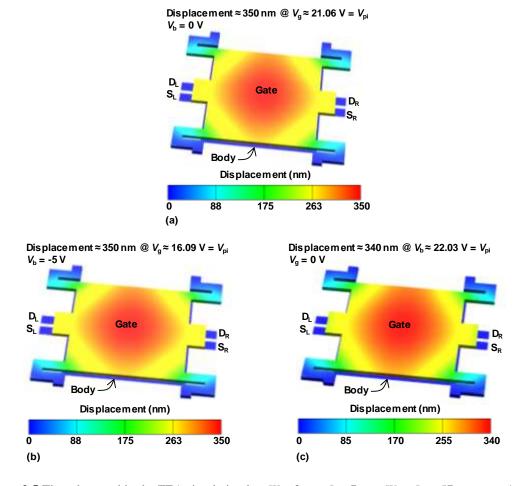

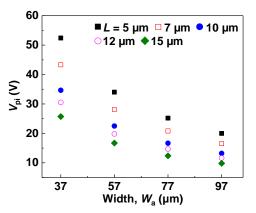

Figure 2.5 The relay used in the FEA simulation has  $W = 3 \mu m$ ,  $L = 7 \mu m$ ,  $W_a = L_a = 57 \mu m$ ,  $g_o = 1 \mu m$ ,  $g_d =$ 500 nm and  $t_{\rm m} = 2.27 \ \mu {\rm m}$ .  $V_{\rm d}$  and  $V_{\rm s}$  were set to 0 V in the simulation. (a) When  $V_{\rm b} = 0$  V, the relay is actuated downward by ~350 nm ( $\approx 1/3g_0$ ) at  $V_g \approx 21.06$  V =  $V_{pi}$ , then it turns on abruptly. (b) When body bias  $V_{\rm b}$  = -5 V, the relay turns on at  $V_{\rm g} \approx 16.21$  V =  $V_{\rm pi}$ . (c) The relay turns on at  $V_{\rm b} \approx 22.03$  V =  $V_{\rm pi}$  and  $V_g = 0$  V. The number of volume element mesh created of the simulation was 25162 and displacement Figure 2.6 (a) Change of  $F_{e}$ ,  $F_{sp}$  vs. gap distance of the prototype relay. (b) The cross-section view of the prototype relay. The ratio of  $g_d$  and  $g_o$  is 0.5, that is greater than 1/3. The relay operates in pull-in mode. The movable gate snaps down abruptly after it travels to  $x = g_0/3$ ,  $F_e$  is always greater than  $F_{sp}$  after the Figure 2.7 (a) Top-down view of the prototype relay layout. Note that release etch holes on gate stack are not shown. The minimum feature size of the photolithography tools (Karl Suss MA6 Mask Aligner and Karl Suss MJB3 Mask Aligner) used for this work is 1 µm and the maximum photolithographic alignment tolerance is conservatively set to 1  $\mu$ m. The spacing between the source and drain electrodes is set to 2  $\mu$ m, the spacing between body and either drain or source is set to  $2 \mu m$  to prevent surface leakage. The gate stack to body cut-out is set to 1 µm to allow for sufficient photolithographic alignment tolerance, the overlap actuation area is determined by the gate stack area ( $W_a \times L_a$ ). The channel is enclosed by the gate stack by 1 µm. The channel to drain/source overlap is minimized to prevent unwanted electrostatic actuation force between the channel and drain/source. (b) Dimensions of the folded-flexures that supports the gate stack. The effective spring constant of the flexure-beams can be estimated from Equation (2-10). (c) Dimensions of the channel. Each contact is enclosed by the channel with boundary of 1  $\mu$ m. The contact dimple dimensions are limited to  $2 \times 2 \,\mu m^2$  to prevent the in-used stiction and  $F_a$  [39]......31 Figure 2.9 FEA simulated  $V_{pi}$  vs.  $W_a$  of the prototype relays. The relays have  $t_m = 2.27 \ \mu m$ ,  $g_o = 1 \ \mu m$ ,  $g_d =$ 500 nm,  $W = 5 \mu$ m, and  $L \le 15 \mu$ m.  $V_b$ ,  $V_d$ , and  $V_s$  were set to 0 V in the simulation. As  $W_a$  increases ( $W_a =$

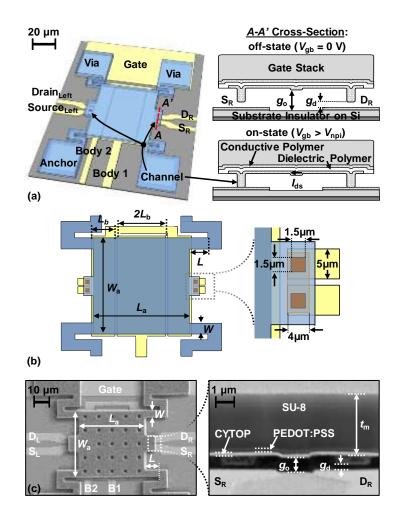

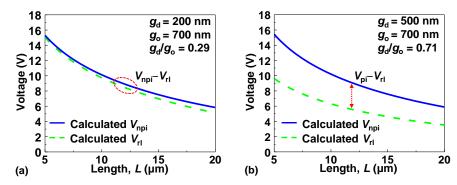

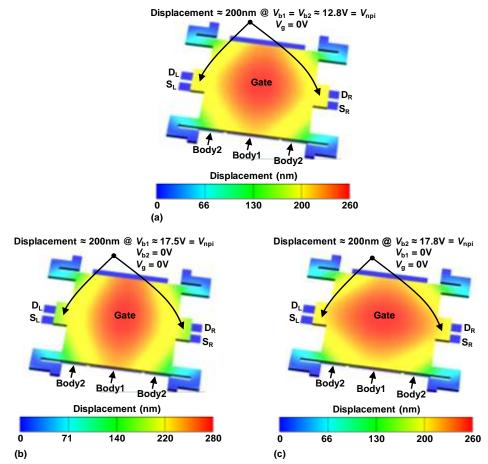

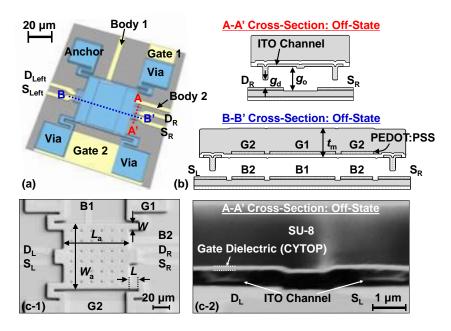

Figure 2.10 (a) Isometric schematic and cross-sectional views of the single-gate dual-body relay. (b) The Figure 2.11 (a) Change of  $F_{e}$ ,  $F_{sp}$  vs. gap distance of the single-gate dual-body relay. (b) The cross-section view of the single-gate dual-body relay. The ratio of  $g_d$  and  $g_o$  is 1/3.5, that is smaller than 1/3. The relay operates in non-pull-in mode, in which  $g_d$  determines the maximum displacement the relay. The relay turns Figure 2.12 (a) The theoretically calculated  $V_{npi}$  and  $V_{rl}$  of the refined single-gate dual-body relay that operates in non-pull-in mode with  $g_0 = 700$  nm,  $g_d = 200$  nm,  $g_d/g_0 = 0.29 < 1/3$ . (b) The theoretically calculated  $V_{pi}$  and  $V_{rl}$  of an arbitrary relay that operates in pull-in mode with  $g_0 = 700$  nm,  $g_d = 500$  nm,  $g_d/g_0 = 0.71 > 1/3$ . The other parameters of the relays are the same:  $W_a = L_a = 57 \ \mu m$ ,  $W = 3 \ \mu m$ ,  $t_m = 2.46$ Table 2.3 The overlap area and parallel-plate capacitance of the single-gate dual-body and the prototype relay......40 Figure 2.13 The FEA simulation result of the single-gate dual-body relay. The parameters of the relay are  $W = 5 \ \mu m, \ L = 10 \ \mu m, \ W_a = L_a = 57 \ \mu m, \ L_b = 13.5 \ \mu m, \ g_o = 700 \ nm, \ g_d = 200 \ nm, \ t_m = 2.46 \ \mu m.$  (a) The relay turns on when  $V_{b1} = V_{b2} \approx 12.8$  V,  $V_g = 0$  V. The maximum downward displacement of ~260 nm occurs at the center of the movable body with the displacement of ~200 nm along the channel regions. (b) The relay turns on at  $V_{b1} \approx 17.5$  V,  $V_{b2} = V_g = 0$  V. (c) The relay turns on at  $V_{b2} \approx 17.8$  V,  $V_{b1} = V_g = 0$  V. The number of volume element mesh created of the simulation was 28417 and displacement tolerance was Figure 2.14 (a) Isometric schematic of the dual-gate dual-body organic MEM relay. (b) Cross-section views across A-A' and B-B' in the off-state of the relay. (c-1) Plan-view and (c-2) cross-section view SEMs of

| Cable 3.1 Fabrication process of SU-8 substrate.                                                     | .46  |

|------------------------------------------------------------------------------------------------------|------|

| To promote the adhesion between the next layer to the hydrophobic SU-8 surface, SU-8 substrate was f | irst |

| ctivated with O2 plasma for 20 seconds with 50 sccm O2, 200 mT, and 50 W, and then an adhes          | ion  |

| promoter (Silquest A-187) was applied prior to the electrode forming step                            | .47  |

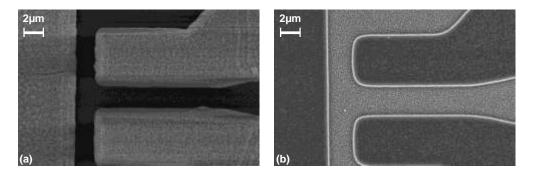

| Figure 3.2 The SEMs of the patterned PEDOT:PSS electrode layers using (a) conventional photore       | sist |

| howing damaged PEDOT:PSS surface and (b) fluorinated photoresist showing intact PEDOT:PSS surface    | ice. |

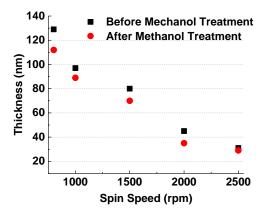

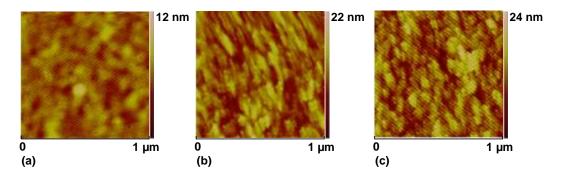

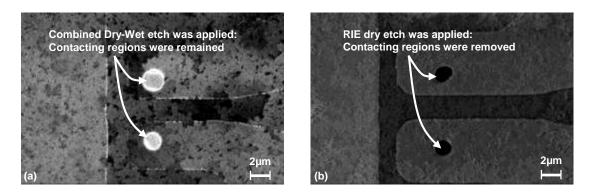

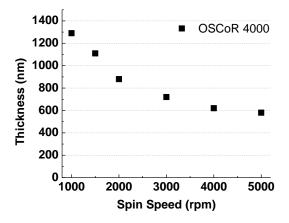

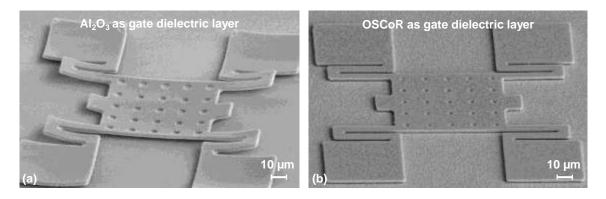

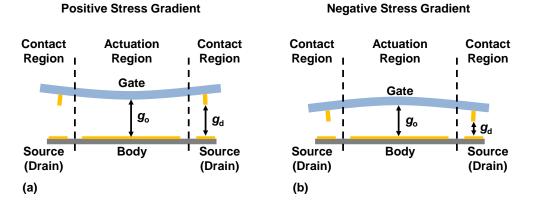

Figure 3.3 The thickness of spin-coated PEDOT:PSS layer vs. spin speed. The black square presents the layer thickness of PEDOT:PSS before methanol treatment, and the red dot indicates the layer thickness of Figure 3.4 AFM images of (a) fresh PEDOT:PSS surface, (b) PEDOT:PSS surface after staying in water for 2 minutes and (c) PEDOT:PSS surface after staying in water for 10 minutes. All the PEDOT:PSS films Figure 3.5 The SEMs of (a) sample that the contacting regions were etched by combined dry-wet etching, showing that the bottom electrode (PEDOT:PSS) is intact and (b) sample that the contacting regions were etched by only RIE dry etching, showing the bottom electrode (PEDOT:PSS) is completely removed......53 Figure 3.7 SEMs of the movable gate stacks (a) with 10 nm  $Al_2O_3$  as dielectric underneath 1  $\mu$ m SU-8 and Figure 3.8 Simplified cross-section schematics of MEM relays with non-zero stress gradient. (a) Positive 57 stress gradient results in a concave upward beam structure. (b) Negative stress gradient results in a concave downward beam structure. The out-of-plane deformation results the actual  $g_0$  and  $g_d$  to be different from the Table 3.2 Young's modulus of common materials used in MEMS [48, 67, 68, 89, 90]......60

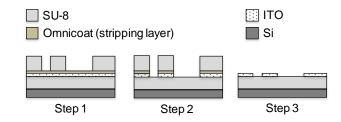

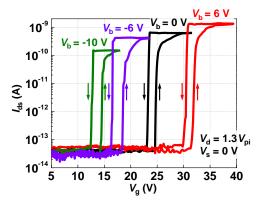

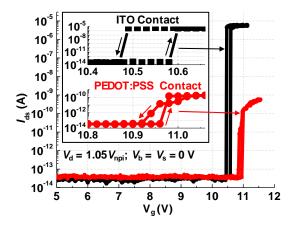

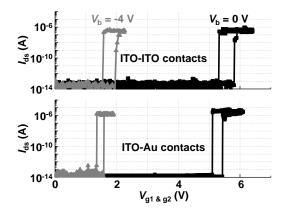

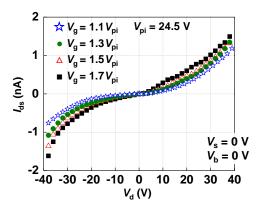

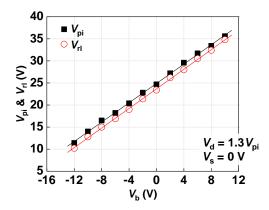

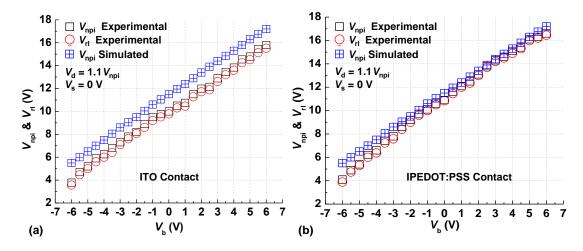

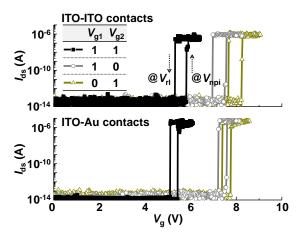

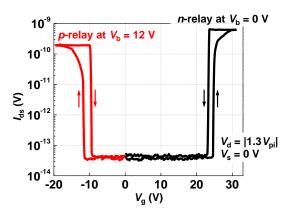

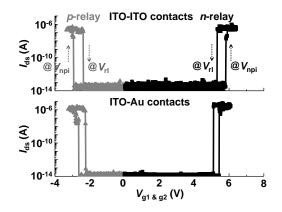

Figure 3.10 The fabrication steps of forming ITO electrodes. Step 1: Patterning of SU-8 on top of Omnicoat stripping layer (~5 nm). Step 2: Etching Omnicoat and ITO layers. Step 3: Stripping the SU-8 layer by Figure 4.1 Measured  $I_{ds}$ - $V_{gb}$  characteristics of the prototype relay for various body biases at 25 °C in air at 1 atm. Immeasurably-low off-state leakage current and abrupt switching behavior were observed. Dimensions of the relay: actuation gap thickness  $g_0 = 1 \ \mu m$ , dimple gap thickness  $g_d = 500 \ nm$ , foldedflexure width  $W = 5 \mu m$ , folded-flexure length  $L = 10 \mu m$ , actuation plate width and length  $W_a = L_a = 57$ Figure 4.2 Measured  $I_{ds}$ - $V_{gb}$  curves of the fully- and partially-polymeric single-gate dual-body relays at 25 °C in air at 1 atm. Maximum  $V_g = 1.05 V_{npi} = V_{dd}$ . Body 1 and Body 2 were tied together to form a body terminal. Dimensions of the relays:  $g_0 = 700$  nm,  $g_d = 200$  nm,  $W = 7 \mu m$ ,  $L = 15 \mu m$ ,  $W_a = L_a = 57 \mu m$ , and Figure 4.3 Measured  $I_{ds}-V_{gb}$  curves of the partially-polymeric dual-gate dual-body relays—one with ITO source and drain (S/D) and the other with Au S/D—for different body biases at 25 °C in air at 1 atm. Body 1 and Body 2 were tied together and biased to 0 V (black ink above) or -4 V (gray) for each relay. Gate 1 and Gate 2 were also tied together. Maximum  $V_{g1} = V_{g2} = 1.1 \cdot V_{npi} = V_{dd}$ ,  $V_s = 0$  V, and  $V_d = V_{dd}$ . Dimensions of the relays:  $g_0 = 600$  nm,  $g_d = 150$  nm,  $W = 6 \mu$ m,  $L = 16 \mu$ m,  $W_a = L_a = 64 \mu$ m, and  $t_m = 1.96$ μm.....71 Figure 4.4 Measured  $I_{ds}$  as a function of  $V_d$  of the prototype relay (in Figure 4.1) at 25 °C in air at 1 atm. A diode behavior is seen due to a potential energy barrier between the PEDOT:PSS and the tungsten probe tip used for testing. A stronger gate-overdrive  $(V_g - V_{pi})$  for a given  $V_d$  results in a larger on-state current,  $I_{ds}$ . Dimensions of the relay:  $g_0 = 1 \mu m$ ,  $g_d = 500 nm$ ,  $W = 5 \mu m$ ,  $L = 10 \mu m$ ,  $W_a = L_a = 57 \mu m$ , and  $t_m = 2.27 \mu m$ .

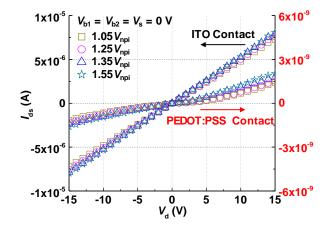

Figure 4.5 Measured  $I_{ds}$ - $V_{ds}$  characteristics of the fully- and partially-polymeric single-gate dual-body relays (in Figure 4.2) at 25 °C in air at 1 atm for various gate overdrive voltages. Maximum  $V_g = n \cdot V_{npi}$ ,

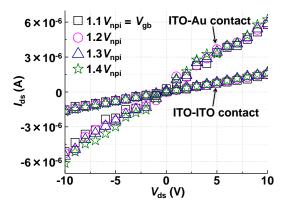

Figure 4.6 Measured  $I_{ds}$ - $V_{ds}$  characteristics of the partially-polymeric dual-gate dual-body relays (in Figure 4.3) for various gate overdrive voltages at 25 °C in air at 1 atm.  $V_{g1} = V_{g2}$  and  $V_b = V_s = 0$  V.  $V_{gb}$  was set to 110 % of  $V_{npi}$  or larger, as indicated in the figure. Dimensions of the relays:  $g_0 = 600$  nm,  $g_d = 150$  nm, W =Figure 4.7 Measured  $V_{pi}$  and  $V_{rl}$  vs.  $V_b$  of the prototype relay (in Figure 4.1). A change in  $V_b$  results in commensurate changes to  $V_{pi}$  and  $V_{rl}$ .  $V_{pi}-V_{rl} = 1.30$  V, 1.28 V, and 1.17 V for V<sub>b</sub> = -6 V, 0 V, and 6 V, respectively. Hysteresis behavior  $(V_{pi} \neq V_{rl})$  is due to finite  $F_a$  and pull-in mode operation. Dimensions of Figure 4.8 Measured  $V_{npi}$ ,  $V_{rl}$  and simulated  $V_{npi}$  vs.  $V_b$  for the fully- and partially-polymeric single-gate dual-body relays (in Figure 4.2) with ITO contact (a) and PEDOT:PSS contact (b), respectively. Body 1 and Body 2 were tied together to form a body terminal. A change in  $V_b$  results in commensurate changes to  $V_{\rm npi}$  and  $V_{\rm rl}$ . Hysteresis behavior ( $V_{\rm npi} \neq V_{\rm rl}$ ) is due to finite  $F_{\rm a}$ . Dimensions of the relays:  $g_{\rm o} = 700$  nm,  $g_{\rm d} =$ Figure 4.9 Measured  $I_{ds}$ - $V_{gb}$  of the dual-gate dual-body relays (in Figure 4.3) for different input voltage combinations at 25 °C in air at 1 atm. '1' =  $V_{dd} = 1.1 \cdot V_{npi} = V_d$  and  $V_s = V_b = 0$  V.  $V_{npi} \cong 5.81$  V and 5.43 V for the relays with ITO and Au S/D, respectively. Body 1 and Body 2 were tied together and biased to 0 V. Only one pair of S/D was used. Dimensions of the relays:  $g_0 = 600$  nm,  $g_d = 150$  nm,  $W = 6 \mu m$ ,  $L = 16 \mu m$ , Figure 4.10 Measured  $I_{ds}$ - $V_g$  for p- and n-type operations based on the prototype relay (in Figure 4.1) at 25  $^{\circ}$ C in air at 1 atm. Since electrostatic actuation is ambipolar, the operation of the prototype relay mimics that of an *n*-channel or a *p*-channel MOSFET. Both *n*-relay and *p*-relay are achieved by biasing the body terminal at 0 V or  $V_{dd}$ , respectively. The left pair of source/drain was left floating. Dimensions of the relay:  $g_{\rm o} = 1 \ \mu m, \ g_{\rm d} = 500 \ nm, \ W = 5 \ \mu m, \ L = 10 \ \mu m, \ W_{\rm a} = L_{\rm a} = 57 \ \mu m, \ {\rm and} \ t_{\rm m} = 2.27 \ \mu m.$

| Figure 4.11 Measured $I_{ds}$ - $V_g$ for $p$ - and $n$ -type operations based on the dual-gate dual-body relays (in Figure                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3) at 25 $^{\circ}$ C in air at 1 atm, showing symmetric operations for digital logic circuits. Gate 1 and Gate 2                                     |

| were tied together to form a single node. One pair of S/D was left floating. Max $V_{g1} = V_{g2} = V_d = 1.1 \cdot V_{npi} =$                          |

| $V_{dd}$ and $V_s = 0$ V. $V_b = 3$ V and 0 V for <i>p</i> - and <i>n</i> -relay, respectively. Dimensions of the relays: $g_0 = 600$ nm,               |

| $g_d = 150$ nm, $W = 6 \mu m$ , $L = 16 \mu m$ , $W_a = L_a = 64 \mu m$ , and $t_m = 1.96 \mu m$                                                        |

| Table 4.1 Hamaker constants of various materials in vacuum [107-109]                                                                                    |

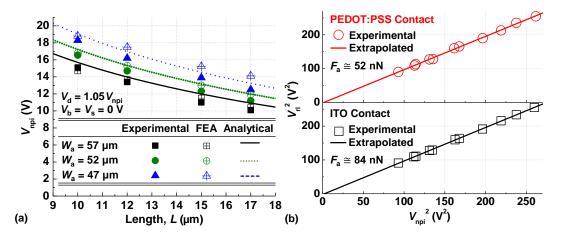

| Figure 4.12 (a) Measured, simulated, and calculated $V_{npi}$ vs. L of the fully- and partially-polymeric single-                                       |

| gate dual-body relays (in Figure 4.2). Maximum $V_g = 1.05 V_{npi} = V_{dd}$ . The measurement was performed at 25                                      |

| °C in air at 1 atm. $W = 7 \mu m$ and $W_a = L_a$ . (b) $V_{rl}^2 vs. V_{npi}^2$ . Each relay has four dimples: two on either side.                     |

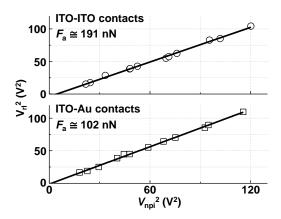

| The area of each dimple is 2.25 $\mu m^2$                                                                                                               |

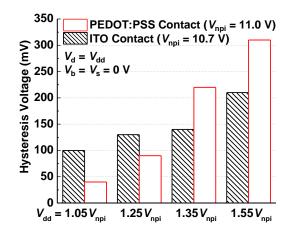

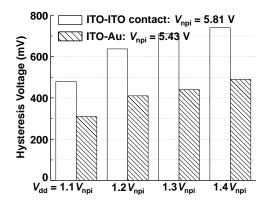

| Figure 4.13 Measured hysteresis voltages of the fully- and partially-polymeric single-gate dual-body relays                                             |

| (in Figure 4.2) for different gate overdrive voltages at 25 °C in air at 1 atm. Max $V_g = V_{dd}$                                                      |

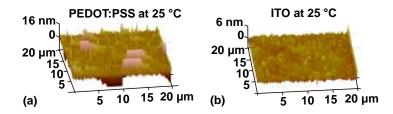

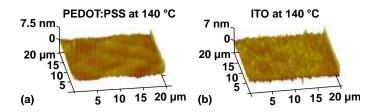

| Figure 4.14 AFM images of (a) PEDOT:PSS and (b) ITO surfaces of polymeric relays measured at 25 °C in                                                   |

| air at 1 atm. $W = 7 \mu m$ , $L = 15 \mu m$ , and $W_a = L_a = 57 \mu m$ . RMS values of surface roughness were extracted                              |

| to be 2.12 nm and 0.74 nm for the PEDOT:PSS and ITO surfaces, respectively                                                                              |

| Figure 4.15 Measured and calculated $V_{rl}^2 vs. V_{npi}^2$ of the dual-gate dual-body relays (in Figure 4.3) at 25 °C                                 |

| in air at 1 atm in order to extract <i>F</i> <sub>a</sub> for ITO-ITO and ITO-Au contacts                                                               |

| Figure 4.16 Measured hysteresis voltages of the dual-gate dual-body relays (in Figure 4.3) for various $V_{\rm g}$ -                                    |

| $V_{\rm npi}$ . Maximum $V_{\rm g1} = V_{\rm g2} = V_{\rm dd}$ , $V_{\rm b} = V_{\rm s} = 0$ V, and $V_{\rm d} = V_{\rm dd}$                            |

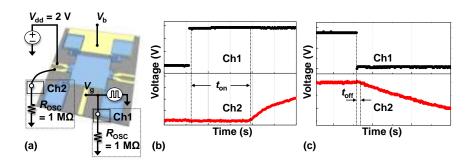

| Figure 4.17 (a) Delay measurement setup of organic MEM relay. (b) The turn-on delay $(t_{on})$ can be                                                   |

| extracted from the difference between the input and output signals. (c) The turn-off delay $(t_{off})$ can be                                           |

| extracted from the difference between the input and output signals. A function generator (Tektronix                                                     |

| AFG3252C) was used to supply the input signals; a DC power supply (GW Instek GPS-4303) to set the DC                                                    |

| biases; and an oscilloscope (Tektronix DPO2024B) to monitor and record the output signals                                                               |

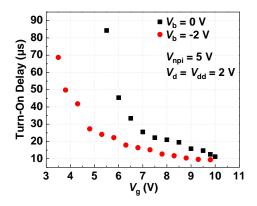

| Figure 4.18 Measured $t_{on}$ for different $V_g$ with 0 V and -2 V body biases at 25 °C in air at 1 atm. Relay has                                     |

| $V_{\rm npi} = 5$ V, $W = 8$ µm, $L = 13$ µm, and $W_{\rm a} = L_{\rm a} = 57$ µm. The $t_{\rm on}$ decreases with increasing $V_{\rm g}$ and saturates |

| at ~9.4 μs                                                                                                                                              |

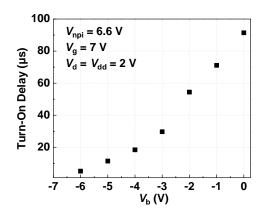

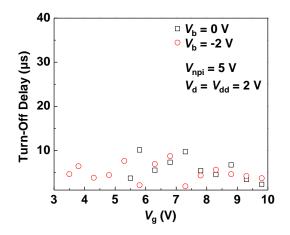

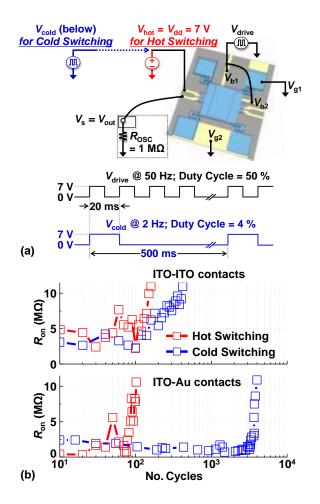

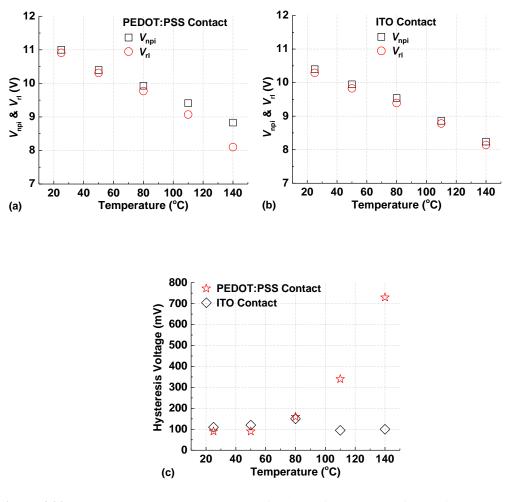

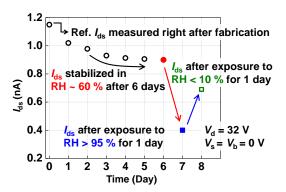

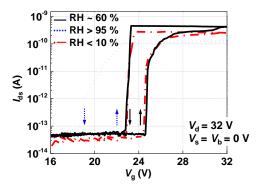

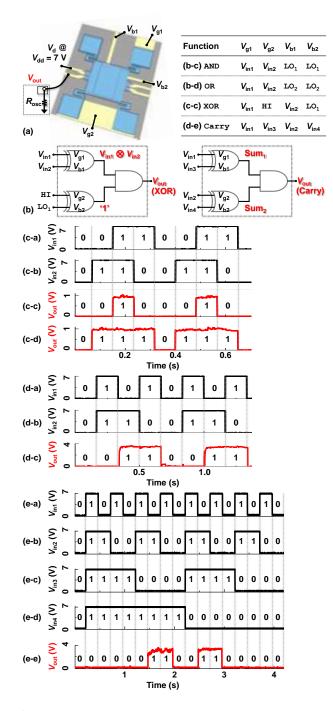

Figure 4.19 Measured  $t_{on}$  with different  $V_b$  at 25 °C in air at 1 atm. Relay has  $V_{npi} = 6.6$  V,  $W = 8 \mu m$ , L =10  $\mu$ m, and  $W_a = L_a = 57 \mu$ m. The increasing  $|V_b|$  decreases the  $t_{on}$ . The minimum  $t_{on}$  of ~5.1  $\mu$ s is achieved Figure 4.20 Measured  $t_{\rm off}$  for different  $V_{\rm g}$  with 0 V and -2 V body biases at 25 °C in air at 1 atm. Relay has  $V_{\rm npi} = 5V$ ,  $W = 8 \,\mu\text{m}$ ,  $L = 13 \,\mu\text{m}$ , and  $W_{\rm a} = L_{\rm a} = 57 \,\mu\text{m}$ . The  $t_{\rm off}$  values are within the range of 1 to 10  $\mu\text{s}$ ...90 Figure 4.21 (a) Testing setup. Either DC  $V_{hot}$  or square-wave  $V_{cold}$  was applied to the drain electrode for hot or cold switching, respectively. (b) Measured  $R_{on}$  of the relays vs. number of hot- and cold-switching cycles. A function generator (Tektronix AFG3252C) was used to supply the input signals; a DC power supply (GW Instek GPS-4303) to set the DC biases; and an oscilloscope (Tektronix DPO2024B) to monitor Figure 4.22 Measured  $V_{npi}$  and  $V_{rl}$  values as a function of temperature for (a) fully-polymeric (b) partiallypolymeric relays (in Figure 4.2) in air at 1 atm. Bias conditions are:  $V_d = 1.05V_{npi} = V_{dd}$ ;  $V_b = V_s = 0$  V; maximum  $V_g = V_{dd}$ . (c) Hysteresis voltages of the relays in (a) and (b). Dimensions of the relays:  $g_0 = 700$ Figure 4.23 AFM images of (a) PEDOT:PSS and (b) ITO surfaces of the polymeric relays (in Figure 4.2) measured at 140 °C in air at 1 atm. RMS values of surface roughness were extracted to be 0.71 nm and 0.76 Figure 4.24 Measured  $I_{ds}$  of the prototype relay (in Figure 4.1) as a function of time at 25 °C in air at 1 atm. When the relay was placed in RH = 60 %,  $I_{ds}$  were decreased gradually and stabilized eventually; in RH = Figure 4.25 Measured  $I_{ds}$  vs.  $V_g$  of the prototype MEM relay (in Figure 4.1) in various RH conditions at 23 °C and 1 atm. After the relay was exposed to RH = 95 % for a day,  $I_{ds}$  and  $V_{pi}$  were lowered. These  $I_{ds}$  and  $V_{\rm pi}$  were recovered partially and fully, respectively, after the relay was stored in RH < 10 % for a day. .....96 Figure 4.26 (a) Bias configuration.  $LO_1 = 0$  V,  $LO_2 = -2$  V, and  $HI = V_{dd} = 7$  V. (b) Symbolic representation for XOR and carry generate functions. (c) Measured logic waveforms: (c-a) input 1 signal; (c-b) input 2 signal; (c-c) AND output signal; and (c-d) OR output signal. (d) Measured logic waveforms: (d-a) input 1

## 1. Introduction

The key idea of Internet of Things (IoT) is that electronic signal-acquisition and processing systems (including sensors, actuators, and computers) we use today can be connected together wirelessly to incorporate the physical world into the internet network for more efficient collection, processing, and distribution of information [1]. New dimensions will be added to the world of information and communication technologies, and as a result, such IoT-based developments are expected to transform our daily lives significantly.

The IoT entails very broad vision. Many smart environments can be involved within the infrastructures of IoT (Figure 1.1), for example, wearable systems, smart buildings and vehicles, more broadly, smart industries and cities [2]. There are billions of applications

**Figure 1.1** Adapted from [2]: The worldwide revenues of electronic devices used in different infrastructures of The Internet of Things (IoT). Smart cities, smart industries, smart vehicles, smart homes, and wearable systems are the main infrastructures of IoT. The revenue of electronic devices required in these infrastructures is 3.9 billion in the year of 2014. It is estimated to increase 195 % and reach 11.5 billion in the year of 2018.

**Figure 1.2** (a) Adapted from [3]: The growth forecast of connected electronic devices of IoT. The number of connected electronic devices is 23 billion in the year of 2016, but it is estimated to reach 50 billion by 2020. (b) Adapted from [4]: The standby energy consumption of electronic devices used in different main IoT applications. It is predicted that the standby power consumption of main IoT electronic devices reach 46 TWh in 2025, which equals to the annual electricity usage of Portugal in the year of 2012.

that could lead to these kinds of IoT enviroments, and many of these applications require one or several semiconductor devices including radio frequency identification tags (RFID), sensors and actuators, memory, display systemsm, *etc.* Mass-manufactured large-area electronics implemented on very thin and flexible plastic substrates, for example, can be one of the enabling technologies in that, any electronics, in principle, could be attached to the surface of any physical platforms. According to Figure 1.1, IoT industry is expected to see a very strong growth in the coming years from 3.9 billion in the year of 2014 to 11.5 billion in the year of 2018.

As the revenue of electronic devices required for IoT grows, an increasing number of electronic devices will be manufactured and used in our daily lives. As predicted in

Figure 1.2(a), while there are approximately 23 billion IoT electronic devices connected in the year of 2016, this number is forecasted to increase to more than 50 billion by 2020. Achieving high energy-efficiency would be of importance when such a large number of devices are connected and used for IoT applications. To assess the potential impact of IoT applications on energy consumption worldwide, research data on the standby power consumption of selected IoT devices is indicated in Figure 1.2(b). It is expected that the standby energy consumption of such IoT electronics would increase with annual growth rate of 20 % and surpass 46 TWh in 2025, which equals to the annual electricity consumption of Portugal in the year of 2012. More than 50 billion electric devices will be connected by 2020, and they would consume \$120 billion energy.

To integrate that large number of electronic devices, IoT drives a huge demand for lowpower/-cost devices that can save manufacturing costs and reduce global energy consumption. In this regard, various technologies that can achieve low manufacturing costs and low power consumption are already established or emerging for the realization IoT applications. One of these promising technologies is the organic thin-film transistor (OTFT). OTFT has been extensively researched over the past decades as an alternative or complement to conventional inorganic TFT in order to realize applications where large area coverage, low temperature processing, low cost, and structural flexibility are required. Recent advances in polymer synthesis and processing [5], together with advancements in polymer microfabrication technology, have recently enabled the implementation of OTFT in several IoT electronics recently including RFIDs [6], organic light emitting diodes (OLEDs) [7], organic nonvolatile memory [8], radio frequency (RF) sensor [9], *etc*.

### 1.1. Status Quo: Organic Thin-Film Transistor Technology

In 1986, Tsumura *et al.* [10] introduced the first OTFT, which used organic semiconductor material as the active layer for the channel. Since then, the performance of OTFT has undergone significant improvements, and OTFT has now been considered as one of the promising semiconductor devices for the realization of low cost, low temperature, large area, and flexible electronic systems used for IoT [11-15]. The low temperature process (typically less than 200 °C) of organic materials makes OTFT suitable for implementation on various flexible substrates (*e.g.*, papers and plastics), which is otherwise not easy to be realized with conventional inorganic materials [12, 16].

Depending on the sequence in which different layers are deposited, there are mainly four different OTFT architectures as shown in Figure 1.3. The OTFT can be implemented on

**Figure 1.3** Schematic cross-section views of (a) Bottom gate bottom contact (BGBC) (b) Bottom gate top contact (BGTC) (c) Top gate bottom contact (TGBC) and (d) Top gate top contact (TGTC) OTFT.

**Figure 1.4** The development of the field-effect carrier mobility ( $\mu$ ) in some common *p*- and *n*-type semiconductors over the past decades [14].

an insulating substrate (*e.g.*, glass or plastic substrate), while an organic semiconductor material is used as a channel layer (which is also called the active layer), and inorganic and/or organic conducting materials are used for the gate and source/drain electrodes. Different OTFT structures as shown in Figure 1.3 have pros and cons [17]. The majority of OTFTs follows the bottom gate structure (Figures 1.3(a) and (b)) for the following reasons: (1) The deposition of organic semiconductor layer after the gate dielectric provides a wider process window for the growth of the high quality dielectric layer (that requires high temperature deposition or thermal treatment) without degrading the sensitive active layer [14]; (2) The deposition and patterning of the metal gate (that could involve high temperature treatments and require organic solvents) might contaminate the organic active layer underneath when the gate electrode is formed in the last step [12].

Figure 1.4 demonstrates the increase in field-effect carrier mobility ( $\mu$ ) of both *p*- and *n*type semiconductors over the past decades. In fact, much research has been performed in order to improve such a relatively low mobility (< 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> typically) of organic semiconductors and thus to improve the performance of OTFT [12-15]. This is because the drain current-gate voltage ( $I_d$ - $V_g$ ) characteristics and intrinsic delay ( $f_t$ ) of OTFT depend on the  $\mu$  of the semiconductor layer:

$$I_{d} = \frac{W}{L} C_{dep} \mu \left( V_{g} - V_{t} - \frac{V_{t}}{2} \right) V_{d} \qquad (\text{When } V_{d} \le V_{g} - V_{t} )$$

(1-1)

or

$$I_{d,sat} = \frac{W}{2L} C_{dep} \mu (V_g - V_t)^2$$

(When  $V_d > V_g - V_t$ ) (1-2)

$$f_t \propto \frac{W}{2L} \mu \left( V_{\rm g} - V_{\rm t} \right) \tag{1-3}$$

where  $C_{dep}$  is the capacitance of the depletion layer,  $V_d$  is the applied drain voltage,  $V_g$  is the applied gate voltage,  $V_t$  is the threshold voltage, and W and L are channel length and width, respectively. High  $\mu$  is strongly desirable in order to manufacture OTFT with high on-state current  $I_{d,sat}$  [5, 18] and low signal propagation delay [12, 14, 19].

Another challenge that hinders the wide adoption of OTFT technology is related to the gate dielectric layer [20]. Gate dielectric layer is of importance because: (1) The gate dielectric prevents the leakage current between the gate and semiconductor layers [21]; (2) The gate dielectric serves as a passivation layer, which can protect the semiconductor layer in the case of the top gate structure, *i.e.* TGBC and TGTC OTFTs shown in Figure 1.3 [22]; (3) The charge carrier accumulation at the interface of semiconductor layer/dielectric is significantly affected by the properties of gate dielectric, *i.e.* morphology, surface condition, the constant, and the thickness of the dielectric layer [23].

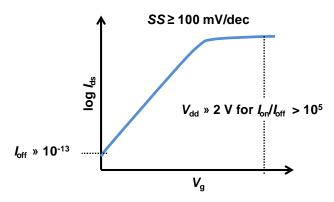

Figure 1.5 The conceptual  $I_{ds}$ - $V_g$  characteristic of OTFT device showing the limited performances.

Generally speaking, large gate oxide capacitance ( $C_{ox}$ ) is desirable to achieve a steep subthreshold swing (SS) [24-26]:

$$SS = \ln 10 \times \frac{k_{\rm B}T}{q} \left( 1 + \frac{C_{\rm dep}}{C_{\rm ox}} \right)$$

(1-4)

where  $k_{\rm B}$  is the bolzman constant, *T* is the temperature, *q* is the elementary charge,  $C_{\rm dep}$  is the capacitance of the depletion layer, and  $C_{\rm ox}$  is the capacitance of dielectric layer. *SS* is fundamentally limited to be  $\ln 10 \times k_{\rm B}T/q = 60$  mV/dec at room temperature and is typically greater 100 mV/dec for state-of-the-art OTFTs [27, 28].

To achieve a flexible OTFT, a suitable conducting polymer should be used as the electrode layer. So far, Poly(3,4-ethylenedioxythiophene):poly(styrenesulfonate) (PEDOT:PSS) [29] and PANI (polyaniline blends) [30] are the most widely used conducting polymers for the formation of electrodes in OTFTs. However, the relatively low conductivity (~1  $\Omega$ ·cm), air instability, and processing complexity make the use of conducting polymers for the realization of fully rollable OTFTs challenging.

There are several critical challenges for the application of OTFTs in organic electronics as shown in the typical  $I_{ds}$ - $V_g$  curve of OTFT in Figure 1.5: (1) Organic semiconductors have a relatively low field-effect carrier mobility  $\mu$  (well below 20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) [12-15]. Therefore, OTFTs tend to exhibit rather limited performance, e.g. V<sub>dd</sub> well above 2 V (typically much above 10 V) is required to achieve reasonable on/off current ratio (>  $10^5$ ) [5, 18] and switching frequency (> 1 MHz) [12, 14, 19]. The large  $V_{dd}$  can lead to large amounts of dynamic power consumption; (2) Due to poor semiconductor/dielectric interface quality [24-28, 31], OTFTs show relatively large off-state leakage current (I<sub>off</sub> is typically well above 10<sup>-13</sup>), which would be exacerbated for small device dimensions in more intensive integrated circuits, particularly if a thin gate insulator is used to achieve a steep SS, which is well above 100 mV/dec [27, 28]. The large  $I_{\text{off}}$  can lead to large amounts of static power dissipation; (3) The large power consumption issue becomes aggravated at the circuit level as *p*-type OTFTs usually far outperform *n*-type OTFTs due to the fact that the  $\mu$  of most p-type organic semiconductor is better than that of the n-type organic semiconductor and the air stability of most *n*-type OTFTs remain unsolved, all these factors makes it difficult to achieve complementary operations [14, 20]. While much work has been done to provide improved or new polymers and polymeric composites for active layers or gate dielectric layer or electrode layer in order to improve the performance of OTFTs [5, 18, 32-36], little work has yet been done (particularly at the transistor level) to reduce the overall power consumption in order to realize low power consumption of IoT electronics.

#### **1.2. New Insight: Organic Microelectromechanical Relay Technology**

Mechanical relays for computing was conceptualized by George Stibitz in 1930 [37]. With the advance of modern planar processing technology and micro-electro-mechanical systems (MEMS) technology over the past decades, it has become possible to fabricate miniaturized relays and integrate them on a single chip. The first micro-electro-mechanical (MEM) relay that turns on/off abruptly by making or breaking physical contact of two electrodes was demonstrated by Petersen in 1979 [38]. Such an abrupt switching behavior leads to high  $I_{on}/I_{off}$  ratio for a small given gate-voltage swing, and the existence of the air gap between contacting electrodes allows zero  $I_{off}$ . Recently, various MEM relay designs (such as laterally- [39-44] or vertically-driven relay structures [45, 46]) for logic application has been proposed to overcome the energy crisis of CMOS technology.

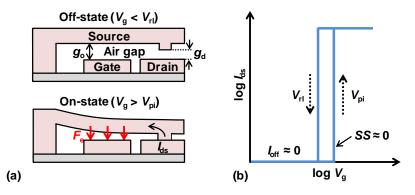

Figure 1.6 shows the structure of a simplified 3-terminal (3-T) MEM relay and the corresponding conceptual  $I_{ds}$ - $V_g$  characteristic. The movable source of the MEM relay stands on the substrate and it forms a parallel plate capacitor with a fixed gate electrode underneath (Figure 1.6(a)). When  $V_g < V_{rl}$ , the relay is in the off-state, where there is an air gap between the source and drain electrodes preventing the current flow  $I_{ds}$ . As a result, the MEM relay has zero  $I_{off}$  as shown in Figure 1.6(b). When  $V_g > V_{pi}$ , the  $F_e$  between the source and gate electrodes attracts the movable source electrode towards the fixed gate electrode. The source then meets with the drain underneath abruptly. Therefore, the electrical contact is made and  $I_{ds}$  flows. The SS of the relay can be very close to zero, which enables the possibility of small applied voltage swing.

**Figure 1.6** (a) Schematic illustration of a simplified 3-terminal (3-T) MEM relay. In the off-state ( $V_g < V_{rl}$ ),  $V_{rl}$  is called the release voltage of the relay. The presence of air gap between source and drain electrodes prevents current flow  $I_{ds}$ , which results in zero off-state leakage. Actuation gap ( $g_o$ ) is the air gap thickness between the source and gate. Dimple gap ( $g_d$ ) is the air gap thickness between source to drain. In the on-state ( $V_g > V_{pi}$ ),  $V_{pi}$  is called the pull-in voltage of the relay. The electrostatic actuation force ( $F_e$ ) induced by the gate and source electrodes attracts the source to move downward so that the electrical contact between the source and drain is made, current flow  $I_{ds}$  is therefore formed, which leads to abrupt on-state transition. (b) The conceptual  $I_{ds}-V_g$  characteristic of MEM relay showing the relay has zero off-state leakage, it can turn on and off abruptly by a small gate-voltage swing with  $SS \approx 0$ . The hysteretic switching behavior ( $V_{pi}-V_{rl}$ ) is due to pull-in mode operation and surface adhesion force ( $F_a$ ) [39].

MEM relay could be considered as a promising switching device since it can provide zero static power consumption, potentially ultralow dynamic power consumption, and complementary switching operations. Specifically, a relay shows abrupt on/off transition behavior. *i.e.* when  $V_g \ge V_{pi}$  is applied, the movable structure will be abruptly actuated to bring the source contact with drain electrode due to the induced electrostatic actuation force, and current can flow thereby, and when  $V_g \le V_{rl}$ , the spring restoring force ( $F_{sp}$ )

will bring the source out of contact with the drain electrode abruptly. As a result, relay can be made to operate with very low  $V_{dd}$  than OTFT in principle since the SS of relay is less than 0.1 mV/dec [47], while that of OTFT is typically well above 100 mV/dec [27, 28]. Relay has immeasurable low  $I_{off}$  and high on/off current ratio because the actuation air gap separates the source and drain when the device is in off-state, but the OTFT has relatively large leakage current due to poor semiconductor/dielectric interface quality and it consumes large static power consequently [31]. Due to the ambipolar nature of the electrostatic actuation force, it is always an attractive force between the movable electrode and fixed electrode regardless of the polarity of the applied voltage. Therefore, the advantage of electrostatic actuation switching behaviors of relay enables the symmetric pairs of n- and p-type relays for complementary operation. But complementary switching is still difficult to be realized by OTFTs simply due to the outperformance of p-type OTFTs to n-type OTFTs and the air instability of most n-type OTFTs [14, 20].

On top of the above intrinsic benefits of the MEM relay, an organic MEM relay could be compelling for the implementation of organic electronics with low power consumption and low manufacturing costs. Relay is operated by the electrostatic actuation of a movable electrode structure rather than by modulating the conductivity of a fixed semiconducting channel. Therefore, the performance of organic MEM relays will not be restricted by the limit of the relatively low  $\mu$  of organic semiconductors. It is desirable to create relay with low effective spring constant ( $k_{eff}$ ) to lower the switching energy needed to turn on the device [39]. The  $k_{eff}$  of the structural beam is proportional to Young's modulus (*E*) of materials, and the threshold voltage (and hence operating voltage) of relays are proportional to  $E^{0.5}$ . Note that the *E* values of most organic materials are approximately two orders of magnitude lower than those of inorganic materials [48]. Along with zero leakage current, potentially very low operation voltage of organic MEM relays could make them appealing for ultralower-power applications. In addition, various polymers and/or light sensitive photoresists are commonly used in MEMS for mechanical structures/support or sacrificial layers [48]. They can be deposited via simple low-cost/-temperature methods (e.g., spin coating), unlike inorganic materials requiring relatively complicated film deposition- or etching-steps [49].

Organic MEM relay that could incorporate the advantages of mechanical relay structures, the salient properties of organic materials, and the low-temperature/-cost material processing, would be a promising candidate as the building block for ultralow power flexible, transparent, and large area electronics used in IoT.

#### **1.3. Organization of the Dissertation**

This Ph.D. dissertation aims to address challenges for achieving organic MEM relay technology that could be a promising alternative to OTFT for ultralow-power, flexible, transparent and large-area electronics.

Chapter 2 begins with the working principle of MEM relay. Then the prototype organic relay design is presented. Lastly, versatile multiple-input/-output relays including single-gate dual-body relay and dual-gate dual-body relay are introduced.

Chapter 3 discusses the fabrication process and materials to realize the implementation of organic MEM relays. The requirement, selection, and evaluation of the materials used for this work as well as fabrication challenges encountered and solution are presented.

Chapter 4 presents the characterizations of fabricated organic MEM relays. Static switching characteristics including  $I_{ds}-V_{gb}$ ,  $I_{ds}-V_{ds}$ , body biasing effect, complementary switching, and hysteretic switching behavior, and dynamic performance including turnon and turn-off switching delays are completely investigated. Endurance testing results show that organic MEM relays can endure a finite number of hot- and cold-switching cycles. The effects of temperature and humidity on switching characteristics (such as  $I_{ds}$ - $V_{gb}$ , hysteresis voltages and on-state resistance) are studied. A dual-gate dual-body organic MEM relay that can perform basic logic functions and can generate a carry for four input bits is also is demonstrated.

Chapter 5 summarizes the key results and contributions of this dissertation.

## 2. Organical Relay Design and Simulation

MEM relay can be used to implement low-power organic electronics for IoT applications due to its unique behaviors such as abrupt on/off switching behavior that allows  $V_{dd}$  to be close to 0 V for low dynamic power consumption and zero off-state leakage current for zero static power consumption. Section 2.1 begins with a description of the structure and operation principle of a typical 4-Terminal (4-T) relay; this design has been proved to serve as a basic building block for various digital logic circuits including logic gates, clocking, memory circuits, adder and multipliers [43, 47, 50-54]. Based on this, the development of the organic MEM relay is discussed in Section 2.2, followed by the improvements made to the prototype (in Section 2.3).

#### 2.1. Microelectromechanical Relay Structures and Operation Principle

The design of electromechanical relays is based on the mechanical motion of the movable structure that makes or breaks the physical contact between two electrodes in order to turn on or off [37, 55]. Two types of movable structures typically used in MEM relays are based on cantilever [56, 57] or clamped-clamped beam structures [44, 58, 59]. The cantilever beam has a fixed base (called "anchor") on either side, and the buckled clamped-clamped structure has fix bases (anchors) at both sides. These two types of movable structures have advantages and disadvantages. Cantilever beam is relatively easier to fabricate than clamped-clamped beams but might not have sufficient spring restoring force ( $F_{sp}$ ) that ensures the reliable turning-off of the relay. Clamped-clamped beam could be more complicated to manufacture, but provides more reliable  $F_{sp}$  to turn

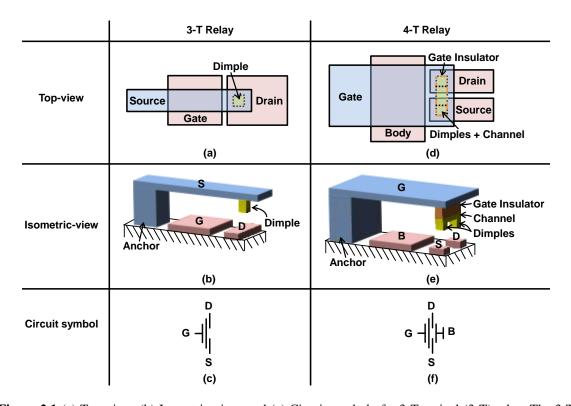

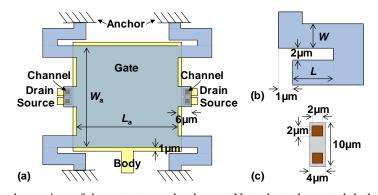

**Figure 2.1** (a) Top-view, (b) Isometric-view, and (c) Circuit symbol of a 3-Terminal (3-T) relay. The 3-T relay comprises three terminals: a movable source, a gate, and a drain. The source electrode has one protruding region, referred to as dimple. The dimple restricts the motion of the movable source when it contacts the drain. (d) Top-view, (e) Isometric-view, and (f) Circuit symbol of a 4-Terminal (4-T) relay. The 4-T relay comprises four terminals: a movable gate, a body, a source, and a drain. The channel beneath the gate insulator has two protruding regions, referred to as dimples. The dimples restrict the motion of the movable gate when they contact the corresponding source and drain.

off the relay. Depending on the number of terminals of a MEM relay, relay can be defined as 3-terminal (3-T) or 4-terminal (4-T) as summarized in Figure 2.1. Note that MEM relays mimic the field-effect transistors (FETs) in that they also have the gate, body, and source/drain electrodes. The conductive contact dimple defines physical contacting regions. The anchor that stands on the substrate is the fixed base of the

cantilever beam.

The 3-T relay comprises three terminals: a movable source, a gate, and a drain (Figures 2.1(a), (b), and (c)). The dimple restricts the motion of the movable source when it contacts the fixed drain underneath. The electrostatic actuation force ( $F_e$ ) that turns on or off the relay is controlled by the voltage difference between gate and source ( $V_{gs}$ ), and the on-state current ( $I_{on}$ ) that equals to  $I_{ds}$  is determined by the voltage between source and drain ( $V_{ds}$ ). Nevertheless, the main disadvantage of 3-T relay occurs when several 3-T relays are used in a series circuit, in which the source of the first relay is connected to GND, and the drain goes to the source of the second relay. In this case, only the first relay can be operated reliably once certain gate voltage is applied to it since the electrostatic actuation is induced by  $V_{gs}$  and the source voltage ( $V_s$ ) of the first relay equals 0 V. However, the source of the second relay is connected to the drain of the first relay. As a result, the  $V_{gs}$  of the second relay is not a stable input which leads to unreliable circuit operation.

An additional terminal (body electrode) can be added to the 4-T relay (Figures 2.1(d), (e), and (f)) to address the aforementioned issues of the 3-T relay. The 4-T relay comprises four terminals: a movable gate, a gate, a source, and a drain. The channel and the gate insulator are attached under the gate electrode, and they move together with the gate electrode during electrostatic actuation. The dimples restrict the motion of the movable gate when they contact the corresponding source and drain.  $F_e$  is now induced by the voltage applied between gate and body ( $V_{gb}$ ) instead of  $V_{gs}$ . Once the relay is actuated, the movable gate structure will bring the two dimples with channel and gate insulator into contact with the corresponding source and drain electrodes underneath. The channel behaves like a bridge connecting the source and drain when the relay turns on (dimples meet the corresponding source and drain electrodes). The function of the gate insulator is to block the conductive channel from the gate electrode. Therefore, current only flows within the channel, between source to drain electrodes, not to the gate electrode once the relay is in the on-state. In a word, vertically, the turn-on voltage is reliably controlled by  $V_{\rm gb}$  independently regardless of the applied source or drain voltage, horizontally, the  $I_{\rm ds}$  is determined by  $V_{\rm ds}$ . Apart from that, the 4-T relay allows operation with reduced gate-voltage swing by applying a body bias [53], which will be discussed in-depth in Chapter 4 of the relay characterizations.

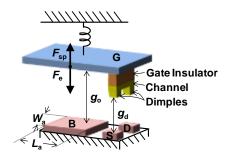

Figure 2.2 shows the spring model of a 4-T MEM relay to illustrate the operation principle. As for the 4-T MEM relay design, a movable gate electrode forms a parallel plate capacitor with a fixed gate electrode underneath. When the relay is in the off-state, there is an air gap between the dimples and source/drain electrodes underneath, which prevents the current flow  $I_{ds}$ . Once a voltage is applied to the capacitor, *i.e.*  $V_{gb} > V_{pi}$  (pull-in voltage of the MEM relay), the  $F_e$  introduced between the gate and body electrodes moves the suspended movable gate stack downward. The movable gate brings the channel into contact with the source and drain to conduct current.  $F_e$  is given as a function of the displacement (*x*) of the movable structure [60]:

$$F_{\rm e}(x) = \frac{\varepsilon_{\rm o} W_{\rm a} L_{\rm a} V^2}{2(g_{\rm o} - x)^2}$$

(2-1)

where  $\varepsilon_0$  is the permittivity of free space,  $g_0$  is the actuation gap, and  $W_a$  and  $L_a$  are the width and the length of the actuation area, respectively.

The spring restoring force  $(F_{sp})$  begins to increase once the movable gate is actuated downward.  $F_{sp}$  is the balancing force of  $F_e$  and it is proportional to *x* of the movable beam [60]:

$$F_{\rm sp}(x) = k_{\rm eff} x \tag{2-2}$$

where  $k_{\text{eff}}$  is the effective spring constant.

At equilibrium state,  $F_e$  is equal to  $F_{sp}$  [60]:

$$\frac{\varepsilon_{\rm o} W_{\rm a} L_{\rm a} V^2}{2(g_{\rm o} - x)^2} = k_{\rm eff} x$$

(2-3)

Note that  $F_e$  increases parabolically with x while  $F_{sp}$  increases linearly with x. The fact that  $F_e$  is bigger than  $F_{sp}$  keeps moving the suspended beam downward. As the beam continues to travel, there exist a critical point beyond which  $F_e$  is always greater than  $F_{sp}$ , and the beam is snapped down abruptly. This phenomenon is referred to as the "pull-in" effect [39, 60]. By analyzing Equation (2-3), one can solve that  $x = \frac{1}{3}g_o$  is the critical point where the movable beam has travelled by  $\frac{1}{3}g_o$ . The voltage at this critical point,

**Figure 2.2** Spring model of the electrostatically actuated 4-T MEM relay. The air gap thickness between gate and body is called the actuation gap  $(g_0)$ . The air gap thickness between the dimples and corresponding source and drain is referred to as the dimple gap thickness  $(g_d)$ . The width and length of the body electrode are  $W_a$  and  $L_a$ , respectively. When  $V_{gb}$  is applied, the electrostatic actuation force  $(F_e)$  induced by the body and gate electrodes moves the suspended gate electrode together with the channel and gate insulator downward. The balancing force is the spring restoring force  $(F_{sp})$  of the movable gate. If  $F_e > F_{sp}$ , the movable gate brings the channel into contact with the source and drain to conduct current, which leads to abrupt on-state transition. The channel beneath the gate insulator has two protruding regions, referred to as dimples. The dimples restrict the motion of the movable gate when they contact the corresponding source and drain.

which triggers the on-state of the relay, is referred to as  $V_{pi}$  [39, 60]:

$$V_{\rm pi} = \sqrt{\frac{8k_{\rm eff} g_{\rm o}^{3}}{27\varepsilon_{\rm o}W_{\rm a}L_{\rm a}}} \tag{2-4}$$

As shown in Figure 2.2, the relay employs dimples to make physical contact with the source and drain electrodes. As discussed above, the "pull-in" effect exists when  $x = \frac{1}{3}g_o$ . If  $g_d \ge \frac{1}{3}g_o$ , the relay operates in pull-in mode. If  $g_d < \frac{1}{3}g_o$ , the relay operates in nonpull-in mode [39, 60]. One can choose the operation mode of the MEM relay by adjusting the ratio of  $g_0$  and  $g_d$ , respectively.

The  $V_{pi}$  of a relay operating in pull-in mode can be expressed as [39, 60]:

$$V_{\rm pi} = \sqrt{\frac{8k_{\rm eff} g_o^3}{27\varepsilon_{\rm o}A_{\rm o}}} \quad \text{where } g_{\rm d} \ge \frac{1}{3}g_o \tag{2-5}$$

where  $k_{\text{eff}}$  is the effective spring constant of the movable structure,  $A_0$  is the overlap area between the movable structure and the fixed electrode, which is the effective actuation area. Note that the effective actuation area equals to the size of body electrode ( $W_a \times L_a$ ) as shown in Figure 2.2.

For a relay operating in non-pull-in mode, the on-state occurs when  $x = g_d$ , and the non-pull-in voltage ( $V_{npi}$ ) can be given by [39, 60]:

$$V_{\rm npi} = \sqrt{\frac{2k_{\rm eff} \left(g_{\rm o} - g_{\rm d}\right)^3}{\mathcal{E}_{\rm o} A_{\rm o}}} \quad \text{where } g_{\rm d} < \frac{1}{3}g_o, \qquad (2-6)$$

When the contact is made, the force balance equation is given by [39, 60]:

$$F_{\rm e} + F_{\rm a} = F_{\rm sp} \tag{2-7}$$

where  $F_a$  is the surface adhesion force when two contact surfaces meet [39, 61].

Substituting Equations (2-1) and (2-2) into (2-7), the force balance equation becomes [39, 60]:

$$\frac{\varepsilon_{\rm o}A_{\rm o}V^2}{2(g_{\rm o}-x)^2} + F_{\rm a} = k_{\rm eff} x$$

(2-8)

To turn off the relay,  $F_{sp}$  needs to be large enough to overcome  $F_e$  and surface adhesion force  $F_a$ . A smaller voltage than  $V_{pi}$  (or  $V_{npi}$ ) needs to be applied. By replacing  $x = g_d$  into Equations (2-8), the release voltage ( $V_{rl}$ ) is solved as [39, 60]:

$$V_{\rm rl} = \sqrt{\frac{2(k_{\rm eff} g_{\rm d} - F_{\rm a})(g_{\rm o} - g_{\rm d})^2}{\varepsilon_{\rm o} A_{\rm o}}}$$

(2-9)

Note that  $V_{\rm rl}$  sets the lower limit for the relay supply voltage scaling [39].

# 2.2. Prototype Organic Relay

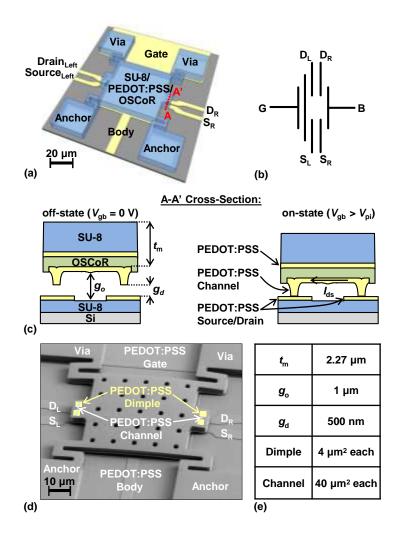

Figure 2.3 presents an isometric schematic, the circuit symbol, cross-section view, scanning electron micrographs (SEM), and the design parameters and values of the prototype fully-polymeric MEM relay. This MEM relay comprises six terminals: a movable gate stack, a body, and two pairs of source/drain on both sides. The operation of the organic MEM relay is similar to that of 4-T relay as introduced in Section 2.1, in which the current flow between the source and drain ( $I_{ds}$ ) on either side is controlled by  $V_{gb}$ . The relay comprises a fully polymer-based movable structure suspended by serpentine springs above source, drain, and body electrodes. Along with vias, the conductive polymer, Poly(3,4-Ethylenedioxythiophene):Polystyrene-Sulfonate (PEDOT:PSS) (attached above an insulating polymer that serves as the gate dielectric) connects the gate electrodes to the movable structure. Note that the etch holes (4  $\mu$ m<sup>2</sup>) are

**Figure 2.3** (a) Schematic view of the prototype organic MEM relay. The movable stack comprises different dielectric (SU-8 and OSCoR) and conductive (PEDOT:PSS) polymer materials, the stack is electrically connected to the gate electrode through the vias. (b) Circuit symbol of the relay. (c) A-A' cross-section view of the relay. Off-state: an air gap prevents current to flow between the source and drain on either side. On-state: electrostatic actuation force between the gate and body brings both channels into contact with the pairs of source and drain. (d) SEM of the relay. (e) Design parameters. Note that 4  $\mu$ m<sup>2</sup> etch holes are patterned onto the gate stack in order to ensure release of the relay by vapor HF and to reduce residual stress of the gate stack [62].

patterned on the gate stack in order to ensure release of the relay by vapor-phase hydrogen fluoride (HF) and to reduce residual stress of the gate stack [62]. In order to provide sufficient charge for the actuation of the structure,  $V_{gb}$  is applied to induce  $F_e$  on the movable structure and actuates the gate stack downward toward the body (shown in Figure 2.3). As  $V_{gb}$  across the actuation gap ( $g_0$ ) increases,  $F_e$  between the gate and body increases parabolically, while the spring restoring force  $(F_{sp})$  of the folded-flexures increases linearly. When the magnitude of  $F_{e}$  exceeds that of  $F_{sp}$ , the movable gate snaps down abruptly, and the conductive polymer channel (underneath a polymer gate dielectric) is brought into contact with the pair of source and drain on either side to conduct current. Because the prototype relay is designed to operate in pull-in mode,  $V_{pi}$  at which the movable stack pulls can be expressed as Equation (2-5). When  $V_{gb}$  is lowered below  $V_{\rm rl}$  (Equation (2-9)),  $F_{\rm sp}$  becomes large enough to overcome  $F_{\rm e}$  and  $F_{\rm a}$ . Thus, the contacts of the dimples to source and drain electrodes on both sides are broken, and the relay turns off. Note that the fringing capacitance, actuation area reduction due to the release holes and the bending of the actuation plate are assumed to be negligible.

Based on the design as shown in Figure 2.3, several key design parameters are summarized as follow: (1) The relay is designed to work in pull-in mode with  $g_0 = 1 \,\mu m$ ,  $g_d = 500 \,\text{nm}$ , and  $g_d/g_0 = 0.5$  because pull-in operation is found to be preferred for optimal energy efficiency [59].  $V_{pi}$  of the relay is therefore determined by  $g_0$  according to Equation (2-5); (2) The relay has a clamped-clamped structure with four bases (anchors) on both side of the movable beam. As mentioned in section 2.1, unlike the cantilever design that suffers from insufficient spring restoring force, the buckled clamped-clamed

beam should produce reliable restoring force to turn off the relay once the electrostatic actuation is revoked; (3) There are four symmetric folded-flexures as serpentine springs to suspend the movable beam while there are only two strain springs to suspend the beam in the conventional clamped-clamped structure. The main benefit of adding extra springs to the overhanging beam is for minimizing the possibility of rotating the beam torsionally during electrostatic actuation; (4)  $k_{eff}$  of the relay depends on the design parameters of the folded-flexures attached to the movable beam [59]; (5) The  $A_0$  between the suspended gate electrode and the fixed body electrode is defined by the size of gate electrode. By changing the dimensions of the gate electrode, the  $A_0$  can be changed, which in turn affects  $F_{e}$ ; (6) Gate leakage current to the body could happen if the bottom of the gate stack is not protected by gate dielectric. Once high gate voltage is applied, the relay is catastrophically pulled in (i.e., the whole gate stack collapses onto the substrate). As a result, huge current could flow from the gate to body, which leads to device failure [39, 60]. To address this issue, the entire bottom of the gate stack of the prototype organic MEM relay is covered with thick (~200 nm) organic gate dielectric to prevent any possible short circuit; (7) The gate dielectric can be patterned together with the whole gate stack and it is a self-aligned process; (8) Two dimples along with a channel underneath both sides of the suspended plate have two main functions. Firstly, one pair of dimples and the channel provide the electrical path once dimples meet with the source and drain electrodes on both sides. Secondly, the dimples reduce the possibility of "catastrophic" pull-in, this "foot" issue is especially common on relay without dimple [39, 60].

# 2.2.1. Electrode Engineering

Overall, the organic relay structure consists of three parts: bottom electrodes, a movable gate stack, and an air gap between the bottom electrodes and the stack. Figure 2.4(a) shows the layout of the prototype organic MEM relay, it has one gate, one body, and two pair of source and drain electrodes. The total footprint is  $412 \times 400 \ \mu\text{m}^2$  for the prototype relay. Conservatively, large electrode pads area of  $100 \times 100 \ \mu\text{m}^2$  and large minimal space of 38  $\mu$ m between adjacent pads are used in the layout. These areas consume relatively large footprint but provide enough space to locate probe tips during device characterizations. In fact, the large pads ( $100 \times 100 \ \mu\text{m}^2$  each) make up 40 % of the total device area in the prototype relay design.

Figure 2.4(b) shows the zoom-in view of the channel and dimple region. The width of the wire routing is decreased from 6  $\mu$ m to 5  $\mu$ m. The minimal distance of 2  $\mu$ m between source and drain electrodes is set in order to prevent undesirable surface leakage, which is conservative larger than the minimum feature size (1  $\mu$ m) of the photolithography tools (Karl Suss MA6 Mask Aligner and Karl Suss MJB3 Mask Aligner) used for this work.

The relay is anchored to the electrode layer by four vias and two of the vias form electrical connection from the gate electrode to the conductive PEDOT:PSS layer in the gate stack as shown in Figure 2.4(c). The size of anchor is  $40 \times 40 \ \mu\text{m}^2$ . The size of via is  $38 \times 38 \ \mu\text{m}^2$ . Because the conductive organic material PEDOT:PSS has a finite conductivity, relatively large-area vias are used to lower the resistance of each via.

**Figure 2.4** (a) Layout of the prototype relay. The minimum size of electrode pad is  $100 \times 100 \ \mu\text{m}^2$ , that is conservative large to place probe tip for relay electrical characterizations. The minimum space between electrode pads is 38  $\mu$ m, that is set in order to conservatively place separate probe tips on two adjacent electrode pads. The relay is anchored by four anchors on PEDOT:PSS substrate. Two vias enable connection from the conductive layer (PEDOT:PSS) in the gate stack to the gate electrode. (b) Zoomed-in view showing channel and dimple region, the spacing between the source and drain electrodes is set to 2  $\mu$ m to prevent surface leakage. (c) Zoomed-in view showing relay is anchored on PEDOT:PSS substrate. The size of the anchor is  $40 \times 40 \ \mu\text{m}^2$ , that is conservative large to provide enough reliability. The size of via is  $38 \times 38 \ \mu\text{m}^2$ . The gate electrode is connected to the conductive layer in the gate stack through two vias.

Note that  $V_{pi}$  can be reduced effectively by adjusting the body bias in order to allow for operation with a lower gate-voltage swing [53, 63]. Ideally, a change in the  $V_b$  results in commensurate change to the gate switching voltages  $V_{pi}$  and  $V_{rl}$ . *i.e.*, a 1 V voltage change in  $V_b$  should result in a 1 V change in  $V_{pi}$ . To validate the prototype organic relay design, Finite-Element-Analysis (FEA) was performed using simulation software (CoventorWare). Figure 2.5(a) shows the simulated  $V_{pi}$  of the organic relay that operates

**Figure 2.5** The relay used in the FEA simulation has  $W = 3 \mu m$ ,  $L = 7 \mu m$ ,  $W_a = L_a = 57 \mu m$ ,  $g_o = 1 \mu m$ ,  $g_d = 500 nm$  and  $t_m = 2.27 \mu m$ .  $V_d$  and  $V_s$  were set to 0 V in the simulation. (a) When  $V_b = 0$  V, the relay is actuated downward by ~350 nm ( $\approx 1/3g_o$ ) at  $V_g \approx 21.06$  V =  $V_{pi}$ , then it turns on abruptly. (b) When body bias  $V_b = -5$  V, the relay turns on at  $V_g \approx 16.21$  V =  $V_{pi}$ . (c) The relay turns on at  $V_b \approx 22.03$  V =  $V_{pi}$  and  $V_g = 0$  V. The number of volume element mesh created of the simulation was 25162 and displacement tolerance was set to be 0.001 µm.

in pull-in mode ( $g_0 = 1 \ \mu m$ ,  $g_d = 500 \ nm$ , and  $g_d/g_0 = 0.5$ ) without body bias. When  $V_g = 21.06 \ V$  is applied,  $F_e$  brings the movable beam downward. The maximum displacement of the suspension beam reaches 350 nm ( $\approx 1/3g_0$ ) before the relay turns on abruptly. This

result confirms that once the movable beam passes the critical point ( $g_0/3$ ), the movable beam suddenly snaps down, and relay turns on. Figure 2.4(b) presents that the simulated  $V_{pi}$  is 16.61V with  $V_b = -5$  V. Compared with the  $V_{pi}$  without body bias in Figure 2.4(a), this result verifies the effective adjustment of  $V_{pi}$  for the relay with body bias, *i.e.* a commensurate change to  $V_{pi}$  with a change in body bias.

Due to the nature of the electrostatic actuation force, it is always an attractive force between the movable gate electrode and fixed body electrode regardless of the polarity of the applied  $V_{gb}$ . As demonstrated in Figure 2.3(c), the simulated  $V_{pi}$  value of the relay that is actuated by the body-to-gate voltage is 22.03 V, which is consistent with the  $V_{pi}$  of the relay that is actuated by the gate-to-body voltage.

## 2.2.2. Air Gap Engineering

The air gap of the relay is important because: (1) The air gap physically separates the movable gate from the underneath body electrode and the channel from the underlying source and drain electrodes in the off-state; (2) The strength of the induced electrostatic force between the gate and body electrodes is affected by the thickness of the air gap, *i.e.*  $F_{\rm e} \propto 1/g_0^2$  [39]; (3) The ratio of  $g_0$  and  $g_d$  defines the operation mode of the relay.

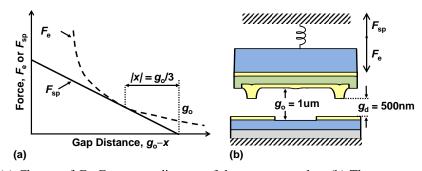

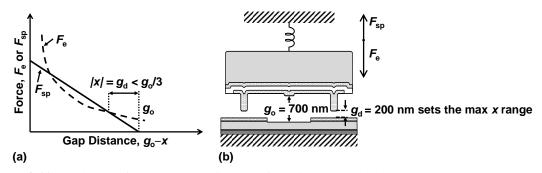

Figure 2.6 shows the change of  $F_e$  and  $F_{sp}$  during the mechanical motion of the movable gate and the cross-section view of the prototype relay to illustrate the transition from the off-state to the on-state. The vertical dimension of the prototype relay is designed as  $g_o =$ 1 µm,  $g_d = 500$  nm, and  $g_d/g_o = 0.5 > 1/3$ . From the prospect of most energy-efficient operation, the dimple gap should be one-half of the actuation gap [39].  $F_{sp}$  is provided by

**Figure 2.6** (a) Change of  $F_{e}$ ,  $F_{sp}$  vs. gap distance of the prototype relay. (b) The cross-section view of the prototype relay. The ratio of  $g_d$  and  $g_o$  is 0.5, that is greater than 1/3. The relay operates in pull-in mode. The movable gate snaps down abruptly after it travels to  $x = g_o/3$ ,  $F_e$  is always greater than  $F_{sp}$  after the movable gate moves beyond  $g_o/3$ .

the folded-flexures of the relay which behave like a serpentine spring.  $F_e$  is induced by  $V_{gb}$ . Initially, x = 0, neither  $F_{sp}$  nor  $F_e$  exists. Once  $V_{gb}$  is applied to the relay,  $F_e$  is induced. According to Equation (2-1),  $F_e$  increases parabolically with x as indicated by the dash-line in Figure 2.6(a). Because the movable stack moves downward,  $F_{sp}$  starts to exist and it increases linearly with x according to Equation (2-2).  $F_{sp}$  is shown as the solid line in Figure 2.6(a). As long as  $V_{pi}$  is applied that enables  $F_e > F_{sp}$ , the gate stack continues to move downward till the critical point  $x = g_0/3$ , where  $F_e = F_{sp}$ . Because  $g_d > g_0/3$ , the dimples do not contact the source and drain electrodes underneath at this moment, relay keeps moving downward. However, once the relay passes the critical point  $(g_0/3)$ ,  $F_e >> F_{sp}$ , the movable stack suddenly snaps down, the dimples meet with the source and drain electrodes underneath, and therefore the relay turns on.

### 2.2.3. Gate Stack Engineering

The details of the gate structure design are shown in Figure 2.7. One of the advantages of the 4-T relay design is that the flexure structures and the actuation area are decoupled, *i.e.*, the  $k_{\text{eff}}$  is only determined by the folded-flexures dimensions (the movable beam is considered as a rigid plate) and the actuation area is defined by the area of the suspended gate stack. As indicated in Equation (2-5) and (2-9), both  $V_{\text{pi}}$  and  $V_{\text{rl}}$  are proportional to  $\sqrt{k_{\text{eff}}}$ .  $k_{\text{eff}}$  is determined by the dimensions of the folded-flexures, the intuitive expression of  $k_{\text{eff}}$  is given by [39, 60]:

$$\frac{1}{k_{\text{eff}}} \cong \left(\gamma_{\text{f}} \frac{E_{eq} W t_{m}^{3}}{L^{3}}\right)^{-1} + \left(\gamma_{\text{t}} \frac{G_{eq} W t_{m}^{3}}{L}\right)^{-1}$$

(2-10)