# WIRELESS ELECTRICAL STIMULATORS FOR NANOFIBERS WITH APPLICATION IN NEXT GENERATION MUSCLE PROSTHESIS

**BY YI HUANG**

A dissertation submitted to the

Graduate School—New Brunswick

Rutgers, The State University of New Jersey

in partial fulfillment of the requirements

for the degree of

**Doctor of Philosophy**

Graduate Program in Electrical and Computer Engineering

Written under the direction of

Professor Laleh Najafizadeh

and approved by

New Brunswick, New Jersey

October, 2017

## ABSTRACT OF THE DISSERTATION

# Wireless Electrical Stimulators for Nanofibers with Application in Next Generation Muscle Prosthesis

# by Yi Huang Dissertation Director: Professor Laleh Najafizadeh

Functional loss and impairment of skeletal muscle could occur as a result of a diverse range of causes including trauma, aging, and diseases such as amyotrophic lateral sclerosis, negatively impacting the lives of more than 2 million people in the United States. Existing solutions for the repair and regeneration of skeletal muscle display contractility only "after" new muscle has been regenerated, which is typically a lengthy process. Such limitations highlight the need for the development of new technologies that can provide function and regeneration of lost tissue in a timely manner. A possible solution to enable patients with immediate function as new tissue regenerates is the development of new classes of subcutaneous muscle prosthesis, which are envisioned to be made by combining biomaterials such as ionic electroactive polymers (iEAPs) with their implantable controllable electrical stimulators. Towards this goal, the work presented here proposes novel circuit-level and system-level solutions for the design and realization of wirelessly tunable electrical stimulators for iEAPs.

The first part of this dissertation focuses on the problem of implementing precise reference circuits that will be required in stimulators. Three novel design solutions are presented. First, a BiCMOS-based curvature compensation technique, which can be realized in any BiC-MOS/CMOS technology, is proposed to completely cancel the nonlinear temperature dependent terms of the base-emitter junction voltage in bandgap reference voltage circuits. Second, a new design solution based on the bandgap voltage difference of Si and SiGe p - n junctions is proposed to significantly improve the accuracy of SiGe-based reference circuits. For both proposed solutions, theoretical derivations are presented, and circuits are designed, fabricated, and experimentally characterized. Finally, a multi-piecewise solution is presented which results in references with maximum stability.

The second part of the dissertation focuses on the design of the tunable stimulators and their integration with iEAPs. The unique characteristics of iEAPs impose several design challenges for the stimulator. These challenges are identified, and solutions are proposed. The electrical stimulation is proposed to be provided using a tunable external capacitor-less low dropout regulator (LDO). To enable remote tuning, the frequency at the primary side is utilized to wirelessly adjust the magnitude of the voltage from the LDO, and hence, the electric field generated at the secondary side (implant). Furthermore, a system-level solution is presented to remotely control the polarity of the electric field as well as its magnitude, enabling iEAPs with a wide range of movement possibilities. The performance of the proposed stimulator in generating reliable output is extensively evaluated experimentally under various conditions, including coil misalignment. The stimulator is integrated with iEAP samples, and the functionality of the end-to-end module is examined based on the response and the movement characteristics of iEAPs in a series of *in vitro* experiments. Results demonstrate the feasibility of using the proposed system as a reliable tunable electrical stimulator for iEAPs.

# Acknowledgements

This dissertation would not have been accomplished without the support and encouragement from so many people. First of all, I would like to express my sincere gratitude to my advisor, Dr. Laleh Najafizadeh, for guiding me in the right direction during this research, helping me patiently in writing scientific publications, and offering me many excellent opportunities in teaching and attending world-class academic conferences. Her close and insightful guidance throughout this research have provided me numerous research opportunities. Her enthusiasm, leadership, and support have constantly encouraged me throughout my Ph.D. journey.

I would also like to thank my dissertation committee members, Dr. Yicheng Lu, Dr. Zoran Gajic, Dr. Jaeseok Jeon, and Dr. Joseph Freeman for their generous availability and insightful comments and suggestions for this dissertation. Many thanks to the faculty and staff members of the ECE department, who helped me during my studies at Rutgers University: Dr. Jian H. Zhao, Dr. Sigrid McAfee, Dr. Michael Caggiano, and the late Dr. Paul Panayotatos. Many thanks to Mr. John Scafidi for his excellent IT support, Ms. Arletta Hoscilowicz, Ms. Tea Akins and Ms. Ora Titus for their administrative coordination.

This work was supported in part by the National Science Foundation (NSF) under grant 1408202. I am very grateful for the support from the NSF and the collaboration from the great team members in completing this work. Many thanks to the current and past members of Rutgers Integrated Systems and Neuroimaging Laboratory, Mr. Li Zhu, Mr. Fanpeng Kong, Mr. Yunqi Wang, Ms. Tianjiao Zeng and Mr. Ali Essam Hameed. My appreciation especially goes to Mr. Li Zhu and Mr. Fanpeng Kong for their selfless help in many of the circuit layout work and the inspiring technical discussion of the research projects. Many thanks to the great technical support from Mr. Danial Browe from Rutgers BME department and Mr. Sanjeevi Thirumurugesan from the ECE department on the iEAP simulator project. I am also thankful to many other students who helped me in the coursework and research in ECE department, Dr.

Jun Tan, Dr. Yanbiao Pan, Dr. Sumati Sehajpal, Ms. Namrata Bansal, and Mr. Sy-Min Chueng.

I am especially grateful to my manager at work, Mr. Chun Cheung in Intersil Corporation, by offering me the work opportunity to enter into the power electronics industry, guiding me to understand electronics in the real world, polishing my theoretical and experimental skills, providing me valuable internal and external training opportunities, and helping me obtain the financial support for my Ph.D. study from the Intersil Education Assistance Program. Thanks to many of the team members in Intersil NJ development center, including Mr. Keerthi Varman Ana Jayaprakash, Mr. Paul Dackow, Mr. Richard Zhu, Ms. Shanice Cheung, Mr. Kongan Zhou, Mr. William Zheng, Mr. Mark Waitt, and Mr. Thomas Umberger, for teaching me circuits theory and the usage of lab equipment.

Appreciation is also given to my venerable senior friends and wonderful peers over the years. Many thanks to Pastor Chen Chi and Ms. Sue Woo of South Bay Chinese Christian Church in Gardena, CA, Mr. Tsu-Yu Chu and Ms. Fang-Hsi Chang of Newark Christian Fellowship in Newark, NJ, for many years' care of me and my family's life in the U.S., and guiding me to hold on to the faith and believe in God all the time. Thanks to Mr. Nicholas Michelinakis and Ms. Susan Thompson of Aircraft Lighting International Incorporation in Hauppauge, NY, by teaching me the practical electronics for my very first time and encouraging me to dream big. Thanks to Dr. Ronald Rothchild of Jona Group Ltd, Huntington, NY, in providing me an intern opportunity in micro-controller programming during my study at Stony Brook University. Thanks to Ms. Hong "Virginia" Wang, for introducing me to the first full-time job in the U.S. I am also grateful to my best friend, Mr. Lumin Zhang, for his continuous guide, encouragement, and lifelong friendship.

Last but not least, I am indebted to my parents and all of my family members. My greatest appreciation is for my parents, Dr. Huang Hansheng and Ms. Gao Huilan, for their unconditional love and support throughout my life. They supported me to pursue my academic goals on the another half of the earth, encourage me to face life's difficulties and never give up. The appreciation and love also go to my grandparents, Mr. Huang Heshui, the late Ms. Zhuang Jinduan, the late Mr. Gao Yongxiang, and Ms. Huang Sumei, who have given me all they have but never asked for anything in return. My gratitude goes to my wife Cen for her understanding, patience, and sacrifice. Many thanks to my parents-in-law, Mr. Zhao Jianguo and Ms. Cen

Huizhen for their selfless support to us. Heartfelt thanks to my daughter Zehan and son Zeqing, whose arrival brings so much joy to the entire family.

# **Table of Contents**

| Ab | Abstract |          |                                                        |    |  |  |  |

|----|----------|----------|--------------------------------------------------------|----|--|--|--|

| Ac | know     | ledgem   | ents                                                   | iv |  |  |  |

| 1. | Intro    | oductior | 1                                                      | 1  |  |  |  |

|    | 1.1.     | Motiva   | tion                                                   | 2  |  |  |  |

|    | 1.2.     | Contrib  | oution of this Research                                | 3  |  |  |  |

|    |          | 1.2.1.   | Circuit-level Contributions                            | 3  |  |  |  |

|    |          | 1.2.2.   | System-level Contributions                             | 5  |  |  |  |

|    | 1.3.     | Thesis   | Outline                                                | 5  |  |  |  |

| 2. | Imp      | lantable | Stimulators                                            | 7  |  |  |  |

|    | 2.1.     | Backgr   | ound                                                   | 7  |  |  |  |

|    | 2.2.     | Design   | Requirements and Challenges                            | 9  |  |  |  |

|    |          | 2.2.1.   | System Design Requirements                             | 9  |  |  |  |

|    |          |          | 2.2.1.1. Size                                          | 9  |  |  |  |

|    |          |          | 2.2.1.2. Power Source and Power Dissipation            | 9  |  |  |  |

|    |          | 2.2.2.   | Stimulation Requirements                               | 11 |  |  |  |

|    |          |          | 2.2.2.1. Stimulation Channels and Sites                | 11 |  |  |  |

|    |          |          | 2.2.2.2. Stimulation Patterns                          | 12 |  |  |  |

|    |          | 2.2.3.   | Wireless Telemetry                                     | 14 |  |  |  |

|    | 2.3.     | Review   | of State-of-the-Art Works                              | 15 |  |  |  |

|    |          | 2.3.1.   | Design Techniques in Addressing Size, Power Challenges | 15 |  |  |  |

|    |          | 2.3.2.   | Design Techniques in Addressing Stimulation Challenges | 17 |  |  |  |

|    |          | 2.3.3.   | Design Considerations for Wireless Telemetry           | 18 |  |  |  |

|    |          | 2.3.4.   | System Level Implementations                           | 20 |  |  |  |

|    | 2.4. | Summa   | ary                                                                     | 22 |

|----|------|---------|-------------------------------------------------------------------------|----|

| 3. | High | Precis  | ion Reference Circuits                                                  | 23 |

|    | 3.1. | Introdu | iction                                                                  | 23 |

|    | 3.2. | Therm   | al Characteristics of the Devices in the SiGe BiCMOS Technology         | 24 |

|    |      | 3.2.1.  | SiGe BiCMOS technology                                                  | 24 |

|    |      | 3.2.2.  | CMOS Transistors                                                        | 25 |

|    |      | 3.2.3.  | Bipolar Junction Transistors                                            | 26 |

|    |      | 3.2.4.  | SiGe Heterojunction Bipolar Transistors                                 | 27 |

|    | 3.3. | Design  | Review of Reference Circuits                                            | 28 |

|    |      | 3.3.1.  | Quadratic Temperature Compensation Technique                            | 29 |

|    |      | 3.3.2.  | Temperature Dependent Resistor Ratio Compensation Technique             | 30 |

|    |      | 3.3.3.  | Nonlinearity Subtraction Technique                                      | 30 |

|    |      | 3.3.4.  | Piecewise Curvature Corrected Technique                                 | 30 |

|    |      | 3.3.5.  | Pseudo " $T \ln(T)$ " Corrected Technique                               | 31 |

|    |      | 3.3.6.  | Comparison of Reviewed Compensation Techniques                          | 31 |

|    | 3.4. | BiCM    | OS-Based Compensation: Towards Fully Curvature-Corrected BGR            | 32 |

|    |      | 3.4.1.  | Proposed Technique for the Compensation of the Nonlinear Term           | 32 |

|    |      | 3.4.2.  | Proof of Concept                                                        | 35 |

|    |      |         | 3.4.2.1. The $I_{PTAT}$ Current Generator                               | 35 |

|    |      |         | 3.4.2.2. The $I_{V_{BE}}$ Current Generator                             | 37 |

|    |      |         | 3.4.2.3. The $I_{V_{GS}}$ Current Generator                             | 38 |

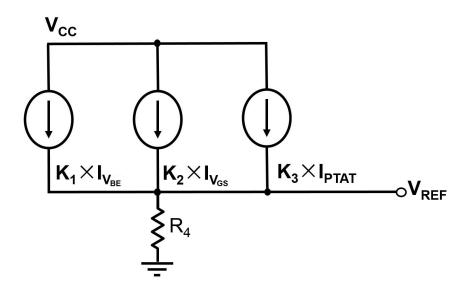

|    |      |         | 3.4.2.4. The $V_{REF}$ Generator                                        | 39 |

|    |      | 3.4.3.  | Verification                                                            | 41 |

|    |      |         | 3.4.3.1. The $I_{PTAT}$ Current                                         | 43 |

|    |      |         | 3.4.3.2. The $I_{V_{GS}}$ Current                                       | 46 |

|    |      |         | 3.4.3.3. The Output Voltage $V_{REF}$                                   | 47 |

|    |      | 3.4.4.  | Discussion                                                              | 56 |

|    | 3.5. | A SiGe  | e Reference Circuit Utilizing Si and SiGe Bandgap Voltage Differences . | 59 |

|    |      | 3.5.1.    | Proposed Compensation Technique                                  |    |  |  |  |  |

|----|------|-----------|------------------------------------------------------------------|----|--|--|--|--|

|    |      | 3.5.2.    | Design Example                                                   | 53 |  |  |  |  |

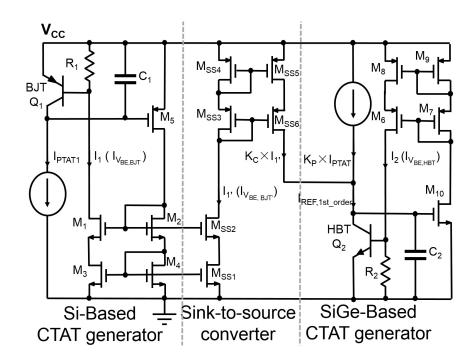

|    |      |           | 3.5.2.1. Si-Based Current Generator                              | 53 |  |  |  |  |

|    |      |           | 3.5.2.2. SiGe-Based Current Generator                            | 54 |  |  |  |  |

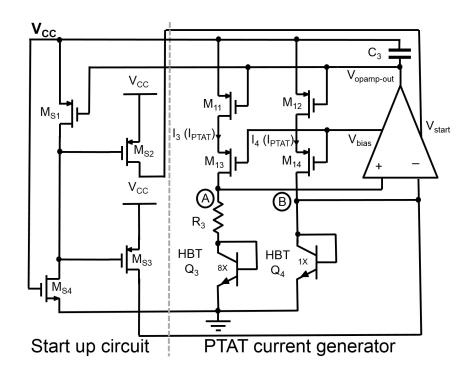

|    |      |           | 3.5.2.3. PTAT Current Generator                                  | 65 |  |  |  |  |

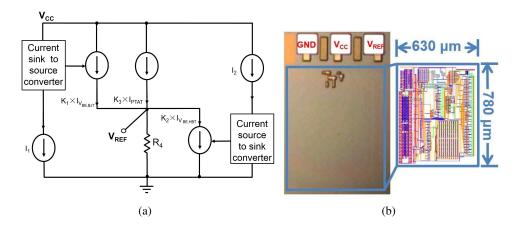

|    |      |           | 3.5.2.4. $V_{\text{REF}}$ Generator                              | 56 |  |  |  |  |

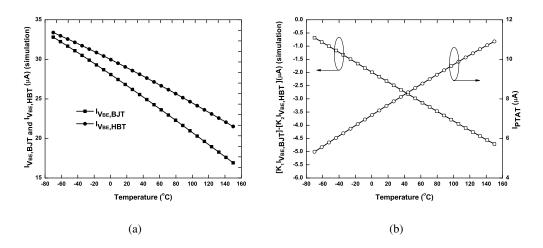

|    |      | 3.5.3.    | Measurement Results                                              | 57 |  |  |  |  |

|    |      | 3.5.4.    | Discussion                                                       | 59 |  |  |  |  |

|    | 3.6. | A Mul     | ti-Piecewise Curvature-Corrected Technique for BGR Circuits 7    | 71 |  |  |  |  |

|    |      | 3.6.1.    | Basic Concepts                                                   | 72 |  |  |  |  |

|    |      | 3.6.2.    | Proposed Compensation Technique                                  | 74 |  |  |  |  |

|    |      |           | 3.6.2.1. Temperature Behavior of $I_D$                           | 74 |  |  |  |  |

|    |      |           | 3.6.2.2. Multi-Piecewise Curvature-Corrected Technique           | 76 |  |  |  |  |

|    |      |           | 3.6.2.3. PMOS vs NMOS implementation                             | 77 |  |  |  |  |

|    |      | 3.6.3.    | Design Consideration and A Design Example                        | 79 |  |  |  |  |

|    | 3.7. | Summa     | ary                                                              | 81 |  |  |  |  |

| 4. | Wire | eless Elo | ectrical Stimulators for Nanofibers                              | 83 |  |  |  |  |

|    | 4.1. | Introdu   | lection                                                          | 84 |  |  |  |  |

|    | 4.2. | Biocor    | npatible ionic Electroactive Polymers and its Electrical Model 8 | 85 |  |  |  |  |

|    |      | 4.2.1.    | Biocompatible ionic Electroactive Polymers                       | 35 |  |  |  |  |

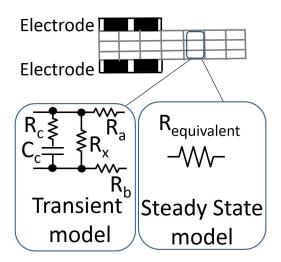

|    |      | 4.2.2.    | Electrical Modeling of the ionic Electroactive Polymers          | 87 |  |  |  |  |

|    | 4.3. | In Vitre  | Characterization of the iEAP using an Tunable LDO                | 88 |  |  |  |  |

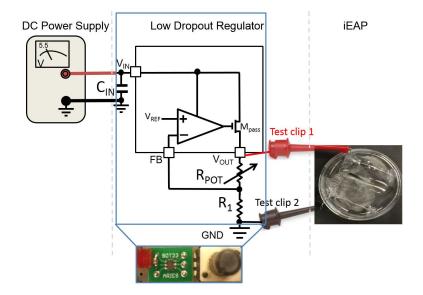

|    |      | 4.3.1.    | Experimental Setup                                               | 88 |  |  |  |  |

|    |      |           | 4.3.1.1. Stimulator                                              | 88 |  |  |  |  |

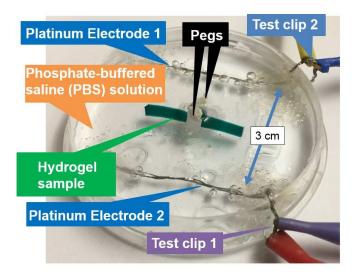

|    |      |           | 4.3.1.2. In Vitro Setup                                          | 89 |  |  |  |  |

|    |      | 4.3.2.    | Experimental Results                                             | 89 |  |  |  |  |

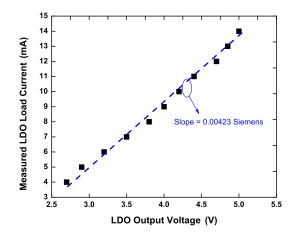

|    |      |           | 4.3.2.1. Electrical Characterization-Measuring Conductance 9     | 90 |  |  |  |  |

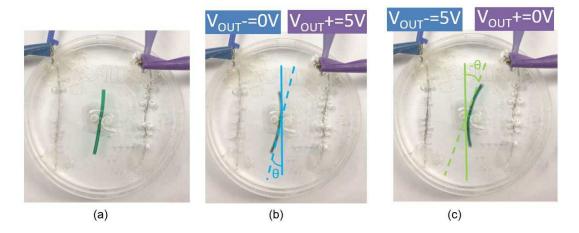

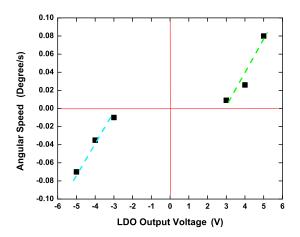

|    |      |           | 4.3.2.2. Movement Characterization-Measuring Angular Speed 9     | 90 |  |  |  |  |

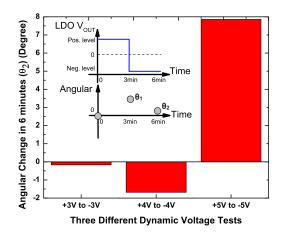

|      |        | 4.3.2.3.  | Movement Characterization-Measuring Angular Changes in          |

|------|--------|-----------|-----------------------------------------------------------------|

|      |        |           | response to Rapid Voltage Changes                               |

|      | 4.3.3. | Summar    | y of the <i>In Vitro</i> Characterization Experiment            |

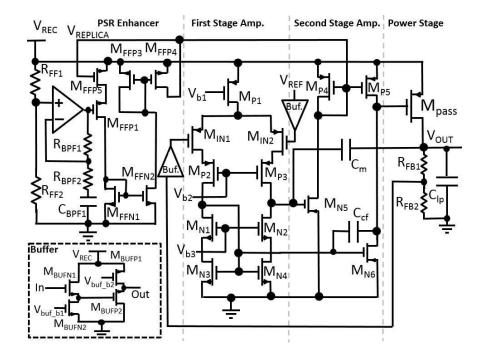

| 4.4. | Design | Consider  | ations of the LDO                                               |

|      | 4.4.1. | Design c  | hallenges of the LDO                                            |

|      | 4.4.2. | Proposed  | 1 LDO                                                           |

|      | 4.4.3. | Simulati  | on Results                                                      |

|      | 4.4.4. | Summar    | y of the LDO Design                                             |

| 4.5. | Wirele | ss Tuning | Technique                                                       |

|      | 4.5.1. | Proposed  | d Wirelessly Tunable Technique                                  |

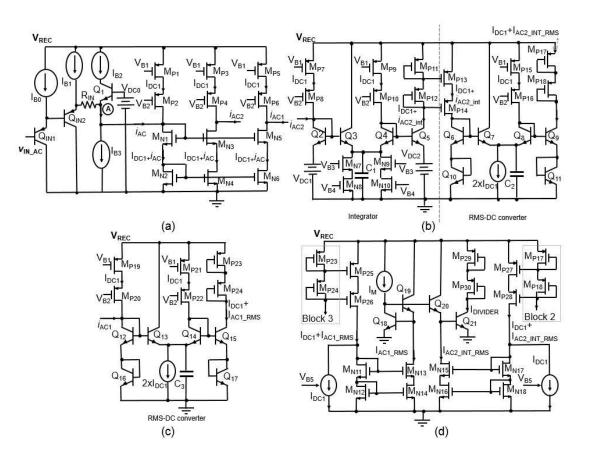

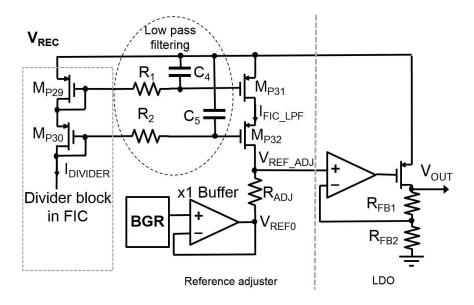

|      | 4.5.2. | Circuit I | mplementation                                                   |

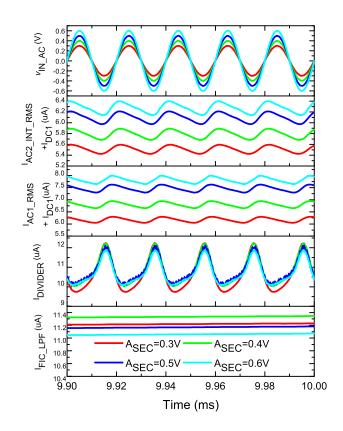

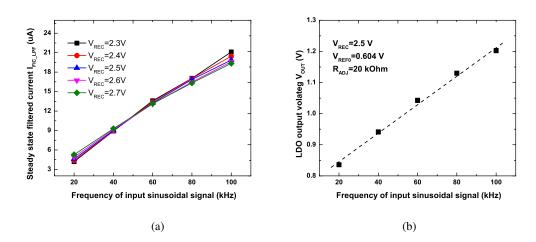

|      | 4.5.3. | Simulati  | on Results                                                      |

|      | 4.5.4. | Summar    | y of the Proposed Wireless Tuning Technique                     |

| 4.6. | System | n Impleme | ntation                                                         |

|      | 4.6.1. | System (  | Overview                                                        |

|      | 4.6.2. | Proof of  | Concept                                                         |

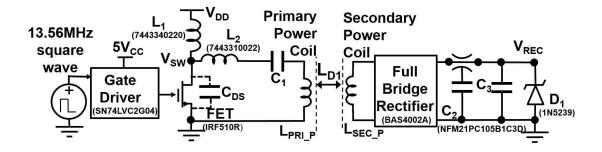

|      |        | 4.6.2.1.  | Power Unit                                                      |

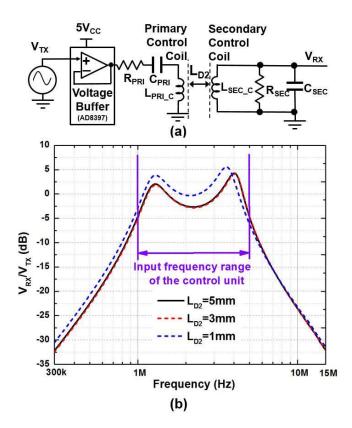

|      |        | 4.6.2.2.  | Control Unit                                                    |

|      | 4.6.3. | Experim   | ental Results-System Level Evaluation                           |

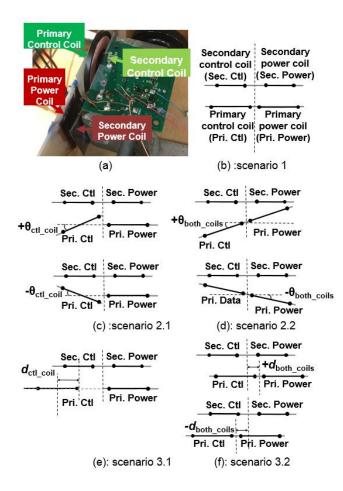

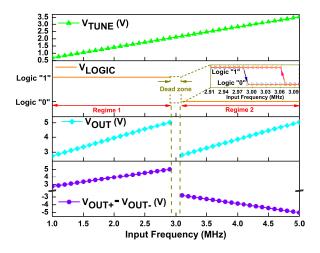

|      |        | 4.6.3.1.  | Experimental Setup                                              |

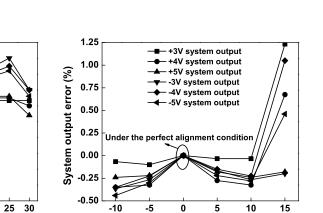

|      |        | 4.6.3.2.  | Performance Evaluation in the Presence of Coil Misalignment 117 |

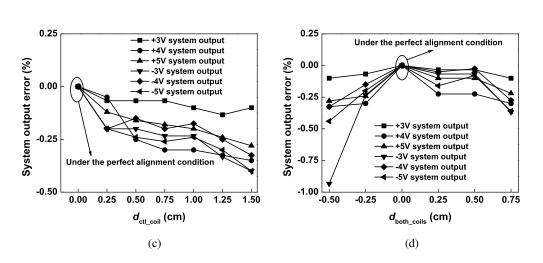

|      |        | 4.6.3.3.  | Controllability of the Output Voltage via Input Frequency 119   |

|      |        | 4.6.3.4.  | Performance Evaluation in Response to Abrupt Frequency          |

|      |        |           | Changes                                                         |

|      | 4.6.4. | Experim   | ental Results-In Vitro Characterization                         |

|      |        | 4.6.4.1.  | Experimental Setup                                              |

|      |        | 4.6.4.2.  | Movement Characterization: Angular Speed                        |

|      |        | 4.6.4.3.  | Movement Characterization: Response to Rapid Frequency          |

|      |        |           | Changes                                                         |

|    |       | 4.6.5. Discussion        |

|----|-------|--------------------------|

|    | 4.7.  | Summary                  |

| 5. | Conc  | clusions and Future work |

|    | 5.1.  | Conclusions              |

|    | 5.2.  | Future work              |

| Re | feren | <b>ces</b>               |

# Chapter 1

# Introduction

The skeletal muscle is responsible for the maintenance of posture and voluntary body movements [1]. When the skeletal muscle suffers from the minor injury, it can regenerate rapidly to avoid the loss of muscle mass [2]. However, regarding the large volume injuries, aging or the illness (such as amyotrophic lateral sclerosis, vascular disease or cancer), the skeletal muscle is incapable of fully restoring function via its regeneration process [3,4]. In the healing process of the large volume injuries, the injury site is occupied by the scar tissue, and thus the satellite cells are not capable of filling the voids around the damaged area [5,6]. As a result, the function of the muscle is degraded and the patients' quality of life is negatively impacted due to the occurrence of functional loss and impairment of skeletal muscle.

Nowadays, the standard treatment for large volume deficiencies in skeletal muscle is the tissue's autologous transplantation from the donor [7]. Although this approach is effective on the reanimation of the elbow and forearm [8, 9], its limited success for larger defects in muscles cannot be denied [10]. In addition, by using autologous transplantation, the donor site morbidity can also increase the risk of infection during the surgery [11]. Therefore, a better treatment is highly demanded to bypass the issues brought from the autologous transplantation.

In the field of tissue engineering [12], several approaches have been investigated for the repair and regeneration of skeletal muscle. A general tissue engineering paradigm includes taking the muscle progenitor cell, seeding them on the 3-D scaffold, applying stimulation to achieve the cell differentiation and eventually constructing the tissue to implant into the patients [13]. A constructed tissue is considered as a functional skeletal muscle replacement only if it is capable of reproducing the contractile stress of native skeletal muscle. In the past few years, several approaches, such as intramuscular injections of skeletal myoblasts [10], have been sought to aid in the regeneration of deteriorated tissue [14–17]. However, there still exist

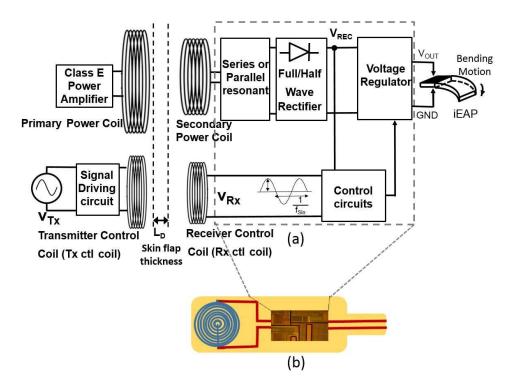

problems with producing artificial muscles that contract and relax similar to real muscles and also display immediate contractility upon being implanted. One possible solution to the problems of flexibility and immediate movement restoration is the development of new classes of subcutaneous muscle prosthesis, which combine ionic electroactive polymers (iEAPs) [18, 19] with integrated circuits as their simulators. In addition to creating movement, such a prosthesis will also speed up the tissue regeneration process by enhancing cellular proliferation alignment via stimulation upon implantation.

The successful implementation and operation of such a system will strongly rely on the implantable microelectronic devices, which have been receiving increased attention in recent years because of their great potential in offering solutions to problems in various clinical applications [20,21]. To develop this iEAP-based subcutaneous muscle prosthesis, several design challenges need to be overcome. The essential requirements for the implantable electronic devices are the compact size and low power consumption. In addition, ideally, all the devices in the implant unit need to be powered-up wirelessly instead of relying on a local battery. Furthermore, reliable function in biological medium needs to be provided by this system.

## 1.1 Motivation

To provide the electrical stimulation to iEAPs for the new classes of muscle prosthesis, novel solutions for the development of responsible integrated circuits and wireless control technique are required. The work presented here is motivated by this demand, and proposes innovative solutions at the circuit and system levels.

The first part of the dissertation focuses on the development of novel high-performance reference circuits, following a "device-circuit interaction" design approach. High precision reference circuits are needed in implantable stimulators and virtually all electronic systems. A key requirement of reference circuits is to generate a robust voltage that is invariant against variations in environmental and operating conditions. Any variations in the reference voltage will directly affect the performance of the overall system. The most commonly used topology for the realization of reference circuits is the bandgap reference (BGR) [22]. A BGR is designed to generate an output voltage that is referred to the bandgap energy of the background

semiconductor material. In Si-based BGR circuits, the relation to the bandgap energy can be established through the base-emitter voltage  $(V_{BE})$ . However,  $V_{BE}$  also depends to the temperature (T) linearly  $(\propto T)$  and nonlinearly  $(\propto [T \ln(T)])$ . Traditionally, a proportional to the absolute temperature (PTAT) component is created to cancel the linear-dependent term of  $V_{BE}$ , known as the complementary to the absolute temperature (CTAT) term [22]. The major problem with this approach is that the output of BGRs will still be dependent on the temperature (due to the existence of  $\propto [T \ln(T)]$  terms), limiting their level of precision. In Chapter 3, three novel BGR topologies with new curvature compensation techniques are proposed, which advance the state-of-the-art BGRs.

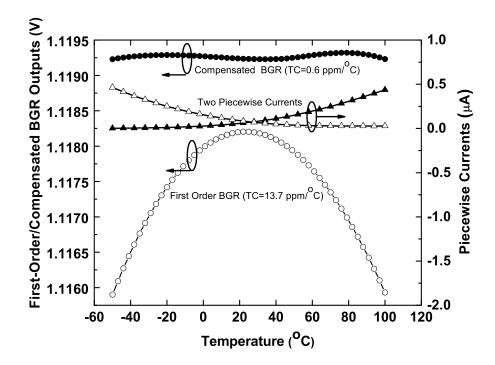

The second part of the dissertation concentrates on the system level solutions for the realization of implantable stimulators. The work in Chapter 4, proposes to provide the electrical stimulation to iEAPs via a wirelessly tunable voltage regulator. This system is capable of remotely controlling the degree and the direction of their movement. Without using digital modulation schemes, the proposed stimulator uses frequency at the primary side, to wirelessly tune the magnitude and the polarity of the electric field generated at the secondary side, enabling iEAPs with a wide range of movement possibilities.

#### **1.2** Contribution of this Research

Driven by the demand for the next generation muscle prosthesis, this dissertation presents innovative circuit and system level solutions for the realization of implantable stimulators for iEAPs.

## **1.2.1** Circuit-level Contributions

The electrical stimulation to the iEAPs needs to be provided by a voltage regulator, such as the low drop-out regulator (LDO). Ideally, a wireless tunable LDO with a stable voltage reference is required.

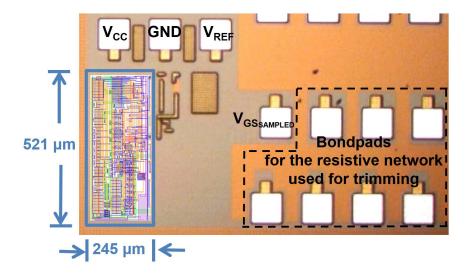

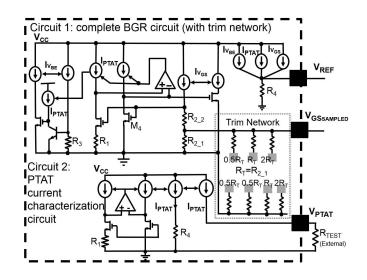

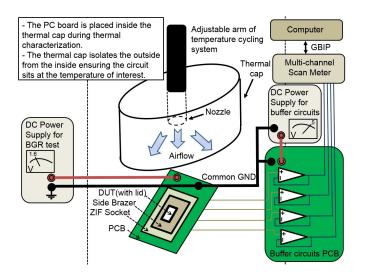

In Chapter 3, three different curvature compensation techniques are proposed to improve the accuracy of the BGR circuits. Section 3.4 presents a BiCMOS compensation approach combining the temperature properties of SiGe heterojunction bipolar transistors (HBTs) and CMOS transistors. This proposed compensation approach has been experimentally demonstrated to outperform the temperature performance of the state-of-the-art SiGe reference circuits. This work is published in [23] and [24].

Section 3.5 presents a novel curvature-compensation technique for bandgap reference circuits implemented in the SiGe BiCMOS technology. The technique utilizes the designers' access to both Si-based and SiGe-based p - n junctions. Curvature compensation is achieved in two steps: first, by weighted subtraction of two currents, one proportional to the base-emitter junction of a Si BJT, and the other proportional to that of SiGe HBTs, the non-linear temperature dependent terms are compensated; and second, by adding a PTAT current, the remaining linear temperature dependent terms are canceled. As a result, an almost complete temperature compensation is achieved. This work is published in [25] and [26].

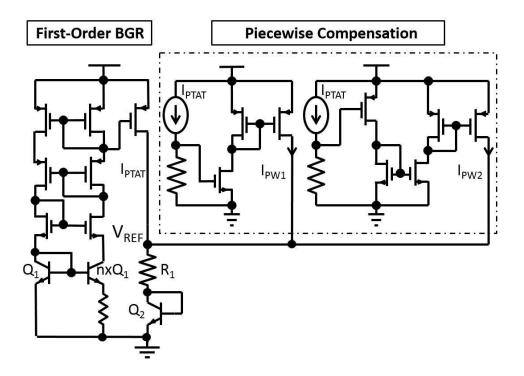

In Section 3.6, a systematic design methodology utilizing a piecewise curvature correction technique to improve the temperature coefficient (TC) of BGRs is presented. It is shown that the temperature dependency of the drain current of a MOSFET transistor depends on the transistor's operating region. Using this property, a multi-piecewise compensation technique over a wide temperature range is achieved by controlling the operating region of MOSFETs through their gate-source voltages. This work is published in [27].

In Section 4.4, an LDO for the electrical stimulation of iEAPs is presented. The challenges brought from the special requirement of the application and the characteristics of iEAPs are discussed, and the circuit level solutions are provided. The proposed LDO uses the external-capacitor-less architecture to enable a fully on-chip solution for providing stable stimulation across a wide load range, as required by the properties of iEAPs. The LDO also offers precise line and load regulations, as well as improved power supply rejection (PSR) to suppress the supply noise when the LDO is powered up through wireless power transfer (WPT) links. This work is published in [28].

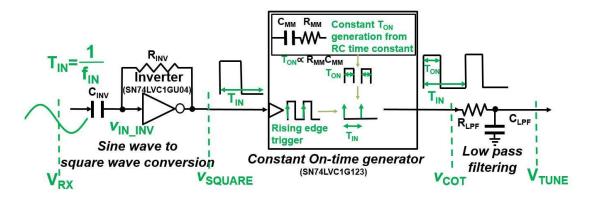

In Section 4.5, a design technique to implement wirelessly tunable LDO is introduced. The proposed technique, built upon the concept of frequency-based telemetry, converts the frequency of the sinusoidal signal at the primary side into an electrical current at the secondary side that will be proportional to the input frequency. This current is then used to change the reference level of the LDO and therefore, its output voltage. The proposed technique provides the capability to tune the output of LDO remotely, and thus LDO can be used as a reliable stimulator for iEAPs to allow different degrees of movement for the subcutaneous muscle prosthesis. This work is published in [29].

#### **1.2.2** System-level Contributions

In Section 4.3, the functionality of electrically stimulated iEAPs is evaluated under steady-state and transient conditions. An LDO is used to provide the electrical stimulation to the iEAPs, and *in vitro* characterization results are presented and discussed. Electrical characteristics of iEAPs in terms of conductance, and movement characteristics of iEAPs in terms of changes in the bending angle during xed and transient stimulation are evaluated. Measured results suggest that iEAPs in combination with LDO-based stimulator have great potentials for the realization of the next generation muscle prosthesis. This work is published in [30].

In Section 4.6, the proposed stimulator is implemented using custom-off-the-shelf components. This section presents a new system-level solution for the realization of a tunable electrical stimulator for iEAPs, capable of remotely controlling the degree and the direction of their movement using one control coil. The performance of the stimulator in generating reliable output is extensively evaluated under various conditions, including coil misalignment. In addition, the functionality of the end-to-end module is examined based on the response and the movement characteristics of iEAPs in a series of *in vitro* experiments. Movement characteristics of iEAPs in terms of changes in the bending angle during fixed and transient stimulation are evaluated. Measured results demonstrate the feasibility of using the proposed system as a reliable tunable electrical stimulator for iEAPs. Moreover, the combination of iEAPs and the proposed stimulator has great potentials for the realization of the next generation muscle prosthesis that is flexible, and can enable immediate movement restoration, upon implantation. This work is published in [31,32].

# 1.3 Thesis Outline

The dissertation is organized as followings. In Chapter 2, a review of the previous works on implantable stimulators is presented. The design criteria, challenges, various applications and the state-of-the-art works on implantable stimulators are surveyed. In Chapter 3, we propose three novel curvature compensated techniques in designing the BGR circuits. In Chapter 4, the system design requirements and challenges in the development of this iEAP-based subcutaneous muscle prosthesis are analyzed. Without using digital modulation schemes, a frequency-based design technique is proposed to wirelessly tune the magnitude and the polarity of the electric field generated at the secondary side, enabling iEAPs with a wide range of movement possibil-ities. Finally, Chapter 5 contains conclusions and potential research directions.

# Chapter 2

# **Implantable Stimulators**

As discussed in Chapter 1, an implantable stimulator can be implemented for the iEAP-based subcutaneous muscle prosthesis. In order to implement an effective system for the subcutaneous muscle prosthesis, we will review prior works on implantable stimulators that are realized in modern electronic technology platforms. In this chapter, the background information on implantable devices will be reviewed first. Next, the system specifications, design requirements and challenges of implantable stimulators will be studied. Finally, the design techniques and considerations are reviewed to meet the design challenges, along with a review of the system level implementation of the state-of-the-art implantable stimulators.

## 2.1 Background

Implantable devices are artificial medical instruments that can be inserted subcutaneously into a patient's body and either act as the replacement for the missing biologic structure or augment the patients' body parts [33]. In 1958, the first implantable device was reported when a cardiac pacemaker was successfully implanted in an animal [34]. After which, implantable devices have been extended to various clinic domains, such as the cochlear implants [35], vagus nerve stimulator [36], drug delivery systems [37] and defibrillator [38]. In the past few decades, the development of microelectronics-based medical implants has gone through revolutionary progress due to the advances in modern electronic devices and integrated circuits.

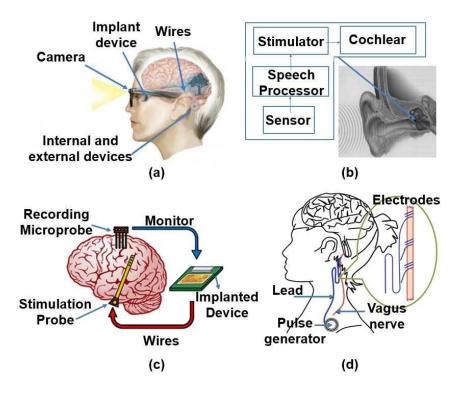

Electrical stimulators are examples of implantable devices, which are designed to provide low-level voltage/currents to excite nerve cells or muscle fibers via electrodes. As shown in Fig. 2.1, examples for application of implantable stimulators are categorized into four areas from the perspective of the dysfunctional body organs that need replacement or augmentation. Figs. 2.1-a, 2.1-b and 2.1-c illustrate the applications of visual neural stimulators (retinal prosthesis)

Figure 2.1: Examples for application of implantable stimulators: a) retinal prosthesis (after [45]), b) cochlear implant (after [48]), c) deep brain stimulator (after [52]), and d) vagus nerve stimulator (after [70])

[39–45], auditory neural stimulators (cochlear implants) [46–48], and deep brains stimulator [49–53], respectively. In addition to these three categories, various neuro stimulators have also been designed for epidural spinal cord [54], the vagus nerve [36, 55, 56], neuromuscular unit [57–59], diaphragmatic/phrenic nerve [60] and sacral nerve [61]. In Fig. 2.1-d, a vagus nerve stimulator is shown as the example of these neuro stimulators.

Due to the similarity between the electrical stimuli and natural biological stimuli, the cells' transmembrane potential [62] can be changed under electrical stimulation. Electrical stimulators can bring various benefits to the patients, depending on the applications. For instance, the stimulation provided from the retinal prosthesis can partially recover the lost perception of vision [63–68], while a vagus nerve stimulator can reduce the frequency of seizures in the patients with refractory epilepsy [69]. To maximize the benefit from these electrical stimulators, they must be designed carefully based on a thorough understanding of the design requirement and challenges.

#### **2.2 Design Requirements and Challenges**

The architecture of typical implantable stimulators can be separated into two units: the external unit and the implant [33]. The external unit usually includes the power transfer unit, and/or user interface to send the control command or the real-time monitoring telemetry. The implant usually includes the power unit (such as the secondary power coil in a wireless power transfer system, or the battery) and the signal conditioning circuits to generate the stimulation pattern. To understand the system architecture of implantable stimulators, it is important to study the design requirements and challenges. The analysis of these metrics will provide further insight into the system design.

# 2.2.1 System Design Requirements

The main system design requirements for implantable stimulators are related to the safety constrains, such as the size and the power consumption and power density of the implant unit.

### 2.2.1.1 Size

One essential requirement for the implantable devices is its overall size. The implantable stimulators' size must be compact to be implanted into the human body. For the applications with multiple electrodes (such as retinal prothesis), the size of implantable stimulators is further constrained to allow for integration with the implanted electrode arrays [71]. For typical implantable stimulators, the off-chip components can be the inductive coils [59] or off-chip antenna [72], the capacitors to tune coils to resonance [59], the capacitors in the charge mode stimulation circuits [73], the blocking capacitors for charge balancing purpose [74], and the energy storage capacitors to aid in power supply regulation [59]. Due to the space limitation in the implant, these discrete components are highly restricted [75] and must be carefully considered in the design iterations.

#### 2.2.1.2 Power Source and Power Dissipation

Optimizing the technique for delivering enough power to implantable devices has been investigated in several works [76, 77]. The conventional implementation of the implantable devices

|                                      | Inductive coupling | Resonance coupling                       | Radio charging            |

|--------------------------------------|--------------------|------------------------------------------|---------------------------|

| Mechanism for power transfer process | Magnetic induction | Resonance-enhanced<br>magnetic induction | Received radio waves      |

| Coupling components & circuits       | Inductive coil     | Resonant LC tuned circuit                | Resonant LC tuned circuit |

|                                      | Sub RF or          | Sub RF or                                |                           |

| Frequency range                      | lower frequencies  | lower frequencies                        | RF band                   |

|                                      | in the RF band     | in the RF band                           |                           |

| Efficiency                           | Medium             | Highest                                  | Least                     |

| Near/Far field transmission          | Near-filed         | Near-filed                               | Far-filed                 |

| Typical power transfer distance      | 5 to 7 mm          | 7 to 40 mm                               | 2 to 10m                  |

| Spatial freedom                      | Less               | More                                     | Largest                   |

| Target location of the implants      | Shallow            | Shallow/deeper                           | Shallow/deeper            |

| Create electromagnetic pollution?    | No                 | No                                       | Yes                       |

Table 2.1: Comparison of three types of wireless power transfer techniques (after [70])

relies on a battery in the implant unit or the power source provided percutaneously from the external unit via the tethering cable [78]. Although using battery or the power source from the external unit features several advantages (such as efficient power transmission), both the battery replacement (due to the size, limited storage capacity and the number of recharge cycles [79]) and the power sourcing via the tethering wire increase the likelihood of different kinds of injuries, hemorrhage, and infection [33]. Thereafter, the WPT approach is more favorable in most of the modern implantable devices. In a WPT system, the power is transferred from the external unit to the implant in a contactless manner, which offers an attractive power delivery solution for implantable devices by limiting the need for battery replacement or percutaneous leads.

In general, WPT technique can be categorized into near field, mid filed and far filed power transfer, based on the distance of the power transfer [76]. For biomedical applications, there are mainly three types of the wireless transfer techniques: the inductive coupling, the resonance coupling and the radio charging [70]. The first two approaches belong to near field power transfer category with a similar operation: the inductive coupling is based on magnetic induction, while the resonance coupling relies on resonance-enhanced magnetic coupling [80]. The radio charging method is one of the far field techniques, which employs the received radio-frequency (RF) waves via the antenna to serve as the power source. These RF waves usually locate at a much higher band than the frequency spectrum used in the inductive coupling and the resonance coupling. A brief comparison of these three power transfer techniques is shown in Table 2.1 [70].

The choice of the wireless power transfer techniques is based on the requirements of the

application. However, when using any of the wireless power transfer systems, the main challenge for the designers is the power transfer efficiency (PTE) [81], which is influenced by the distance of the coils, the energy transfer rate and the coupling coefficients between the coils. In addition, the power dissipation of the implantable devices is also of concern due to the heat density requirements of the human body. When allocating the power budget of the implantable system, it is important to investigate the amount of heat it will dissipate to the surrounding tissue to avoid the possibility of destroying the cells [33].

The PTE and power dissipation concerns become more important when the frequency locates in RF band. The RF waves can cause the thermal losses when it heats the tissues, which degrades the PTE and raised the possibility of the cell death [70].

#### 2.2.2 Stimulation Requirements

Many implantable stimulators are required to provide precise, reproducible voltage or current stimulation for the target sites. The font-end circuits in the stimulator provide the selection command in activating the target channels, while a unique shape and firing pattern are created for each electrode [62]. Here we will review the stimulation requirements and the design challenges.

## 2.2.2.1 Stimulation Channels and Sites

Conventional implants include the single-channel type and multi-channel type. Single-channel implants produce the stimulation at a single site using a single electrode, while the multi-channel implants provide the electrical stimulation at different sites using an array of electrodes [82]. For general applications, the number of the channels is related to the control and coverage of the neural tissue when the tissue interfaces with the electrodes [69]. For some specific cases, such as retinal prosthesis, hundreds of the electrodes are unavoidable to bring the useful pixelated image to the patients [83–85]. This requirement hence raises the challenges for the size of the implant unit and calls for novel techniques in reducing the overall size brought from the multi-channel designs. One solution is the multiplexed CMOS stimulating probe [86, 87], in which one channel is associated with one multi-site probe. The probe itself includes the power, clock, command recovery and data control units, while each electrode in the probe is

connected to one stimulation site. For these sites, each of them must own the capability to be enabled/disabled, as well as be programmed with different stimulation parameters. To achieve this, several local building block circuits are designed in each site, such as the local finite state machine, recovery circuit, amplitude and timing registers, counters and the current driver [62]. The number of the stimulation sites depend on the application. For example, in [87], a 64-site system is designed for stimulating the central nervous system. Likewise, in [88], the multisite system is designed for cortical stimulation.

## 2.2.2.2 Stimulation Patterns

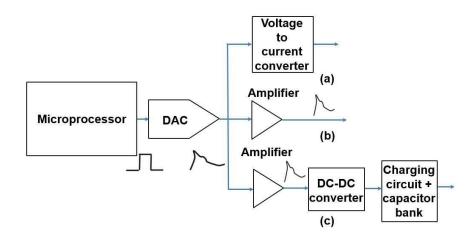

Conventionally, three types of stimulation modes have been used to generate the target stimulation signal, including the current mode stimulation (or current-controlled stimulation, CCS) [40–42, 89–91], the voltage mode stimulation (or voltage-controlled stimulation (VCS)) [92– 96], and charge mode stimulation (or charge-controlled stimulation (ChCS)) [73,97,98]. In Fig. 2.2, the typical block diagram of all these three modes are depicted [70]. In each of them, the voltage signal generated from the microprocessor is passed to the digital to analog converter (DAC) [99]. Then for CCS, the output of the DAC feeds into a voltage to current converter (VIC) to produce the current stimulation signal to the tissue. The implementation of the VCS and ChCS are different from that of CCS. For VCS, an amplifier is connected in the signal path to generate the stimulation voltage signal, while an amplifier, a DC-DC converter, the charging circuit and the capacitor bank constitute the charge mode stimulation circuits.

The selection of the proper charging mode among the three candidates in Fig. 2.2 depends on the application requirements and the available size of the stimulator. For example, ChCS will be preferred when multiple off-chip capacitors are allowed in the design, due to its simple implementation and excellent safety performance [100].

By using any of the charging modes mentioned above, the designed stimulation waveforms can be either monophasic or biphasic [101]. The monophasic wave only consists of one kind of pulses in a unidirectional manner. In biphasic waveforms, a sequence of pulses shows up, while the adjoining pulses have opposite directions. The choice of the stimulation waveform is related to the charge balancing requirements inside the human body. When the electrical stimulation takes place, electrical charges are transferred to the tissue. The long period of

Figure 2.2: Three types of stimulation modes: a) current mode, b) voltage mode, and c) charge mode (after [70])

charge exchange will likely initiate the electrochemical processes inside the human body, such as the electrolysis. These processes are destructive to the tissues and cells, and thus need to be avoided. To prevent the onset of these issues, the net charge must be nulled in each stimulation cycle [102]. In the clinic, the suggested stimulation pattern is the biphasic current, in which the theoretical full charge balance can be ensured [103]. However, in practice both monophasic and biphasic waveforms can cause charge unbalance due to the device mismatches during the IC fabrication. Therefore, the charge balance requirements also impose the challenges of the stimulator design.

In addition to the charging mode and stimulation waveform, the precise control of the pattern specifications is also critical for an effective stimulation. For example, for a stimulation current, the pattern specifications include the current amplitude, the pulse width range, the fine gradients of the stimulation strength, and the repetition rates of the pulses [62, 104]. First, the pulse amplitude matters in most of the applications. For instance, in the cochlear device, the auditory percept can only be elicited with a minimum 1 mA pulse amplitude [47]. Moreover, a large amplitude resolution offers the adjustment flexibility in the stimulation driver, such as the creation of different brightness levels for the patients using retinal prosthesis [105]. Last but not least, the stimulation frequency is directly related to the outcome of the stimulation, such as the frame rate of the retinal prosthesis [43]. To achieve such a stimulation pattern, the stimulation driver must be capable of providing robust wireless programmability with high flexibility.

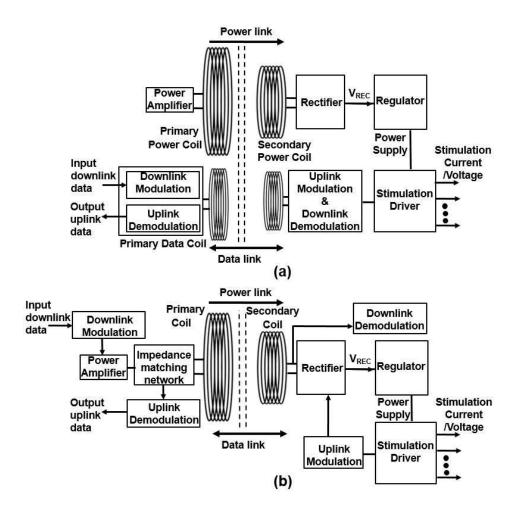

Figure 2.3: Block diagrams of two paradigms of implantable stimulators with bidirectional biotelemetry schemes: a) dual band system (after [104]), b) single band system (after [70]).

#### 2.2.3 Wireless Telemetry

In the discussion of the stimulation pattern, it is acknowledged that it must be programmed wirelessly. Generally, for most of the implant applications, the bidirectional or unidirectional exchange of data needs to be maintained for the remote control and real-time monitoring purpose. The data communication can be achieved by a dedicated pair of data/control coils or via power coils in some circumstances. In Fig. 2.3, two paradigms of implantable stimulators with bidirectional biotelemetry schemes are illustrated.

In Fig. 2.3-a, an example of the dual band implantable stimulator with bidirectional biotelemetry system is shown [106, 107]. In the dual band wireless power and data telemetry systems, the power link and data link are separated to achieve both high data rate and good PTE. As shown in Fig. 2.3-a, the modulation and demodulation building blocks are designed on both the external unit and the internal unit. In Fig. 2.3-b, a single band system [58,70,108] is shown, in which both power link and data link share the same coils. The information-carrying signals are transmitted bidirectionally between the external unit and the implant unit. The data telemetry uplink transmits the monitored/detected signal in the implant to the external unit, while the downlink sends the control command in the opposite direction. The single band system is an attractive solution for the applications that require compact size. However, it sometimes suffers from the interference issue due to the oppositely directed requirements from the power- and information-carrying signals [70].

The digital modulation schemes are commonly employed in the biomedical implanted devices [109]. The existing methods include amplitude shift keying (ASK) [110, 111], On-off keying (OOK) [112], phase-shift keying (PSK) [113–115], frequency-shift keying (FSK) [116], and load-shift-keying (LSK) [117, 118]. In addition, the telemetry can be performed as active telemetry [119] or passive telemetry [120]. The determination of the modulation scheme and the implementation of the telemetry requires a good understanding of the applications' requirements, such as the data rate.

# 2.3 Review of State-of-the-Art Works

To meet the design requirements and challenges, several design techniques have been proposed. In this section, we will first review the techniques in addressing specific challenges discussed in Section 2.2. After that, the state-of-the-art works in the system level implementation will be categorized according to the applications and reviewed.

## 2.3.1 Design Techniques in Addressing Size, Power Challenges

Due to the intrinsic size limitation of the implantable electronics, the design techniques to minimize the usage of the external components are attractive to the circuit designers. One example is the external capacitor-less configuration [121, 122] for the low drop-out regulator. As will be discussed in Chapter 4, this technique can be introduced for the iEAP-based muscle prosthesis to remove bulky LDO output capacitor and maintain the loop stability over wide

load ranges. Likewise, the design techniques to reduce the size of the multi-channel multisite stimulators are important to overcome the size constrains for many applications. In [123], two approaches (1:4 demultiplexer and chip clustering) were presented in extending the 256channel stimulator to a 1024-channel counterpart for the retinal prosthesis.

The power related challenges include the power budget, the PTE and the power consumption of the implant unit. First, since the power consumption of the implant unit is directly related to the heating effects, the prescribed global standards and regulations for electromagnetic protection (such as the specic absorption rate (SAR) [124, 125]) must be obeyed to guide the power budget allocation. Similarly, the upper limit of allowable exposure (MPE) for current and elds in [126] needs to be carefully studied in the system power planning. To avoid overheat effects to the tissues caused by the WPT system, the power budget for most of the implant unit is limited to a few milliwatts [127–129].

Second, within the allowable power budget for an application, the PTE needs to be optimized for an effective wireless power transfer. Several novel configurations for the wireless power transfer system have been presented, aiming at boosting the PTE. For example, in [81], an adaptive solution based on the closed-loop operation was proposed. The supply voltage of the class E power amplifier was dynamically adjusted to fulfill the load variations in the implant. Furthermore, the novel configurations have also been proposed to optimize the PTE. The invention of the 3-coil and 4-coil inductive link configurations [76, 130] have been proven to be effective for PTE boost. For a 3-coil wireless power transfer structure, the third link was inserted into the implant between the conventional primary and secondary coil, to transform the variable load impedance to an optimal impedance needed for an improved power transfer efficiency.

In the third place, the reduction of the implant unit's power consumption is also important. Currently, the low power circuit design techniques [131] have been extensively used for the building blocks in the implant unit. For instance, a low power current sensing circuit was proposed in [132] for monitoring implantable brain chemistry. Another attempt in reducing the power loss (and thus avoid overheat effects) is the employment of the full wave rectifier in processing the received sinusoidal power at the secondary power coil [81, 133].

#### 2.3.2 Design Techniques in Addressing Stimulation Challenges

As discussed in Section 2.2.2, the application-specific stimulation patterns are needed in designing the stimulation drivers. To achieve the optimized solution, the circuit designers need to understand the metrics of three stimulation modes introduced in Section 2.2.2 (CCS, VCS and ChCS) and the associated issues.

We start from the CCS. According to the relationship among the charge, current, and stimulation duration, the amount of charge supplied in each stimulus is easily controlled by programming the current amplitude and the stimulation time. Therefore, the safety of tissue is under control when CCS is applied. However, CCS is usually complex in the circuit implementation and not competitive in the power efficiency [70]. In addition, it also suffers from two extra issues in practice. One is the high output impedance requirements. Due to the highly variable impedance of the tissue, the stimulation driver must provide high output impedance with the generated current source in all conditions [134]. The second one is the large compliance voltage associated with the current source. Under a large stimulation current and high output impedance conditions, high compliance voltage is necessary to preserve the accuracy of the output current and prevent it from saturation [43]. As a result, the high voltage requirement brought from the CCS will bring the safety challenges to a human body. Moreover, CCS also requires the high voltage CMOS technology to implement the circuits, which in turn increase the solution cost.

In terms of VCS, it features the simplest implementation (shown in Fig. 2.2-b) and thus the highest power efficiency among these three modes. Besides that, no high compliance voltage is required in using VCS. However, the charge delivered to the tissue using VCS can vary over a wide range, due to the tissue's load impedance. This variation can cause the safety concern for many applications [70].

The ChCS mode [98] offers a good balance between the design complexity and safety related issues. In virtue of the capacitor bank, the (well controlled) quantized amounts of charge are delivered to the tissue. Nevertheless, the capacitor bank needs to be implemented by the off-chip capacitors, which constrains its use in some applications.

A summary of the comparison of these three stimulation modes are provided in Table 2.2

|                                 | CCS  | VCS    | ChCS   |

|---------------------------------|------|--------|--------|

| Design complexity               | High | Lowest | Low    |

| Charge controllability (Safety) | Good | Poor   | Good   |

| Power efficiency                | Low  | High   | Medium |

Table 2.2: Comparison of three stimulation modes (after [70])

Table 2.3: Comparison of active and passive charge balancing techniques (after [70])

|                   | Active charge balancing    | Passive charge balancing                     |  |

|-------------------|----------------------------|----------------------------------------------|--|

| Design complexity | High                       | Low                                          |  |

| Solution size Low |                            | Large (mainly due to the blocking capacitor) |  |

|                   | High                       | Lower                                        |  |

| Adaptivity        | (can be used for different | (due to the larger time constant             |  |

|                   | stimulation parameter)     | from the blocking capacitor)                 |  |

[70]. Being aware of the safety requirements and the size budget from the application will aid the system designers in choosing the right stimulation modes.

In addition to the stimulation mode, the residual charge from either the monophasic or biphasic current stimulation is also a challenging issue. The residual charge during the stimulation cycles can increase the electrode voltage above the safe limit and thus jeopardize the human safety. Therefore, it is important to maintain the balanced charge in the stimulation cycles with the aid of dedicated circuits or components [135]. Currently, both active balancing techniques [42, 136, 137] and passive techniques [97, 138–140] are being used to tackle the charge unbalance issues. For the active charge balancing techniques, the charge in the stimulation is either being surveillanced in the real time [136] or corrected by a inserted discharging pulse [42] to achieve the balance. On the other hand, the counterpart passive solution can be implemented by a blocking capacitor [97, 138, 139] or the electrode discharge resistors [140]. A comparison between these two charge balance solutions is listed in Table 2.3 [70], from which we can see the active charge balancing technique is more versatile, while the passive one owns the lower design complexity. By choosing the proper charge balancing techniques to remove the residual charge, the electrode corrosion and the death of the cells can be well prevented.

## 2.3.3 Design Considerations for Wireless Telemetry

To provide the wireless programability of the stimulation pattern, the command signal needs to be modulated onto a carrier in the inductive link. As discussed in Section 2.2.3, the choice of the

|                                        | Active telemetry       | Passive telemetry   |

|----------------------------------------|------------------------|---------------------|

| Produce RF waves?                      | Yes                    | No                  |

| Power attenuation                      | Low                    | High                |

| Size of required antenna               | Small                  | Large               |

| Target implant size                    | Smaller                | Larger              |

| Typical location of the target implant | Deeper inside the body | Underneath the skin |

| Power consumption                      | High                   | Low                 |

| Favored data rate                      | High                   | Low                 |

Table 2.4: Comparison of active telemetry and passive telemetry (after [70])

Table 2.5: Comparison of three basic digital modulation schemes (after [70])

|                               | ASK       | FSK                   | PSK                                               |

|-------------------------------|-----------|-----------------------|---------------------------------------------------|

| Modulation parameter          | Amplitude | Frequency             | Phase                                             |

| Complexity of implementation  | Simple    | Medium                | High                                              |

| Noise rejection               | Poor      | Moderate              | Good                                              |

| Bandwidth and its utilization | Low       | Twice of ASK spectrum | Can achieve higher bandwidth utilization than FSK |

| Interference sensitivity      | High      | Less than ASK         | Less than ASK                                     |

modulation schemes introduced in Section 2.2.3 is based on the requirements of the application. In Table 2.4, a comparison was made between active telemetry and passive telemetry [70], which shows the active telemetry is more appropriate for the applications with high data rate, such as the retinal prosthesis. In contrast, the passive telemetry will be of favor when only a small quantity of data needs to be transmitted.

The comparison study of the three basic binary digital modulation schemes is shown in Table 2.5 [70]. For these schemes, a tradeoff exists among the implementation complexity, the data-rate and the rejection of the noise and interference. Among these metrics, the data-rate requirement of the applications plays an important role in the selection of the modulation schemes. Typically, the carrier frequency must be limited to a certain range to avoid the increased heat and power dissipation in the tissue [141]. Therefore, data-rate-to-carrier-frequency (DRCF) ratio [142] is introduced as a figure of merit in justifying the modulated data amount on a certain carrier frequency. Usually, a higher DRCF can be obtained from the binary FSK than from the ASK. This fact can be taken into account in the modulation choice decision. For the other applications requiring high data rate, PSK should be considered first due to its advantages in the bandwidth utilization.

One such an example is the retinal stimulator, in which a relatively high data rate is desired. In the forward data telemetry, 1000 pixels are needed to restore important visual function using [63]. To achieve the pixels requirements in the retinal prosthesis, each stimulator must be independently controlled to provide a customized stimulation pattern [123]. In [123, 143], PSK schemes are employed with novel techniques to overcome the data rate bottleneck caused by the budget of the acceptable power consumption. In [123], a data bandwidth reduction is achieved, and the data discard rate is reduced when the stimulation parameters are sent only by demand. Similarly, in [143], an on-chip address generator is introduced to take the initial address, while all other addresses are obtained following a programming rule.

In addition to the three basic schemes in Table 2.5, some other modulation schemes also exist. For instance, OOK and LSK are the special forms of the ASK. A notable feature of the LSK schemes is that the simultaneous power and data transfer is allowed at the same inductive link [144]. However, using the same link for both power and data raises a risk of power supply discontinuation when the secondary coil undergoes the short-circuiting condition for a certain period [70]. The pros and cons of LSK can also be considered in evaluating the proper schemes for the applications.

## 2.3.4 System Level Implementations

The discussion above demonstrates the design techniques and considerations to improve one or more metrics of implantable stimulators. Here, the system level state-of-the-art works are reviewed based on the four application category mentioned in Section 2.1.

In Table 2.6, the state-of-the-art works of the retinal prosthesis are presented. Due to the demand of the large volume data, the unidirectional data link must be carefully designed with the proper modulation scheme to provide the optimum data rate. In addition, the number of stimulation channels, the error rate in the data link, the resolution of the current generator (number of bits in DAC) and pixel size is also of concern in these designs to provide an acceptable visual quality to the patients. These considerations are taken care in the works shown in Table 2.6, without severe degrading of the overall chip size and power consumption.

In Table 2.7, the state-of-the-art works of the cochlear implants are surveyed. Since the quality of the generated current pulses from the stimulator will determine the hearing restoration, the amplitude and the resolution of the current source is the key parameter in the stimulator design [47]. On the other hand, compared with the other applications, the requirement for the

|                           | [114]   | [44]              | [146]      | [147]                  | [148]     | [149] | [43]      |

|---------------------------|---------|-------------------|------------|------------------------|-----------|-------|-----------|

| Year                      | 2013    | 2013              | 2012       | 2011                   | 2011      | 2011  | 2010      |

| CMOS technology (µm)      | 0.065   | 0.18 HV           | 0.35 HV    | 0.5                    | 0.35 HV   | 0.35  | 0.18 HV   |

| Area $(mm^2)$             | 14      | 37.6              | 64         | 5.3                    | 24        | 10.5  | 27.03     |

| # of stimulation channel  | 512     | 1024              | 1024       | 15                     | 98        | 1600  | 256       |

| Compliance voltage (V)    | ±2.5    | $\pm 10$          | ±10        | ±2.5                   | 8 to 20   | ±2    | ±10       |

| Current range (mA)        | 0-0.05  | 0.003-0.5         | 0.004-1    | 0.03-0.96              | 0.02-1.24 | 0-0.1 | 0.003-0.5 |

| Modulation                | PSK     | DPSK              | Photodiode | ASK                    | FSK       | N/A   | DPSK      |

| <b>Data-rate</b> $(Mb/s)$ | 20      | 2                 | 0.968      | 0.025-0.714            | 2.083     | N/A   | 2         |

| Data link bit             | N/A     | $2 \cdot 10^{-7}$ | N/A        | $10^{-2}$ to $10^{-5}$ | N/A       | N/A   | $10^{-4}$ |

| error rate (BER)          | IN/A    | 2.10              | 11/74      | (estimation)           | IN/A      | 11/1  | 10        |

| # of bits in DAC          | 4       | 7                 | 6          | 5                      | 7         | N/A   | 4         |

| Pixel size $(\mu m^2)$    | 260×260 | 303×337           | 500×470    | N/A                    | N/A       | 70×70 | 260×309   |

Table 2.6: State-of-the-Art retinal stimulators.

N/A: information not available.

HV: high voltage

|                                      | [47] | [150]  | [151]  | [152] | [134] |

|--------------------------------------|------|--------|--------|-------|-------|

| Year                                 | 2008 | 2007   | 2006   | 2005  | 2005  |

| <b>Power dissipation</b> (mW)        | N/A  | 0.047  | 2.5    | 0.126 | N/A   |

| CMOS technology (µm)                 | 0.35 | 0.7 HV | 0.7 HV | 0.8   | 1.5   |

| Area $(mm^2)$                        | 0.26 | 5.29   | 7      | 21    | 0.05  |

| # of stimulation channel             | N/A  | 16     | 4      | 16    | 4     |

| Compliance voltage $(V)$             | 4.77 | 13     | ±2     | N/A   | 4.25  |

| Maximum current(mA)                  | 1    | 1      | 0.5    | 0.7   | 0.21  |

| # of bits in DAC                     | 9    | 7      | 8      | 6     | 5     |

| <b>Output resistance</b> $(M\Omega)$ | >50  | N/A    | N/A    | N/A   | >10   |

Table 2.7: State-of-the-Art cochlear stimulators.

N/A: information not available.

HV: high voltage

wireless data telemetry is not crucial. Therefore, in the works shown in Table 2.7, the corresponding modulation and demodulation circuits were not designed as a tradeoff to save the overall chip size and power consumption.

In Table 2.8 and Table 2.9, the state-of-the-art works of the deep brain stimulators and some general neural stimulators are reviewed. The requirements of these two applications have many metrics in common. For example, the stimulators are usually incorporated into the recording systems in the neuroprosthetic devices to enable the bidirectional data communication on a closed-loop basis [145]. The specifications of the recording systems are not shown in these two tables because it is out of the scope of this work. However, it is worthwhile to note that the existence of the recording system reduce the power and chip area budget for the stimulators, while the bidirectional communication requirements raised the design complexity of the entire system. For the works shown in these two tables, the power dissipation, area, and data transmission rates are carefully considered to meet the design challenges discussed Section 2.2.

|                                        | [153]        | [53]      | [52]  | [51]      | [50]    | [154]     |

|----------------------------------------|--------------|-----------|-------|-----------|---------|-----------|

| Year                                   | 2016         | 2015      | 2014  | 2013      | 2012    | 2011      |

| <b>Power dissipation</b> ( <i>mW</i> ) | N/A          | N/A       | 0.468 | 15        | 4.1     | 0.375     |

| CMOS technology (µm)                   | 0.18         | 0.35      | 0.18  | 0.5       | 0.35 HV | 0.35      |

| Area $(mm^2)$                          | 7.74         | 12        | 4     | 2.25      | 0.71    | 10.9      |

| # of stimulation channel               | 8            | 4         | 8     | 4         | 3       | 4         |

| Current range (mA)                     | 0.0825-0.229 | 0.012-1.5 | 0-4.2 | 0.08-2.48 | 0-1.85  | 0-0.0945  |

| Stimulation frequency (Hz)             | 60-220       | 7.6-244   | N/A   | N/A       | N/A     | 1k - 1Meg |

| Modulation                             | LSK/ASK      | OOK/LSK   | N/A   | ASK/LSK   | N/A     | FSK/OOK   |

| <b>Data-rate</b> $(Mb/s)$              | 2/0.1        | 0.0156    | 0.8   | 0.05      | N/A     | N/A       |

Table 2.8: State-of-the-Art deep brain stimulators.

N/A: information not available.

HV: high voltage

|                                  | [155]    | [155]    | [56]    | [55]   | [103]    | [49]  | [156]   |

|----------------------------------|----------|----------|---------|--------|----------|-------|---------|

| Year                             | 2017     | 2017     | 2016    | 2014   | 2013     | 2012  | 2010    |

| <b>Power dissipation</b> (mW)    | 18       | < 0.1    | 2.17    | 2.8    | 1.5      | 0.47  | 0.27    |

| CMOS technology (µm)             | 0.18 HV  | 0.18 SOI | 0.13    | 0.18   | 0.13     | 0.18  | 0.18    |

| Area $(mm^2)$                    | 29.5     | 9        | 16      | 13.47  | 12       | 4     | 4       |

| # of stimulation channel         | 160      | 16       | 64      | 1      | 64       | 10    | 64      |

| <b>Compliance voltage</b> (V)    | ± 12     | N/A      | N/A     | N/A    | 2        | N/A   | 1.8     |

| Current range (mA)               | 0.5      | 0-0.145  | 0.01-1  | 0-0.03 | 0.01-1.2 | 0-0.1 | 0-0.135 |

| Modulation                       | DPSK/LSK | ASK/LSK  | UWB/FSK | OOK    | UWB      | FSK   | N/A     |

| <b>Data-rate</b> ( <i>Mb/s</i> ) | 2        | N/A      | N/A     | 4      | 10       | 0.8   | N/A     |

Table 2.9: State-of-the-Art general neural stimulators.

N/A: information not available. HV: high voltage

SOI: silicon on insulator

# 2.4 Summary

In this chapter, the background of implantable stimulators is introduced first. After that, the design challenges and the design techniques to meet the requirements are presented. Last, the state-of-the-art works on implantable stimulators are reviewed based on the applications. Generally, the stimulators discussed in this section employ the digital modulation schemes to generate various AC stimulation patterns to meet different application requirements. As will be discussed in Chapter 4, the special application requirements of the iEAP-based muscle prosthesis (such as the requirements of the tunable DC output voltage) will be analyzed during the development of the stimulators. The proposed stimulator will employ a novel design technique (other than the digital communication schemes reviewed in this chapter) to provide the tuning capability of the LDO's DC output voltages to actuate the iEAPs.

# Chapter 3

# **High Precision Reference Circuits**

For all modern electronic systems, such as the voltage regulator in implantable stimulators, precise voltage reference circuits are essential building blocks. A key requirement of a voltage reference circuit is to generate a voltage that is independent of temperature variations. Thermal independence is particularly important in applications where maintaining a high level of accuracy is required across wide temperature ranges [157–164].

#### 3.1 Introduction

The most commonly used topology for the implementation of reference circuits is the BGR [165, 166]. A BGR is "ideally" designed to generate an output voltage that is referred to the bandgap energy of the background semiconductor material (which is strongly temperature independent). In Silicon (Si)-based technologies, the base-emitter voltage ( $V_{BE}$ ) is related to the bandgap energy, and so it has been utilized to develop BGR circuits. However, in addition to being related to the bandgap energy,  $V_{BE}$  is also a strong function of the temperature, depending linearly ( $\propto T$ ) and nonlinearly ( $\propto T \ln(T)$ ) on the temperature. Therefore, a major challenge in BGR design has been to find innovative ways to cancel the temperature dependent parameters in  $V_{BE}$ .

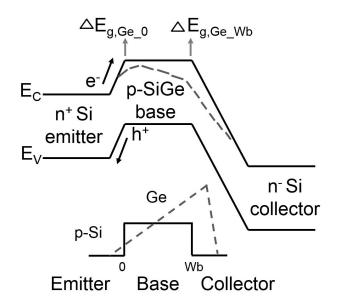

In a conventional BGR circuit, a PTAT component is generated to cancel the temperature dependency of  $V_{BE}$  only to the first order. However, due to the existence of the high-order temperature effects, these circuits offer medium performance and are not adequate for high performance applications. To improve the temperature stability of BGR circuits, a variety of high-order temperature compensation solutions have been proposed to cancel higher order temperature effects of  $V_{BE}$  related to  $T \ln(T)$  [167–188]. The majority of these solutions cancel a few higher order terms, leaving out some levels of temperature dependency in the output voltage. In this chapter, three different kinds of curvature compensation techniques for BGR circuits are presented using IBM's Silicon-Germanium (SiGe) BiCMOS technology.

This chapter is organized as followings. A brief review of the SiGe BiCMOS technology and the design challenges of the BGR circuits are given in Section 3.2 and Section 3.3. In Section 3.4, a novel BiCMOS-based compensation technique is introduced which aims to "*directly*" cancel the nonlinear term  $T \ln(T)$  in the  $V_{BE}$ , thereby, offering the possibility of achieving fully temperature-independent BGR circuits. In Section 3.5, a temperature compensation technique based on the weighted difference of Si-Si and SiGe-Si p - n junction voltages for SiGe reference circuits is presented. In Section 3.6, a systematic piecewise curvature-corrected compensation technique is proposed.

## 3.2 Thermal Characteristics of the Devices in the SiGe BiCMOS Technology

The circuits proposed in this chapter are implemented in IBM's SiGe BiCMOS 8HP technology. In this section, the 8HP technology is introduced first. Then the operation and the thermal characteristics of CMOS, BJT and SiGe HBTs, available in this process are described.

#### 3.2.1 SiGe BiCMOS technology

The SiGe BiCMOS technology, by offering high-speed, low-noise bandgap-engineered HBTs while maintaining integration capability with conventional Si CMOS [189,190], has emerged as a promising technology platform for the realization of a wide variety of analog, RF and mixed-signal circuits. Examples include voltage regulators [160, 191], high-speed data converters [192, 193], comparators [194], oscillators [195], RF amplifiers [196, 197], and microprocessors [198].

Generally, in analog and mixed-signal designs using this technology, the key device parameters of SiGe HBTs, such as the current gain ( $\beta$ ), the cut-off frequency ( $f_T$ ), the Early voltage ( $V_A$ ) and the transconductance ( $g_m$ ), are exploited for improved circuit performance, and designs are complemented by using CMOS transistors [199].

For this study, IBM's third-generation SiGe BiCMOS 8HP technology has been utilized.

| Parameters                   | Values |  |  |

|------------------------------|--------|--|--|

| $W_{E,eff}(\mu m)$           | 0.12   |  |  |

| $peak \; eta$                | 400    |  |  |

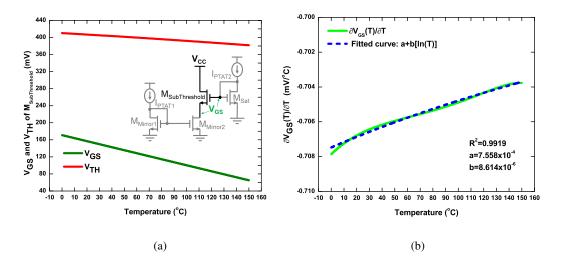

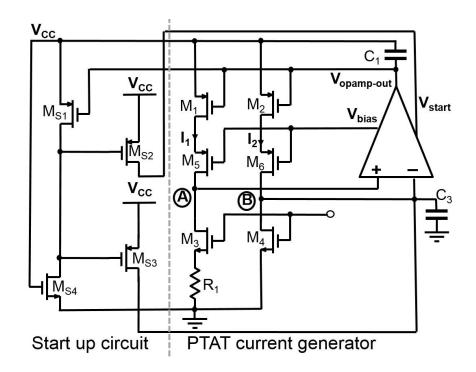

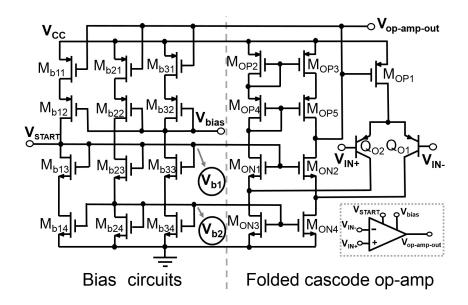

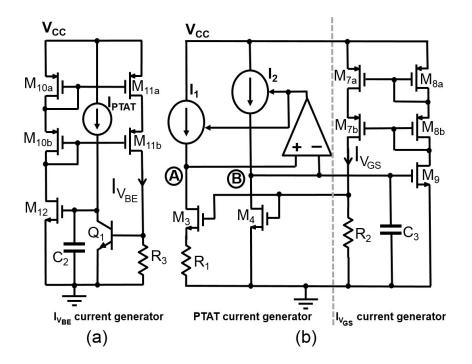

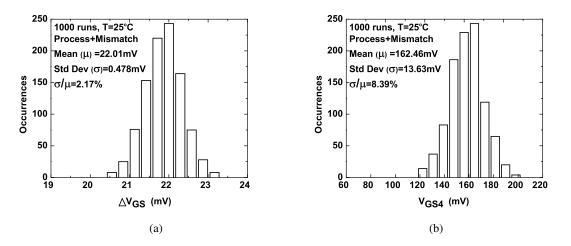

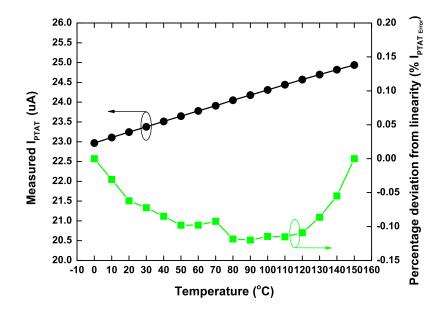

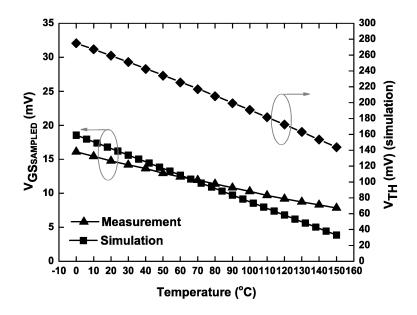

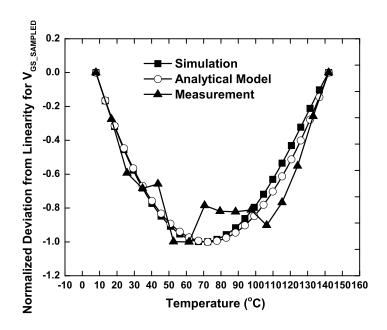

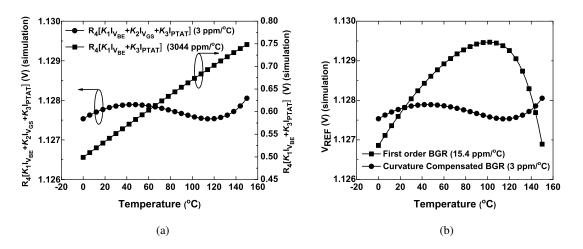

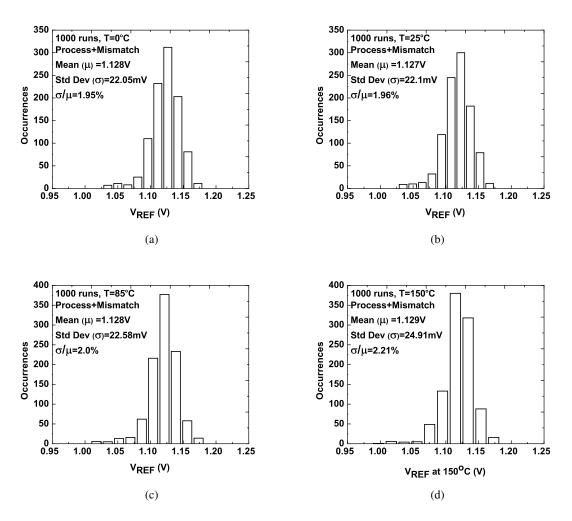

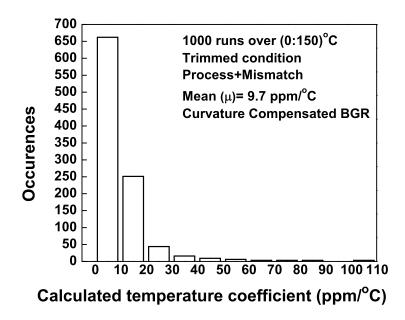

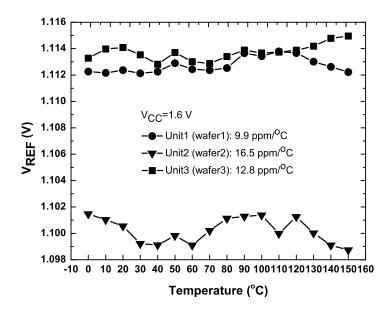

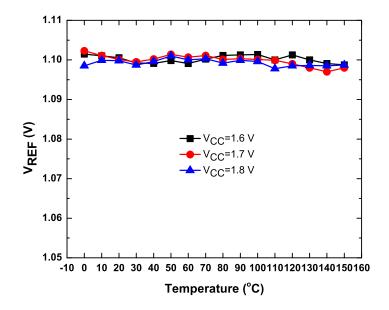

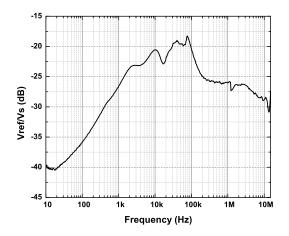

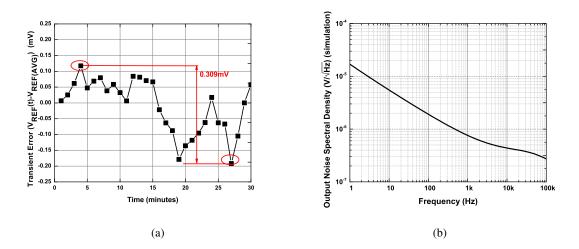

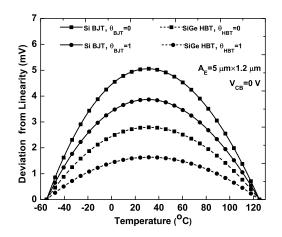

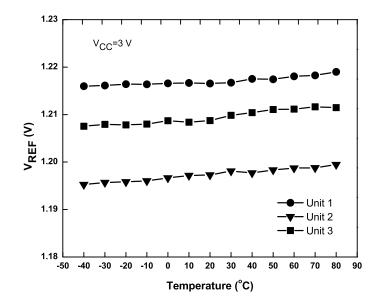

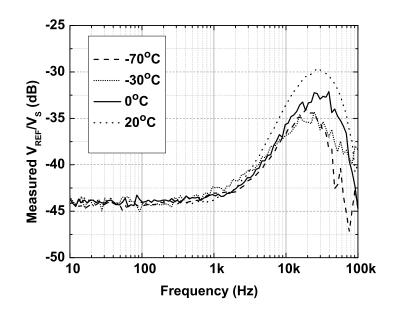

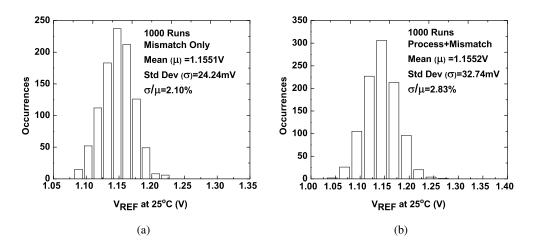

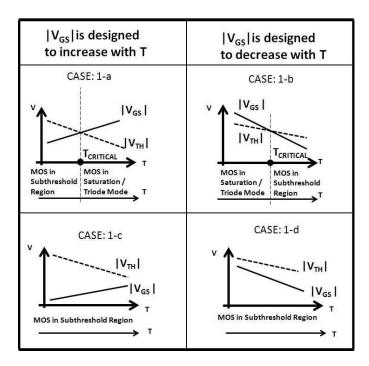

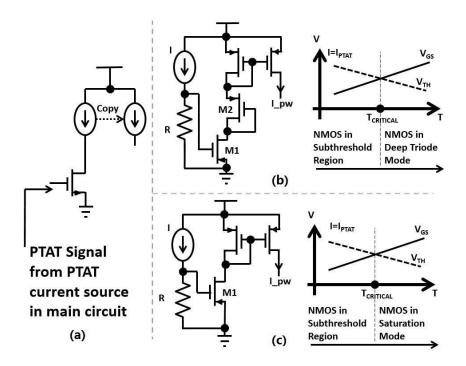

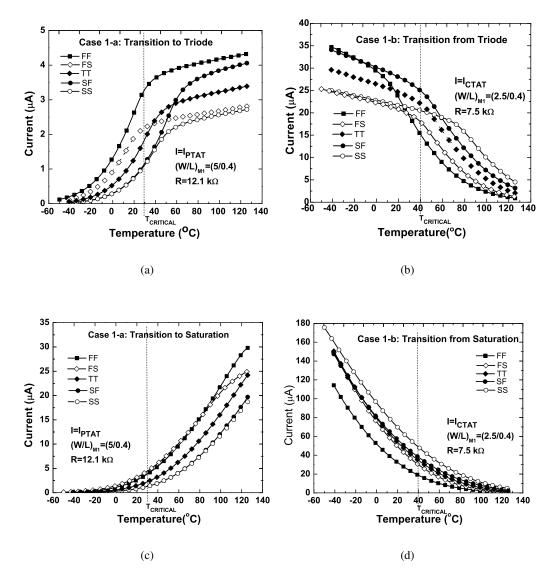

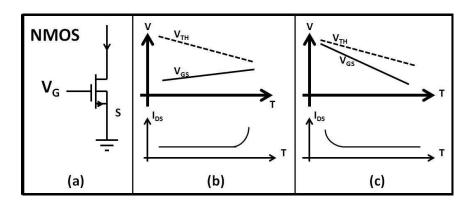

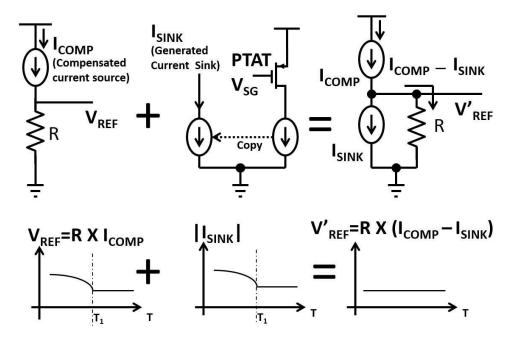

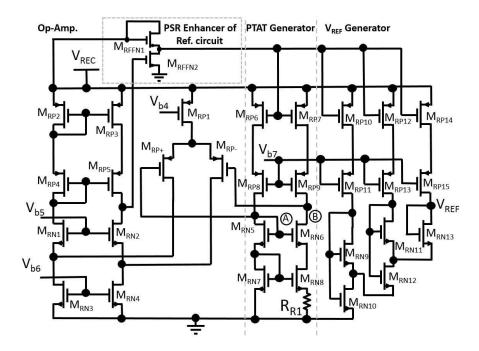

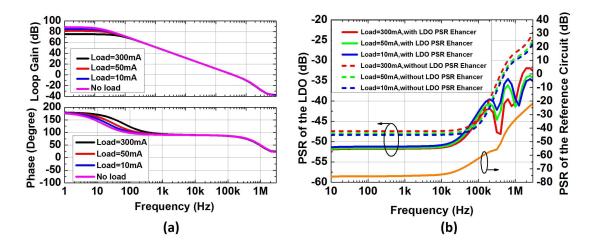

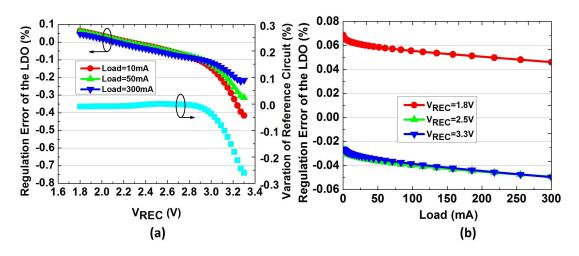

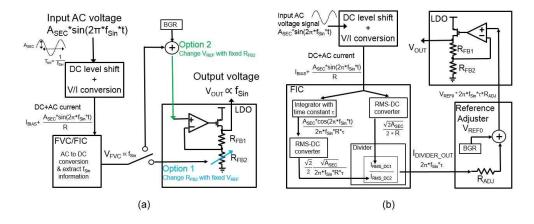

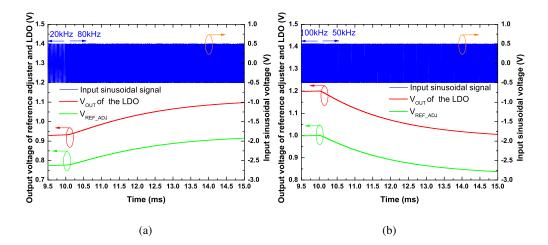

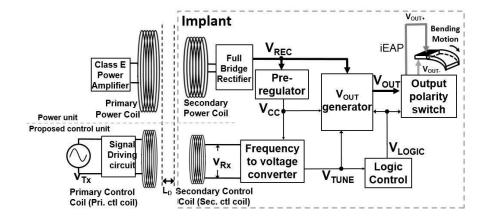

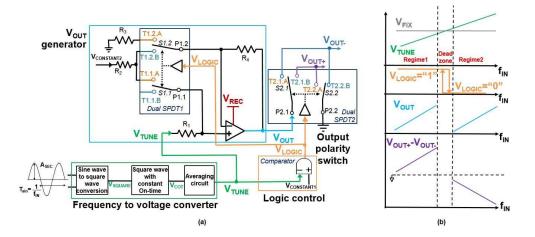

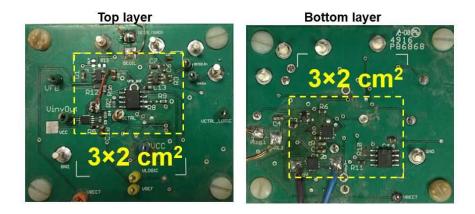

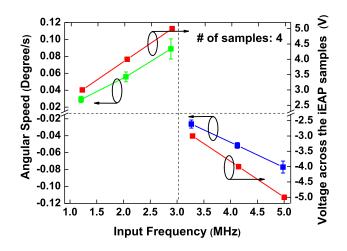

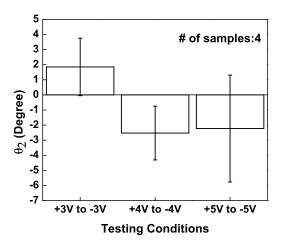

| $V_A(V)$                     | > 150  |  |  |