### IMPROVING AND COMPLEMENTING VIRTUAL MEMORY USING HARDWARE TECHNIQUES

by

#### GUILHERME MOTA CAVALCANTI DE ALBUQUERQUE COX

A dissertation submitted to the School of Graduate Studies Rutgers, The State University of New Jersey In partial fulfillment of the requirements For the degree of Doctor of Philosophy Graduate Program in Computer Science Written under the direction of Abhishek Bhattacharjee And approved by

> New Brunswick, New Jersey October, 2018

#### ABSTRACT OF THE DISSERTATION

### Improving and Complementing Virtual Memory Using Hardware Techniques

### by GUILHERME MOTA CAVALCANTI DE ALBUQUERQUE COX Dissertation Director: Abhishek Bhattacharjee

Virtual memory is a classic computer science abstraction and is ubiquitous in all scales of computing today. However, despite years of research, virtual memory faces critical performance and security challenges. This thesis aims to address these challenges. The first challenge we address is the growing performance overheads faced by virtual memory as workloads continue demanding ever-increasing amounts of memory. The key culprit of these overheads is address translation, the mechanism by which virtual memory translates a program's virtual addresses to physical addresses. Performing fast address translation requires the design of fast and efficient hardware translation lookaside buffer (TLB) caches. Unfortunately, TLBs struggle to perform efficiently for "big data" workloads. This thesis proposes a range of hardware mechanisms to improve TLB performance. The second challenge we address pertains to the security mechanisms offered by the virtual memory abstraction through memory protection and process isolation. Despite their utility, protection/isolation are insufficient to avoid important classes of remote attacks. Attackers can corrupt the operating system and thereby gain control of the entire machine. Therefore, there is a need for security mechanisms complementary to those provided by virtual memory. We propose lowoverhead mechanisms achieve this. Our approach is to build hardware that can snapshot

physical memory in an efficient manner, so that we can enable faster/better memory forensics to enhance system security.

Both sets of studies highlight some important themes in this thesis. One unifying theme of our work is to build hardware mechanisms that are transparent to application developers and systems programmers. Another unifying theme is ease of implementation – we deliberately use hardware mechanisms that require modest hardware modifications. In situations when the modifications are more substantial, we formally verify the correctness of our approach. Finally, we quantify the benefits of our approaches using not only software performance models (like most architecture studies), but also go beyond by quantifying real-system performance when possible.

### Acknowledgements

A Ph.D. is a long journey where persistence and endurance are put to the test. Throughout my years in the program, I am happy to say that many things were accomplished beyond the degree. I have learned about how to research in Systems in Computer Science. I met an incredible amount of really smart people who helped me along the way. I made great friends, people that are going to be present in my life for the rest of it.

Chronologically, I must recognize and thank the support, the letters of recommendation, and the incentive given by Cristiana Bentes and Ricardo Farias, my Masters co-advisors in Brazil. They paved the way for me to be admitted into the Rutgers Ph.D. program. Along with them, my friend David Cluxton who played a fundamental role in my preparation for the entrance exams. Ricardo Bianchini, for having accepted me to the program and helped me find my research advisor.

I am grateful for the opportunity to learn from and interact with many faculty members from Rutgers, particularly Liviu Iftode, Santosh Nagarakatte, Thu Nguyen, Ulrich Kremer, and Vinod Ganapathy.

I would not have completed my Ph.D. without the guidance, support, and trust of my advisor Abhishek Bhattacharjee. The thorough, detailed, forward-looking way to brainstorm new ideas and projects has been vital to the success of my Ph.D. More than an advisor, we have become friends after so many heated and inspiring debates.

I was lucky to work with a group of motivated and bright fellow students. The members of the RUArch lab and the systems group at Rutgers: Bill Katsak, Binh Pham, Chris Woithe, Jae Woo Joo, Jan Vesely, Karthik Sriram, and Zi Yan. Members of the extinct DarkLab: Cheng Li, Inigo Goiri, Luiz Ramos, and Qingyuan Deng.

My wife Marina who joined me in this adventure, my daughter that unknowingly

raised the bar by keeping me awake more than what one would expect, but also rewarding me every time that I came back home from the lab. My mother Marize and sisters Gabriela and Roberta, for all the remote, but important, support.

Finally, the support of friends and family, people that one way or another helped me cope with the challenges of the Ph.D. Dedication

To my wife Marina, my daughter Olivia, along with my family and friends for their encouragement, support, and unconditional love.

## Table of Contents

| Al            | Abstract                                      |         |                                                            |     |  |  |  |  |  |

|---------------|-----------------------------------------------|---------|------------------------------------------------------------|-----|--|--|--|--|--|

| A             | Acknowledgements                              |         |                                                            |     |  |  |  |  |  |

| De            | Dedication                                    |         |                                                            |     |  |  |  |  |  |

| $\mathbf{Li}$ | st of                                         | Tables  | 5                                                          | xi  |  |  |  |  |  |

| Li            | st of                                         | Figure  | es                                                         | xii |  |  |  |  |  |

| 1.            | Intr                                          | oducti  | on                                                         | 1   |  |  |  |  |  |

|               | 1.1.                                          | My Re   | esearch Contributions                                      | 4   |  |  |  |  |  |

|               |                                               | 1.1.1.  | Efficient Address Translation for Multiple Page Sizes      | 5   |  |  |  |  |  |

|               |                                               | 1.1.2.  | Scalable Distributed Shared Last-Level TLBs                | 6   |  |  |  |  |  |

|               |                                               | 1.1.3.  | Scheduling Page Table Walks for Irregular GPU Applications | 7   |  |  |  |  |  |

|               |                                               | 1.1.4.  | Secure, Consistent, and Fast Memory Snapshotting           | 7   |  |  |  |  |  |

|               | 1.2.                                          | Thesis  | Organization                                               | 8   |  |  |  |  |  |

| 2.            | Effic                                         | cient A | Address Translation for Multiple Page Sizes                | 9   |  |  |  |  |  |

|               | 2.1.                                          | Introd  | uction                                                     | 9   |  |  |  |  |  |

|               | 2.2.                                          | Scope   | of This Work                                               | 12  |  |  |  |  |  |

|               | 2.3.                                          | High-I  | Level Approach                                             | 13  |  |  |  |  |  |

|               | 2.4.                                          | Hardw   | vare Details                                               | 16  |  |  |  |  |  |

|               |                                               | 2.4.1.  | MIX TLB Entries                                            | 17  |  |  |  |  |  |

|               |                                               | 2.4.2.  | MIX TLB Operation                                          | 19  |  |  |  |  |  |

|               | 2.4.3. Interactions with Replacement Policies |         |                                                            |     |  |  |  |  |  |

|               |                                               | 2.4.4.  | OS Operations                                              | 22  |  |  |  |  |  |

|               |                                               | 2.4.5.  | Hardware and Energy Complexity                             | 24  |  |  |  |  |  |

|    | 2.5. | Compa   | arison to Past Work                                    | 24 |

|----|------|---------|--------------------------------------------------------|----|

|    |      | 2.5.1.  | Multi-Indexing Methods                                 | 25 |

|    |      | 2.5.2.  | Prior Work on Page Allocation Contiguity               | 26 |

|    | 2.6. | Metho   | dology                                                 | 27 |

|    |      | 2.6.1.  | Real-System CPU Measurements                           | 27 |

|    |      | 2.6.2.  | CPU Simulations and Analytical Models                  | 27 |

|    |      | 2.6.3.  | GPU Simulation                                         | 28 |

|    |      | 2.6.4.  | Workloads                                              | 28 |

|    | 2.7. | Evalua  | ation                                                  | 29 |

|    |      | 2.7.1.  | OS Page Allocation Characterization                    | 29 |

|    |      | 2.7.2.  | Results                                                | 34 |

|    | 2.8. | Conclu  | usion                                                  | 39 |

| 3. | Scal | lable E | Distributed Shared Last-Level TLBs                     | 41 |

|    | 3.1. | Introd  | uction                                                 | 41 |

|    | 3.2. |         | round and Motivation                                   | 43 |

|    |      | 3.2.1.  | Limitations of Private TLBs and Promise of Shared TLBs | 43 |

|    |      | 3.2.2.  | Shared L2 TLB Hit Rates                                | 44 |

|    |      | 3.2.3.  | Shared TLB Access Time                                 | 45 |

|    |      | 3.2.4.  | Shared TLB Performance                                 | 46 |

|    |      | 3.2.5.  | Understanding Shared L2 TLB Access Patterns            | 47 |

|    |      | 3.2.6.  | Low-Latency Interconnects                              | 50 |

|    | 3.3. | NOCS    | TAR Design                                             | 51 |

|    |      | 3.3.1.  | TLB Organization: Distributed TLB slices               | 51 |

|    |      | 3.3.2.  | TLB Interconnect                                       | 52 |

|    |      |         | Datapath: Latchless Switches                           | 52 |

|    |      |         | Control Path: Fine-Grained Circuit-Switching           | 53 |

|    |      |         | Implementation                                         | 54 |

|    |      | 3.3.3.  | Timeline of L2 TLB Access in NOCSTAR                   | 55 |

|    |                | 3.3.4. L2 TLB Access Latency and Energy 5                 | 7  |

|----|----------------|-----------------------------------------------------------|----|

|    |                | 3.3.5. Insertion/Replacement Policy                       | 8  |

|    |                | 3.3.6. Handling Page Table Walks                          | 8  |

|    |                | 3.3.7. TLB Shootdowns                                     | 9  |

|    | 3.4.           | Methodology                                               | 0  |

|    | 3.5.           | Experimental Evaluations                                  | 1  |

|    | 3.6.           | Conclusions                                               | 2  |

| 4. | $\mathbf{Sch}$ | eduling Page Table Walks for Irregular GPU Applications 7 | '3 |

|    | 4.1.           | Introduction                                              | 3  |

|    | 4.2.           | Background and the Baseline                               | 5  |

|    |                | 4.2.1. Execution Hierarchy in a GPU                       | 5  |

|    |                | 4.2.2. Virtual Address Translation in GPUs                | 7  |

|    | 4.3.           | The Need for Smarter Scheduling of Page Table Walks       | 9  |

|    |                | 4.3.1. Shortest-job-first Scheduling of Page Table Walks  | 1  |

|    |                | 4.3.2. Batch-scheduling of Page Table Walk Requests       | 2  |

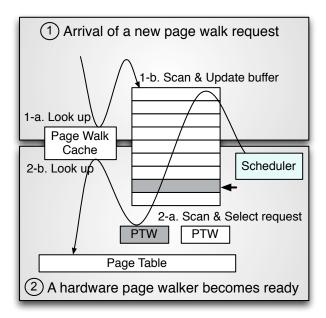

|    | 4.4.           | Design and Implementation                                 | 5  |

|    | 4.5.           | Evaluation                                                | 9  |

|    |                | 4.5.1. Methodology                                        | 9  |

|    |                | 4.5.2. Results and Analysis                               | 1  |

|    |                | Analyzing Sources of Speedup                              | 2  |

|    |                | Sensitivity Analysis                                      | 5  |

|    | 4.6.           | Discussion                                                | 7  |

|    | 4.7.           | Related Work                                              | 8  |

|    |                | 4.7.1. TLB Management                                     | 8  |

|    |                | 4.7.2. Scheduling in Memory Controllers                   | 0  |

|    |                | 4.7.3. Work Scheduling in GPUs                            | 1  |

|    | 4.8.           | Conclusion                                                | 1  |

| 5. | Secu  | ure, Co | $\mathbf{D}$ on sistent, and High-Performance Memory Snapshotting . 102                                                                            |

|----|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.1.  | Introd  | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $102$                                                                                 |

|    | 5.2.  | Overvi  | ew and Threat Model                                                                                                                                |

|    | 5.3.  | Design  | of SnipSnap $\ldots \ldots \ldots$ |

|    |       | 5.3.1.  | Snapshot Consistency                                                                                                                               |

|    |       | 5.3.2.  | Triggering Snapshot Acquisition                                                                                                                    |

|    |       | 5.3.3.  | DRAM and Memory Controller Design                                                                                                                  |

|    |       | 5.3.4.  | Near-Memory Processing Logic                                                                                                                       |

|    |       | 5.3.5.  | Snapshot Driver and HW/SW Interface                                                                                                                |

|    |       | 5.3.6.  | Formal Verification                                                                                                                                |

|    | 5.4.  | Securi  | ty Analysis                                                                                                                                        |

|    | 5.5.  | Experi  | mental Methodology 125                                                                                                                             |

|    |       | 5.5.1.  | Evaluation Infrastructure                                                                                                                          |

|    |       | 5.5.2.  | Workloads                                                                                                                                          |

|    | 5.6.  | Evalua  | tion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $127$                                                                                   |

|    |       | 5.6.1.  | Performance Impact on Target Applications                                                                                                          |

|    |       | 5.6.2.  | CoW Analysis                                                                                                                                       |

|    | 5.7.  | Relate  | d Work                                                                                                                                             |

|    | 5.8.  | Conclu  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $134$                                                                                                    |

| 6. | Sun   | nmary   |                                                                                                                                                    |

| AĮ | open  | dix A.  | SnipSnap TLA+ Model                                                                                                                                |

| Re | efere | nces .  |                                                                                                                                                    |

## List of Tables

| 3.1. | TLB interconnect design choices                                                                                      | 51 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 3.2. | Major configurations of TLB that were simulated                                                                      | 61 |

| 3.3. | Speedups for a 32-core Haswell system. We study the impact of prefetch-                                              |    |

|      | ing, hyperthreading, and page table walk latencies on the speedups achieved $% \left( {{{\bf{n}}_{\rm{s}}}} \right)$ |    |

|      | by NOCSTAR and other shared L2 TLB configurations versus private L2 $$                                               |    |

|      | TLBs. Speedup averages across workloads, as well as minima/maxima                                                    |    |

|      | are shown                                                                                                            | 68 |

| 4.1. | The baseline system configuration.                                                                                   | 90 |

| 4.2. | GPU benchmarks for our study                                                                                         | 90 |

# List of Figures

| 1.1. | Thesis overview                                                                          | 1  |

|------|------------------------------------------------------------------------------------------|----|

| 2.1. | Percentage of runtime devoted to address translation, running natively                   |    |

|      | on Intel Haswell with Linux (green). We assume cases where the OS                        |    |

|      | allocates only one page size (4KB, 2MB, 1GB) and when page sizes are                     |    |

|      | mixed. We compare performance against an ideal case where all TLB                        |    |

|      | resources are well-utilized (blue)                                                       | 10 |

| 2.2. | Example address space in an x86-64 architecture. We show 4KB frame                       |    |

|      | numbers in hexa<br>decimal. For example, translation ${\sf B}$ is for a 2MB page,        |    |

|      | made up of 4KB frame numbers $B0-B511.\ 2\mathrm{MB}$ translations $B-C$ are             |    |

|      | contiguous.                                                                              | 13 |

| 2.3. | Superpage B lookup and fill for split versus MIX TLBs                                    | 14 |

| 2.4. | Though superpages ${\sf B}$ and ${\sf C}$ are maintained by multiple sets but on         |    |

|      | lookup, we only probe the set corresponding to the 4KB region within                     |    |

|      | the superpage that the request is to                                                     | 15 |

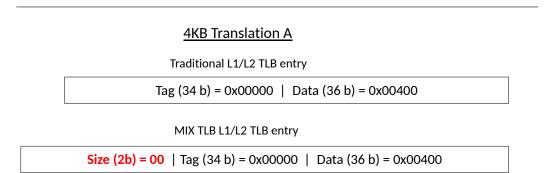

| 2.5. | Traditional TLB and $MIX$ TLB entries for the translation corresponding                  |    |

|      | to 4KB page $A.$ We show the TLB entries at the L1 and L2 level, assuming                |    |

|      | both have 4 sets. MIX TLBs require just an additional 2 bits to record                   |    |

|      | the page size                                                                            | 17 |

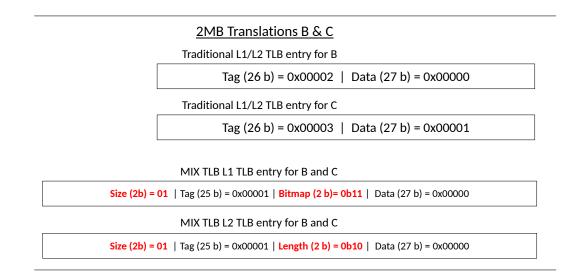

| 2.6. | Traditional TLB and $MIX\ TLB$ entries for the translation corresponding                 |    |

|      | to 2MB pages B-C. L1 MIX TLB and L2 MIX TLB entries use a bitmap                         |    |

|      | and a length field to record contiguous superpages, respectively. We                     |    |

|      | assume 2-set TLBs                                                                        | 18 |

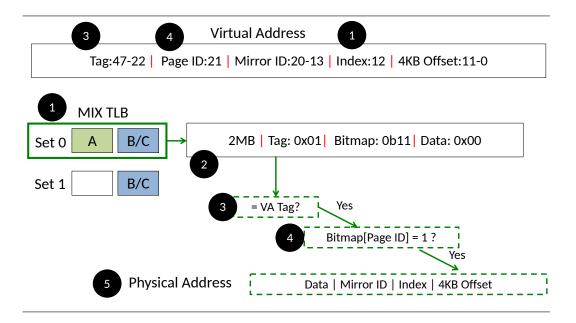

| 2.7. | ${\sf L1}{\sf MIX}{\sf TLB}$ lookup and hit (assuming a 2-set TLB). The physical address |    |

|      | is found using bit shifting and concatenation.                                           | 19 |

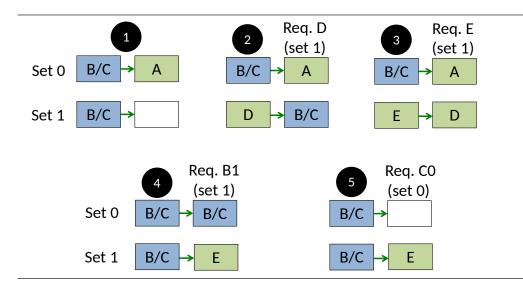

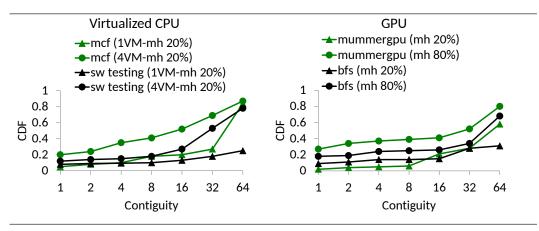

| 2.8. Replacement decisions are made independently on mirror copies, which       |    |

|---------------------------------------------------------------------------------|----|

| can cause duplication issues                                                    | 22 |

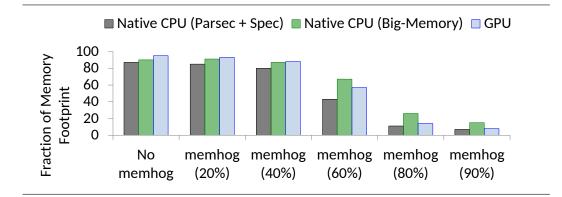

| 2.9. Fraction of memory footprint occupied by superpages, as fragmentation      |    |

| varies. Results shown for native CPUs and GPUs                                  | 30 |

| 2.10. Fraction of memory footprint occupied by superpages, as a function of the |    |

| memory fragmentation and VM consolidation. Results are for virtualized          |    |

| CPU workloads. N VM: M mh stands for N consolidated VMs, each with              |    |

| memhog running at M%                                                            | 31 |

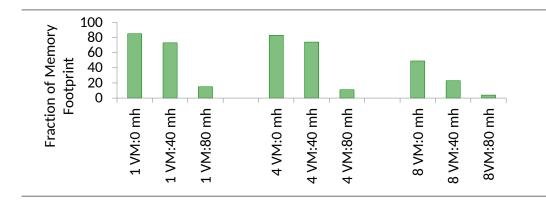

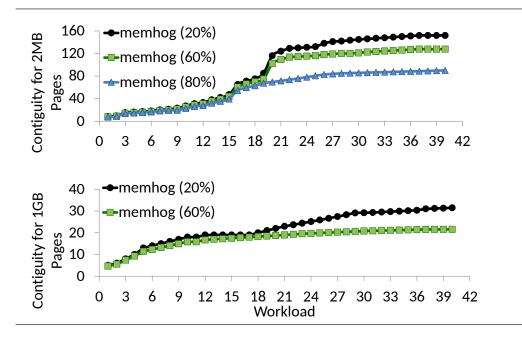

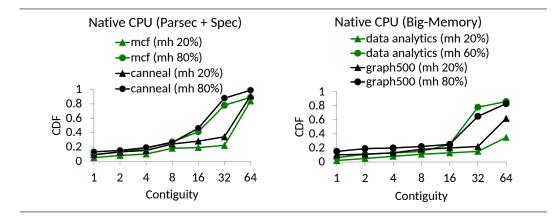

| 2.11. Average superpage contiguity for native and virtualized CPU, and GPU      |    |

| workloads. We show trends as memory fragmentation is increased with             |    |

| memhog, separately for 2MB and 1GB superpages                                   | 32 |

| 2.12. Superpage contiguity CDF as $memhog$ varies, for native CPU workloads.    | 33 |

| 2.13. Superpage contiguity CDF as membog varies, for virtualized CPU and        |    |

| GPU workloads                                                                   | 33 |

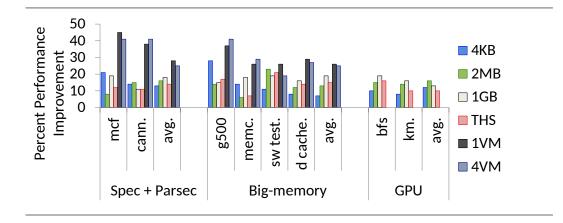

| 2.14. Percent performance improvement from $MIX TLBs$ compared to area-         |    |

| equivalent split TLBs.                                                          | 35 |

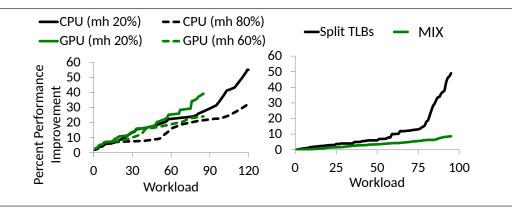

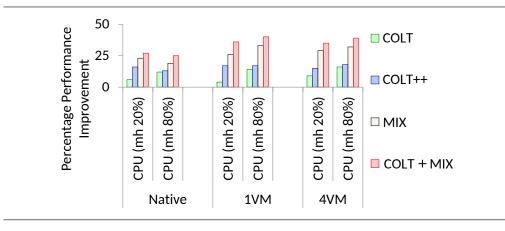

| 2.15. (Left) percentage performance improvement of $MIX\ TLBs$ versus split     |    |

| TLBs, with membog varying; (Right) Performance overheads of split               |    |

| TLBs and $MIX\ TLBs$ compared to ideal hypothetical TLBs which never            |    |

| miss                                                                            | 35 |

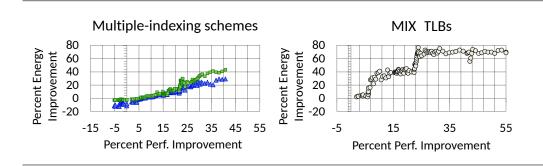

| 2.16. (Left) performance-energy tradeoffs for skew-associative TLBs with pre-   |    |

| diction (blue) and hash-rehash with prediction (green); and (Right) $MIX$       |    |

| TLB performance-energy tradeoffs.                                               | 37 |

| 2.17. Percentage of address translation dynamic energy devoted to various       |    |

| TLB maintenance operations                                                      | 37 |

| 2.18. Compared to split TLBs, performance improvements from $MIX\ TLBs$ and     |    |

| their combination with COLT                                                     | 39 |

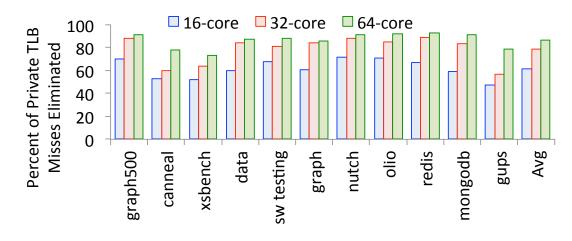

| 3.1. Percentage of private L2 TLB misses eliminated by replacing with a         |    |

| shared TLB. Results shown for 16-64-core systems                                | 44 |

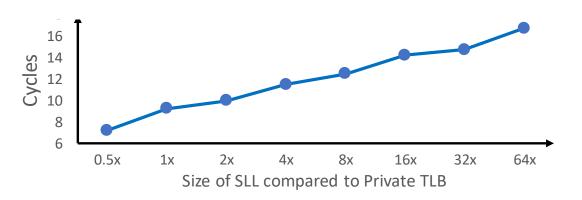

| 3.2. | Access latency of SRAM TLB compared to number of entries in a TLB.                                                                                                                 |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Post-synthesis in 28 <i>nm</i> TSMC PDK                                                                                                                                            | 45 |

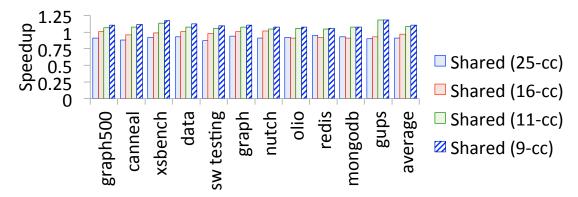

| 3.3. | Speedups using shared multi-banked TLBs over private L2 TLBs. Shared                                                                                                               |    |

|      | TLB access latencies varies from 25 to 9 cycles                                                                                                                                    | 46 |

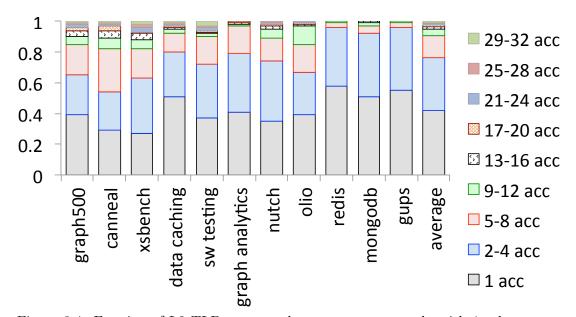

| 3.4. | Fraction of L2 TLB accesses that occur concurrently with 1 other access,                                                                                                           |    |

|      | 2-4 other accesses, etc., on a 32-core Haswell system                                                                                                                              | 48 |

| 3.5. | (Left) Fraction of L2 TLB accesses that occur concurrently with 1 other                                                                                                            |    |

|      | access, 2-4 other accesses, etc. Each bar averages results across work-                                                                                                            |    |

|      | loads; (right) fraction of L2 TLB accesses to a TLB slice that occurs                                                                                                              |    |

|      | concurrently with 1 other access to that slice, 2-4 other accesses to that                                                                                                         |    |

|      | slice, etc. Each bar shows a distributed shared L2 TLB, where the num-                                                                                                             |    |

|      | ber of TLB slices is equal to the number of cores                                                                                                                                  | 48 |

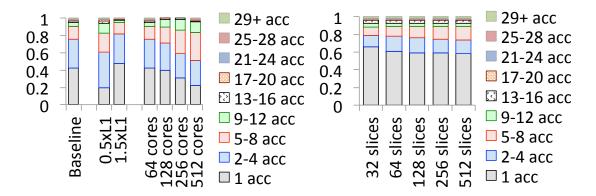

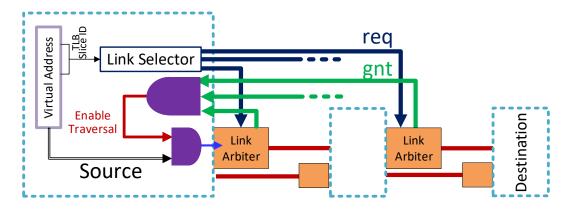

| 3.6. | (a) TLB hierarchy near each core in NOCSTAR. (b) Source and desti-                                                                                                                 |    |

|      | nation of a request and the path of taken by the request. (c) Micro-                                                                                                               |    |

|      | architecture of the switch which enables single cycle traversal through                                                                                                            |    |

|      | the network. (d) Cores that can send requests to a given arbiter                                                                                                                   | 52 |

| 3.7. | For setting up the path a core sends requests to all link arbiters in the                                                                                                          |    |

|      | path and waits for grants from them                                                                                                                                                | 54 |

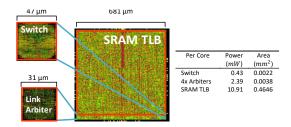

| 3.8. | Place-and-routed NOCSTAR tile in 28nm TSMC with the L2 TLB SRAM, $% \mathcal{A} = \mathcal{A}$ |    |

|      | switch and link arbiters highlighted and power/area of a switch and link                                                                                                           |    |

|      | arbiters for each slice in comparison to a SRAM based TLB slice. Target                                                                                                            |    |

|      | Clock Period = $0.5$ ns                                                                                                                                                            | 55 |

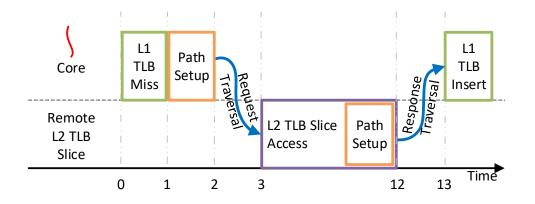

| 3.9. | Timeline of a virtual address translation in case of an L1 TLB miss and                                                                                                            |    |

|      | remote L2 TLB access in NOCSTAR                                                                                                                                                    | 56 |

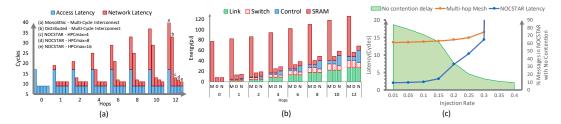

| 3.10 | . (a) Latency of each message in the TLB Interconnect in various configu-                                                                                                          |    |

|      | rations. (b) Energy consumed by each message in the TLB Interconnect                                                                                                               |    |

|      | in various configurations. (M)onolithic, (D)istributed, and (N)OCSTAR                                                                                                              |    |

|      | vs number of hops (c) Average latency of messages with respect to in-                                                                                                              |    |

|      | creasing injection rate in NOCSTAR interconnect compared to a multi-hop $% \mathcal{A}$                                                                                            |    |

|      | interconnect.                                                                                                                                                                      | 58 |

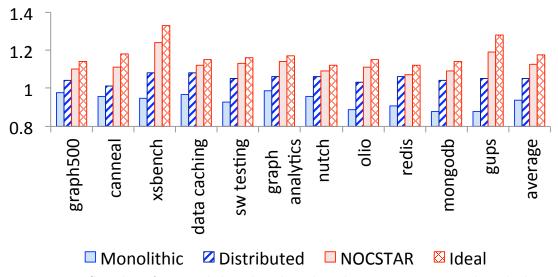

| 3.11. Speedups for monolithic, distributed, and NOCSTAR compared to ideal                                      |    |

|----------------------------------------------------------------------------------------------------------------|----|

| case with zero interconnect latency to the shared L2 TLB. Results assume                                       |    |

| 16-core Haswell systems using only 4KB pages                                                                   | 62 |

| 3.12. Complementary results to Figure 3.11 but when Linux uses transparent                                     |    |

| superpages for a mix of 4KB and 2MB pages                                                                      | 62 |

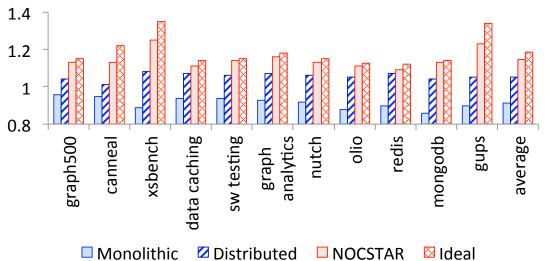

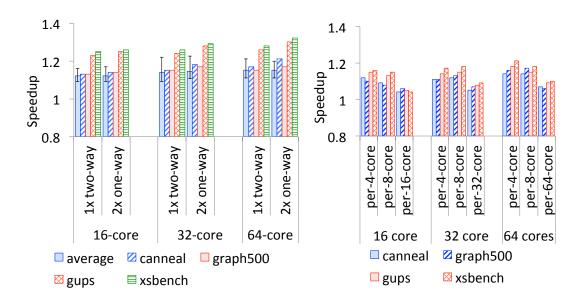

| 3.13. (Left) Speedups for varying core counts for Linux with transparent $2MB$                                 |    |

| superpage support; and (right) percent of address translation energy                                           |    |

| saved versus private L2 TLBs                                                                                   | 63 |

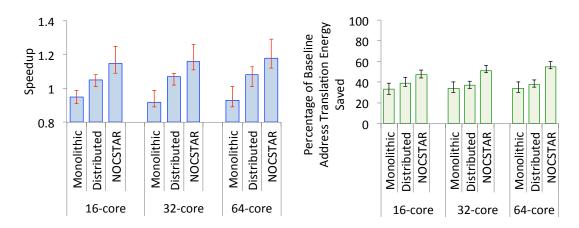

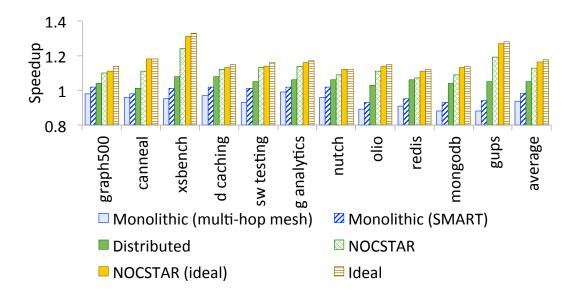

| 3.14. Speedup over baseline configuration with private L2 TLBs. We show                                        |    |

| two monolithic approaches (with traditional $\texttt{multi-hop}\ \texttt{mesh}\ \texttt{and}\ \texttt{SMART},$ |    |

| as well as an ideal NOCSTAR, where we have no contention on the                                                |    |

| interconnect. We compare this to an ideal case where the TLB slices                                            |    |

| have zero interconnect latency.                                                                                | 65 |

| $3.15.  ({\rm Left})$ Speedups with varying core counts versus private L2 TLBs for                             |    |

| round-trip acquire $(1 \times two-way)$ and one-way acquire $(2 \times one-way)$ ; and                         |    |

| (right) speedups of TLB invalidation policies                                                                  | 66 |

| 3.16. Page walks at requesting and remote core                                                                 | 67 |

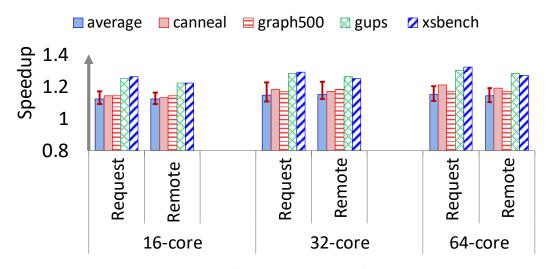

| $3.17.~({\rm Left})$ Overall throughput on $32$ cores with $330$ combinations of 4 work-                       |    |

| loads; and (Right) Speedup of the worst-performing sequential applica-                                         |    |

| tion over private L2 TLBs                                                                                      | 70 |

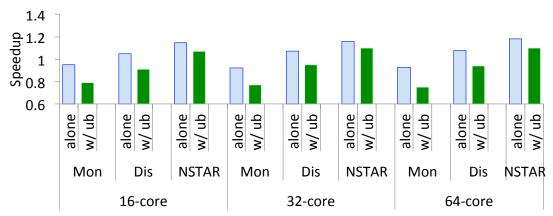

| 3.18. Average speedups for workloads versus private L2 TLB configuration,                                      |    |

| for varying core counts. Bars for <b>alone</b> represent results from when the                                 |    |

| workloads run alone (i.e., matching already-presented data). Bars for                                          |    |

| w/ub represent data for when the workloads were concurrently run with                                          |    |

| the TLB storm microbenchmark                                                                                   | 71 |

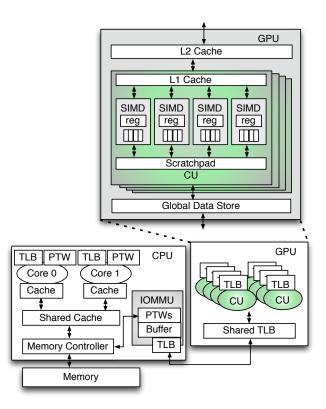

| 4.1. Baseline system architecture                                                                              | 76 |

| 4.2. Performance impact of page walk scheduling                                                                | 80 |

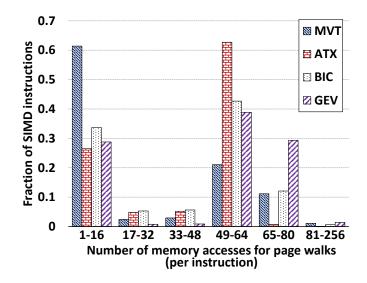

| 4.3. Distribution of number of memory accesses $(i.e., 'work')$ for servicing                                  |    |

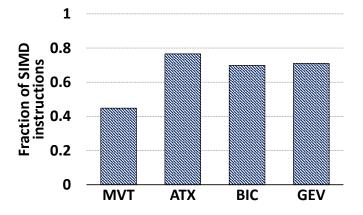

| address translation needs of SIMD instructions                                                                 | 82 |

|                                                                                                                |    |

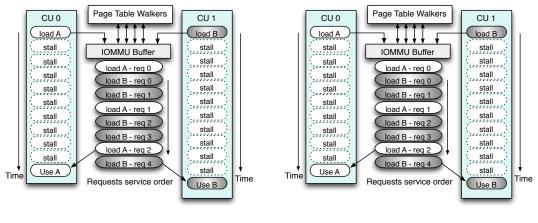

| 4.4.  | Impact of interleaving of a GPU's page walk requests.                              | 83  |

|-------|------------------------------------------------------------------------------------|-----|

| 4.5.  | Fraction of instructions whose page walk requests are interleaved with             |     |

|       | requests from other instructions.                                                  | 83  |

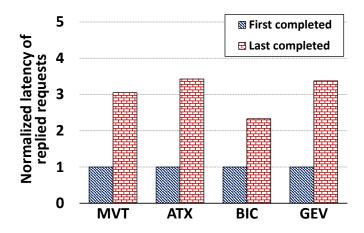

| 4.6.  | Average latencies of the first- and the last-completed page walk request           |     |

|       | per instruction.                                                                   | 84  |

| 4.7.  | Key components and actions of the SIMT-aware page table walk scheduler.            | 85  |

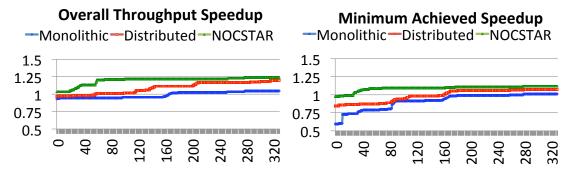

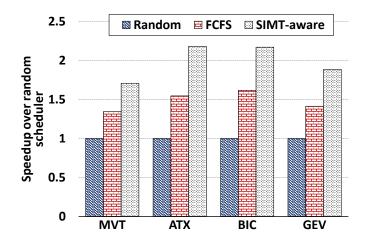

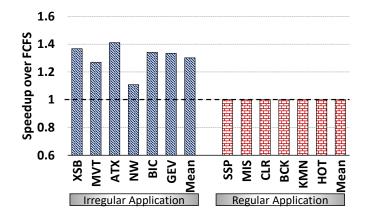

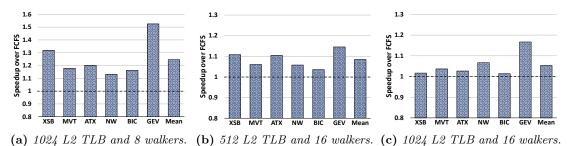

| 4.8.  | Speedup with SIMT-aware page walk scheduler                                        | 91  |

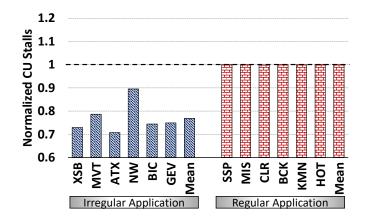

| 4.9.  | GPU stall cycles in execution stage.                                               | 92  |

| 4.10. | Latency gap between the first and the last-completed page walk request             |     |

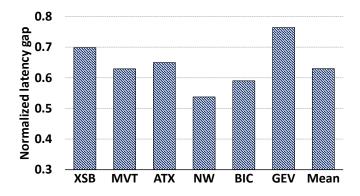

|       | per instruction.                                                                   | 93  |

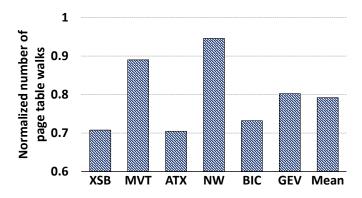

| 4.11. | Number of page walk requests with SIMT-ware scheduler normalized                   |     |

|       | over FCFS                                                                          | 94  |

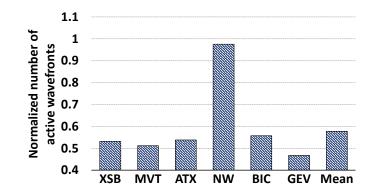

| 4.12. | Number of active wavefronts accessing the GPU's L2 TLB with SIMT-                  |     |

|       | aware scheduler (normalized over FCFS).                                            | 95  |

| 4.13. | Speedups with varying GPU L2 TLB size and page table walker counts.                | 95  |

| 4.14. | Speedups with varying IOMMU buffer size                                            | 96  |

| 5.1.  | Design tradeoffs in snapshot acquisition. (*) Virtualized systems provide          |     |

|       | tamper-resistance assuming that the hypervisor is trusted; however, at-            |     |

|       | tacks on hypervisors violate this assumption [71, 72, 73, 74, 75, 131].            |     |

|       | $(\star\star)$ While external hardware-based techniques were originally thought to |     |

|       | be tamper-resistant, a number of attacks have allowed malicious OSes               |     |

|       | to evade detection by hiding state from the external hardware mecha-               |     |

|       | nism [182, 113, 130]                                                               | 104 |

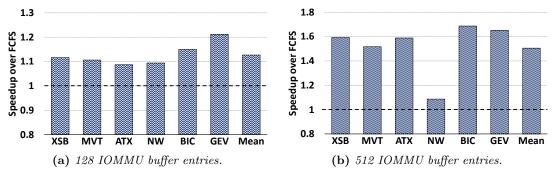

| 5.2.  | Architecture of SnipSnap. Only the on-chip hardware components are                 |     |

|       | in the TCB                                                                         | 107 |

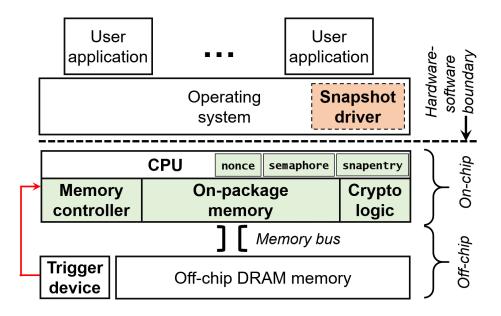

| 5.3. | Example showing need for snapshot consistency. Depicted above is the                     |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | memory state of a target machine at two points in time, T and T+ $\delta$ . At           |     |

|      | T, a pointer in $F_1$ points to an object in $F_2$ . At $T+\delta$ , the object has been |     |

|      | freed and the pointer set to NULL. Without consistency, the snapshot                     |     |

|      | could contain a copy of $F_1$ at time T and $F_2$ at time T+ $\delta$ (or vice-versa),   |     |

|      | causing problems for forensic analysis.                                                  | 110 |

| 5.4. | Layout of on-chip memory.                                                                | 114 |

| 5.5. | Pseudocode of the snapshot driver and the corresponding hardware/soft-                   |     |

|      | ware interaction.                                                                        | 117 |

| 5.6. | Description of benchmark user applications                                               | 126 |

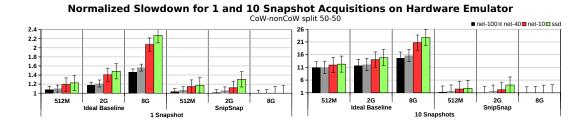

| 5.7. | Performance impact of snapshot acquisition from hardware emulator                        |     |

|      | studies. Slowdown caused by modern snapshot mechanisms that also as-                     |     |

|      | sure consistency, and compare against $SnipSnap$ . We plot results for 1                 |     |

|      | and 10 snapshots separately (note the different $y$ axes), showing aver-                 |     |

|      | ages, minima, and maxima amongst benchmark runtimes. X-axis shows                        |     |

|      | the amount of on-package memory available on the emulated system.                        |     |

|      | SnipSnap provides 1.2-22× performance improvements against current                       |     |

|      | approaches                                                                               | 127 |

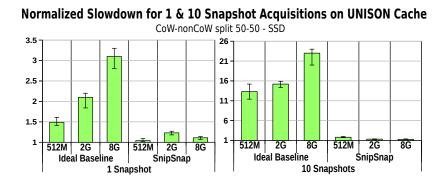

| 5.8. | Performance impact of snapshot acquisition from simulator studies with                   |     |

|      | UNISON cache [116]. SnipSnap outperforms idealized versions of current                   |     |

|      | snapshotting approaches by as much as $22 \times$ (graphs show benchmark                 |     |

|      | averages, maxima, and minima).                                                           | 129 |

| 5.9. | Average performance with varying off-chip DRAM size. Bigger off-chip                     |     |

|      | $DRAM\ takes\ longer\ to\ snapshot,\ so\ SnipSnap\ becomes\ even\ more\ advan-$          |     |

|      | $tageous \ over \ current \ idealized \ approaches.$ These results assume UNI-           |     |

|      | $SON\ cache\ with\ 8GB,\ split\ 50:50\ in\ CoW: non-CoW\ mode\ during\ snap-coW$         |     |

|      | shot acquisition and SSDs, taking just one snapshot. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 129 |

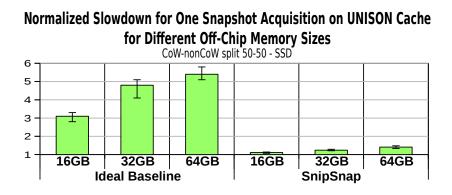

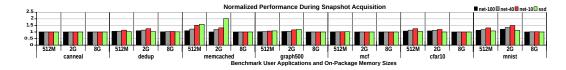

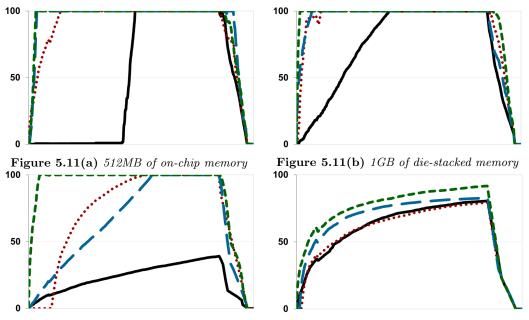

- 5.11. CoW area utilization over time for memcached. Y-axis shows CoW area percentage used to store page frames that have not yet been included in the snapshot. X-axis denotes execution progress. We measured CoW utilization for every 1024 snapshot entries recorded. The two charts show CoW utilization trends for various sizes of die-stacked memory and for different methods to write out the snapshot: . Snapshot acquisition does not impact memcached performance when CoW utilization is below 100%. 131

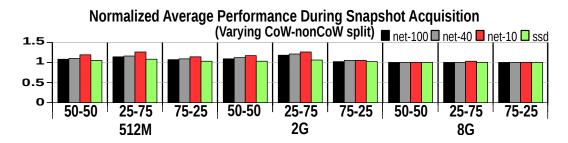

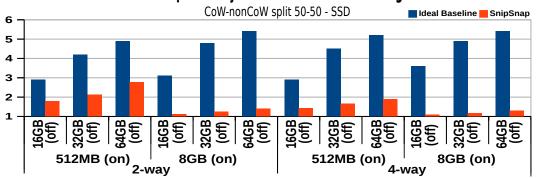

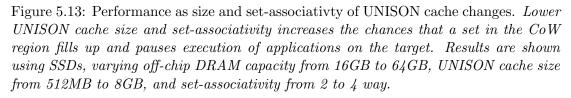

- 5.12. Performance impact of snapshot acquisition for different CoW-Cache partitions. Y-axis shows average performance impact of all benchmarks to take a snapshot, varying CoW-nonCoW partition for different cache sizes. X-axis shows different total sizes of die-stacked memory and various ways in which to partition die-stacked memory for CoW (50%, 25% and 75% for CoW).

### Chapter 1

## Introduction

Virtual memory is a classic computer science abstraction that has been vital to the success of computing over several decades. It used ubiquitously today in systems as diverse in scale as mobile devices, wearable devices, desktops/laptops, and even large-scale data centers. Virtual memory's success can be attributed to benefits for programmers: **programmability** and **security**. The mechanisms used to provide these benefits are *address translation* and *memory protection*, which are both implemented by all modern page-based virtual memory systems. Even though it is possible to implement these features without page-based virtual memory, all modern systems pack them as a whole. This thesis shows the pitfalls, however, facing the traditional virtual memory abstraction. We show that both address translation and memory providing the needs that modern systems have.

|               | Virtual Memory                                   |                                                |                                                                              |              |  |  |

|---------------|--------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|--------------|--|--|

|               | Program                                          | mmability                                      | Security                                                                     |              |  |  |

|               | via Addres                                       | s Translation                                  | via Memory Prot                                                              | ection       |  |  |

| Trend         | Problem                                          | Solution                                       | Problem                                                                      | Solution     |  |  |

| Heterogeneity | Unified VM for<br>CPUs and<br>accelerators       | MIX TLBs (§2)<br>Nocstar (§3)<br>PTW-Sched(§4) | Heterogeneity in the<br>techniques and platforms<br>used to enhance security | SnipSnap(§5) |  |  |

| Big data      | TLB reach for<br>ever-increasing<br>memory sizes | MIX TLBs (§2)<br>Nocstar (§3)                  | Security without<br>compromising performance                                 | SNIPSNAP(§5) |  |  |

Figure 1.1: Thesis overview

Figure 1.1 illustrates the overall structure of this thesis, the problems that focus on, and our approaches to solving these problems. Specifically, we focus on:

#### **Programmability:**

- Virtual memory improves programmability by enabling programmers to view memory as a flat and linear array of bytes, thereby hiding the complexity of the physical memory which is made up of a complex assortment of memory and storage devices [77, 76, 36, 98]. This means, however, that program virtual addresses must be translated to physical addresses on all memory references an operation known as address translation. The problem with address translation is that the structures that are used to accelerate it, such as Translation Lookaside Buffers (TLB), Memory Management Unit (MMU) caches, and Page Table Walkers (PTW), were built at a time when CPUs running single-threaded workloads were the de facto standard. Our world is very different today and these hardware structures have now suffer from performance problems [29, 66, 34]. Specifically, the advent of big data workloads means that CPUs as well has hardware accelerators (*e.g.*, GPUs, etc.) require infeasibly large TLBs for efficient translation. This is why, for example on CPUs, we find execution time overheads of up to 50% due to address translation [29, 66].

- While ensuring that the programmability benefits of virtual memory continue to be realized efficiently on CPUs is already challenging, these problems are even more pronounced when one considers hardware accelerators. Consider, for example, the GPU, which has become a key accelerator in the server, datacenter, cloud, and high-performance computing domains. GPUs also benefit from virtual memory when processing an ever-increasing set of general-purpose applications [13, 134]. However, implementing GPU virtual memory support is challenging because TLBs must be enormous to cope with the GPU's high levels of concurrency [175, 172, 195, 216, 24]. Consequently, GPU virtual memory overheads can slow down application runtime by as much as 3.7-4.0× [210, 195]. Such problems posed by heterogeneity are not restricted to GPUs alone for example, large TLBs are particularly ill-sutied for area-constrained fixed function units and other accelerators.

The first problem this thesis addresses is the design of more efficient address translation hardware for CPUs and hardware accelerators like GPUs.

#### Security:

- One of the underpinnings of modern computer security is the memory protection facility provided by virtual memory [111, 77, 76, 36]. Nevertheless, while memory protection is crucial to security, is not sufficient in and of itself [51, 191]. One important class of security vulnerabilities and a focus of our thesis that cannot be obviated by protection alone is that of remote rootkit attacks compromising systems software in data-center and cloud environments. The core reason that virtual memory is insufficient for these types of attacks is that it was conceived at a time predating modern security attacks. But today, the simple time-sharing mainframes that virtual memory was design on have given way to data-center environments with complex rack-scale systems with disaggregated or distributed shared memory running many layers of sophisticated software. Therefore, we now rely on mechanisms beyond memory protection to give us the security guarantees modern systems need. Our goal in this thesis is to show how we can built hardware complementary to virtual memory to enable techniques like memory forensics [51, 191] in this dramatically different computing landscape.

- Unfortunately, modern memory forensics techniques suffer from performance problems posed by increasing amounts of memory used by workloads. In particular, memory forensics need to take a snapshot – a scan of a workload's entire virtual address space and/or the system physical address space. As memory grows, so does the time taken to snapshot memory. Therefore our goal is to use hardware techniques to acquire snapshots quicker than the time it takes today (*e.g.*, minutes in a typical server to snapshot its memory), during which the entire machine and its services are stalled.

The second problem this thesis addresses is the question of complementing traditional virtual memory security mechanisms with hardware for faster snapshots and better memory forensics techniques.

#### **1.1** My Research Contributions

To detail solutions to the problems described above, I now provide a conceptual overview of the problems facing address translation and security.

Address Translation: The first topic in this thesis is faster address translation. We discuss two trends that make this challenging to achieve. The first trend is the advent of *heterogeneity*, or the integration of hardware accelerators. With heterogeneity, computer systems add accelerators on a chip. Writing code to exploit the benefits of these accelerators is complex [13, 134]. Additionally, accelerators have size, power, and performance constraints. To simplify the programming model with CPUs and accelerators, a single unified address space visible to all processing elements is desirable. The benefits of a unified address space are well established by recent studies [175, 172]. The benefits range from a pointer is a pointer semantics, *i.e.*, the idea that programmers can use the same data structure in any of the processing elements. Additionally, unified address spaces spare programmers from having to carefully managing data copies and data marshaling between processing elements. Providing a unified address space is one crucial step at the realization of a genuinely heterogeneous programming model. To achieve this, however, we need to implement efficient address translation hardware in all of our accelerators. This is problematic because many accelerators have tight area, energy, and power constraints. We explore the question of how to design efficient TLB for all of our accelerators, specifically in the context of programmable GPUs.

A related question that affects address translation is that of physical memory capacity. Along with increasing heterogeneity in processing, vendors are also adopting heterogeneity in memory. Ultimately, this means that the physical address space is growing fast to keep pace with the needs of big data workloads. This is the second trend motivating our work – "big data". Unfortunately, big-data workloads necessitate larger TLBs to enable access to data efficiently. The questions that arise are: How can we scale our TLBs? How can we particularly scale our TLBs for area-constrained accelerators? These are the problems our work addresses in Chapters 2, 3, and 4.

Security: We use the same two trends to address the second problem of this thesis, which is to improve security on modern systems. We have already established that the VM memory protection is not sufficient to fully secure a modern computer system. The challenge is on how to enhance security for the type of heterogeneous systems that we discussed above, which may potentially run a range of operating systems, be connected to a vast variety of peripherals, etc. To take a step towards holistic security, we complement memory protection with memory forensics. Memory forensics is a branch of computer forensics that focuses on acquiring and analyzing all the data in memory. After these analyses, the system is deemed to be corrupted or secure. What is still an open problem is how to acquire the entire physical memory of a computer system in a secure, complete, consistent, and efficient manner. We explore this problem in this thesis, showing that our mechanism to snapshot the memory achieves all of these properties. All prior techniques can be categorized into two groups: non-consistent but fast snapshots, or consistent but slow snapshots. Non-consistent and fast snapshots do not halt the machine while acquiring the data. However, their non-consistency means that memory analysis tools may not be able to detect all manners of attacks. On the other hand, consistent snapshots overcome this problem, but with a pernicious performance penalty. This performance penalty is worsening because of "big data" trends. Our solution provides a highly efficient, secure and consistent memory snapshot; this is addressed in Chapter 5 of this thesis. We now detail our specific research contributions.

#### 1.1.1 Efficient Address Translation for Multiple Page Sizes

In almost all modern systems today, processors and operating systems (OSes) support multiple memory page sizes. These systems have a base page size (or small page size), typically 4KBs, and page sizes that are multiples of the base page size. For example, x86-64 has support to 2MB and 1GB page sizes. A page that is larger than a base page size is called a superpage. Superpages increase Translation Lookaside Buffer (TLB) hits, while small pages provide fine-grained memory protection. Ideally, TLBs should perform well for any distribution of page sizes. In reality, set-associative TLBs used frequently for their energy efficiency compared to fully-associative TLBs - cannot (easily) support multiple page sizes concurrently. Instead, commercial systems typically implement separate set-associative TLBs for different page sizes. This means that when superpages are allocated aggressively, TLB misses may, counter-intuitively, increase even if entries for small pages remain unused (and vice-versa). This happens because TLBs have fixed size that the operating systems are not aware of.

We propose MIX TLBs, energy-frugal set-associative structures that concurrently support all page sizes by exploiting superpage allocation patterns. MIX TLBs boost the performance (often by 10-30%) of big-memory applications on native CPUs, virtualized CPUs, and GPUs. MIX TLBs are simple and require no software changes.

#### 1.1.2 Scalable Distributed Shared Last-Level TLBs

Modern computer systems implement per-core multi-level TLBs. Recent studies have, however, shown the potential of replacing private per-core L2 TLBs with a last-level TLBs shared by multiple cores. A key stumbling block hindering their effectiveness however is their high access time.

We present a design methodology to reduce these high access times so as to realize high-performance and *highly scalable* shared L2 TLBs. As a first step, we study the benefits of replacing monolithic shared TLBs with a distributed set of small TLB slices. While this approach does reduce TLB lookup latency, it increases interconnect delays in accessing remote slices, jeopardizing overall performance. Therefore, as a second step, we devise a lightweight single-cycle interconnect among the TLB slices by tailoring wires and switches to the unique communication characteristics of memory translation requests and responses. Our approach combines the high hit rates of shared TLBs with low access times of private L2 TLBs, enabling significant system performance benefits.

#### 1.1.3 Scheduling Page Table Walks for Irregular GPU Applications

Throughput-oriented accelerators, such as GPUs, pose pressure on TLBs and page table walkers. "Big data" applications with memory accesses with poor locality can halt a GPU completely due to outstanding address translation requests. Recent studies [210] on commercial hardware demonstrated that irregular "big data" GPU applications can bottleneck on virtual-to-physical address translations. We explore ways to reduce address translation overheads for such applications.

We discover that the order of servicing a GPU's address translation requests (specifically, page table walks) plays a key role in determining the amount of translation overhead experienced by an application. We find that different SIMD instructions executed by an application require vastly different amounts of *work* to service their address translation needs, primarily depending upon the number of distinct pages they access. We show that better forward progress is achieved by prioritizing translation requests from the instructions that require less work to service their address translation needs.

Further, in the GPU's Single-Instruction-Multiple-Thread (SIMT) execution paradigm, all threads that execute in lockstep (wavefront) need to finish operating on their respective data elements (and thus, finish their address translations) before the execution moves ahead. Thus, batching walk requests originating from the same SIMD instruction could reduce unnecessary stalls. We demonstrate that the reordering of translation requests based on the above principles improves the performance of several irregular GPU applications by 30% on average.

#### 1.1.4 Secure, Consistent, and Fast Memory Snapshotting

Many security and forensic analyses rely on the ability to fetch memory snapshots from a target machine. With that, we can complement the security mechanisms offered by VM memory protection. To date, the security community has relied on virtualization, external hardware or trusted hardware to obtain such snapshots. These techniques either sacrifice snapshot consistency or degrade the performance of applications executing atop the target. We present SNIPSNAP, a new snapshot acquisition system based on on-package DRAM technologies that offers snapshot consistency without excessively hurting the performance of the target's applications. We realize SNIPSNAP and evaluate its benefits using careful hardware emulation and software simulation.

#### 1.2 Thesis Organization

Having described the problems this thesis addresses, Figure 1.1 also shows the various chapters of this thesis and how we address these problems. In more detail:

Chapter 2 describes MIX TLBs [66] (published in ASPLOS '17), which is used to achieve efficient address translation on CPUs and GPUs, in bare-metal and virtualized environments.

Chapter 3 describes NOCSTAR [31] (published in MICRO '18), which is used to achieve efficient address translation on CPUs with big-memory systems in bare-metal and virtualized environments.

Chapter 4 describes a novel GPU TLB miss scheduling [195] (published in ISCA '18), a mechanism to efficiently reorder page table walks of irregular GPU applications.

Chapter 5 describes SNIPSNAP [67] (published in CODASPY '18), a mechanism to efficiently and securily acquire memory snapshots by complementing the virtual memory abstraction.

Chapter 6 discusses conclusions and future directions.

### Chapter 2

# Efficient Address Translation for Multiple Page Sizes

#### 2.1 Introduction

The operating system's (OS') choice of page sizes for an application's memory needs critically impacts system performance. Modern processors and OSes maintain multiple page sizes. Superpages (or large pages) increase Translation Lookaside Buffer (TLB) hit rates [158, 201, 202]. Small pages provide fine-grained page protection and permissions [158, 202, 170]. This work's objective is to design a TLB that leverages any distribution of page sizes, with the following properties:

(1) Good performance: TLB hardware should not be underutilized and conflict misses should be avoided.

(2) Energy efficiency: TLBs can consume a significant amount – as much as 13-15%

[80, 124, 120, 121, 196] – of processor energy. Our design should be energy-efficient.

(3) Simple implementation: TLBs reside in the timing-critical L1 datapath of pipelines, and must be simple to meet timing constraints. This means that TLB lookup, miss handling, and fill must not be complex.

Meeting all three objectives, while handling multiple page sizes, is challenging. Meeting (2) means that we use set-associative rather than fully-associative TLBs. However, set-associative TLBs cannot (easily) support multiple page sizes. This is because, on lookup, they need the lower-order bits of the virtual page number to select a TLB set. But identifying the virtual page number requires the page size, so that the page offset bits can be masked off. This presents a chicken-and-egg problem, where the page

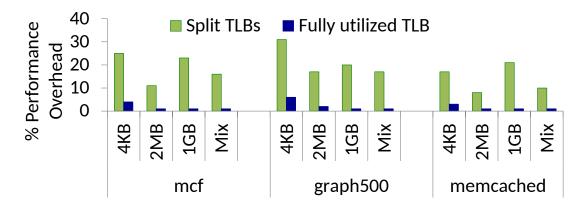

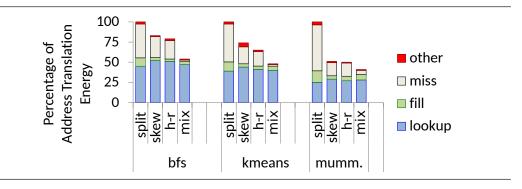

Figure 2.1: Percentage of runtime devoted to address translation, running natively on Intel Haswell with Linux (green). We assume cases where the OS allocates only one page size (4KB, 2MB, 1GB) and when page sizes are mixed. We compare performance against an ideal case where all TLB resources are well-utilized (blue).

size is needed for TLB lookup, but lookup is needed to determine page size. In general, industry and academia have responded in two ways, which compromise (1) and/or (3).

**Split TLBs:** Most processor vendors use split (or partitioned) TLBs, one for each page size [109, 110, 161]. This side-steps the need for page size on lookup. A virtual address can look up all TLBs in parallel. Separate index bits are used for each TLB, based on the page size it supports; *e.g.*, the set indices for split 16-set TLBs for 4KB, 2MB, and 1GB pages (assuming an x86 architecture) are bits 15-12, 24-21, and 33-30 respectively. Two scenarios are possible. In the first, there is either hit in one of the split TLBs, implicitly indicating the translation's page size. In the second, all TLBs miss [161].

Unfortunately, while split TLBs achieve ③, and arguably ②, they often underutilize TLBs and compromise ①. The problem is that if the OS allocates mostly small pages, superpage TLBs remain wasted. On the other hand, when OSes allocate mostly superpages, performance is (counterintuitively) worsened because superpage TLBs thrash while small page TLBs lie unused [84, 48]. Figure 2.1 quantifies the extent of the problem, showing the percentage of runtime that mcf, graph500, and memcached devote to address translation. Results are collected using performance counters on Intel Haswell systems with 84GB of memory, running Linux with the methodology of Section 2.6. We assume that the OS allocates only a fixed page size (*i.e.*, 4KB, 2MB, 1GB) or mixed

pages. One would expect that using large pages consistently improves performance. In reality, performance remains poor even with, for example, 1GB pages (green bars). Further, we compare these numbers to a hypothetical ideal set-associative TLB which can support all page sizes (blue); the gap with the green bars indicates the performance potential lost due to poor utilization of split TLBs.

Multi-indexing approaches: In response to this problem, past work has augmented set-associative TLBs to concurrently support multiple page sizes [161, 193]. Unfortunately, while this does improve (1), it does so at the cost of (2) and (3). The central problems, described in Section 2.5.1, are variable access latencies, increased access energy, and complex implementation. Even in the rare cases when they are implemented commercially, they don't support all page sizes (*e.g.*, Intel's Haswell, Broadwell, and Skylake L2 TLBs cache 4KB and 2MB pages together but not 1GB pages, which require separate TLBs [109, 110]).

**Our contributions:** This work proposes (**MIX**) **TLBs**, fast ①, energy-efficient ②, and readily-implementable ③ structures that concurrently support all page sizes. MIX **TLBs** use a single set-indexing scheme – the one for small pages (*e.g.*, 4KB pages on x86) – for translations of all page sizes. While this simplifies the design, it also presents a problem. We use bits within the superpage page offset to select a TLB set. This means that a superpage is mapped to multiple (potentially all) TLB sets, an operation we refer to as **mirroring** (see Section 2.3). We overcome this problem, however, by observing that OSes frequently (though they don't have to) allocate superpages (not just their constituent small pages) in adjacent or *contiguous* virtual and physical addresses. We detect these adjacent superpages, and **coalesce** them into the same TLB entry (see Section 2.3). If we coalesce as many, or close to as many, superpages as the number of mirror copies – which we usually can in real-world systems – we counteract the redundancy of mirrors, achieving energy-efficient performance.

This work showcases MIX TLBs, their ease of implementation, and performance improvements of 10-30%. Using real-system characterization and careful simulation, we compare MIX TLBs to traditional set-associative designs, and previously proposed TLBs

for concurrent page sizes [161, 193]. We also characterize superpage allocation patterns. Our results focus on Linux, but we've also studied FreeBSD and Solaris. One might initially expect that highly loaded sytems with long uptimes would be hard-pressed to defragment memory sufficiently to allocate superpages adjacently. Indeed, we observe that if system memory is sufficiently fragmented, OSes rarely generate superpages at all. However, we also observe that if OSes can generate even a few superpages, they have usually defragmented memory sufficiently to generate other adjacent and contiguous superpages too. MIX TLBs outperform their counterparts in both cases. When superpages are scarce, MIX TLBs use all TLB resources for small pages. When superpages are present, MIX TLBs seamlessly leverage any distribution of page sizes.

#### 2.2 Scope of This Work

Systems are embracing workloads with increasing memory needs and poorer access locality (*e.g.*, massive key-value stores, graph processing, data analytics, deep learning frameworks, etc.). These workloads stress hardware TLB performance; as a result, address translation overheads often consume 15-30% of runtime today [169, 168, 29, 33, 35].

MIX TLBs also aid virtualized systems, where address translation is even more pernicious. Virtualized systems require two dimensions of address translation - guest virtual pages are converted to guest physical pages, which are then translated to system physical pages [170, 84, 32]. Two-dimensional page table walks are expensive, requiring 24 sequential memory accesses in x86 systems, instead of the customary 4 accesses for non-virtualized systems. Virtualization vendors like VMware identify TLB misses as a major culprit in the performance difference between non-virtualized and virtualized systems [170, 84, 48].

Finally, vendors have begun embracing shared virtual memory abstractions for heterogeneous systems made up of CPUs and GPUs [172, 173, 175, 17, 18, 134, 210, 216], accessing a single virtual address space. This allows "a pointer is a pointer everywhere" simplications of the programming model [134, 210]. However, now GPUs must also

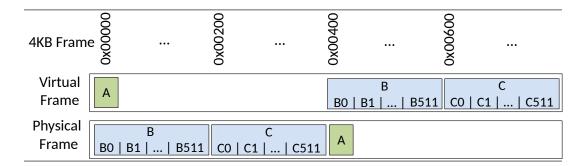

Figure 2.2: Example address space in an x86-64 architecture. We show 4KB frame numbers in hexadecimal. For example, translation B is for a 2MB page, made up of 4KB frame numbers B0-B511. 2MB translations B-C are contiguous.

perform address translation, just like CPUs. GPU TLBs are critical to performance as they must service the demands of hundreds to thousands of concurrent threads [172, 173, 210]. Unfortunately, we find that CPU-GPU systems also suffer from TLB utilization issues when using multiple page sizes.

#### 2.3 High-Level Approach

We compare MIX TLBs to traditional split TLBs, using the address space of Figure 2.2. We show virtual and physical address spaces, with translations for small pages (A), and superpages (B-C). Without loss of generality, we assume an x86-64 architecture with 4KB and 2MB pages (1GB are handled similarly). Note that while we assume 64-bit systems, our examples show 32-bit addresses to save space. These addresses are shown in 4KB frame numbers (full addresses can be constructed by appending 0x000). Therefore, superpage B is located at virtual address 0x00400000 and physical address 0x00000000. Superpages B and C have 512 constituent 4KB frames, indicated by B0-511 and C0-511.

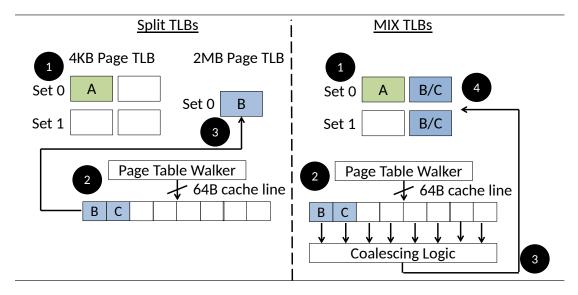

Figure 2.3 illustrates the lookup and fill operation of MIX TLBs and contrasts it to split TLBs. In step ①, B is looked up. However, since B is absent (both split and MIX TLBs maintain only A), the hardware page table walker is invoked ②. The page table walker reads the page table in units of caches lines; since a typical cache line is 64 bytes, and translations are 8 bytes, 8 translations (including B and C) are read in the cache line. Split TLBs then fill B into the superpage TLB ③. Unfortunately, there remains

Figure 2.3: Superpage B lookup and fill for split versus MIX TLBs.

no room for C despite 3 unused small page TLB entries.

MIX TLBs, on the other hand, cache all page sizes. After a miss (1) and a page table walk (2), we must fill B in the correct set. This presents a challenge; since MIX TLBs use the index bits for small pages (in our 2-set TLB example, bit 12) on all translations, the index bits are picked from the superpage's page offset. Thus, superpages do not uniquely map to either set. Instead, we mirror B in both TLB sets.

Mirroring presents a problem. Whereas split TLBs maintain one copy of a superpage translation, MIX TLBs maintain several mirror copies, reducing effective TLB capacity. However, MIX TLBs counteract this problem with the following observation – OSes frequently (though they don't have to) allocate superpages adjacently in virtual and physical addresses. For example, Figure 2.2 shows that B and C are contiguous, not just in terms of their constituent 4KB frames (*e.g.*, B0-511 and C0-511) but also in terms of the full superpages themselves. MIX TLBs exploit this contiguity; when page table walkers read a cache line of translations (2), adjacent translations in the cache line are scanned to detect contiguous superpages. We propose, similar to past work [169, 168], simple combinational coalescing logic for this (3). In our example, B and C are contiguous and are hence coalesced and mirrored. Coalescing counteracts mirroring. If there are as many contiguous superpages as there are mirror copies (or close to as

Figure 2.4: Though superpages B and C are maintained by multiple sets but on lookup, we only probe the set corresponding to the 4KB region within the superpage that the request is to.

many), MIX TLBs coalesce them to achieve a net capacity corresponding to the capacity of superpages, despite mirroring.

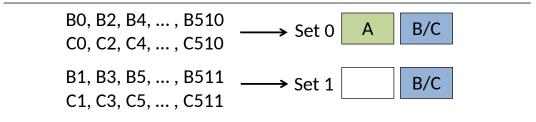

Crucially, Figure 2.4 shows that MIX TLB lookup remains simple. While coalesced mirrors of superpages reside in multiple sets, lookups only probe one TLB set. In other words, virtual address bit 12 in our example determines whether we are accessing the even- or odd-numbered 4KB regions within a superpage; therefore accesses to B0, B2, etc., and C0, C2, etc., are routed to set 0.

Naturally, this overview presents several important questions. We briefly address them below:

Why do MIX TLBs use the index bits corresponding to the small pages? Specifically, one may instead consider using the index bits corresponding to the superpage and apply that on small pages too. In our example, this would be like using virtual address bit 21 as the index (assuming we base the index on 2MB superpages). The advantage of this approach is that each superpage maps uniquely to a set, *eliminating* the need for mirrors (*e.g.*, B maps to set 0, and C maps to set 1).

Unfortunately, this causes a different problem. Now, spatially adjacent small pages map to the same set. For example, if we use the index bits corresponding to a 2MB superpage (*i.e.*, in our 2-set TLB example, bit 21), groups of 512 adjacent 4KB virtual pages map to the same set. Since real-world programs exhibit spatial locality, this elevates TLB conflicts (unless associativity exceeds 512, which is far higher the 4-8 way associativity used today [109, 110]). One could envision coalescing these small pages if the OS does allocate them contiguously in virtual and physical addresses; however past work shows that while small pages can be contiguous, they usually are not contiguous beyond more than tens of pages [169, 168]. We have evaluated using superpage index bits and have found that they increase TLB misses by  $4-8\times$  on average, compared to using small page index bits.

Why do MIX TLBs perform well? MIX TLBs are well utilized for any distribution of page sizes. When the system is highly fragmented and superpages are scarce, all TLB resources can be used for small pages. When the OS can generate superpages, it usually sufficiently defragments physical memory to allocate superpages adjacently too. MIX TLBs utilize all hardware resources to coalesce these superpages.

How many mirrors can a superpage produce and how much contiguity is needed? Assume that the superpage has N 4KB regions, and that our MIX TLB has M sets. N is 512 and 262144 for 2MB and 1GB superpages. Practical commercial L1 and L2 TLBs tend to have 16-128 sets [161, 109, 110]. Therefore, today's systems have N > M, meaning that a superpage has a mirror per set (or N mirrors). However, if future systems see N < M, there would be M mirrors.

Ultimately, good MIX TLB utilization relies on superpage contiguity. If the number of contiguous superpages is equal (or sufficiently near) the mirror count, performance is good. On modern 16-128 set TLBs, we desire (close to) 16-128 contiguous superpages. Section 2.7.1 shows that real systems do frequently see this much superpage contiguity. Section 2.4 shows how we can coalesce these many contiguous superpages, despite only scanning for contiguity within a single cache line, which maintain 8 translations, on a TLB miss.

#### 2.4 Hardware Details

We now detail MIX TLB hardware, implementing them differently for the L1 and L2 levels. L1 MIX TLBs must be simple and fast; we sacrifice some coalescing opportunity to meet these requirements. L2 MIX TLBs can tolerate higher access latencies (*e.g.*, Intel and AMD L2 TLBs usually have 5-7 cycle access times [161]). Therefore, L2 MIX TLBs support more coalescing with (slightly) more complex hardware. MIX TLBs require no

Figure 2.5: Traditional TLB and MIX TLB entries for the translation corresponding to 4KB page A. We show the TLB entries at the L1 and L2 level, assuming both have 4 sets. MIX TLBs require just an additional 2 bits to record the page size.

OS or application changes.

#### 2.4.1 MIX TLB Entries

MIX TLB entries are similar to traditional set-associative entries. We detail the modest differences between the two. Although actual x86-64 architectures can use up to 52-bit physical addresses, use assume 48-bit physical addresses in our example for simplicity. Extending this approach to 52-bits parallels our example.

**Small pages**: Figure 2.5 contrasts traditional TLB and MIX TLB entries for 4KB pages. We use translation A from Figure 2.2, and assume 4-set L1 and L2 TLBs. Therefore, the two least significant bits of the virtual page need not be stored in the tag. MIX TLBs only require a 2-bit page size field to distinguish among the 3 page sizes. Though they are not shown, the entries also maintain page permission bits.

Superpages: Figure 2.6 compares traditional to MIX TLB entries for superpages, assuming 2-set TLBs. Aside from the page size, MIX TLBs must maintain information about coalesced superpages. L1 entries use a bitmap for this. 2-set MIX TLBs maintain a 2-bit bitmap to record coalescing information of up to two superpages. Furthermore, since this entry caches superpage information, it uses 9 fewer tag bits for this versus small page entries. In fact, we can even drop a 10th bit because 2-bit bitmaps implicitly store information about  $2 \times 2MB$  (4MB) memory regions. These bits can be repurposed

Figure 2.6: Traditional TLB and MIX TLB entries for the translation corresponding to 2MB pages B-C. L1 MIX TLB and L2 MIX TLB entries use a bitmap and a length field to record contiguous superpages, respectively. We assume 2-set TLBs.

for the bitmap. Figure 2.6 records 0b11 to indicate information about contiguous superpages B and C.

L2 MIX TLBs record longer contiguity, with marginally greater complexity. Instead of a bitmap, we use a contiguity length field. Therefore, a 2-bit length field (though it could use more bits) records contiguity of up to 4 superpages.

MIX TLBs are only marginally bigger than a standard set-associative entry since the bitmap and length fields are repurposed with unused tag bits. Only a 2-bit page size field is added, increasing per-entry size by less than 1%.

Alignment restrictions: To simplify MIX TLB hardware, we only coalesce superpages that are suitably aligned. Specifically, to coalesce up to N superpages, only contiguous superpages that begin at virtual address boundaries of N may be coalesced. Our MIX TLB example in Figure 2.6, which coalesces up to 2 superpages, therefore only coalesces superpages that begin at multiples of  $2 \times 2$ MB or 4MB. This does reduce coalescing opportunity slightly, but as we show in Section 2.7.2, performance continues to be good.

**Bitmap versus length:** For the same number of bits, length fields record more information, allowing L2 MIX TLBs to coalesce longer runs of contiguous superpages. The

Figure 2.7: L1 MIX TLB lookup and hit (assuming a 2-set TLB). The physical address is found using bit shifting and concatenation.

slight downside is the slightly more complex TLB lookup this prompts (which we detail later in this section). L1 bitmaps do have one more advantage – they can record information about "holes" in contiguously allocated superpages.

# 2.4.2 MIX TLB Operation

In this section, we describe MIX TLB operation, including hits, misses, and fills.

L1 lookup: Figure 2.7 shows how L1 MIX TLBs are looked up. Since 4KB page lookups remain unchanged, we focus on superpages. Index bits are selected from the virtual address as per small page size – therefore, assuming a 2-set TLB and 4KB small pages, we use bit 12 as the index. Consequently, there is a question as to what happens with the remainder of the 2MB page offset, bits 20-13, and bits 11-0. We call bits 20-13 the mirror ID, as they identify individual 4KB regions within a superpage (*i.e.*, B0, B1, B2, etc., in Figure 2.4). Bits 11-0 are the offset within these 4KB regions. Finally, the remaining upper order bits of the virtual address are split into a tag and a page ID. The page ID identifies the specific superpage within a contiguous bundle – since our example assumes a 2-set TLB that can coalesce up to 2 entries, 1 page ID bit suffices

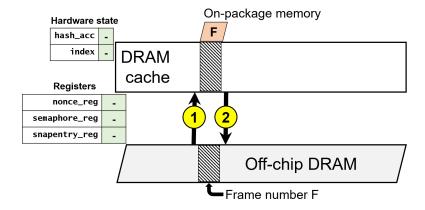

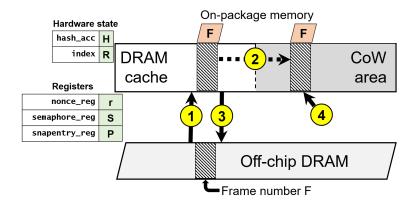

to identify the desired superpage.