### VIRTUAL MEMORY FOR NEXT-GENERATION TIERED MEMORY ARCHITECTURES

$\mathbf{B}\mathbf{y}$

ZI YAN

A dissertation submitted to the Schoool of Graduate Studies Rutgers, The State University of New Jersey In partial fulfillment of the requirements For the degree of Doctor of Philosophy Graduate Program in Computer Science Written under the direction of Abhishek Bhattacharjee And approved by

#### ABSTRACT OF THE DISSERTATION

### Virtual Memory for Next-Generation Tiered Memory Architectures

by Zi Yan

### Dissertation Director: Abhishek Bhattacharjee

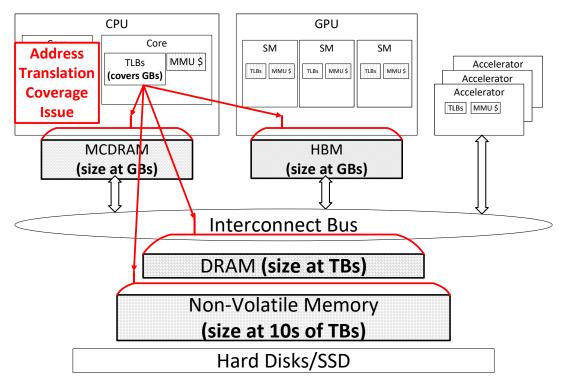

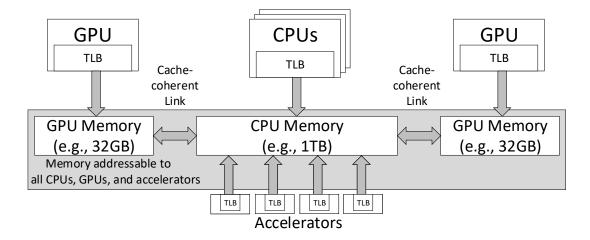

Virtual memory offers a simple hardware abstraction to programmers freeing them from the tedious process of manual memory management. However, the emergence of new memory technologies is posing challenges for conventional virtual memory. Homogeneous memory systems are being replaced by complex heterogeneous systems with multiple memory devices with different latency, bandwidth, and capacity characteristics. This poses two problems. The first is that operating systems (OSes) must migrate pages among the heterogeneous memory devices based on attributes like page hotness and proximity to the compute unit/accelerator that uses the data. As this thesis shows, current support for page migration is infeasibly slow on emerging hardware, both due to the slow speeds of data movement and metadata update operations like TLB shootdowns. The second is that the ever-increasing aggregate capacities of these emerging heterogeneous memory systems pose immense pressure on TLBs, aggravating address translation overheads. This thesis addresses these problems by proposing modest hardware/software techniques that achieve a more efficient virtual memory system via fast hardware support for translation coherence, software support for faster page copies, and hardware/software co-design that compresses TLB entries to reduce address translation overheads.

Page migration is the means by which OSes can dynamically shift data to the memory devices that best benefit latency, bandwidth, capacity, and persistence characteristics in different phases of the program lifetime. The key to good performance is fast page migration. This thesis attacks two bottlenecks that currently constrain page migration performance — high-overhead translation coherence and low-throughput page copying. To mitigate the first source of overhead, this thesis implements hardware support for translation coherence by fusing it with existing cache coherence protocols. To mitigate the second source of overhead, this thesis implements OS support that parallelizes, aggregates, and consolidates page migration operations to maximize migration throughput.

Heterogeneous systems are also continuing a trend that has long been seen with traditional homogeneous memory systems — the drive towards ever-increasing memory capacities. Specific types of emerging systems with die-stacking technologies and byte-addressable persistent memories are further accelerating the total physical memory capacity that must be addressable for each process. Consequently, page tables are becoming bigger and TLB misses more frequent. To mitigate increasing address translation overheads, this thesis offers software techniques to facilitate the possibility of compressing TLB entries which rely on translation contiguity.

In summary, this work upgrades virtual memory to effectively support heterogeneous memory systems with high-performance page migration and scalable address translation. In so doing, this dissertation identifies bottlenecks in the existing virtual memory, profiles the performance impacts of these bottlenecks, and proposes hardware and software solutions to remedy them.

### Acknowledgements

First of all, I would like to thank my advisor Abhishek Bhattacharjee. He provided enormous help throughout my Ph.D. study both personally and professionally. He always gave me the freedom to explore my own research and pushed me to improve in all aspect of my career. I will be always grateful for his mentorship.

I would also like to thank Daniel Lustig, David Nellans, and the rest of my thesis committee: Ulrich Kremer, Sudarsun Kannan, and Gabriel Loh. Their feedback and suggestions helped me greatly improve my thesis. I would especially like to thank Daniel Lustig and David Nellans for all of their support and guidance during the latter half of my Ph.D. study. I really enjoyed our weekly meetings and research discussions, which are invaluable research experience.

I cannot thank my girlfriend, Shisi Wang, enough for her great support during my Ph.D. She was always there no matter what happened. We shared all the highs and lows together. It is my fortune to be with her.

My colleagues have been important and helpful to the completion of my thesis. Bharath Pichai, Binh Pham, Jan Vesely, Guilherme Cox, Karthik Sriram, and Jae Woo Ju have all provided feedback, support, and entertainment through the years I spent in Rutgers.

## Dedication

To Shisi, Mom, and Dad

## Table of Contents

| A             | ostra            | act                                                     |     |    |  |  | • |  | ii |

|---------------|------------------|---------------------------------------------------------|-----|----|--|--|---|--|----|

| A             | Acknowledgements |                                                         |     |    |  |  |   |  |    |

| De            | Dedication       |                                                         |     |    |  |  |   |  |    |

| $\mathbf{Li}$ | st of            | f Tables                                                |     |    |  |  |   |  | х  |

| $\mathbf{Li}$ | st of            | f Figures                                               |     |    |  |  |   |  | xi |

| 1.            | Intr             | roduction                                               |     |    |  |  | • |  | 1  |

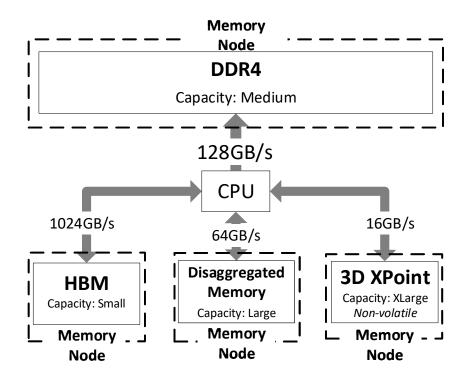

|               | 1.1.             | . Memory Systems                                        |     |    |  |  |   |  | 2  |

|               | 1.2.             | . Research Goals                                        |     |    |  |  |   |  | 7  |

|               | 1.3.             | . Fast Page Migration                                   |     |    |  |  |   |  | 8  |

|               |                  | 1.3.1. Low Overhead Hardware Translation Coherence      |     |    |  |  |   |  | 9  |

|               |                  | 1.3.2. High Throughput Operating System Page Migra      | tio | n. |  |  |   |  | 10 |

|               | 1.4.             | . Scalable Address Translation with Fast Page Migration |     |    |  |  |   |  | 11 |

|               | 1.5.             | . Contributions                                         |     |    |  |  |   |  | 12 |

|               | 1.6.             | . Dissertation Organization                             |     |    |  |  |   |  | 13 |

| 2.            | Har              | urdware Translation Coherence for Virtualized Syst      | en  | ıs |  |  | • |  | 14 |

|               | 2.1.             | . Introduction                                          |     |    |  |  |   |  | 14 |

|               | 2.2.             | . Background                                            |     |    |  |  |   |  | 18 |

|               |                  | 2.2.1. HW and SW Support for Virtualization             |     |    |  |  | • |  | 18 |

|               |                  | 2.2.2. Page Remapping in Virtualized Systems            |     |    |  |  | • |  | 20 |

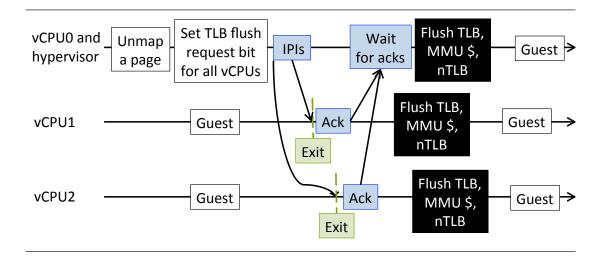

|               | 2.3.             | . Software Translation Coherence                        |     |    |  |  |   |  | 21 |

|               |                  | 2.3.1. Translation Coherence Overheads                  |     |    |  |  |   |  | 22 |

|               |                  | 2.3.2. Page Remapping Anatomy                           |     |    |  |  | • |  | 24 |

|            |                                                  | 2.3.3.                                                   | Hardware Versus Software Solutions                                                                                                                                             | 26                                                                                                                                 |

|------------|--------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|            | 2.4.                                             | Hardw                                                    | are Design                                                                                                                                                                     | 26                                                                                                                                 |

|            |                                                  | 2.4.1.                                                   | Co-Tags                                                                                                                                                                        | 27                                                                                                                                 |

|            |                                                  | 2.4.2.                                                   | Coherence States and Initiators                                                                                                                                                | 29                                                                                                                                 |

|            |                                                  | 2.4.3.                                                   | Coherence Directory and Co-Tag Interaction                                                                                                                                     | 29                                                                                                                                 |

|            |                                                  | 2.4.4.                                                   | Putting It All Together                                                                                                                                                        | 36                                                                                                                                 |

|            |                                                  | 2.4.5.                                                   | Other Key Observations                                                                                                                                                         | 37                                                                                                                                 |

|            | 2.5.                                             | Metho                                                    | dology                                                                                                                                                                         | 39                                                                                                                                 |

|            |                                                  | 2.5.1.                                                   | Die-Stacked DRAM Simulation                                                                                                                                                    | 39                                                                                                                                 |

|            |                                                  | 2.5.2.                                                   | KVM Paging Policies                                                                                                                                                            | 40                                                                                                                                 |

|            |                                                  | 2.5.3.                                                   | Workloads                                                                                                                                                                      | 41                                                                                                                                 |

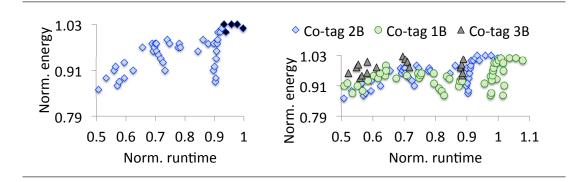

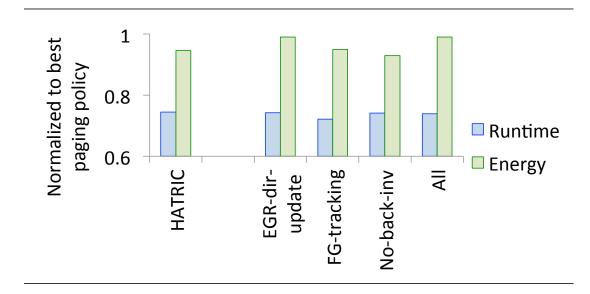

|            | 2.6.                                             | Evalua                                                   | tion                                                                                                                                                                           | 41                                                                                                                                 |

|            | 2.7.                                             | Conclu                                                   | sion                                                                                                                                                                           | 49                                                                                                                                 |

| 3          | Nim                                              | uble Pa                                                  | ge Management for Tiered Memory Systems                                                                                                                                        | 50                                                                                                                                 |

|            | T 4 T T T                                        |                                                          | ge management for frered memory bystems                                                                                                                                        | 00                                                                                                                                 |

| <b>J</b> . |                                                  | Introd                                                   | uction                                                                                                                                                                         | 50                                                                                                                                 |

| 0.         | 3.1.                                             |                                                          | uction                                                                                                                                                                         | 50<br>54                                                                                                                           |

| 0.         | 3.1.                                             | Backg                                                    | round                                                                                                                                                                          | 54                                                                                                                                 |

| 9.         | 3.1.                                             | Backgr<br>3.2.1.                                         | round                                                                                                                                                                          | 54<br>55                                                                                                                           |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.                               | cound                                                                                                                                                                          | 54<br>55<br>56                                                                                                                     |

|            | 3.1.                                             | Backgr<br>3.2.1.<br>3.2.2.<br>Native                     | cound                                                                                                                                                                          | 54<br>55<br>56<br>57                                                                                                               |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native                     | cound          Page Management Policies and Mechanisms          Recent Developments          OS Support for Multi-Level Memories          Optimizing Page Migration Mechanisms | 54<br>55<br>56<br>57<br>57                                                                                                         |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native                     | cound                                                                                                                                                                          | 54<br>55<br>56<br>57<br>57<br>58                                                                                                   |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native                     | round                                                                                                                                                                          | <ol> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>59</li> </ol>                                     |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native                     | round                                                                                                                                                                          | <ul> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> </ul>                         |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native<br>3.3.1.           | cound                                                                                                                                                                          | <ul> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> </ul>             |

|            | <ul><li>3.1.</li><li>3.2.</li><li>3.3.</li></ul> | Backgr<br>3.2.1.<br>3.2.2.<br>Native<br>3.3.1.<br>3.3.2. | cound                                                                                                                                                                          | <ul> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>63</li> </ul> |

|            | 3.1.<br>3.2.                                     | Backgr<br>3.2.1.<br>3.2.2.<br>Native<br>3.3.1.<br>3.3.2. | round                                                                                                                                                                          | <ul> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>63</li> <li>65</li> </ul> |

|            | <ul><li>3.1.</li><li>3.2.</li><li>3.3.</li></ul> | Backgr<br>3.2.1.<br>3.2.2.<br>Native<br>3.3.1.<br>3.3.2. | cound                                                                                                                                                                          | <ul> <li>54</li> <li>55</li> <li>56</li> <li>57</li> <li>57</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>63</li> </ul> |

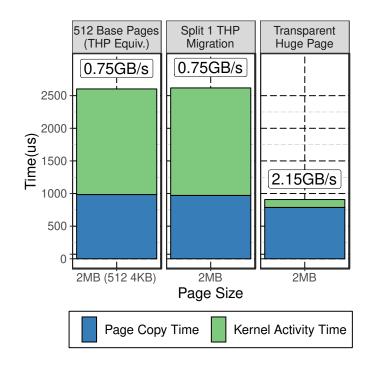

|                               |                                                                                                                                                           | Native THP Migration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

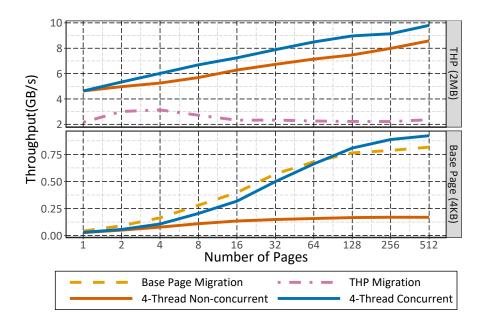

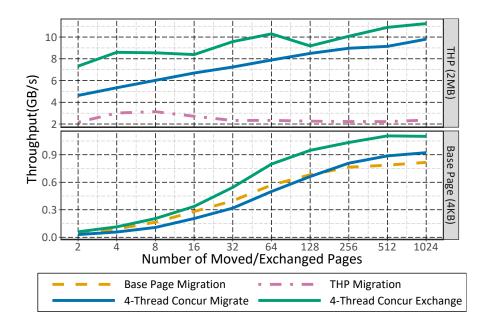

|                               |                                                                                                                                                           | Multi-threaded Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                                                       |

|                               |                                                                                                                                                           | Concurrent Page Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                       |

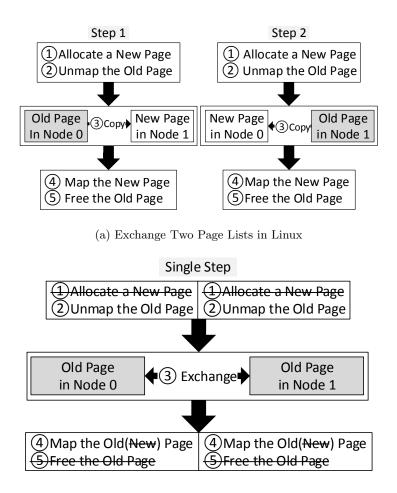

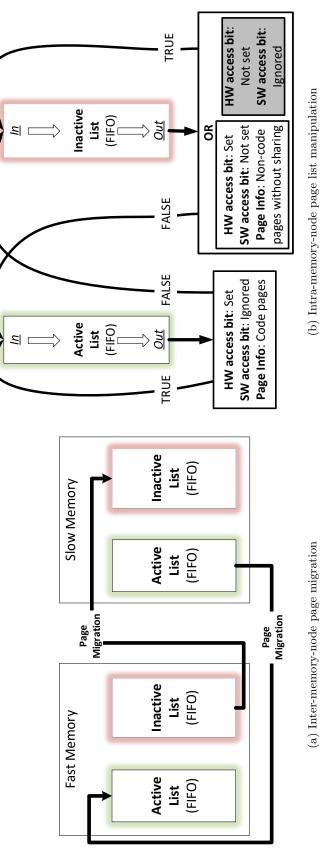

|                               |                                                                                                                                                           | Symmetric Exchange Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                       |

|                               |                                                                                                                                                           | Microbenchmark Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                       |

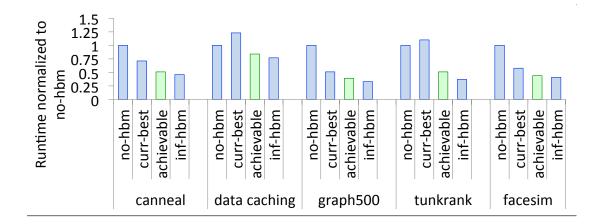

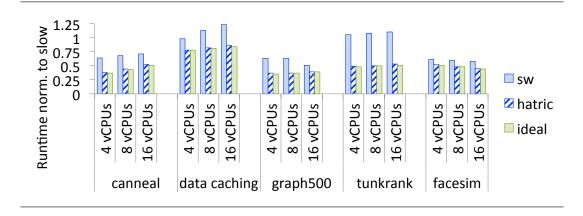

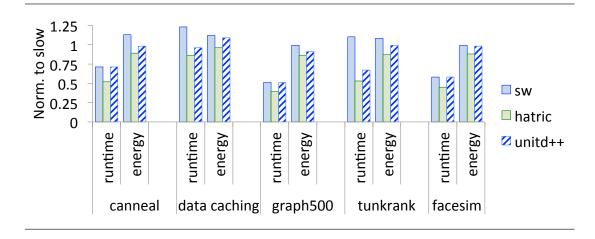

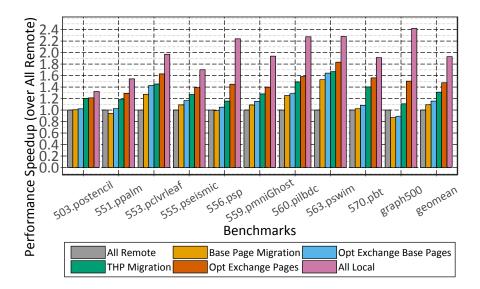

|                               | 3.4.3.                                                                                                                                                    | End-to-End Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71                                                       |

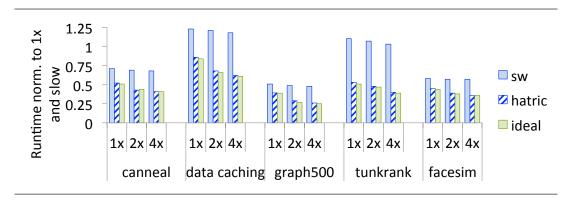

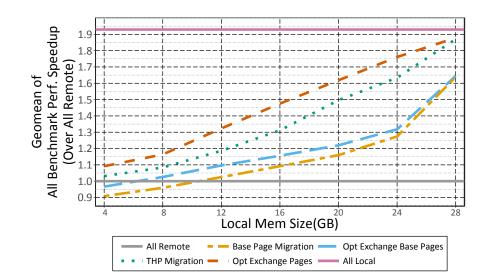

|                               | 3.4.4.                                                                                                                                                    | Sensitivity to Local Memory Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                       |

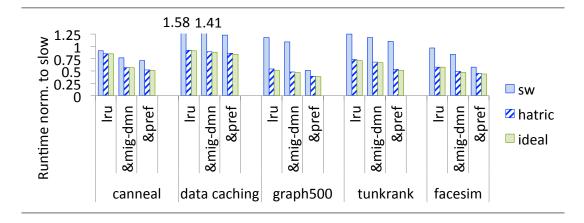

|                               | 3.4.5.                                                                                                                                                    | Sensitivity to Tunable Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                                                       |

|                               |                                                                                                                                                           | Number of threads used for parallel page migration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                                       |

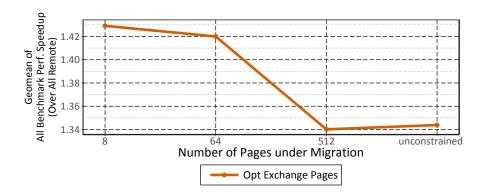

|                               |                                                                                                                                                           | Number of pages being migrated concurrently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75                                                       |

|                               | 3.4.6.                                                                                                                                                    | Architectural Independence of OS Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                       |

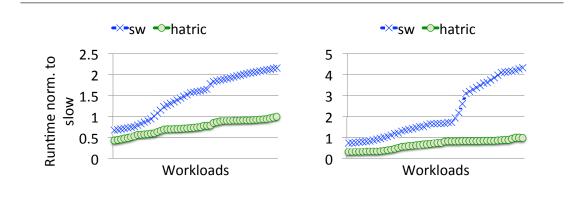

|                               | 3.4.7.                                                                                                                                                    | Summary of Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                                                       |

| 3.5.                          | Relate                                                                                                                                                    | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                       |

| 3.6.                          | Concl                                                                                                                                                     | isions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79                                                       |

|                               |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

| 1 Tra                         | nalatio                                                                                                                                                   | n Pangon Operating System Support to Actively Produce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

|                               |                                                                                                                                                           | n Ranger: Operating System Support to Actively Produce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80                                                       |

| Addres                        | ss Trai                                                                                                                                                   | slation Contiguity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80<br>80                                                 |

| Addres<br>4.1.                | ss <b>Tra</b><br>Introd                                                                                                                                   | aslation Contiguity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                       |

| Addres<br>4.1.                | ss Tran<br>Introd<br>Backg                                                                                                                                | Inslation Contiguity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80<br>83                                                 |

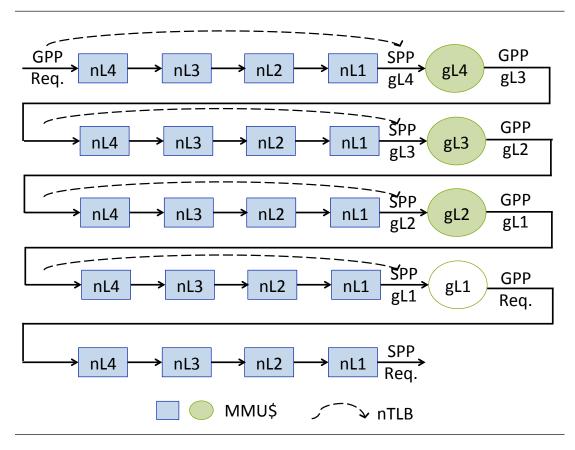

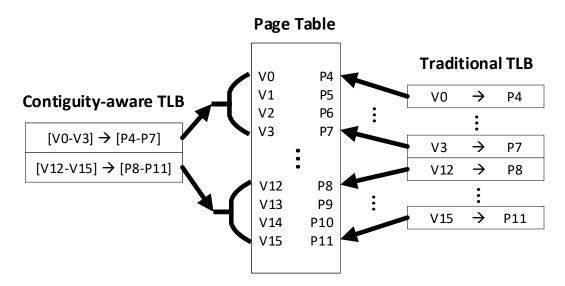

| Addres<br>4.1.                | Introd<br>Backg<br>4.2.1.                                                                                                                                 | Inslation Contiguity       Image: Contiguity         uction       Image: Contiguity         round       Image: Contiguity         Specialized Contiguity-Aware Hardware       Image: Contiguity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80<br>83<br>83                                           |

| Addres<br>4.1.                | <b>Tran</b> Introd Backg 4.2.1. 4.2.2.                                                                                                                    | Instantion Contiguity       Image: Stantage         Instantion Contiguity       Image: Stantage         Instantiation Contiguity-Aware Hardware       Image: Stantage         Improving Allocation-Time Contiguity       Image: Stantage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80<br>83<br>83<br>84                                     |

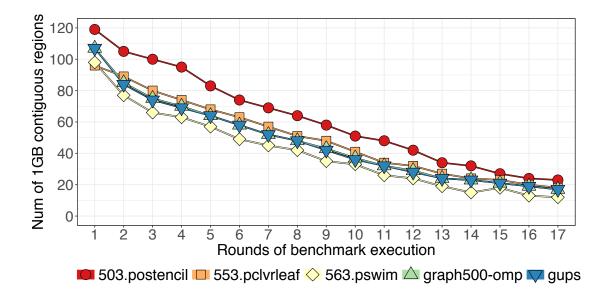

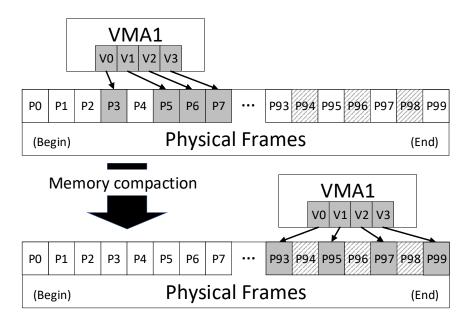

| Addres<br>4.1.                | <ul> <li><b>Tran</b></li> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> </ul>                                            | Instantion Contiguity       Image: Imag          | 80<br>83<br>83                                           |

| Addres<br>4.1.                | <ul> <li><b>Tran</b></li> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> </ul>                                            | Instation Contiguity       Image: Image          | 80<br>83<br>83<br>84                                     |

| <b>Addres</b><br>4.1.<br>4.2. | <ul> <li><b>Tran</b></li> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> </ul>                                            | Inslation Contiguity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80<br>83<br>83<br>84<br>85                               |

| <b>Addres</b><br>4.1.<br>4.2. | <ul> <li><b>5s Tran</b></li> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> <li>Transl</li> </ul>                         | Instantion Contiguity       Image: Imag          | 80<br>83<br>83<br>84<br>85<br>87                         |

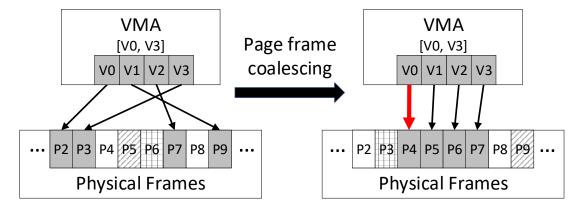

| <b>Addres</b><br>4.1.<br>4.2. | <ul> <li><b>5s Tran</b></li> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> <li>Transl</li> <li>4.3.1.</li> </ul>         | Image: Sector of the sector | 80<br>83<br>83<br>84<br>85<br>87<br>88                   |

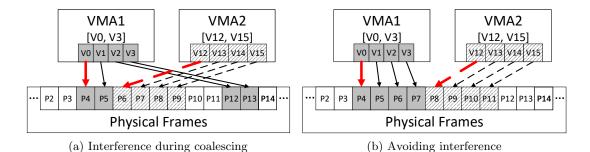

| <b>Addres</b><br>4.1.<br>4.2. | <ul> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> <li>Transl</li> <li>4.3.1.</li> <li>4.3.2.</li> </ul>                 | Implementation Contiguity       Implementation         Instant Contiguity       Implementation         Specialized Contiguity-Aware Hardware       Implementation         Improving Allocation-Time Contiguity       Implementation         Memory Fragmentation and Defragmentation       Implementation         Intra-VMA Page Coalescing       Implementation         Avoiding Inter-VMA Interference       Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80<br>83<br>83<br>84<br>85<br>87<br>88<br>88<br>89       |

| <b>Addres</b><br>4.1.<br>4.2. | <ul> <li>Introd</li> <li>Backg</li> <li>4.2.1.</li> <li>4.2.2.</li> <li>4.2.3.</li> <li>Transl</li> <li>4.3.1.</li> <li>4.3.2.</li> <li>4.3.3.</li> </ul> | Image: A set of the set  | 80<br>83<br>83<br>84<br>85<br>87<br>88<br>88<br>89<br>91 |

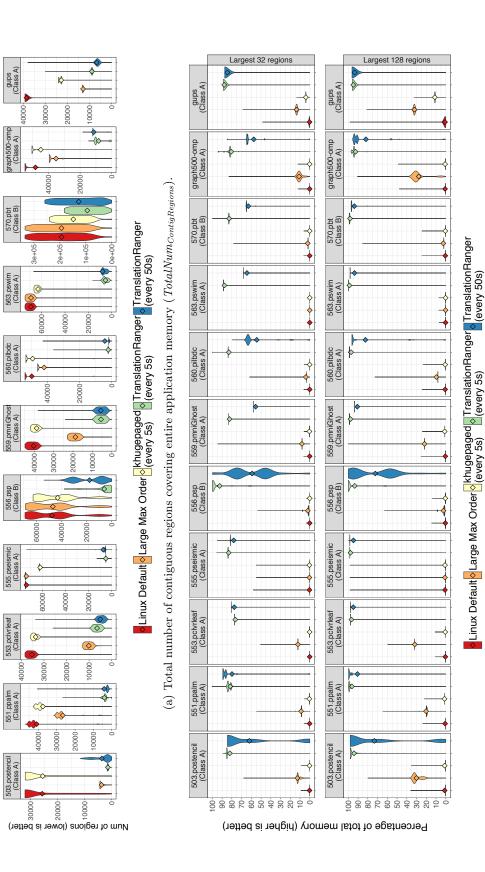

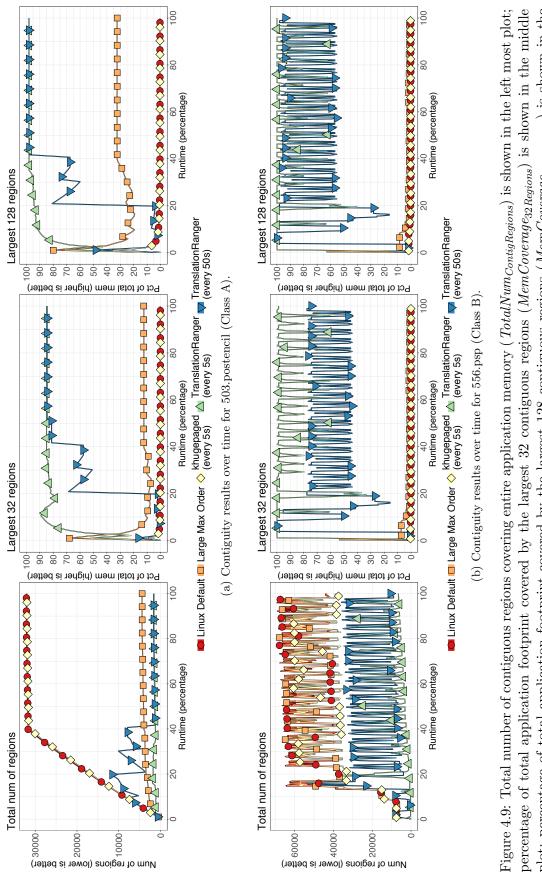

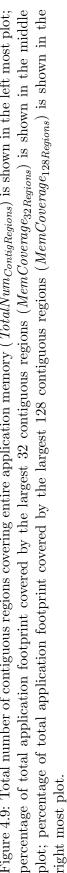

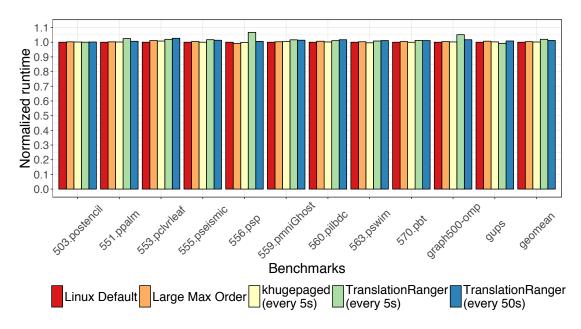

|    |       | 4.4.1. | Evaluation Platform                                                                                                                         |

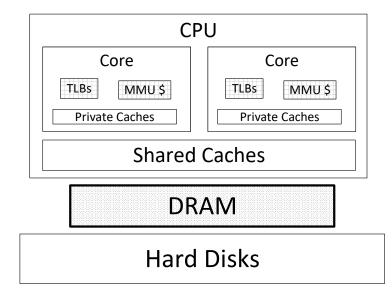

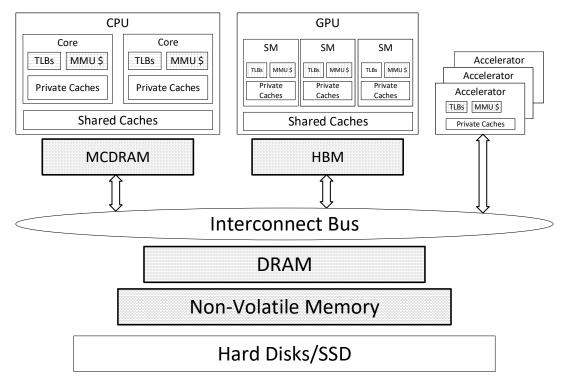

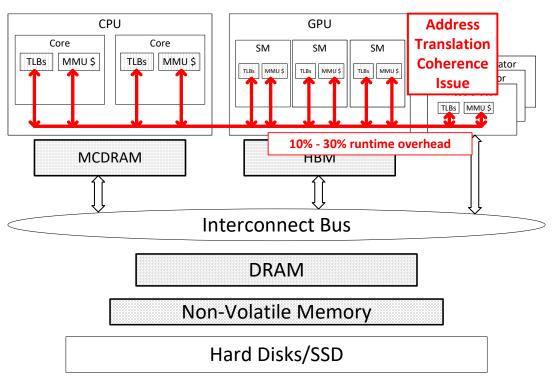

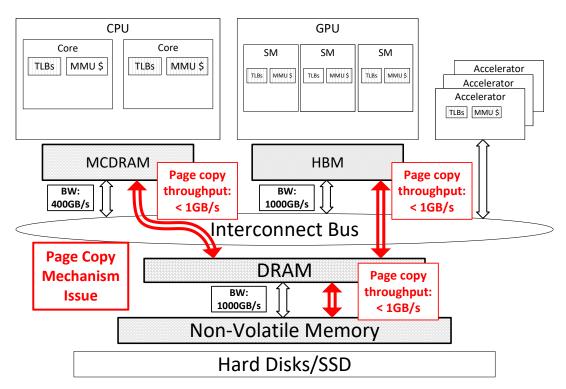

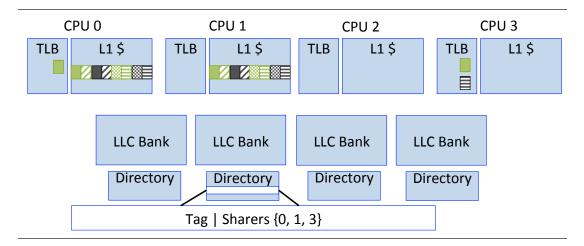

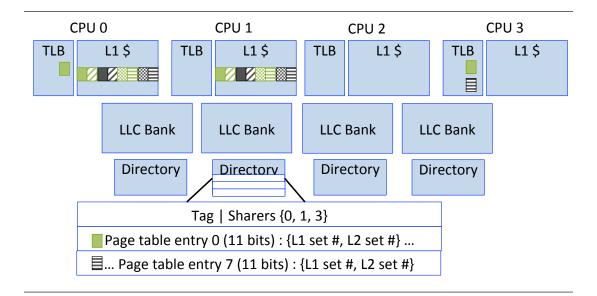

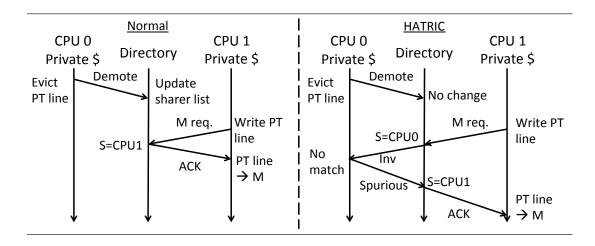

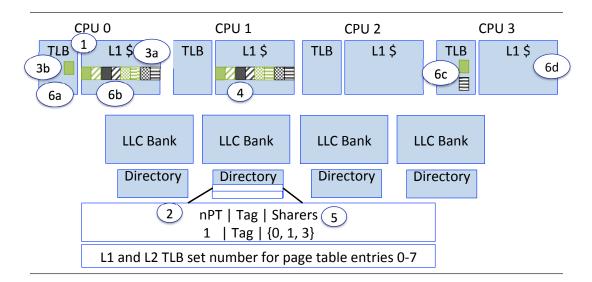

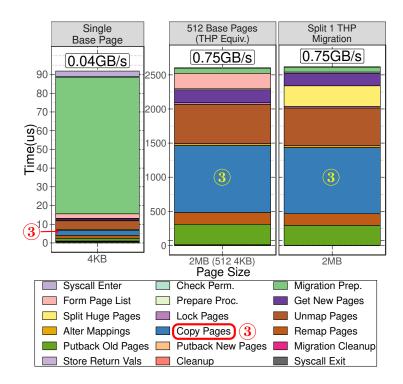

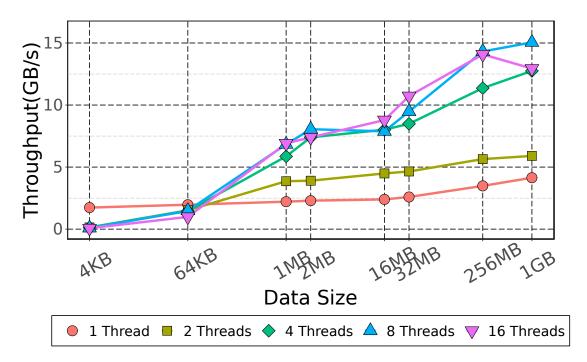

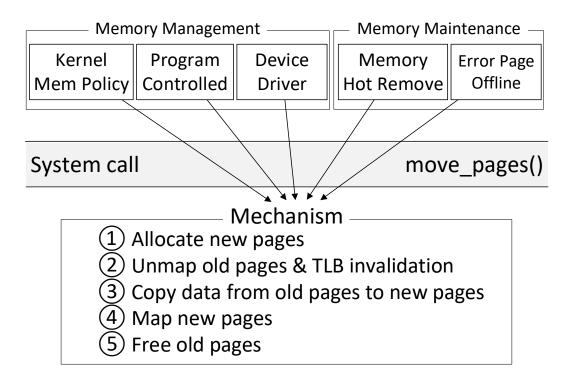

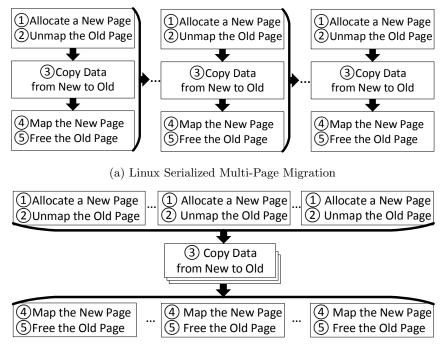

|----|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|